[Blog] Optimizing FPGA Design Simulation Workflow with QuestaSim qrun

Posted 02/19/2026 by Phil Simpson, Product Marketing Manager, Lattice Semiconductor

FPGA development moves fast, and your verification flow and simulations need to keep up. Long compile times, manual setup steps, and constant design changes can easily slow momentum when you are trying to iterate fast. Before a design ever reaches hardware, you need absolute confidence that it behaves exactly as intended. Lattice Radiant® Software, paired with Siemens QuestaSim Lattice FPGA Edition simulator, delivers powerful functional verification capabilities, but the reality is familiar to many engineers: configuring simulations, handling design changes, and keeping everything in sync can quickly become a bottleneck.

This is where Siemens’ QuestaSim qrun makes a real difference. Included in both Lattice Radiant and Lattice Diamond™ software, QuestaSim qrun is designed to simplify and accelerate your simulation workflow. It reduces setup complexity, adjusts effortlessly to ongoing design changes, and helps you move through iterations at a pace that keeps creativity and productivity high. The result is more simulation runs per day, faster debug cycles, and a clear boost in overall efficiency.

In this post, we will look at how to make the most of the QuestaSim qrun , with practical guidance and proven techniques that can help you build a faster and more efficient simulation flow.

What is qrun?

qrun is a command-line tool that streamlines the simulation process in QuestaSim by providing makefile-like incremental compilation, intelligent default values for common command line options, and automatic compiler selection based on file extension. This makes it easier for users to switch between command line mode and GUI mode for debugging.

By streamlining these essential tasks, ‘qrun’ bridges the gap between the command-line and GUI experiences, making it effortless to switch modes and accelerate debugging.

Why Use qrun?

Using qrun offers several advantages:

- Simplified Workflow: qrun supports one, two, three, and four step flows. Most users use the three-step flow. It enables users to combine the compile, optimize, and simulate steps into a single command, reducing the complexity of the simulation process.

- Incremental Compilation: qrun supports incremental compilation, which speeds up the simulation process by only recompiling modified files.

- Intelligent Defaults: qrun provides intelligent default values for common command line options, making it easier to get started with simulation.

- Automatic Compiler Selection: qrun automatically selects the appropriate compiler based on the file extension, reducing the need for manual configuration.

- Automatic VHDL Source File Ordering: qrun automatically determines the correct order of VHDL source files for compilation and simulation.

- Customizable: You can add your own custom options to meet your verification needs.

- Parallel Compilation: qrun supports multiple vlog and vcom compiles executing at the same time, enabling multiple simulations to run in parallel. The parallel option determines the dependencies of packages and design units and orders the compiles accordingly.

Real-World Use Cases

qrun can be used in various real-world scenarios, such as:

- Regression Testing: Automate regression testing benefits from the -snapshot switch. The -snapshot switch usage is not exclusive to regression testing. It can be used to name different optimized images, enabling users to create fully optimized versions, debug versions, etc. This enables running multiple tests using the -snapshot switch.

- Complex Flows: QuestaSim Lattice Edition supports Assertions. The Siemens commercial edition of QuestaSim enables more complex flows, such as UVM, Power Aware, Coverage, and SystemC, by adding the appropriate switches to the qrun command.

How to Use qrun

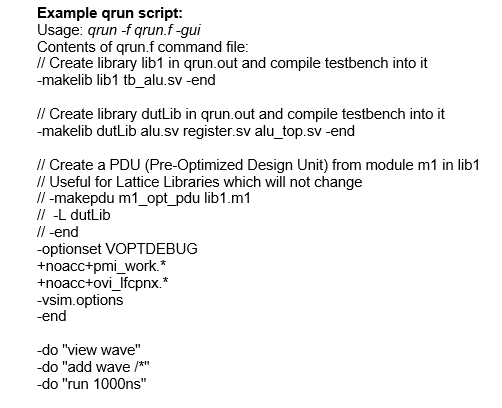

Here's an example of how to use qrun with Lattice FPGA libraries for your simulation:

- Prepare Your Design Files: Organize your design and testbench files into separate directories.

- Create a File List: Create a file list for your design and testbench files. For example, design_files.f and tb_files.f.

- Run qrun: Use the qrun command to compile, optimize, and simulate your design with Lattice FPGA libraries.

- Parallel Compilation: To parallelize the compilation process and distribute it across multiple cores, use the -parallel switch and use -jcomp <n> to indicate how many cores to use. The default number is 4. For best parallel performance -makelibs should be present and use different libraries. For even faster turnaround time, if you have multiple testbenches you can perform multiple compiles in parallel using multiple make files.

- Debugging: Switch between command line mode and GUI mode for debugging by adding the appropriate switches to the qrun command.

By following these steps, you can effectively use qrun with designs targeting Lattice FPGA devices to optimize your FPGA design simulations.

Ready to Elevate Your Lattice Design Experience

In today’s demanding verification environments, efficiency matters. qrun helps streamline simulation so designers can focus on developing high quality FPGA solutions instead of managing repetitive setup tasks. With features like incremental and parallel compilation, it slashes turn-around time, and its seamless integration makes debugging faster and more intuitive.

If you are ready to get even more out of your Lattice design flow, explore the resources available through Lattice Radiant and Lattice Diamond. You will find tutorials, documentation, training, and application notes that can help you refine your simulation practices and accelerate development.

To go deeper into advanced verification concepts, visit the Lattice Insights portal for software training courses and the Siemens Verification Academy for expert guidance and hands on learning opportunities.

To learn more about how Lattice design software and simulation tools can help you build faster, more efficient FPGA applications, reach out to our team today.