Power Management with a Control PLD

Posted 08/17/2016 by Shyam Chandra

In this 6-part series, we are looking at the challenges of implementing an efficient power management architecture in today’s complex circuit board designs.

Our first post focused on the problem of the increasing complexity in modern circuit boards. In particular, this sophistication has led to challenges in designing efficient power management systems for modern circuit boards. In this blog post, we will look at one common architecture used for the implementation of power management in circuit boards and how it addresses some of these challenges.

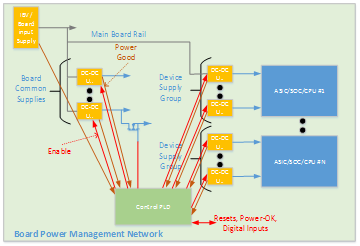

In this first model, the control PLD performs 3 out of the 4 crucial power management tasks:

- Monitoring “Power Good” - The digital "Power Good" signals of each DC-DC converter are under constant surveillance by the control PLD.

- Managing “Power-On/Power Off” – The control PLD drives the “enable” signals of the DC-DC converters to implement board “Power On/Power Off” sequence.

- Sending Control Signals – Power-related control signals (Reset, Power OK etc…) for the payload devices ensure proper operation during power up and terminate their operations during power down.

Fig.1: A Power Management system implemented using a Control PLD

Pros:

- Low cost.

- Straightforward architecture allows control PLD's sequencing logic to be easily scaled to accommodate applications of varying complexity.

- Designs can be implemented using a single design environment (typically VERILOG/ VHDL).This simplifies integrating power management coupled with control signal generation.

- Time-based and/or event-based sequencing support easily responds to individual faults.

Cons:

- Each supply requires two connections to the centrally located PLD, resulting in high control PLD I/O count and board congestion.

- Reduced reliability due to inaccurate “Power Good” fault detection signal from the DC-DC Converter (typically 8% to 20% error).

- Adding telemetry (monitoring the actual supply voltages to respond to system level voltage measurement commands) requires additional A/D converter(s).

- Requires implementation support by a board-level engineer, with expertise in power supply management.

Having all of the control done by an existing on-board control PLD helps lower the BOM, cost and simplify design. However, the cost savings can be potentially offset by the need for a control PLD with larger footprint to meet the increased need for I/Os and an additional A/D converter for some designs. But the challenges do not stop here. Layout issues associated with congestion, debug complications from poor-accuracy “Power Good” signals and the need for a specialized team are many factors that make this solutions less than ideal.

In our next blog, we will consider a hybrid architecture, where the power management design uses a dedicated power manager IC in addition to a control PLD performing housekeeping tasks to overcome some of the drawbacks of the first architecture.

Click on the links to learn more about our power manager products and development kits and boards.