# Reveal User Guide for Radiant Software

### Copyright

Copyright © 2025 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. QuestaSim is a trademark or registered trademark of Siemens Industry Software Inc. or its subsidiaries in the United States or other countries. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

# **Type Conventions Used in This Document**

| Convention        | Meaning or Use                                                                                    |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| Bold              | Items in the user interface that you select or click. Text that you type into the user interface. |  |  |  |

| <italic></italic> | Variables in commands, code syntax, and path names.                                               |  |  |  |

| Ctrl+L            | Press the two keys at the same time.                                                              |  |  |  |

| Courier           | Code examples. Messages, reports, and prompts from the software.                                  |  |  |  |

|                   | Omitted material in a line of code.                                                               |  |  |  |

|                   | Omitted lines in code and report examples.                                                        |  |  |  |

| [ ]               | Optional items in syntax descriptions. In bus specifications, the brackets are required.          |  |  |  |

| ( )               | Grouped items in syntax descriptions.                                                             |  |  |  |

| { }               | Repeatable items in syntax descriptions.                                                          |  |  |  |

| 1                 | A choice between items in syntax descriptions.                                                    |  |  |  |

|                   |                                                                                                   |  |  |  |

# **Contents**

| Chapter 1 | Introduction 7                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | Reveal Inserter 9 Using JTAG Debugger 9 Debug Flows 10 Input and Output Files 16 Limitations 17                                                                                                                                                                                                                                                                                      |

|           | Getting Started 19 Starting Reveal Inserter 19 Creating a New Reveal Inserter Project 20 Opening an Existing Reveal Inserter Project 22 Using the Reveal Controller Simulation Model 22                                                                                                                                                                                              |

|           | Managing the Cores in a Project 23 Renaming a Core 24 Removing a Core 24                                                                                                                                                                                                                                                                                                             |

|           | Viewing Signals in the Design Tree Pane 24                                                                                                                                                                                                                                                                                                                                           |

|           | Searching for Signals 25                                                                                                                                                                                                                                                                                                                                                             |

|           | Setting Up the Trace Signals 26 Selecting the Debug Logic Core 26 Selecting the Trace Signals 26 Viewing Trace Signals and Buses 27 Grouping Trace Signals into a Bus 28 Ungrouping Trace Signals in a Bus 28 Removing Signals and Buses from the Trace Data Pane 28 Renaming a Bus 28 Setting Required Sample Parameters 29 Power-on Reset (POR) Debug 30 Setting Sample Options 30 |

|           | Setting Up the Trigger Signals 32 Triggering 32 Adding Trigger Units 41 Renaming Trigger Units 41                                                                                                                                                                                                                                                                                    |

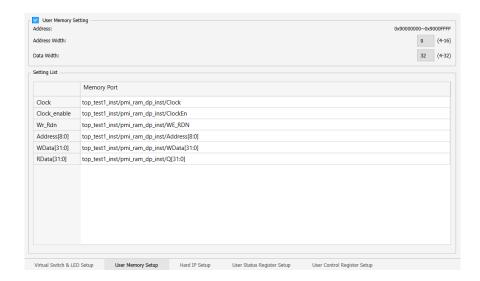

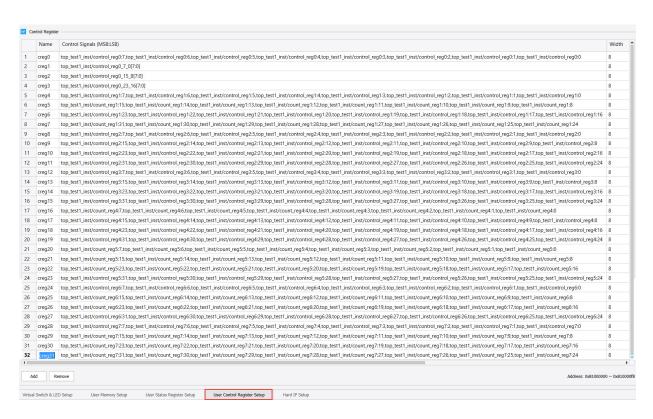

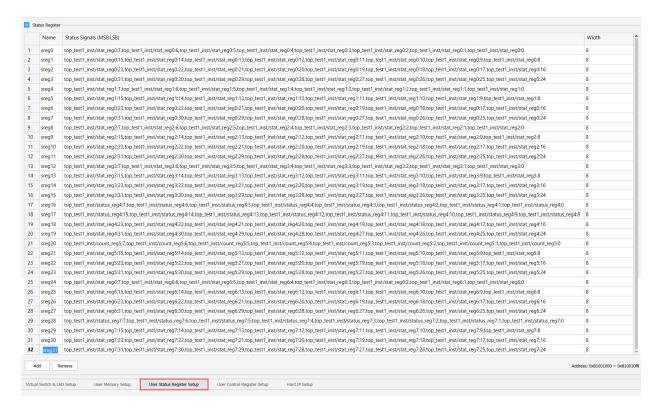

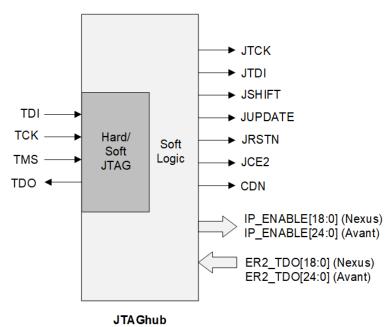

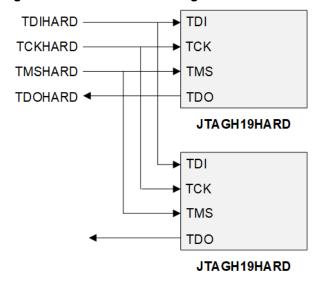

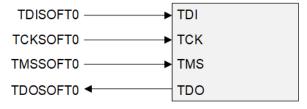

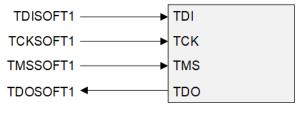

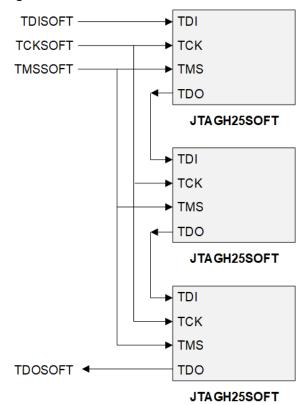

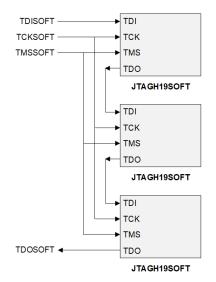

|           | Removing Trigger Units 44 Adding Trigger Expressions 44 Renaming Trigger Expressions 45 Setting Up Trigger Expressions 45 Removing Trigger Expressions 47 Setting Up Virtual Switch/LED Settings 48 Configuring User Memory Setup 48 Configuring User Control Register Setup 50 Configuring User Status Register Setup 52 Configuring Hard IP Setup 53 Checking the Debug Logic Settings 53 Saving a Project 55 Inserting the Debug Logic Cores 55 Removing Debug Logic from the Design 56 Closing a Project 56 Exiting Reveal Inserter 56 Performing Logic Analysis with Reveal Analyzer 57 Using JTAGhub 57 JTAGhub Input and Output Ports 61 JTAGhub Cosystem 63 JTAGhub Usage and Design Examples 64 JTAGhub Addressing Scheme 65 JTAGhub CORES 65 Setting Parameters and Connectivity 66 JTAG BYPASS Instruction in SOFTJTAG Chain 67 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Using JTAGMON 69  JTAGMON Input and Output Ports 69  JTAGMON Design Flow 70  User Interface Descriptions 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 3 | Reveal Analyzer 73  About Reveal Analyzer 74 Reveal On-Chip Debug Design Flow 74 Inputs 75 Outputs 75 Inserting the Debug Logic 76  Mapping, Placing, and Routing the Design 76 Generating a Bitstream File 76 Connecting to the Evaluation Board 77 Downloading a Design onto the Device 77  Starting Reveal Analyzer 78 Starting with a New File 79 Starting with an Existing File 80 Changing the Cable Connection 81  Selecting a Reveal Analyzer Core 81  Setting Up the Trace Signals 82 Setting the Trace Bus Radix 82 Adding Time Stamps to Trace Samples 82                                                                                                                                                                                                                                                                       |

Setting Up the Trigger Signals 83 Renaming Trigger Units 83 Setting Up Trigger Units 83 Renaming Trigger Expressions 85 Setting Up Trigger Expressions 85 Setting Trigger Options 86 Creating Token Sets 87 Debugging with Reveal Controller 88 Performing Logic Analysis 104 Data Capture with Sample Enable 105 Common Error Conditions 105 Stopping a Logic Analysis 105 Using Manual Triggering 106 Viewing Waveforms 106 Viewing Logic Analysis 106 Adjusting the Waveform Display 107 Panning 107 Zooming In and Out 107 Specifying the Clock Period 109 Placing, Moving, and Locating Cursors 110 Counting Samples 111 Exporting Waveform Data 111 Saving a Project 112 Exiting Reveal Analyzer 112 User Interface Descriptions 113 LA Trigger Tab 113 LA Waveform Tab 118 Viewing and Saving Waveforms 119 Using the Memory Controller Debug 120 **Best Practices** General Guidelines 125 Best Practices for Post-Synthesis Flow 126 Guidelines when Updating User Design in Post-Synthesis Debug Flow **126** Guidelines when Changing the Synthesis Tool 127 127

Revision History 128

Chapter 4

### Introduction

The Radiant software contains the Reveal Inserter and the Reveal Analyzer tools used for design debugging. This guide describes Reveal Inserter and Reveal Analyzer.

One of the most common activities in debugging is logic analysis. To do this, use Reveal Inserter and Reveal Analyzer. You can use both with all supported FPGA devices.

Reveal continuously monitors signals within the FPGA for specific conditions, which can range from simple to quite complex. When the trigger condition occurs, Reveal can save signal values preceding, during, and following the event for analysis, including a waveform presentation. The data can be saved to a value change dump file (.vcd), which can be used with tools such as QuestaSim, or to an ASCII tabular format that can be used with tools such as Excel.

Before running Reveal Analyzer, use Reveal Inserter to add Reveal modules to your design. In these modules, specify the signals to monitor, define the trigger conditions, and other options. Reveal supports multiple logic analyzer cores using hard/soft JTAG interface. You can have up to 15 modules, typically one for each clock region of interest. When the modules are set up, regenerate the bitstream data file to program the FPGA.

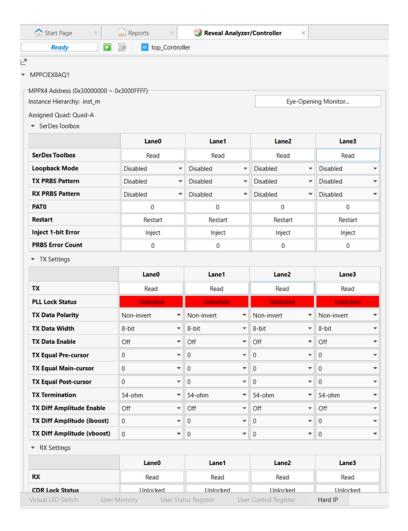

A feature is enabling an added module called Reveal Controller. This controller module enables:

- Access to the control and status registers of the hard IPs such as I2CFIFO, PLL, PCIe, CDR, and DPHY via the LMMI (Lattice Memory Mapped Interface) slave interface

- Virtual switches and LEDs emulating on-board switches and LEDs to control and monitor a user design. Up to 32 switches and 32 LEDs are supported.

Read/write access to a bank of user registers and/or initialize memory post-configuration.

The main purpose is narrowing down to problem areas during debug cycles using a divide and conquer method into many small functional blocks to control and monitor the status of each block.

Before starting a test run, set up Reveal Analyzer. This includes setting a number of options, including modifying trigger conditions and customizing the waveform display. You can save these settings for later use. During and after a test run, view the incoming data in Reveal's LA Waveform view. You can also save the data to a .vcd or .txt file to analyze with other tools.

#### Note:

Reveal supports IEEE-P1735 encryption. If this encryption is applied to a design, the design tree will allow only the visible ports and signals that are not encrypted to be inserted by the Reveal Inserter for triggering purposes.

## **Reveal Inserter**

Reveal Inserter enables you to select which design signals to use for debug tracing or triggering, then generate a core on the basis of these signals and their use. After generating the required core, it generates a modified design with the necessary debug connections and links it to the signals. Reveal Inserter supports VHDL, Verilog, System Verilog and mixed-HDL flows for debug insertion. Once the design has been modified for debug, it is mapped, placed, and routed with the normal design flow in the Radiant software.

### Using JTAG Debugger

JTAG can be used to access debug logic to test and analyze your design. Devices in Radiant support hard and soft JTAG cores. Hard JTAG is basically a JTAG block IP that is part of the device. Soft JTAG is built in RTL, which uses the device fabric logic.

In the iCE40 device, Reveal JTAG support is implemented using logic for JTAG state machine and GPIO pins for four JTAG pins (JTAG\_TCK, JTAG\_TDI, JTAG\_TMS, and JTAG\_TDO).

Consider the following recommendations:

Lock the JTAG\_TCK pin to PCLK or GR\_PCLK to avoid using general routing, as clock general routing may violate the CLK 1-PLC rule. For an example of the ldc\_set\_location constraint:

```

ldc_set_location {JTAG_TCK} -site J2

```

- ▶ Lock pins JTAG\_TCK, JTAG\_TDI, JTAG\_TMS, and JTAG\_TDO on the same bank. Make other banks available for DDR, MIPI or LVDS usage.

- Set the frequency constraint as follows:

```

create_clock -name {JTAG_TCK} -period 166.67

```

Likewise, in CrossLink device, there is no hard JTAG block and Reveal uses soft JTAG debug logic and GPIO pins for the four JTAG pins.

Refer to "Using JTAGhub" on page 57 for information about the use and merging of JTAGhubs in Nexus and Avant devices.

### **Debug Flows**

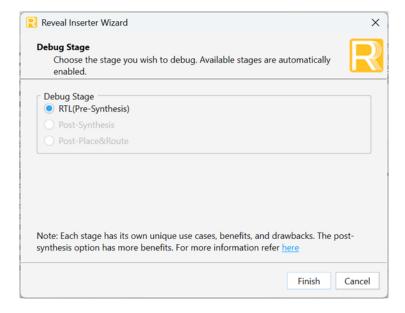

Reveal Inserter features two debug flows. When you open Reveal Inserter, the Reveal Inserter Wizard prompts you to choose the debug flow to use.

- RTL (Pre-Synthesis) This is the standard flow for debugging a design all at once. The user inserts the logic core before the design is synthesized the first time. Refer to "RTL (Pre-Synthesis) Debug Flow" on page 11 for details.

- Post-Synthesis This flow allows you to insert debug logic after running synthesis. As such, this option is available if you have already run synthesis. It is useful for isolating or monitoring certain signals and focus your changes or improvements in specific areas of the design. Refer to "Post-Synthesis Debug Flow" on page 11 for details.

- Post-Place & Route This flow allows you to insert debug logic after running place and route. As such, this option is available if you have already completed synthesis, mapping, and placement and routing. Also referred to as non-intrusive debugging, you can add your debug core after place and route without having to alter your original design. The postplace & route debug flow is available when designing for Avant and Nexus devices. Refer to "Post-Place & Route Debug Flow" on page 15 for details.

Figure 1: Reveal Inserter Wizard

### RTL (Pre-Synthesis) Debug Flow

The following are the general steps in the Reveal Inserter RTL design flow.

- 1. Start Reveal Inserter.

- 2. In the Reveal Inserter Wizard, select RTL (Pre-Synthesis) as debug stage and click Finish.

- Create a new Reveal Inserter project or open an existing Reveal Inserter project.

- 4. Add and set up analyzer and controller modules.

- 5. Insert the debug logic.

This process generates and synthesizes the necessary debug logic.

The generated .rvl is automatically imported into the Radiant software if you enabled the "Activate Reveal file in design project" option in the Insert Debug to Design dialog box.

- 6. Map, place, and route the design.

- 7. Generate the .bin bitstream file.

If you want to perform logic analysis with Reveal Analyzer, continue with these steps:

- 8. Set up the cable connection with Programmer.

- 9. Download the design onto the device.

- 10. Start Reveal Analyzer and perform logic analysis with it.

### **Post-Synthesis Debug Flow**

In post-synthesis debugging, it is required that you mark the specific signal objects that you want to monitor by adding the syn\_rvl\_debug synthesis attribute in the RTL source files. This allows you to keep track of these signals more easily as they are highlighted on the user interface. The syn\_rvl\_debug attribute is the same for both Synplify and LSE tools.

The syn rvl debug attribute performs two functions:

- ► This attribute highlights the signal so it can be easily identified in the user interface.

- After synthesis, this attribute tells the synthesis tool to preserve the signal without optimizing it. If it is a bus, the data width is also preserved. The synthesis tool passes the same attribute to the signal in the post-synthesis netlist (\*.vm).

The syntax in Verilog/System-Verilog is:

```

/* synthesis syn rvl debug = 1 */;

```

#### The syntax in VHDL is:

```

attribute syn_rvl_debug : boolean;

attribute syn_rvl_debug of sig1 : signal is true

```

#### For example:

```

input clki /*synthesis syn_rvl_debug = 1 */,

wire clk1 /* synthesis syn_rvl_debug = 1 */;

reg [39:0] cnt /* synthesis syn_rvl_debug = 1 */;

reg [31:0] cnti /* synthesis syn_rvl_debug = 1 */;

```

The synthesis tool may add a suffix to the name of a signal with the syn\_rvl\_debug attribute. This change is minimal and the signal remains recognizable to the user.

The syn\_rvl\_debug attribute may be attached to top level input/output ports, which will be connected to the input/output buffers. In case of an input port with the syn\_rvl\_debug attribute, in the .vm file, the output of the input buffer should get the passed attribute. In case of an output port with attribute, in the .vm file, the input of the output buffer should get the passed attribute.

#### Example 1

#### RTL Code:

```

input clki /* synthesis syn_rvl_debug = 1 */,

```

#### The expected output is:

```

wire clki_c /* synthesis syn_rvl_debug = 1 */;

```

where clki is driving the input port of IB and clki\_c is connected to the output port. This is similar in the output port:

```

output dout /* synthesis syn rvl debug = 1 */,

```

#### The expected output is:

```

wire dout c /* synthesis syn rvl debug = 1 */

```

#### Example 2

#### RTL Code:

```

reg [31:0] counter /*synthesis syn_rvl_debug = 1*/;

```

This is the expected .vm code when the exact signal name is preserved:

```

wire [31:0] counter /*synthesis syn_rvl_debug = 1*/;

```

When the exact signal name cannot be preserved, some suffix(\*) may be added.

```

wire [31:0] counter_* /*synthesis syn_rvl_debug = 1*/;

```

#### Example 3

If the attribute is provided in the following way, it is applied to the last signal:

#### RTL Code:

```

reg sig1, sig2, sig3 /*synthesis syn_rvl_debug = 1*/;

```

#### The expected .vm code is:

```

wire sig3 /*synthesis syn_rvl_debug = 1*/;

```

The synthesis tool may also expand/elaborate the RTL code if the attribute is attached to the states in the FSM. This depends on the type of encoding such as binary, one-hot and others.

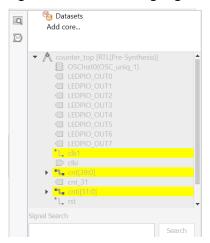

Here is an example of highlighted signals attached with the syn\_rvl\_debug attribute.

Figure 2: Marked Debug Signals

#### Note:

Before you start post-synthesis debugging, make sure that there is no active .rvl project in your design. If there is, make it inactive. To change a file's status to inactive, right-click the file in the File List view and choose Set as Inactive.

The following are the general steps in the Reveal Inserter Post-Synthesis debug flow.

- 1. After running synthesis, start Reveal Inserter.

- 2. In the Reveal Inserter Wizard, select Post-Synthesis as debug stage and click Finish.

In the list of signals displayed in Reveal Inserter, the signals with the syn\_rvl\_debug attributes are highlighted for easy tracking.

3. Add and set up analyzer and controller modules, if needed.

#### **Note**

When Reveal Controller is used for switches in post-synthesis, make sure the signals are not driven by other signals in the design. Multiple driver issues produce an error in Place & Route.

- 4. Click the **Design Rule Check** button and fix errors, if needed.

- 5. Click the **Insert Debug** button.

- 6. In the Insert Debug to Design dialog box, select the modules to insert. Select Activate Reveal file in design project to include it in synthesis. This also sets other .rvl files as inactive.

- 7. Click **OK**. The .rvl file is listed in the File List pane under Debug Files.

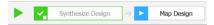

You will note that the Synthesize Design process bar now has a small white box to indicate that only Reveal is to be synthesized in postsynthesis stage.

- 8. Run **Synthesize Design**. Only the changes in Reveal are processed. In the Task Detail View, you will observe the added Post-Synthesis Reveal task in progress.

- 9. Map, place, and route the design.

- 10. Generate the bitstream file.

If you want to perform logic analysis with Reveal Analyzer, continue with these steps:

- 11. Set up the cable connection with Programmer.

- 12. Download the design onto the device.

- 13. Start Reveal Analyzer and perform logic analysis with it.

### Post-Place & Route Debug Flow

Similar to the post-synthesis debug flow, in post-place & route debugging, it is required that you mark the specific signal objects that you want to monitor by adding the syn\_rvl\_debug synthesis attribute in the RTL source files. The syntax for Verilog and VHDL are the same. See "Post-Synthesis Debug Flow" on page 11.

The following are the general steps in the Reveal Inserter Post-Place & Route debug flow.

#### Note

When you initially run synthesis, map, and place & route, make sure there is no active Reveal (.rvl) project. If there is an active .rvl project, make it inactive by right-clicking the .rvl file In the File List view and choosing Set as Inactive.

- 1. After running synthesis, map, and place & route, start Reveal Inserter.

- 2. In the Reveal Inserter Wizard, select **Post-Place & Route** as debug stage and click **Finish**.

#### **Note**

In the Tcl Console, you will see that a new Reveal project is created in the post-PAR stage. The placed and routed design is preserved in the PAR output udb.

```

> rvl new project -stage postpar

```

In the design tree, the entire database after place and route is shown. The signals with the syn\_rvl\_debug attributes are highlighted.

3. Add and set up logic analyzer cores

#### Note

Adding Reveal Controller cores is not supported in post-Place & Route debug flow.

- Click the **Design Rule Check** button and fix errors, if needed.

- 5. Click the **Insert Debug** button.

- In the Insert Debug to Design dialog box, select the modules to insert.

Select Activate Reveal file in design project to include it in synthesis.

This also sets other .rvl files, if any, as inactive.

Click OK.

In the Save Reveal Project dialog box, type the file name of the .rvl file and click Save. The .rvl file is listed in the File List view under Debug Files.

You will note that the Place & Route process bar now has a small white box to indicate that only Reveal is to be processed in post-place and route stage.

- 8. In the Task Detail View, you will observe that the following sub-tasks are unchecked. These will be run when you click the Place & Route button.

- Place & Route Reveal

- Place & Route Timing Analysis

- 9. Run Place & Route. Only the changes in Reveal are processed.

- 10. Generate the bitstream file.

If you want to perform logic analysis with Reveal Analyzer, continue with these steps:

- 11. Set up the cable connection with Programmer.

- 12. Download the design onto the device.

- 13. Start Reveal Analyzer and perform logic analysis with it.

## Input and Output Files

The inputs to the Reveal Inserter flow are the following:

VHDL, Verilog, and System Verilog files

Reveal Inserter generates the following files in the debug flow:

- ▶ Reveal Inserter project (.rvl) file, which contains the signal connections for each core and some settings for the debugging logic, such as maximum sequence depth and maximum event counter. The information in this file is statically set in Reveal Inserter and cannot be changed in Reveal Analyzer.

- Reveal Inserter settings (.rvs) file, which contains settings that can be dynamically changed without regenerating the debug logic. This information includes trigger units, comparison types, values, and trigger expressions. The information in this file is dynamically set in either Reveal Analyzer or in both Reveal Analyzer and Reveal Inserter.

- Reveal Inserter parameter (.rvp) file, which contains information needed for debug logic generation, is produced during the design implementation process.

### Limitations

Reveal Inserter has the following limitations in the current release.

### Unsupported VHDL, Verilog and System Verilog Features in Reveal Inserter

The following features that are valid in the VHDL, Verilog and System Verilog languages are not supported in Reveal Inserter when you use the RTL flow:

- Array types of two dimensions or more are not shown in the port or node section.

- Undeclared wires attached to instantiated component instances are not shown in the hierarchical design tree. You must declare these wires explicitly if you want to trace or trigger with them.

- Variables used in conditional statements like if-then-else statements are not available for tracing and triggering.

- Variables used in selection statements like the case statement are not available for tracing and triggering.

- If function calls are used in the array declaration, the actual size of the array is unknown to Reveal Inserter.

- Entity and architecture of the same design cannot be in different files.

- In Verilog, you must explicitly declare variables at the very beginning of a module body to avoid obtaining different results from various synthesis tools.

- In VHDL, you must declare synthesis attributes within an entity, not within an architecture, to avoid obtaining different results from various synthesis tools.

- Signals used in VHDL "generate" statements are not available for tracing and triggering.

- Signals that are VHDL user-defined enumerated types, integer type, or Boolean type are not available for tracing and triggering.

- Some signals in a System Verilog design appear in the signal hierarchy but are not available for triggering or tracing. These signals include:

- Array types of two dimensions or more are not shown in the port or node section

- Signals that are user defined enumerated types, integer type, byte/ shortint/int/longint type

- Signals that belong to typedef and interface

### Syn keep and Preserve signal Attributes

In VHDL, always define the syn keep and preserve signal attributes as Boolean types when you declare them in your design. Synplify defines them as Boolean types, and Reveal Inserter will issue an error message if you define them as strings.

### Signals Implemented as Hard Routes

Signals that are implemented as hard routes in the FPGA instead of using the routing fabric are not available for tracing or triggering. Examples are connections to IB and OB components. Many common hard routes are automatically shown as unavailable in Reveal Inserter, but some are not. If you select a signal for tracing or triggering that is implemented as a hard route, an error will occur during the synthesis, mapping, placement, or routing steps.

### **Dangling or Unconnected Nets**

Dangling or unconnected nets in Verilog, System Verilog, or VHDL code are available for use with Reveal Inserter.

### **Synthesis Parameters**

VHDL generics for synthesis must be added via HDL Parameters field in Project Properties. The current version does not support parameters via Command Line Options field in Synthesis Strategy setting.

# **Getting Started**

After you create a project in the Radiant software, you can start Reveal Inserter and create a Reveal project. Or open an existing Reveal project for modification.

## **Starting Reveal Inserter**

Reveal Inserter is started from the main window. Open the desired design project to have access to the tools.

#### To start Reveal Inserter:

- Do one of the following:

- In the main window, choose Tools > Reveal Inserter.

- In the toolbar, click the Reveal Inserter button.

Choose the debug flow in the Reveal Inserter Wizard and click Finish.

When Reveal Inserter opens, it shows the active Reveal project or, if there are no existing projects, Reveal Inserter creates one.

When Reveal Inserter opens a design, it must parse and statically elaborate it. In some cases, code successfully synthesized with some synthesis tools may be flagged as having an error when Reveal Inserter tries to open the design. In these cases, Reveal Inserter is interpreting the HDL code more strictly than the chosen synthesis tool. It is likely that the code would not synthesize with a different synthesis tool or would have other compliance issues.

To correct this problem, see the reveal\_error.log file in the project directory. This file contains information and error messages that enable you to see any problems found in the design.

## **Creating a New Reveal Inserter Project**

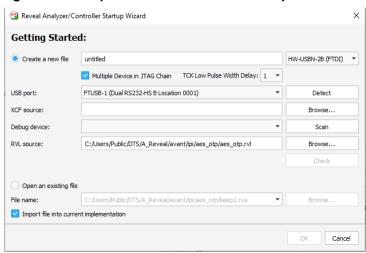

Before you can start Reveal Analyzer with a new .rva file, you need to be connected to your evaluation board with a download cable and have the board's power turned on.The following steps can also be seen in Figure 3

#### To start Reveal Analyzer with a new file:

- 1. Issue the start command. To start:

- ► For stand-alone in Windows, go to the Windows Start menu and choose Programs > Lattice Radiant Reveal > Reveal Logic Analyzer.

- For stand-alone in Linux, go to a command line and enter the following:

- <Reveal install path>/bin/lin64/revealrva

The Reveal Analyzer Startup Wizard dialog box appears.

- 2. If Reveal Analyzer opens with an existing file, choose **File > Save As**.

- The Save Reveal Analyzer File dialog box opens. Change the file name and click **Save**. You now have a new .rva file ready to work with.

- 3. In the Reveal Analyzer Startup Wizard dialog box, Select **Create a new file** (at the upper-left of the dialog box).

The dialog box presents a few rows of boxes that need to be filled in. In the figure below, the numbers match up with the steps in this procedure and show where the boxes, buttons, and menus are for each step.

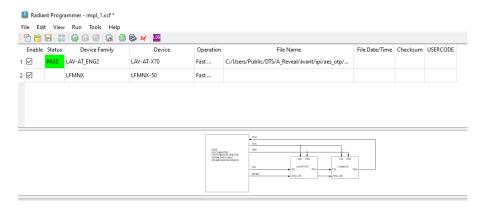

Figure 3: Startup Wizard with Steps for a New File

4. In the first second row, type in the base name of the file. The extension is added automatically.

- If there are daisy-chained devices, select Multiple Device in JTAG Chain.

- 6. To the right of this row is a pulldown menu. Choose the type of cable that your board is connected to.

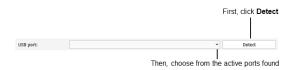

- 7. Select the port. The method depends on the cable type:

- ▶ If USB, click **Detect**. Then choose from the active ports found. The following figure shows the row after choosing a USB type.

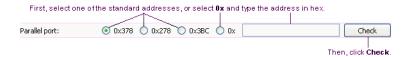

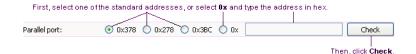

If parallel, select the port address. If it's not one of the standard addresses given, select **0x** and type in the hexadecimal address. Then click **Check** to verify that the connection is working. The following figure shows the row after choosing a parallel type.

- 8. If there are daisy-chained devices, click **Browse** in the XCF source row to find the XCF source file.

- 9. Click Scan to find the FPGA.

- 10. If there is more than one FPGA on your board, go to the "Debug device" menu and choose one that has a Reveal icon. The icon indicates the presence of a Reveal module.

- 11. Click **Browse** in the RVL source row to find the Reveal Inserter project (.rvl) file.

- 12. To add the new .rva file to the File List view, select **Import file into current implementation**. The .rva file works the same either way.

- 13. Click **OK**.

# Opening an Existing Reveal Inserter Project

If you want to start with an existing file, you just need to have that .rva file in the design project. You need to be connected to the evaluation board only if you want to run a test and capture data.

#### To start Reveal Analyzer with an existing file:

- 1. Issue the start command. To start:

- ► The stand-alone Reveal Analyzer in Windows, go to the Windows Start menu and choose Programs > Lattice Radiant Reveal > ™ Reveal Logic Analyzer.

- The stand-alone Reveal Analyzer in Linux, enter the following on a command line:

- <Reveal install path>/bin/lin64/revealrva

The Reveal Analyzer Startup Wizard dialog box appears.

If Reveal Analyzer opens with the .rva file you want to use, you're ready to go. Otherwise continue with the following steps.

- 2. Select Open an existing file (in the lower part of the dialog box).

- 3. In the "File name" box, choose one of the available .rva files.

- If the file you want is not in the menu, click **Browse** and browse to the desired .rva file.

- 5. Click OK.

# Using the Reveal Controller Simulation Model

The Reveal Controller Simulation Model replicates the functionality of Reveal Controller in simulation.

#### To set up the Reveal Controller Simulation Model:

- Choose Tools > Reveal Inserter to insert a reveal module into the design.

- 2. Run **Synthesize Design** to generate the reveal\_workspace file.

- ▶ If you insert Reveal Controller only, the tool will create the sim\_src folder with the pre-synthesis Reveal generated source file under reveal\_workspace.

- If you insert Reveal Controller and Analyzer, the Reveal engine will not create the folder and no source files will be provided.

- Click Tools > Simulation Wizard or click the icon in the toolbar.

- 4. In the Simulator Project Name and Stage dialog box, enter the project name.

#### Click Next.

5. In the Add and Reorder Source dialog box, select and add the source files from the sim\_src folder.

#### Click Next.

The following compiler directives are all enabled in the source file. You can use the OEM simulator or any stand-alone simulator to compile and simulate the Controller:

- `define en\_sw

- `define en\_led

- `define en\_user\_mem

- `define en\_user\_creg

- `define en\_user\_sreg

## Managing the Cores in a Project

Each Reveal Inserter project can include multiple debug logic cores and one Reveal controller core. The core has its own settings for the debug logic, such as trace signals, trigger signals, sample clock, sample enable, and trigger output signal. These settings are called a dataset. In many cases, a single core is all that is required to debug a design.

When you open a new project, Reveal Inserter automatically adds the first debug logic core to the first dataset and gives it a name of <top\_module>\_LA<number>, where top\_module is the name of the top module in the Reveal Inserter project, and number is a sequential number. The core name is case insensitive—for example, "core\_LA0" is the same as "core\_la0."

All Reveal cores are listed in the Dataset pane in the Reveal Inserter window.

#### Note:

For the Avant device, you need to add the PAR Strategy command line option "-exp WARNING\_ON\_PCLKPLC1=1" when using Reveal and JTAGH25 to avoid errors related to the jtck N clock.

## Renaming a Core

You can rename a debug logic core if you want to change its initial name.

#### To rename a core or cores in a project:

- Highlight the name of the core in the Dataset pane, and choose **Debug > Rename Core**, or right-click on the name of the core and choose **Rename Core** from the pop-up menu.

- 2. Type the new name of the module over the old name.

During the renaming process, Reveal Inserter verifies that:

- The core name begins with a letter and consists of letters, numbers, and underscores (\_).

- ▶ The core name is not the same as that of any other core.

- The core name is not the same as that of any module or instance in the design.

### Removing a Core

You can also remove a debug logic core.

#### To remove a core or cores from a project:

Select the core in the Dataset pane, and choose **Debug > Remove Core**, or right-click on the name of the core and choose **Remove Core** from the pop-up menu.

# Viewing Signals in the Design Tree Pane

In the Design Tree pane of the Reveal Inserter window, you can display the hierarchy of the whole design, including the ports and nodes in the top module and submodules, so that you can choose the signals to use for data tracing and triggering.

From the Design Tree pane, you can drag a signal to the upper half of the Trace Signal Setup tab to set it as a trace signal or drag it to the lower half of the tab to set it as a sample clock signal or a sample enable signal.

In the Design Tree pane, the names of trace, trigger, and control signals are in bold font if they are currently being used.

#### To view all signals in the design tree:

Right-click on the design name in the Design Tree pane and choose Expand All from the pop-up menu.

# To view the buses, ports, top-level signals, and top level of the hierarchy:

Right-click on the design name in the Design Tree pane and choose Collapse All from the pop-up menu.

You can also view signals and buses in the Trace Data pane of the Trace Signal Setup tab.

### **Searching for Signals**

You can search for a signal or signals and set the selected signals as trace signals, trigger unit signals, sample clock signals, or sample enable signals. You can search for signal names or patterns of characters.

#### To search for a signal:

- 1. In the Signal Search box in the Design Tree pane, enter the name of the signal or pattern to find. You can set a filter by using the case-insensitive alphanumeric characters and wildcards shown in the following table.

- 2. Click Search.

If Reveal Inserter finds only one signal, it highlights it in the Design Tree pane.

If Reveal Inserter finds multiple signals, it opens the Search Result dialog box to list all the signals found.

- 3. If you are searching for multiple signals, select the desired signals in the Search Result dialog box, and click **OK**.

- Shift-click to select contiguous signals.

- Control-click to select non-contiguous signals.

The selected signals are now highlighted in the Design Tree pane.

From the Design Tree pane, you can drag signals to the Trace Data pane, the Sample Clock box, and the Sample Enable box in the Trace Signal Setup tab. You can also drag signals to the Signals (MSB:LSB) box in the Trigger Unit section of the Trigger Signal Setup tab.

Although the buses are displayed as "busname[n:m]" in the Design Tree pane, Reveal Inserter ignores the string after the bus name when it searches for buses. For example, if the design contains a bus called a[0:2], you can search for it by a pattern such as "a" or "a\*," but you cannot use a pattern such as "a[\*."

If a bus is named xyz, a search for xyz highlights the entire bus. A search for xyz\* brings up the Search Result dialog box and all the individual signals in the xyz bus.

The following wildcards are supported in searches:

| Wildcard<br>Character | Characters to Replace                                      | Example                                                                            |  |

|-----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| ?                     | Any single character                                       | ?a?                                                                                |  |

|                       |                                                            | where "a" is the middle character in a three-character string                      |  |

| *                     | Any sequence of                                            | *a*                                                                                |  |

|                       | characters                                                 | where the string contains the "a" character                                        |  |

| [abc]                 | "a," "b," or "c"                                           | [abc]*                                                                             |  |

|                       |                                                            | where the string begins with "a," "b," or "c"                                      |  |

| [^abc]                | Any character except "a," "b," or "c"                      | [^abc]*                                                                            |  |

|                       |                                                            | where the string does not begin with "a," "b," or "c"                              |  |

| [a-d]                 | Any character in the range of "a" through "d"              | [a-d]*                                                                             |  |

|                       |                                                            | where the string begins with any character in the range of "a" through "d"         |  |

| [^a-d]                | Any character except those in the range of "a" through "d" | [a-d]*                                                                             |  |

|                       |                                                            | where the string does not begin with any character in the range of "a" through "d" |  |

|                       |                                                            |                                                                                    |  |

# **Setting Up the Trace Signals**

The first step in performing a logic analysis is to specify how the data from the trace bus will be captured. Use the Trace Signal Setup tab in the Reveal Inserter window to choose the signals from which to collect sample data in the selected core.

# **Selecting the Debug Logic Core**

Before you configure the trace signals, select the debug logic core to configure in the Dataset pane. This is either the regular debug logic core or the controller core.

# **Selecting the Trace Signals**

You can use either of two methods to select trace signals: dragging and dropping or using a search engine to find them. You can select up to 512 trace signals in each core.

#### To select trace signals by dragging and dropping:

Select the desired signals in the Design Tree pane and drag them to the Trace Data pane in the Trace Signal Setup tab.

#### To select trace signals by using a search engine:

- In the Signal Search box in the Design Tree pane, enter the name or pattern of the signal to find. You can set a filter by using case-insensitive alphanumeric characters and wildcards. See "Searching for Signals" on page 25 for information about the wildcards that you can use.

- 2. Click Search.

If Reveal Inserter finds only one signal, it highlights it in the Design Tree pane.

- If Reveal Inserter finds multiple signals, it opens the Search Result dialog box to list all the signals found.

- 3. If you are searching for multiple signals, select the desired signals in the Search Result dialog box, and click **OK**.

- The signals are now selected in the Design Tree pane.

- 4. Drag them to Trace Data pane in the Trace Signal Setup tab.

# **Viewing Trace Signals and Buses**

In the Trace Data pane in the Trace Signal Setup tab, you can display the signals in buses or remove them from view.

#### To display all the signals in all the buses:

Right-click in the Trace Data pane, and choose Expand All from the popup menu.

#### To hide all the signals in all the buses:

Right-click in the Trace Data pane, and choose Collapse All from the pop-up menu.

#### To display all the signals in an individual bus:

Right-click on the bus and choose Expand from the pop-up menu.

#### To hide all the signals in an individual bus:

Right-click on the bus and choose **Collapse** from the pop-up menu.

## **Grouping Trace Signals into a Bus**

You can group trace signals, buses, or both into a bus.

#### To group signals or buses into a bus or to add signals or buses to a bus:

- 1. In the Trace Data pane of the Trace Signal Setup tab, select the signals, buses, or both to be grouped.

- 2. Choose **Debug > Group Trace Data**.

- 3. Double-click the new bus and type in the desired name.

# **Ungrouping Trace Signals in a Bus**

You can ungroup the signals or buses in a bus.

#### To ungroup the signals, buses, or both in a bus:

- 1. In the Trace Data pane in the Trace Signal Setup tab, select the signals, buses, or both to be ungrouped from the bus.

- Choose Debug > UnGroup Trace Bus.

# Removing Signals and Buses from the Trace Data Pane

You can remove signals from the Trace Data pane in the Trace Signal Setup tab.

#### To remove a signal or a bus from the Trace Data pane:

- 1. In the Trace Signal Setup tab, select the signals to be removed from the Trace Data pane.

- 2. Choose **Debug > Remove Trace Data**, or right-click and choose **Remove** from the pop-up menu. You can also press the Delete key.

## Renaming a Bus

You can rename a bus.

#### To rename a bus:

- 1. In the Trace Data pane of the Trace Signal Setup tab, select the bus.

- 2. Choose **Debug > Rename Trace Bus**, or right-click and choose **Rename** from the pop-up menu.

- 3. Type the new name of the module over the old name.

# **Setting Required Sample Parameters**

For each core, you must set the certain sample parameters for the trace signals.

#### To set the required sample parameters:

In the Sample Clock box in the Trace Signal Setup tab, type the name of the clock signal or drag the clock signal from the design tree shown in the Design Tree pane.

#### **Note**

On the board, make sure that the minimum sample clock frequency is at least that of the JTAG clock. If the sample clock speed is too slow, you will be unable to complete logic analysis with Reveal Analyzer.

The sample clock frequency should be no more than 200 MHz.

2. In the **Buffer Depth** box, specify the size of the trace memory buffer.

This parameter defines the number of trace bus samples that a core can capture. It can be set to a minimum of 16 or to powers of 2 from 16 to 65536. The buffer size is determined by the amount of embedded memory in the FPGA.

- 3. In the **Implementation** box, specify how the debug logic is to be implemented in the FPGA. You can choose one of the following:

- ► EBR Implements the debugging logic as embedded block RAM (EBR). This setting is the default.

- 4. In the **Data Capture Mode** box, select Single Trigger Capture or Multiple Trigger Capture. Single Trigger Capture is enabled by default.

- 5. If you choose Multiple Trigger Capture, you must also set the **Minimum samples per trigger** option, which specifies the minimum number of data samples to collect per trigger. The minimum is either 8 or 1/256 of the total buffer depth, whichever is greater. The maximum number of samples depends on the design.

## Power-on Reset (POR) Debug

An automatic "trigger enable" signal must be built into the Reveal module to monitor POR functions. Before Reveal Analyzer starts, these functions happen immediately after the power-on of the test board. When the trigger enables signal transitions to "active," the module will watch for the trigger and collect samples. It is similar to clicking the Run button in Reveal Analyzer. When Reveal Analyzer starts, it loads and displays any data collected by the POR modules.

POR modules are not supported in iCE40UP devices.

#### To set a POR trigger enable:

- 1. In the POR Debug section, select **Trigger Enable**.

- 2. Find the POR trigger signal in the Design Tree view and drag it to the text box in the POR Debug section.

- 3. Choose whether the signal is **Active High** or **Active Low**.

### **Setting Sample Options**

In addition to the required parameters, you can set options for the data sample.

### **Using a Sample Enable**

A sample enable is an optional signal used to capture data only when the sample enable is active, either high or low. If you do not specify a sample enable signal, trace data is collected on every sample clock after the trigger.

You may want to use a sample enable in cases where you need to capture a lot of data, but the data is only important during certain times, not whenever the sample clock is running. In these cases, the sample enable is a "gate" that allows you to turn the capturing of data on and off. An example is a design that contains many different sections, but some sections only work during certain clock phases. You typically use a master clock and generate different signals for the phases. You could use one of the phases as the sample enable.

#### To set the sample enable:

- In the **Sample Enable** checkbox, indicate whether a sample enable signal is to be used. If you want to use a sample enable:

- a. Select the checkbox to indicate that a sample enable signal will be used. The checkbox is deselected by default.

- b. Enter the name of the sample enable signal in the box beneath the checkbox, or drag the signal from the Design Tree pane.

- c. In the box to the right of the signal name box, select either **Active High**, which means that trace data is captured when the sample

enable is high and the sample clock occurs, or **Active Low**, which means that trace data is captured when the sample enable is low and the sample clock occurs. Active High is the default.

Each sample shown in the trace buffer is only captured when the sample enable is active and there is a sample clock. Data samples can be discontiguous, unlike those in a normal data capture.

Additionally, it is possible that the actual trigger condition may occur when the sample enable is not active. This causes two changes from a normal data capture:

- The actual data values for the trigger condition may not be visible, because the data cannot be captured when the sample enable is inactive.

- Reveal Analyzer cannot accurately calculate the trigger point, since the trigger point may have occurred when the sample enable is inactive. Normally a trigger point is shown as a single marker on the clock on which the trigger occurred. If a sample enable is used, a trigger region that spans 5 clock cycles is shown instead. Reveal Analyzer can guarantee that the trigger occurred in this region, but it cannot determine during which clock cycle the trigger occurred.

The sample enable is a very useful feature, but it takes more understanding than a normal data capture.

### **Adding Trigger Signals to Trace Signals**

You can add trigger signals to the trace signals so that the data from the trigger signals is included in the trace data. Tracing trigger signals increases the amount of logic used by the trace buffer.

#### To add the trigger signals to the trace signals:

Select the Include trigger signals in trace data option. This option is turned off by default.

### **Adding Time Stamps to Trace Samples**

In Reveal Inserter, you can optionally specify a sample clock count value to be stored with each trace sample to indicate the sample count clock value at which the sample was captured. This count is extra data (bits) captured into the trace buffer that increase the trace buffer's width. This time stamp enables you to see how many sample clock intervals have elapsed between data captures when you use a sample enable. It is useful in some cases when it is necessary to know if you captured the right data. A time stamp is also useful when you try to synchronize data between multiple cores, off-chip data, or both. For example, if you trigger two cores at the same time, you can use the time stamps on the trace samples to calculate how the data between the cores compares.

#### To add time stamps to the trace samples:

- 1. Select the **Timestamp** box in the Trace Signal Setup tab.

- 2. In the drop-down menu in the Bits box next to the Timestamp box, select the amount of trace memory storage needed by the time stamp, in bits.

The number of bits for the timestamp is the number of bits in the maximum count of the timestamp. But each bit is equivalent to adding another signal to be traced, so the amount of trace memory needed is therefore much larger. The minimum number of bits that appears in the drop-down menu is obtained by multiplying the value in the Buffer Depth box by 2 and converting the result to an exponential value. For example, if the value in the Buffer Depth box is 256, the minimum number of bits in the Bits drop-down menu is calculated as follows:

256 X 2 = 512

$512 = 2^9$

So the minimum number of bits available in the Bits menu in this case is 9.

The maximum number of bits available in the Bits menu is always 63.

### **Setting Up the Trigger Signals**

The Reveal software has some similarities to and some differences from external logic analyzers. An external logic analyzer typically offers up to a few dozen signals or channels and megabits worth of capture data depth. Internal or embedded logic analyzers have different constraints. An internal logic analyzer can offer thousands of signal connections, since no extra pins are required to connect to the signal. But the resources inside an FPGA force a limitation on the amount of data that can be captured, typically constrained to several thousand bits. This difference drives different requirements. An internal logic analyzer requires the ability to accurately pinpoint the desired event in order to capture a smaller amount of data around that precise event. The capabilities in the Reveal software are designed specifically for the triggering requirements of an internal logic analyzer.

# **Triggering**

With the Reveal software, it is easy to set up simple triggering conditions, as well as extremely complex triggers. Triggering in Reveal is based on the trigger unit and the trigger expression. A trigger unit is used to compare signals to a value, and a trigger expression is used to combine trigger units to form a trigger.

Some of Reveal's triggering features are static and some are dynamic. Static features can only be changed in Reveal Inserter and require the design to be re-implemented by synthesis, map, place, and route. Although you can set most of the dynamic features in Reveal Inserter, you can change all dynamic

features when Reveal Analyzer is running, and you do not have to reimplement the design.

**Table 1: Where Trigger Features Can Be Changed**

| Feature                  |                               | Reveal<br>Inserter | Reveal<br>Analyzer |

|--------------------------|-------------------------------|--------------------|--------------------|

| Trigger Units            | Add                           | ✓                  |                    |

|                          | Remove                        | 1                  | <b>✓</b>           |

|                          | Name                          | <b>√</b>           | <b>✓</b>           |

|                          | Signals                       | <b>√</b>           |                    |

|                          | Operator                      | ✓                  | <b>✓</b>           |

|                          | Radix                         | ✓                  | <b>V</b>           |

|                          | Value                         | ✓                  | <b>√</b>           |

| Trigger Expressions      | Add                           | ✓                  |                    |

|                          | Remove                        | ✓                  | <b>1</b>           |

|                          | Name                          | ✓                  | <b>1</b>           |

|                          | Expression                    | ✓                  | <b>1</b>           |

|                          | RAM type                      | ✓                  |                    |

|                          | Maximum sequence depth        | ✓                  |                    |

|                          | Maximum event counter         | ✓                  |                    |

| Single Trigger Capture   | Make available                | ✓                  |                    |

| Multiple Trigger Capture | Make available                | ✓                  |                    |

|                          | Number of samples per trigger | ✓                  | <b>✓</b>           |

|                          | Number of triggers            |                    | <b>1</b>           |

| Other Features           | AND All versus OR All         |                    | <b>✓</b>           |

|                          | Trace buffer depth            | <b>√</b>           |                    |

|                          | Timestamp                     | <b>√</b>           |                    |

|                          | Trigger position              |                    | 1                  |

### **Trigger Units**

The trigger unit is used to compare a number of input signals to a value. A number of different operators are available for comparison and can be dynamically changed during analysis, along with the comparison value and the trigger unit name.

You can change the signals in a trigger unit only in Reveal Inserter. Changing the input signals requires the design to be re-implemented.

You can specify up to 16 trigger units for each debug core. A common technique is to group associated input signals into a trigger unit. For example, you might use a trigger unit for the address bus in a design, another for the data bus, and another for the control signals.

Most of the trigger unit operators use standard logical comparisons between the current value of the combined signals of the trigger unit and a specified value. But some of the operators are unusual and need some explanation.

With the exception of "serial compare," the operators can be changed in Reveal Analyzer.

#### **Standard Logical Operators**

Reveal includes the following operators:

- == equal to

- != not equal to

- > greater than

- > = greater than or equal to

- < less than</p>

- <= less than or equal to</p>

#### Rising-Edge and Falling-Edge Operators

The "rising edge" and "falling edge" operators check for change in the signal value, not the value itself. So the trigger unit's specified value is a bit mask showing which signals should have a rising or falling edge. A 1 means "look for the edge;" a 0 means "ignore this bit." A multiple-bit value is true if any of the specified bits has the edge.

For example, consider a trigger unit defined as cout[3:0], rising edge, 1110. This trigger unit will be true only when cout[3], cout[2], or cout[1] have a rising edge. What happens on cout[0] does not matter.

**>** 0000 > 1110

True because cout[3], cout[2], and cout[1] rise.

0000 > 1111

True for the same reason. It does not matter whether cout[0] rises or not.

0000 > 0100

True because a rising edge on any of the specified bits is sufficient.

**1000 > 1000**

False because cout[3] did not rise. It just stayed high.

#### **Serial Compare**

The "serial compare" operator checks for a series of values on a single signal. For example, if a trigger unit's specified value is 1011, the "serial compare" operator looks for a 1 on the first clock, a 0 on the next clock, a 1 on the next clock, and a 1 on the last clock. Only after those four conditions are met in those four clock cycles is the trigger unit true.

Serial compare is available only when a single signal is listed in the trigger unit's signal list. The radix is automatically binary.

You can only set the serial compare operator in Reveal Inserter. You cannot change it or select it in Reveal Analyzer as you can the other operators.

### **Trigger Expressions**

Trigger expressions are combinations of trigger units. Trigger units can be combined in combinatorial, sequential, and mixed combinatorial and sequential patterns. A trigger expression can be dynamically changed at any time. Each core supports up to 16 trigger expressions that can be dynamically enabled or disabled in Reveal Analyzer. Trigger expressions support AND, OR, XOR, NOT, parentheses (for grouping), THEN, NEXT, # (count), and ## (consecutive count) operators. Each part of a trigger expression, called a sequence, can also be required to be valid a number of times before continuing to the next sequence in the trigger expression.

#### **Detailed Trigger Expression Syntax**

Trigger expressions in both Reveal Inserter and Reveal Analyzer use the same syntax.

#### **Operators**

You can use the following operators to connect trigger units:

- & (AND) Combines trigger units using an AND operator.

- (OR) Combines trigger units using an OR operator.

- ^ (XOR) Combines trigger units using a XOR operator.

- ! (NOT) Combines a trigger unit with a NOT operator.

- Parentheses Groups and orders trigger units.

- THEN Creates a sequence of wait conditions. For example, the following statement:

```

TU1 THEN TU2

```

means "wait for TU1 to be true, then wait for TU2 to be true."

#### The following expression:

```

(TU1 & TU2) THEN TU3

```

means "wait for TU1 and TU2 to be true, then wait for TU3 to be true."

Reveal supports up to 16 sequence levels.

See **Sequences and Counters** below for more information on THEN statements.

- NEXT Creates a sequence of wait conditions, like THEN, except the second trigger unit must come immediately after the first. That is, the second trigger unit must occur in the next clock cycle after the first trigger unit. See **Sequences and Counters** below for more information on NEXT statements.

- # (count) Inserts a counter into a sequence. See Sequences and Counters below for information on counters.

- ## (consecutive count) Inserts a counter into a sequence. Like # (count) except that the trigger units must come in consecutive clock cycles. That is, one trigger unit immediately after another with no delay between them. See Sequences and Counters below for information on counters.

#### **Case Sensitivity**

Trigger expressions are case-insensitive.

#### **Spaces**

You can use spaces anywhere in a trigger expression.

#### **Sequences and Counters**

Sequences are sequential states connected by THEN or NEXT operators. A counter counts how many times a state must occur before a THEN or NEXT statement or the end of the sequence. The maximum value of this count is determined by the Max Event Counter value. This value must be specified in Reveal Inserter and cannot be changed in Reveal Analyzer.

Here is an example of a trigger expression with a THEN operator:

```

TU1 THEN TU2

```

This trigger expression is interpreted as "wait for TU1 to be true, then wait for TU2 to be true."

If the same example were written with a NEXT operator:

```

TU1 NEXT TU2

```

it is interpreted as "wait for TU1 to be true, then wait *one clock cycle* for TU2 to be true." If TU2 is not true in the next clock cycle, the sequence fails and starts over, waiting for TU1 again.

The next trigger expression:

```

TU1 THEN TU2 #2

```

is interpreted as "wait for TU1 to be true, then wait for TU2 to be true for two sample clocks." TU2 may be true on consecutive or non-consecutive sample clocks and still meet this condition.

### The following statement:

```

TU1 ##5 THEN TU2

```

means that TU1 must occur for five consecutive sample clocks before TU2 is evaluated. If there are any extra delays between any of the five occurrences of TU1, the sequence fails and starts over.

### The next expression:

```

(TU1 & TU2) #2 THEN TU3

```

means "wait for the second occurrence of TU1 and TU2 to be true, then wait for TU3."

#### The last expression:

```

TU1 THEN (1) #200

```

means "wait for TU1 to be true, then wait for 200 sample clocks." This expression is useful if you know that an event occurs a certain time after a condition.

You can only use one count (# or ##) operator per sequence. For example, the following statement is not valid, because it uses two counts in a sequence:

```

TU1 #5 & TU2 #2

```

Multiple count values are allowed for a single trigger expression, but only one per sequence. For two count operators to be valid in a trigger expression, the expression must contain at least one THEN or NEXT operator, as in the following example:

```

(TU1 & TU2) #5 THEN TU2 #2

```

This expression means "wait for TU1 and TU2 to be true for five sample clocks, then wait for TU2 to be true for two sample clocks."

Also, the count operator must be applied to the entire sequence expression, as indicated by parentheses in the expression just given. The following is not allowed:

```

TU1 #5 & TU2 THEN TU2 #2

```

The count (#) operator cannot be used as part of a sequence following a NEXT operator. A consecutive count (##) operator may be used after a NEXT operator. The following is not allowed:

```

TU1 NEXT TU2 #2

```

The count (# or ##) operators can only be used in one of two areas:

- Immediately after a trigger unit or parentheses(). However, if the trigger unit is combined with another trigger unit without parentheses, a # cannot be used.

- After a closing parenthesis.

#### **Precedence**

The symbols used in trigger expression syntax take the following precedence:

- Because it inserts a sequence, the THEN and NEXT operators always take the highest precedence in trigger expressions.

- Between THEN or NEXT statements, the order is defined by parentheses that you insert. For example, the following trigger expression:

```

TU1 & (TU2|TU3)

```

means "wait for either TU1 and TU2 or TU1 and TU3 to be true."

If you do not place any parentheses in the trigger expression, precedence is left to right until a THEN or NEXT statement is reached.

For example, the following trigger expression:

```

TU1 & TU2|TU3

```

is interpreted as "wait for TU1 & TU2 to be true or wait for TU3 to be true."

- ► The precedence of the ^ operator is same as that of the & operator and the | operator.

- ► The logic negation operator (!) has a higher precedence than the ^ operator, & operator, or | operator, for example:

```

!TU1 & TU2

```

means "not TU1 and TU2."

- ► The # and ## operators have the same precedence as the ^ operator, & operator, or | operator. However, they can only be used in one of two areas:

- Immediately after a trigger unit or trigger units combined in parentheses. However, if the trigger unit is combined with another trigger unit without parentheses, a # or ## operator cannot be used.

Here is an example of correct syntax using the count (#) operator:

```

TU1 #2 THEN TU3

```

This statement means "wait for TU1 to be true for two sample clocks, then wait for TU3."

However, the following syntax is incorrect, because the count operator is applied to multiple trigger units combined without parentheses:

```

TU1 & TU2#2 THEN TU3

```

After a closing parenthesis. Use parentheses to combine multiple trigger units and then apply a count, as in the following example:

```

(TU1 & TU2) #2 THEN TU3

```

This statement means "wait for the combination of TU1 and TU2 to be true for two sample clocks, then wait for TU3."

Following is a series of examples that demonstrate the flexibility of trigger expressions.

### **Example 1: Simplest Trigger Expression**

Following is the simplest trigger expression:

TU1

This trigger expression is true, causing a trigger to occur when the TU1 trigger unit is matched. The value and operator for the trigger unit is defined in the trigger unit, not in the trigger expression.

### **Example 2: Combinatorial Trigger Expression**

An example of a combinatorial trigger expression is as follows:

TU1 & TU2 | TU3

This trigger expression is true when (TU1 and TU2) or TU3 are matched. If no precedence ordering is specified, the order is left to right.

# **Example 3: Combinatorial Trigger Expression with Precedence Ordering** In the following example of a combinatorial trigger expression, precedence makes a difference:

TU1 & (TU2 | TU3)

This trigger expression gives different results than the previous one. In this case, the trigger expression is true if (TU1 and TU2) or (TU1 and TU3) are matched.

#### **Example 4: Simple Sequential Trigger Expression**

Following is an example of a simple sequential trigger expression:

#### TU1 THEN TU2

This trigger expression looks for a match of TU1, then waits for a match on TU2 a minimum of one sample clock later. Since this expression uses a THEN statement, it is considered to have multiple sequences. The first sequence is "TU1," since it must be matched first. The second sequence is "TU2," because it is only checked for a match after the first sequence has been found. The "sequence depth" is therefore 2.

The sequence depth is an important concept to understand for trigger expressions. Since the debug logic is inserted into the design, logic must be used to support the required sequence depth. Matching the depth to the entered expression can be used to minimize the logic. However, if you try to define a trigger expression that has a greater sequence depth than is available in the FPGA, an error will prevent the trigger expression from running. The dynamic capabilities of the trigger expression can therefore be limited. To allow more flexibility, you can specify the maximum sequence depth when you set up the debug logic in Reveal Inserter. You can reserve more room for the trigger expression than is required for the trigger

expression currently entered. If you specify multiple trigger expressions, each trigger expression can have its own maximum sequence depth.

### **Example 5: Mixed Combinatorial and Sequential Trigger Expression**

Here is an example showing how you can mix combinatorial and sequential elements in a trigger expression:

### TU1 & TU2 THEN TU3 THEN TU4 | TU5

This trigger expression only generates a trigger if (TU1 AND TU2) match, then TU3 matches, then (TU4 or TU5) match. You can set precedence for any sequence, but not across sequences. The expression (TU1 & TU2) | TU3 THEN TU4 is correct. The expression (TU1 & TU2 THEN TU3) | TU4 is invalid and is not allowed.

### **Example 6: Sequential Trigger Expression with Sequence Counts**

The next trigger expression shows two new features, the sequence count and a true operator to count sample clocks:

### (TU1 & TU2)#2 THEN TU3 THEN TU4#5 THEN (1)#200

This trigger expression means wait for (TU1 and TU2) to be true two times, then wait for TU3 to be true, then wait for TU4 to be true five times, then wait 200 sample clocks. The count (# followed by number) operator can only be applied to a whole sequence, not part of a sequence. When the count operator is used in a sequence, the count may or may not be contiguous. The always true operator (1) can be used to wait or delay for a number of contiguous sample clocks. It is useful if you knew that an event that you wanted to capture occurred a certain time after a condition but you did not know the state of the trigger signals at that time.

However, there is a limitation on the maximum size of the counter. This depends on how much hardware is reserved for the sequence counter. When you define a trigger expression, the Max Event Counter setting in the Trigger Expression section of Reveal Inserter and Reveal Analyzer specifies how large a count value is allowed in the trigger expression. Each trigger expression can have a unique Max Event Counter setting.

# **Trigger Expression and Trigger Unit Naming Conventions**

You can rename trigger units and trigger expressions. The names can be a mixture of lower-case or upper-case letters, underscores, and digits from 0 through 9. The first character must be either an underscore or a letter. The names can be any length.

### **Adding Trigger Units**

You can add trigger units only in Reveal Inserter. You cannot add them in Reveal Analyzer. You can change some of the trigger conditions defined in Reveal Inserter in Reveal Analyzer during hardware debugging.

All trigger units are automatically available for use in all trigger expressions defined.

Each core can support up to 16 trigger expressions. Each trigger unit consists of the following:

- Trigger unit name (label)

- Signals in the trigger unit

- Comparison function

- Radix of the trigger unit value

- Value of the trigger unit

### To add a trigger unit:

- If you want the buses in the new trigger units that you will add to have a certain radix by default, set that radix in the **Default Trigger Radix** box in the Trigger Unit section of the Trigger Signal Setup tab before you add any trigger units.

- Changing the trigger radix value does not affect any trigger units that were created before you made the change.

- 2. To add a new trigger unit, click **Add** in the Trigger Unit section of the Trigger Signal Setup tab.

- A line now appears in the Trigger Unit section, with a default trigger unit named TU<number>, where number is a sequential number. The first trigger unit is named TU1 by default.

### **Renaming Trigger Units**

You can rename a trigger unit.

### To rename a trigger unit:

Double-click in the appropriate box in the Name column of the Trigger Unit section of the Trigger Signal Setup tab, backspace over the existing name, and type in the new name.

### **Setting Up Trigger Units**

All signals must be defined for a trigger unit in Reveal Inserter. You cannot change them in Reveal Analyzer.

### To set up a trigger unit:

- If you want to change the default name of the trigger unit, backspace over the default name in the Name box in the Trigger Unit section of the Trigger Signal Setup tab and type the new name.

- 2. Specify the signals in the trigger unit:

- a. Double-click in the box in the Signals (MSB:LSB) column.

- The TU Signals dialog box appears.

- b. In the Select Signals box of the dialog box, highlight the signal or signals that you want to use in the trigger unit, and click > to move them to the box on the right. (Shift-click to select multiple signals.)