# Lattice Radiant Software 2025.2 User Guide

### Copyright

Copyright © 2025 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopity Pro are trademarks of Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. QuestaSim is a trademark or registered trademark of Siemens Industry Software Inc. or its subsidiaries in the United States or other countries. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

# **Type Conventions Used in This Document**

| Convention        | Meaning or Use                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------|

| Bold              | Items in the user interface that you select or click. Text that you type into the user interface. |

| <italic></italic> | Variables in commands, code syntax, and path names.                                               |

| Ctrl+L            | Press the two keys at the same time.                                                              |

| Courier           | Code examples. Messages, reports, and prompts from the software.                                  |

|                   | Omitted material in a line of code.                                                               |

|                   | Omitted lines in code and report examples.                                                        |

| [ ]               | Optional items in syntax descriptions. In bus specifications, the brackets are required.          |

| ( )               | Grouped items in syntax descriptions.                                                             |

| { }               | Repeatable items in syntax descriptions.                                                          |

| 1                 | A choice between items in syntax descriptions.                                                    |

|                   |                                                                                                   |

Chapter 1

# **Contents**

Introduction 9

|           | User Guide Organization 10                                                                                                                                                                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | Getting Started 11 Prerequisites 11 Creating a New Project 12 Opening an Existing Project 15 Importing a Lattice Diamond Project 16 Next Steps 16                                                                                                                          |

| Chapter 3 | Design Environment Fundamentals 18 Overview 18 Project-Based Environment 19 Process Flow 20 Shared Memory 21 Context-Sensitive Data Views 22                                                                                                                               |

| Chapter 4 | User Interface Operation 24  Start Page 24  Menus and Toolbars 25  Reports and Messages Views 25  File List Views 26  Tool View Area 26  Output and Tcl Console 27  Basic UI Controls 28  File List 28  Using Revision Control for Radiant Projects 29  Source Template 34 |

```

IP Catalog 35

Process 36

Task Detail View 37

Hierarchy 37

Reports 38

Tool Views 39

Tcl Console 40

Output 40

Message 41

Find Results 41

Common Tasks 42

Controlling Views 42

Cross-Probing 43

Chapter 5

Working with Projects

Overview 47

Implementations 49

Adding Implementations 49

Cloning Implementations 50

Input Files 51

Pre-Synthesis Constraint Files 51

Post-Synthesis Constraint Files 52

Debug Files 53

Script Files 53

Analysis Files 54

Programming Files 54

Strategies 54

Area 56

Timing 57

User-Defined 57

Constraint Propagation Options 57

Synplify Pro Options 58

LSE Options 64

Post-Synthesis Options 71

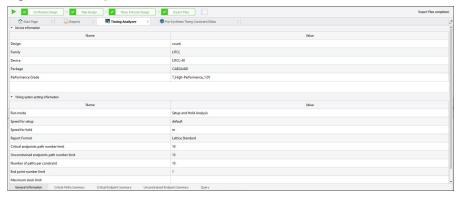

Post-Synthesis Timing Analysis Options 72

Map Design Options 73

Map Timing Analysis Options 74

Place & Route Design Options 76

Place & Route Timing Analysis Options 79

IO Timing Analysis Options 80

Timing Simulation Options 80

Bitstream Options 81

Common Tasks 83

Creating a Project 84

Changing the Target Device 84

Setting the Top Level of the Design 84

Editing Files 85

Saving Project Data 85

```

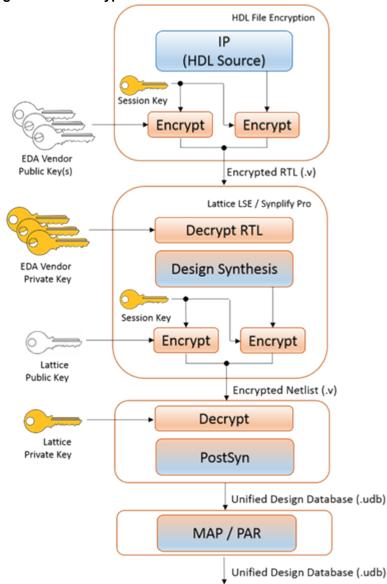

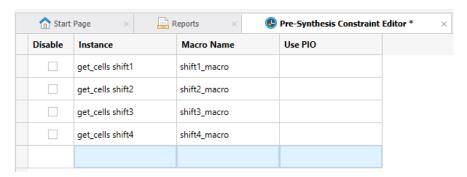

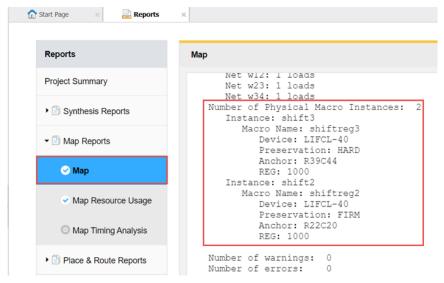

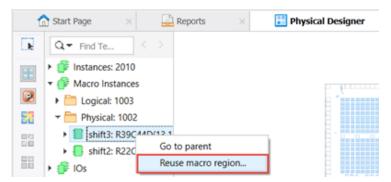

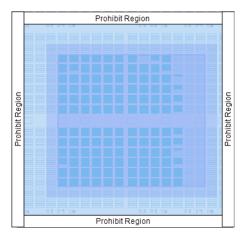

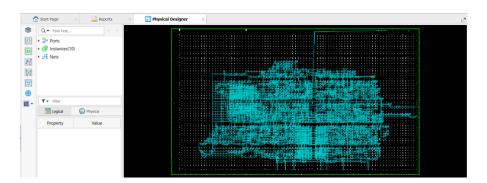

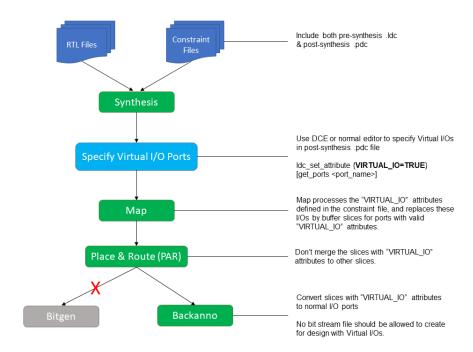

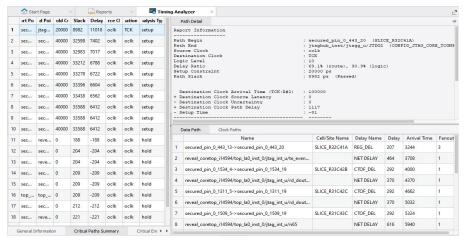

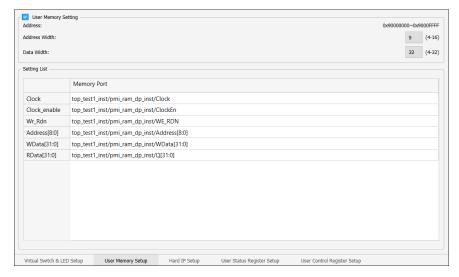

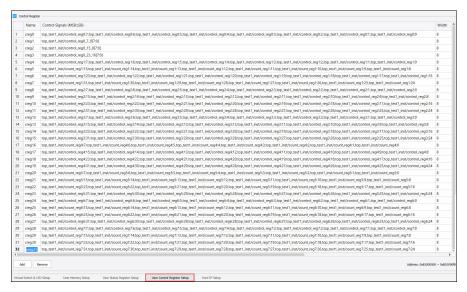

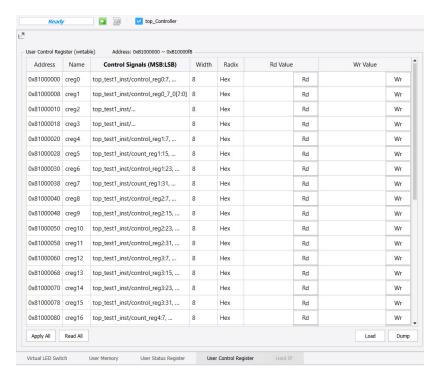

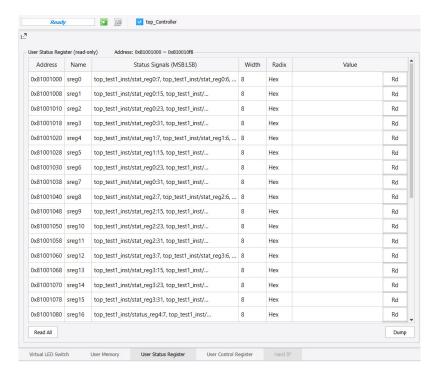

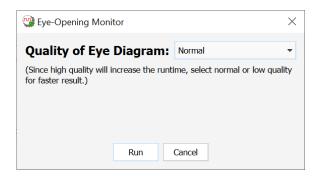

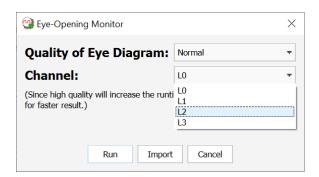

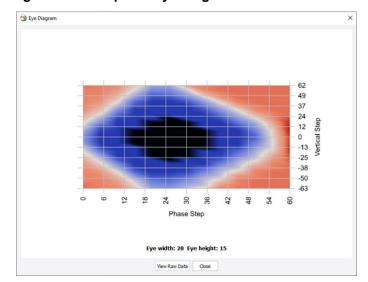

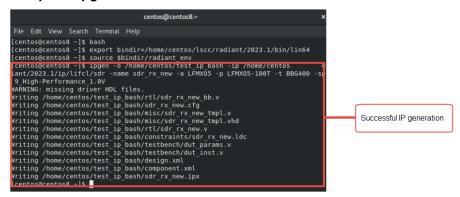

#### Chapter 6 Radiant Software Design Flow 86 Overview 86 Design Flow Processes 87 Running Processes 88 IP Encryption Flow 88 HDL File Encryption Flow 90 HDL File Encryption Steps 91 Block-Based Design - Using Macro Blocks 94 Creating a Macro Block 96 Creating a Macro Region 99 Exporting Macro 103 Reusing a Macro Block 105 Macro Usage Guidelines 110 Implementation Flow and Tasks 110 Synthesis Constraint Creation 111 Constraint Creation 112 Simulation Flow 114 Simulation Wizard Flow 115 Chapter 7 Working with Tools and Views 119 Overview 119 View Menu Highlights 119 Start Page 120 Reports 120 Tools 121 Timing Constraint Editor 122 Unified Constraints Flow 123 Constraint Propagation 124 Device Constraint Editor 124 Specifying Virtual I/O Ports 138 Checking the Virtual I/O Ports 140 Verifying Virtual I/O Ports 141 Netlist Analyzer 142 Physical Designer 143 Timing Analyzer 145 Using Standalone Timing Analyzer 146 Reveal Inserter 149 Configuring User Memory Setup 150 Configuring User Control Register Setup 152 Configuring User Status Register Setup 153 Reveal Analyzer 154 Reveal Controller 160 Power Calculator 160 ECO Editor 161 Programmer 162 Run Manager 163 Synplify Pro for Lattice 163 Mentor ModelSim 164 Simulation Wizard 164 Source Template 165

IP Catalog 165

IP Packager 166 SEI Editor 167 Common Tasks 167 Controlling Tool Views 167 Using Zoom Controls 169 Displaying Tool Tips 170 Setting Display Options 170 Chapter 8 **Command Line Reference Guide** 172 Command Line Program Overview 172 Command Line Basics 174 Command Line Data Flow 174 Command Line General Guidelines 175 Command Line Syntax Conventions 176 Setting Up the Environment to Run Command Line 177 Invoking Core Tool Command Line Programs 178 Invoking Core Tool Command Line Tool Help 179 Command Line Tool Usage 179 Running cmpl libs.tcl from the Command Line 180 Running HDL Encryption from the Command Line 183 Running Synthesis from the Command Line 190 Running Postsyn from the Command Line 197 Running MAP from the Command Line 198 Running PAR from the Command Line 200 Running Timing from the Command Line 206 Running Backannotation from the Command Line **209** Running Bit Generation from the Command Line 212 Running Programmer from the Command Line 216 Running the Deployment Tool from the Command Line 220 Running SSPI from the Command Line 246 Running Various Utilities from the Command Line 249 Using Command Files 261 Using Command Line Shell Scripts 263 **Chapter 9 Tcl Command Reference Guide** 266 Launching the Tcl Console 269 Running Radiant Tcl 272 Log and Tcl Files 272 Valid Characters in File Name and Project Path 273 Lattice Implementation Directory 273 Attributes 274 Understanding Design Flows 274 Using Implementation Strategies and Options 275 Running Project Flow 277 Running Non-Project Flow 278 Switching From Project Flow to Non-Project Flow 278 Running Milestone Results in Non-Project Flow 279

> Accessing Command Help and Command Options in the Tcl Console 285 Changes in the Interface 286

Creating and Running Custom Tcl Scripts 286

Opening GUI in Non-Project Flow 280

Design Flow Examples 280

Radiant Software Tool Tcl Command Syntax General Radiant Commands 291 Radiant Software Tcl Console Commands 291 System Tcl Commands 293 Device Tcl Commands 295 IP Version Update Tcl Commands 299 Message Control Tcl Commands 302 Project Flow Commands 308 Radiant Software Project Tcl Commands 308 Non-project Commands 331 Synthesis Tcl Command 331 Place & Route Tcl Commands 332 Physical Synthesis Tcl Commands 334 Reveal Commands 335 Reveal Inserter Tcl Commands 335 Reveal Analyzer Tcl Commands 354 Power Calculator Commands 367 Power Calculator Tcl Commands 367 Simulation Related Commands 380 Simulation Libraries Compilation Tcl Commands 380 Timing and Physical Constraints Commands 383 Radiant Software Timing Constraints Tcl Commands 383 Radiant Software Physical Constraints Tcl Commands 397 Radiantc TCL Commands 410 Bitstream Generation Tcl Commands 411 Design Tcl Commands 412 Device Tcl Commands 423 Technology Mapping Tcl Commands 424 Placement Tcl Commands 425 Routing Tcl Commands 427 Timing Analysis Tcl Commands 429 Other Commands 438 Design Object Tcl Commands 438 Engineering Change Order Tcl Commands 445 Chapter 10 Advanced Topics 450 Shared Memory Environment 450 Clear Tool Memory 450 Environment and Tool Options 451 Batch Tool Operation 452 Tcl Scripts 452 Creating Tcl Scripts from Command History 452 Creating Tcl Scripts from Scratch 453 Sample Tcl Script 453 Running Tcl Scripts 454 Project Archiving 454 File Descriptions 455 Revision History 458

Running Tcl Scripts When Launching the Radiant Software 289

# Chapter 1

### Introduction

Lattice Radiant<sup>™</sup> software is the leading-edge software design environment for cost- sensitive, low-power Lattice Field Programmable Gate Arrays (FPGA) architectures. The Radiant software integrated tool environment provides a modern, comprehensive user interface for controlling the Lattice Semiconductor FPGA implementation process. Its combination of new and enhanced features allows users to complete designs faster, more easily, and with better results than ever before.

This user guide describes the main features, usage, and key concepts of the Radiant software design environment. It should be used in conjunction with the Release Notes and reference documentation included with the product software. The Release Notes document is also available on the Lattice Web site and provides a list of supported devices.

### **Radiant Software Overview**

The Radiant software uses an expanded project-based design flow and integrated tool views so that design alternatives and what-if scenarios can easily be created and analyzed. The *Implementations* and *Strategies* concepts provide a convenient way for users to try alternate design structures and manage multiple tool settings.

System-level information—including process flow, hierarchy, and file lists—is available, along with integrated HDL code checking and consolidated reporting features.

A fast Timing Analysis loop and Programmer provide capabilities in the integrated framework. The cross-probing feature and the shared memory architecture ensure fast performance and better memory utilization.

The Radiant software is highly customizable and provides Tcl scripting capabilities from either its built-in console or from an external shell.

The Radiant software has many of the same features as Lattice Diamond software, and adds new features, such as:

- Constraints support utilizing industry standard SDC format.

- Efficient, easy-to-use integrated graphical user interface (GUI) with a new look-and-feel that gives users more efficient access to popular tools.

Unified timing analysis engine with enhanced timing reports for faster design timing closure.

# **User Guide Organization**

This user guide contains all the basic information for using the Radiant software. It is organized in a logical sequence from introductory material, through operational descriptions, to advanced topics.

Key concepts and work flows are explained in "Design Environment Fundamentals" on page 18 and "Radiant Software Design Flow" on page 86.

Basic operation of the design environment is described in "User Interface Operation" on page 24.

The chapter "Working with Projects" on page 47 shows how to set up project implementations and strategies.

The chapter "Working with Tools and Views" on page 119 describes the many tool views available.

# **Getting Started**

This chapter explains how to run the Radiant software and open or create a project. For more information about project fundamentals, see the chapters "Design Environment Fundamentals" on page 18 and "Working with Projects" on page 47.

# **Prerequisites**

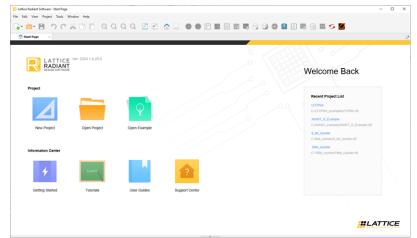

To run the Radiant software, select **Radiant Software** from the installation location. This opens the default Start Page, shown in Figure 1.

Figure 1: Default Start Page

# **Creating a New Project**

A project is a collection of all files necessary to create and download your design to the selected device. The New Project wizard guides you through the steps of specifying a project name and location, selecting a target device, and adding existing sources to the new project.

#### **Note**

Do not place more than one project in the same directory.

#### To create a new project:

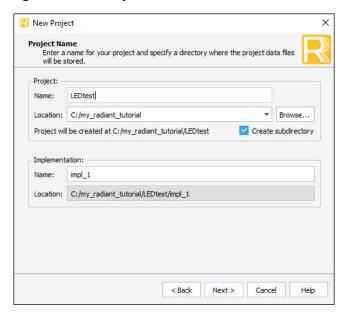

The New Project confirmation window opens, shown in Figure 2.

Figure 2: New Project Confirmation Window

2. Click **Next**. The New Project wizard opens, shown in Figure 3.

Figure 3: New Project Wizard

- 3. In the Project Name dialog box, do the following:

- Under Project, specify the name for the new project.

- File names for Radiant software projects and project source files must start with a letter (A-Z, a-z) and must contain only alphanumeric characters (A-Z, a-z, 0-9) and underscores (\_). Spaces are allowed.

- ➤ To specify a location for your project, click **Browse**. In the Project Location dialog box, you can specify a desired location.

- ▶ Under Implementation, specify the name for the first version of the project. You can have more than one version, or "implementation," of the project to experiment with. For more information on implementations, refer to "Implementations" on page 49.

- ➤ To create a sub-directory with the same name as your location directory, click Create Subdirectory. This will allow you to keep your project implementations separate. If this box is left unchecked, no subdirectory will be created in the project directory.

- When you finish, click Next.

- 4. In the Add Source dialog box, do the following if you have an existing source file that you want to add to the project. If there are no existing source files, click **Next**.

- a. Click Add Source. You can import HDL files at this time. In the Import File dialog box, browse for the source file you want to add, select it, and click Open.

The source file is then displayed in the Source files field.

- b. Repeat the above to add more files.

- c. To copy the added source files to the implementation directory, select Copy source to implementation directory. If you prefer to reference these files, clear this option.

- d. To create empty Lattice Design Constraint (.ldc) file and Physical Constraint File (.pdc) files that can be edited at a later time, select Create empty constraint files. Refer to the chapter "Implementations" on page 49 for more information about constraint files.

- e. When you finish, click Next.

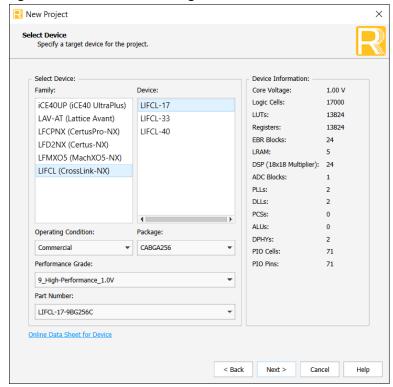

- 5. In the Select Device dialog box, shown in Figure 4, select a device family and a specific device within that family. Then choose the options you want for that device. When you finish, click **Next**.

Figure 4: Select Device Dialog Box

- In the Select Synthesis Tool dialog box, select the synthesis tool that you want to use. This choice can be changed at any time. When you finish, click Next.

- 7. In the Project Information dialog box, make sure the project settings are correct.

#### **Note**

If you want to change some of the settings, click **Back** to modify them in the previous dialog boxes of the New Project Wizard.

Click **Finish**. The newly created project, shown in Figure 5, is now created and open.

| Lattice Padent Software - Corlibal, countered | Reports | Report

Figure 5: Opened Project

Select the File List tab under the left pane, to view the Test project file list.

To close a project, choose File > Close Project.

# **Opening an Existing Project**

Use one of the following methods to open an existing Radiant software project:

- On the Start Page, click the Open Project button.

- From the File menu, choose Open > Project.

- On the Start Page, select the desired project from the Recent Projects

List. Alternatively, choose a recent project from the File > Recent

Projects menu.

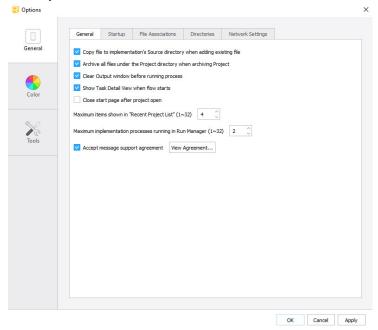

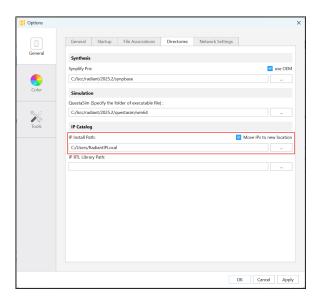

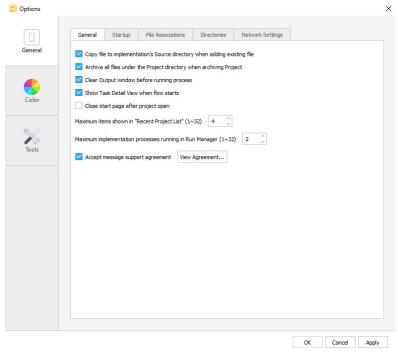

You can use the Options dialog box to increase the number of projects that are shown in the Recent Projects list and to automatically load the previous project at startup. Choose **Tools > Options** to open the dialog box. To increase the number of recent projects listed, click the **General** tab and enter a number for "Maximum items shown in Recent Project List" (up to 32). To automatically open the previous project during startup, click the **Startup** tab and then choose **Open Previous Project** from the "At Lattice Radiant Software startup" menu.

Figure 6: Recent Project List

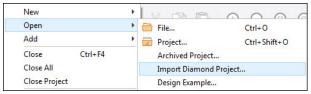

# **Importing a Lattice Diamond Project**

To import a Lattice Diamond project into the Radiant software, choose **File > Open > Import Diamond Project**.

Figure 7: Import Lattice Diamond Project

The file browser applies an \*.ldf file filter to help you find Lattice Diamond project files. The Lattice Diamond project is converted to a Radiant project.

For more information about importing Lattice Diamond projects into the Radiant software, refer to the *Lattice Radiant Software Guide for Diamond Users*.

### **Next Steps**

After you have a project opened in the Radiant software, you can go sequentially through the rest of this user guide to learn how to work with the entire design environment, or you can go directly to any topic of interest.

- ► The chapters "Design Environment Fundamentals" on page 18 and "Radiant Software Design Flow" on page 86 provide explanations of key concepts.

- "User Interface Operation" on page 24 provides descriptions of the functions and controls that are available in the Radiant software environment.

- The chapters "Working with Projects" on page 47 and "Working with Tools and Views" on page 119 explain how to run processes and use the design tools.

- Reference Guides > Tcl Command Reference Guide in the Radiant Help provides an introduction to the scripting capabilities available, plus command-line shell examples.

"Advanced Topics" on page 450 provides further details about environment options, shared memory, and Tcl scripting.

# Chapter 3

# **Design Environment Fundamentals**

This chapter provides background and discussion on the technology and methodology underlying the Radiant software design environment. Important key concepts and terminology are defined.

### Overview

Understanding some of the fundamental concepts behind the Radiant software framework technology will increase your proficiency with the tool and allow you to quickly come up to speed on its use.

The Radiant software is a next-generation software design environment that uses a new project-based methodology. A single project can contain multiple implementations and strategies to provide easily managed alternate design structures and tool settings.

The process flow is managed at a system level with run management controls and reporting. Context-sensitive views ensure that you only see the data that is available for the current state in the process flow.

The shared memory technology enables many of the advanced functions in the Radiant software. Easy cross-probing between tool views and faster process loops are among the benefits.

#### Note

By loading the Radiant software multiple times, you can run different Radiant projects simultaneously. However, you must not load the same project in more than one Radiant software instance, as software conflicts can occur.

The Radiant software can also be run remotely. Refer to the Lattice Radiant Software Installation Guide for Windows or Lattice Radiant Software Installation Guide for Linux for more information.

# **Project-Based Environment**

A project in the Radiant software consists of the following file types:

- HDL source files

- Constraint files

- Reveal debug files

- Script files for simulation

- Analysis files for power calculation and timing analysis

- Programming files

The Radiant software also includes settings for the targeted device and the different tools. The project data is organized into implementations, which define the project structural elements, and strategies, which are collections of tool settings.

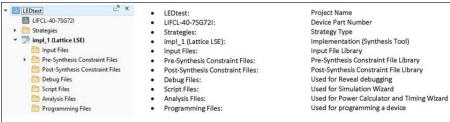

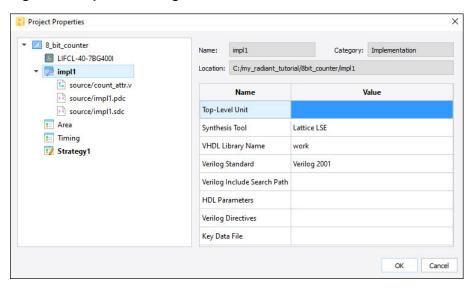

The following File List shows the items in a sample project.

Figure 8: File List

Each item that is displayed in **bold** means that it has been selected as the active item for an implementation. An implementation displayed in **bold** means that it has been selected as the currently active implementation for the project. Your project must have one active implementation, and the implementation must have one active strategy. Optional items, such as Reveal hardware debugger files, can be set as active or inactive.

The project is the top-level organizational element in the Radiant software, and it can contain multiple implementations and multiple strategies. This enables you to try different design approaches within the same project. If you want to have a Verilog version of your design, for example, make an implementation that consists of only the Verilog source files. If you want another version of the design with primarily Verilog files but a Structural Verilog (.vm) netlist for one module, create a new implementation using the Verilog and .vm source files. Each implementation can have Verilog, VHDL or Structural Verilog source or mixed of them. The same project and design is used, but with a different set of modular blocks.

Similarly, if you want to try different implementation tool options, you can create a new strategy with the new option values.

You manage these multiple implementations and strategies for your project by setting them as active. There can only be a single active implementation with its one active strategy at a time.

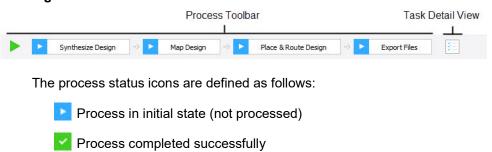

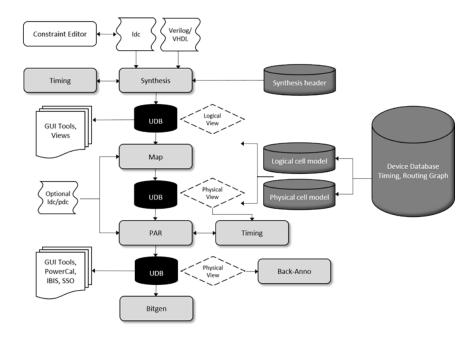

### **Process Flow**

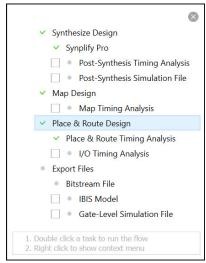

A process is a specific task in the overall processing of a source or project. Typical processing tasks include synthesizing, mapping, placing, and routing. You can view the available processes for a design in the Process Toolbar.

Figure 9: Process Toolbar

Click the Task Detail View 🔄 to see detailed information of the processes.

Processes are grouped into categories according to their functions.

#### Synthesize Design

Click on this process and Lattice Synthesis Engine (LSE) runs to synthesize the design. By default, this process runs the LSE tool.

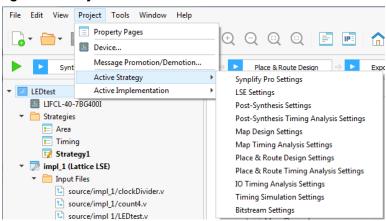

If you are using Synplify Pro, choose Synplify Pro as the synthesis tool (**Project > Active Implementation > Select Synthesis Tool**).

#### Post-Synthesis Timing Analysis

Runs timing analysis after the Synthesize Design process.

#### Post-Synthesis Simulation File

Generates a netlist file < file\_name > \_syn.vo used for functional verification.

#### Map Design

This process maps a design to an FPGA. Map Design is the process of converting a design represented as a network of device-independent components (such as gates and flip-flops) into a network of device-specific components (for example, configurable logic blocks).

#### Map Timing Analysis

Runs timing analysis after the Map Design process.

#### Place & Route Design

After a design has undergone the necessary translation to bring it into the Unified Database (.udb) format, you can run the Place & Route Design process. This process takes a mapped physical design .udb file, places and routes the design, and then outputs a file that can then be processed by the design implementation tools.

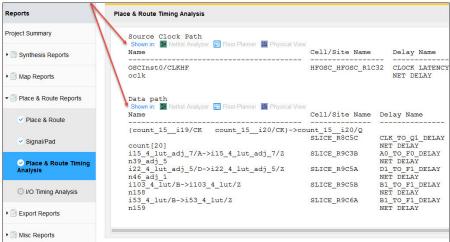

#### Place & Route Timing Analysis

Runs timing analysis after Place & Route process.

#### I/O Timing Analysis

Runs I/O timing analysis that allows you to view the path delay tables and Timing Analyzer report of your timing constraints after placement and routing.

#### Export Files

You can check the desired file you want to export and run this process.

#### Bitstream File

This process takes a fully routed physical design as input and produces a configuration bitstream (bit images). The bitstream file contains all of the configuration information from the physical design defining the internal logic and interconnections of the FPGA, as well as device-specific information from other files associated with the target device.

#### IBIS Model

This process generates a design-specific IBIS (I/O Buffer Information Specification) model file (*<project\_name>*.ibs).

IBIS models provide a standardized way of representing the electrical characteristics of a digital IC's pins (input, output, and I/O buffers).

#### Gate-Level Simulation File

This process backannotates the routed design with timing information so that you may run a simulation of your design. The backannotated design is a Verilog netlist.

The Reports view allows you to examine and print process reports.

Messages are displayed in the Messages window at the bottom of the Radiant software main window.

The process status icons are defined as follows:

- Process in initial state (not processed)

- Process completed successfully

- Process completed with unprocessed subtasks

- Process failed

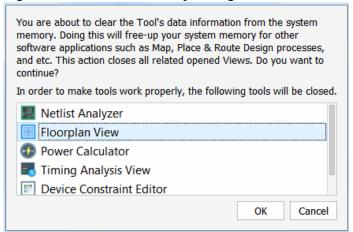

### Shared Memory

The Radiant software uses a shared memory architecture. All tool and data views look at the same design data at any point in time. This means that when you change a data element in one view of your design, all other views will see the change, whether they are active or not.

When project data has been changed but not yet saved, an asterisk (\*) is displayed in the title tab of the view.

Figure 10: Title Tab with Changed Content Indication

Notice that the asterisks indicating changed data will appear in all views referencing the changed data.

If a tool view becomes unavailable, the Radiant software environment will need to be closed and restarted.

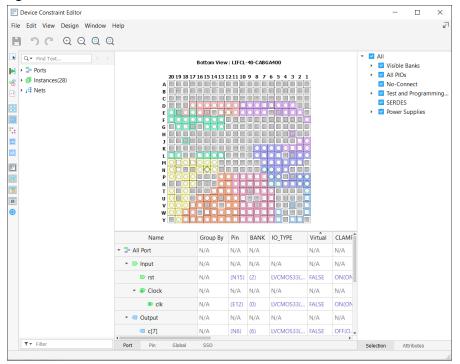

### **Context-Sensitive Data Views**

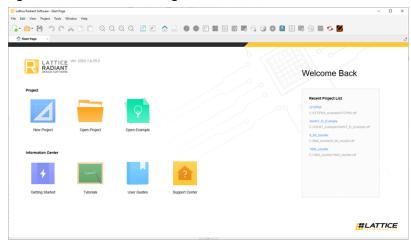

The data in shared memory reflects the state or context of the overall process flow. This means that views such as Device Constraint Editor Spreadsheet View will display only the data that is currently available, depending on process steps that have been completed.

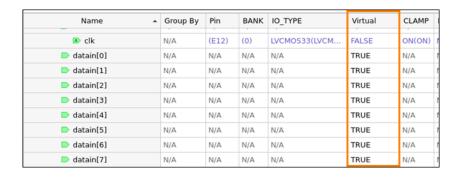

For example, Figure 11 shows the Process flow before Synthesis. Therefore, Spreadsheet View shows no IO Type or PULLMODE.

After Synthesis has been completed, Spreadsheet View displays IO Type and PULLMODE assignments, as shown in Figure 12.

Virtual Name Group By Pin BANK IO\_TYPE CLAMP All Port N/A N/A N/A N/A N/A N/A N/A ▼ ■ Input N/A N/A N/A N/A (N15) LVCMOS33(... FALSE rst N/A (2) ON(ON) ▼ 📾 Clock N/A N/A N/A N/A N/A N/A clk N/A (E12) (0) LVCMOS33(... **FALSE** ON(ON) Output N/A N/A N/A N/A N/A N/A LVCMOS33(... (N6) (6) **FALSE** OFF(O... c[7] N/A Pin Global SSO Port

Figure 12: Process Completed Through Synthesis

When you see the "Loading Data" message displayed in Figure 13, it means that a process has been completed and that the shared memory is being updated with new data.

Figure 13: Loading Data

All tool views are dynamically updated when new data becomes available. This means that when you rerun an earlier process while a view is open and displaying data, the view will remain open but dimmed because its data is no longer available.

# Chapter 4

# **User Interface Operation**

The Radiant user interface (UI) provides a comprehensive, integrated tool environment. The UI is very flexible and configurable, enabling you to store constraints for the layout you choose.

This chapter describes the user interface, controls, and basic operation of the Radiant software. Each major element of the interface is explained. The last section in the chapter describes common user interface tasks.

### Start Page

The Start Page contains three major sections, as shown in Figure 14.

Figure 14: Default Start Page

- **Project**: This section allows you to create a new project; open an existing Project, and open an example.

- Information Center: This section has links to Getting Started, Tutorials, User Guides, and Support Center.

- Recent Project List: Provides a quick way to load a recent project you've been working on.

The Start Page appears in the View area by default when the Radiant software is first launched, and can be opened from the View tab on the menu. The Start Page can be closed, opened, detached, and attached using the Attach button. See "Basic UI Controls" on page 28.

### **Menus and Toolbars**

At the top of the main window is the menu and toolbar area. High-level controls for accessing tools, managing files and projects, and controlling the layout are contained here. All toolbar functionality is also contained in the menus. The menus also have functions for system, project and toolbar control.

The Process Toolbar lists all the processes available, such as Synthesize Design, Map Design, Place & Route Design, and Export Files. A process is a specific task in the overall processing of a source or project. You can view the available processes for a design in the Process Toolbar. Click Task Detail **View** E to see detailed information of the processes available.

# **Reports and Messages Views**

The Reports view allows you to examine and print process reports. There are two panes in the Reports view. The left pane lists the reports. The right pane displays the reports.

Log messages are displayed in the Output frame of the Radiant software main window.

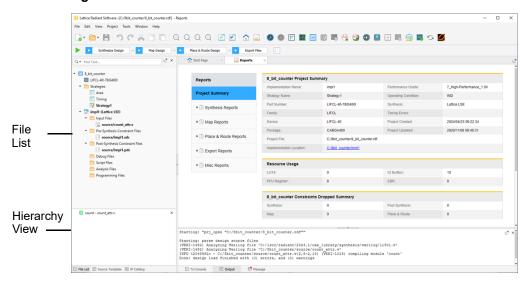

Figure 15: Reports and Log Message Views

### **File List Views**

In the middle of the main window on the left side is the File List area. This is where the overall project and process flow is displayed and controlled.

Figure 16: File List Area

Tabs at the bottom of the File List area allow you to select between the following views:

- File List shows the files in the project organized by implementations and strategies. This is not a hierarchical listing of the design.

- Source Template provides templates for creating VHDL, Verilog, and Constraint files.

- IP Catalog lists available modules/intellectual properties (IP).

Underneath the File List is the Hierarchy View area. It allows you to view the hierarchical design representation. Hierarchy view shares the left pane with File List view.

### **Tool View Area**

In the middle of the main window on the right side is the Tool View area. This is where the Start Page, Reports View, and all the Tool views are displayed.

Figure 17: Tool View Area

Multiple tools can be displayed at the same time. The tool tabs include controls for grouping the tool views as well as integrating all tool views back into the main window.

Each tool view is specific to its tool and can contain additional toolbars and multiple panes or windows controlled by additional tabs. The chapter "Working with Tools and Views" on page 119 provides more details about each tool and view.

Figure 18: Multiple Tools

## **Output and Tcl Console**

Near the right bottom of the main window is the Tcl Console, Output, and Message area.

Tabs at the bottom of this area allow you to select between Tcl Console, Output, and Message. Tool output is automatically displayed in the Output tab, and Errors and Warnings in the Message tab.

Figure 19: Output and Tcl Console Area

### **Basic UI Controls**

The Radiant software environment is based on modern industry standard user interface concepts. The menus, toolbars, and mouse pointer all behave in familiar ways. You can resize any of the window panes, drag and drop elements, right-click a design element to see available actions, and hold the mouse pointer over an object to view the tool tip. Window panes can also be detached from the main window and operated as independent windows.

### File List

The File List is a project view that shows the files in the project, including implementations and strategies. It is not a hierarchical listing of the design, but rather a list of all the design source, configuration and control files that make up the project.

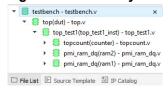

Figure 20: File List

At the top of the File List is the project name. Directly below the project name is the target device, followed by the strategies, and then the implementations. There must be one active implementation, and it must have one active strategy. Active elements are indicated in bold.

You can right-click any file or item in the File List to access a pop-up menu of currently available actions for that item. The pop-up menu contents vary, depending on the type of item selected.

The File List view can be hidden by clicking the small arrow in right border: "Click to show/hide side panel."

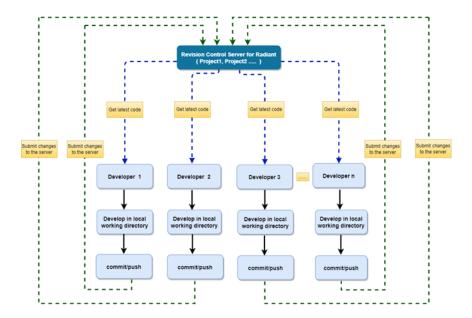

# **Using Revision Control for Radiant Projects**

Radiant supports revision control for your projects. When changes are logged into the revision control system, you can get all the change logs and switch to previous milestones if necessary. Compile times can be reduced when using revision control with Radiant design. The compilation will only start when inputs are changed.

#### **Recommended Revision Control System**

Radiant recommends the following revision control systems:

- **GIT**

- SVN

- Perforce

### Radiant Revision Control Strategies

You can select different revision control systems to work with Radiant, the software does not directly integrate a specific revision control into the system. Radiant recommends two strategies:

Minimum Files Strategy (Radiant Recommendation) – The revision control system only manages the necessary files of the project. Other files - including some intermediate and configuration files, are only used in your project and will not be submitted to the version management system.

The following files are recommended to commit to revision control systems:

- .rdf project file and .sty strategy file

- All source files under source directory

- All files under ip directory

- **Complete Strategy** You can also add some intermediate files on the project to the revision control system.

For this strategy, the files under implementation can be committed to the revision control system. You can select files to submit to the system under each implementation, which mainly includes intermediate and analysis files.

It is recommended to use the following strategy directory structure to manage source code and designs:

Radiant design can use one source directory to put all source or design files. The software can automatically identify various types of files and display them in categories in the File List View.

Use a source directory to place all source and design files for every implementation. Under the source folder, each implementation has its own file directory (e.g. impl\_1, impl\_2).

Create an IP directory (e.g. ip\_designs) under the source directory of the project to store all IP designs of Radiant. Each IP design has a subdirectory under the source directory to store IP source code and design files.

Use one implementation directory (e.g. impl\_1, impl\_2) to compile the relative implementation of the project. All intermediate files will be generated under this folder (.udb, status, report, and other intermediate type files are all here).

### **Radiant File Types**

The Radiant project directory contains the following file types:

- .rdf file Radiant project file

- .sty file Radiant strategy file

Common source or design file types under the source directory:

- .v file Verilog file

- .vhdl file VHDL file

- .sv file System Verilog file

- .ldc file LSE Design Constraints file

- .pdc file Post-Synthesis Constraint file

- .pcf file Power Calculator file

- .sdc file Pre-Synthesis Constraint file

- .rvl file Reveal Project file

- .rva file Reveal Analyzer file

- .vm file Structural Verilog file

- .fdc file Synplify Pro Constraint file

- IP\_ folder One IP instance file under the folder

#### Other intermedia file types:

- .ini file Initialization file

- .log file Log file

- .build\_status file Status file

- xml file XML configuration file

- ▶ .html file HTML file

- .ibs file Input/Output Buffer Information Specification file

- udb file User design Database file

- .bit file Bitstream

- synthesis.log LSE synthesis report

- .mrp Radiant map report

- .twr Radiant timing report

#### Note:

Intermedia files might be re-generated if you rerun the flow.

#### **Radiant Revision Control Workflow**

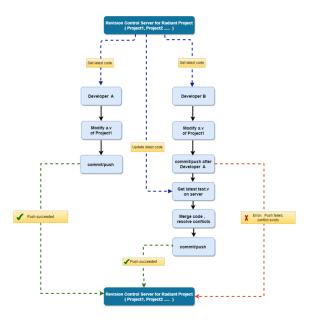

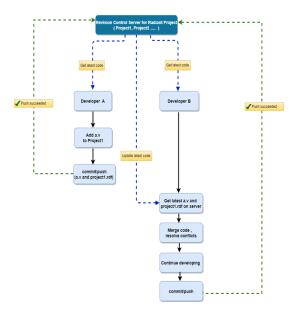

The following diagrams show the revision control workflow of Radiant.

#### **Revision Control Normal Workflow**

You can get the latest code from the radiant version server and develop in your own environment and working directory. Later on, you can submit the modified code or new design to the radiant version server as needed.

#### Multiple developers working on the same file

You may have your code changes and modify the same source file or design. For example, if you submit a file and another user updates it, you will get an error. At this time, you need to update the latest code locally from the server, integrate it with your modifications, and submit it again. This is the collaborative operation of multiple users for the revision control system.

#### Multiple developers adding files

If you add a new a.v file in the design, and submit this file and the Radiant project file to the revision control server, another user can do the following:

Get the latest code from the server

- Merge the local code

- Resolve the conflict

- Continue the subsequent development

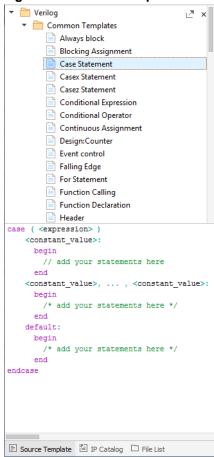

### **Source Template**

The Source Template is a project view that provides templates for creating VHDL, Verilog, and constraint files. Templates increase the speed and accuracy of design entry. You can drag and drop a template directly to the source file. You can also create your own templates.

To access templates, choose **View > Show Views > Source Template**, or click icon in the toolbar, or click on the **Source Template** tab in the bottom-left pane, to locate and access the following templates:

- Verilog, including common and Parameterized Module Instantiation (PMI), Primitives, Attributes, Encryption, and User Templates

- VHDL, including common, PMI, Primitives, Attributes, Encryption, and User Templates

- Constraints for LSE, including Timing and Physical constraints and User Templates

#### Note

For more information on PMI, refer to the Radiant Software Help. See **User Guides > Entering the Design > Designing with Soft IP, Modules, and PMI > PMI or IP Catalog?**

You can simply drag any template and drop it into your source file.

Figure 21: Source Template

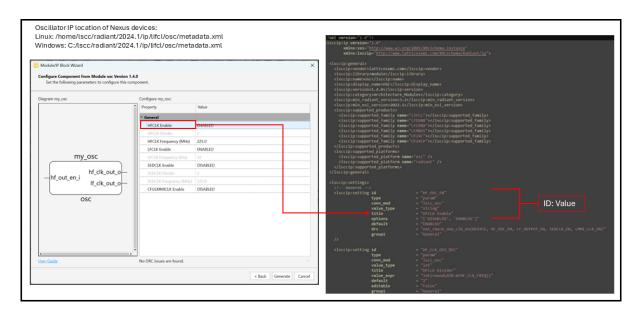

# **IP Catalog**

IP Catalog enables you to customize a collection of functional blocks from Lattice Semiconductor. Through the IP Catalog, you can access two types of functional blocks, Modules and IP.

To access IP catalog, choose **View > Show Views > IP Catalog**, or click icon in the toolbar, or click on the **IP Catalog** tab in the bottom-left pane.

Figure 22: IP Catalog

Each module is configurable with a unique set of properties. Once generated, the module or IP appears in your design's File List.

### **Process**

A process is a specific task in the overall processing of a source or project. Typical processing tasks include synthesizing, mapping, placing, and routing. You can view the available processes for a design in the Process Toolbar.

Figure 23: Process Toolbar

- Process completed with unprocessed subtasks

- Process failed

For more detail of different designs and Export Files available, see "Process Flow" on page 20.

## Task Detail View

Click Task Detail View 📒 to see detailed information of each process.

The default design flow processes are marked by check marks. To enable the remaining tasks, either check-mark the specific task and rerun the process step, or double-click the task's name. You can also right-click on the task to show the context menu.

Once the process has finished, the process status icon next to the task replaces the gray dot.

Figure 24: Task Detail View

Processes are grouped into categories according to their functions. To learn more about each process, view "Design Flow Processes" on page 87.

## Hierarchy

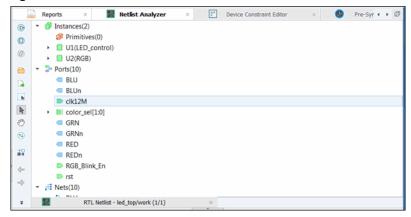

The Hierarchy view is a project view that displays the design hierarchy and is displayed by default. The hierarchical view is available when File List tab is selected.

Figure 25: Hierarchy View

If you would prefer that it not open by default, simply close Hierarchy View. The next time you launch the Radiant software, the Hierarchy View will not be opened. You can open it manually by selecting it from the View > Show View menu.

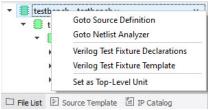

Right-click any of the objects in the Hierarchy View to see the available actions.

Figure 26: Hierarchy Item Pop-up Menu

The Hierarchy view can be selected, closed, and opened.

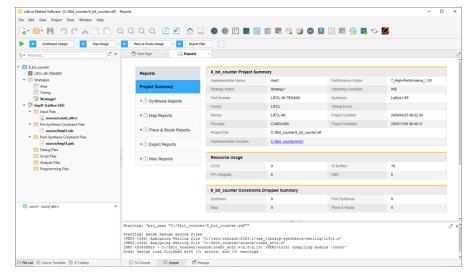

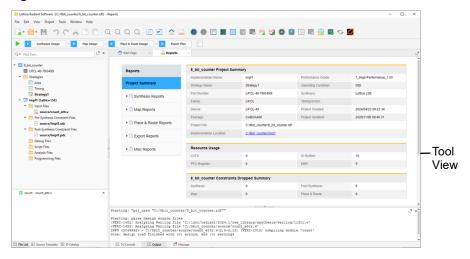

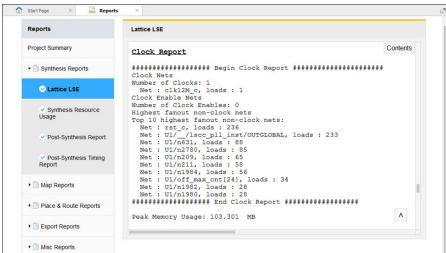

# Reports

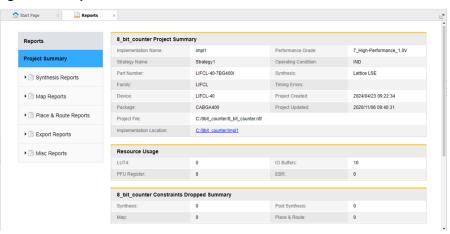

The Reports View provides a centralized reporting mechanism in the Tools view area. The Reports View is automatically displayed and updated when processes are run. It provides a separate tab for the current implementation, enabling you to compare results quickly.

The right pane displays the report for the selected step. You can also click the icon in the toolbar.

Figure 27: Reports View

The Reports pane on the right shows the detail of the project summary and resource usage. It also shows the number of dropped constraints from Synthesis, Post-Synthesis, MAP, and Place & Route.

The Report View can be selected, closed, opened, detached, and attached with the Attach button. See "Basic UI Controls" on page 28.

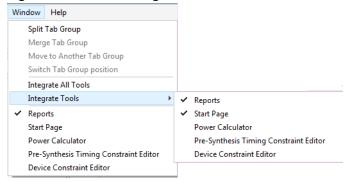

## **Tool Views**

The Tool view area of the UI displays the tools that are currently active. Each tool that you have opened from the toolbar or the Tools menu is displayed. The Reports and Start page, which can be opened from the toolbar or the Windows menu, are also displayed. When multiple tools are active, the display can be controlled with the tab group functions in the Window menu. See "Common Tasks" on page 42 for more information on tab group functions.

Each tool view is specific to its tool and can contain additional toolbars, multiple panes, or multiple windows controlled by additional tabs. See "Working with Tools and Views" on page 119 for descriptions of each tool and view, plus details on controlling their display.

The Tool views can be selected, closed, opened, detached, and attached using the Attach button. See "Basic UI Controls" on page 28

Figure 28: Tool View Tab Title

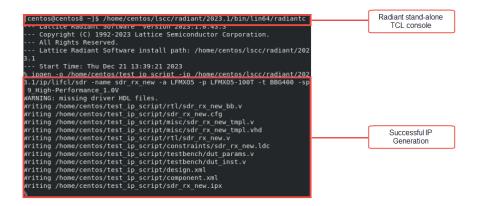

## Tcl Console

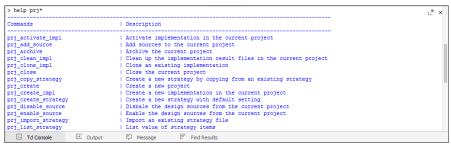

The Tcl Console is an integrated console for Tcl scripting. You can enter Tcl commands in the console to control all of the functionality of the Radiant software. Use the Tcl help command (help <tool name>\*) to display a list of valid extended Tcl commands.

Figure 29: Tcl Console

# **Output**

The Output View is a read-only area where tool output is displayed.

Figure 30: Output View

## Message

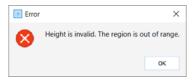

There are three message types available:

- Error -- displayed in red.

- Critical -- displayed in orange.

- Warnings -- displayed in yellow.

- General Information -- displayed in blue.

A red dot in the Message tab provides a visual notification Message that a new message/warning was received. Once you view the notification, the dot disappears.

Right-clicking a message provides a menu of commands, including Location in > Text Editor, which opens the source file in the Source Editor and highlights the location of the problem.

Figure 31: Message Display

## **Find Results**

The **Edit > Find in Files** command enables you to search for information in the files within your project directory. The search results are then displayed in the Find Results view.

Figure 32: Find Results View

## **Common Tasks**

The Radiant software UI controls many tools and processes. The following sections describe some of the more commonly performed tasks.

## **Controlling Views**

All of the views in the Radiant software are controlled in a similar manner, even though the information they contain varies widely. Here are some of the most common operations:

- ▶ Open Use the View > Show Views menu selections or right-click in the menu or toolbar areas to select a view from the pop-up menu.

- Select If a view is already open you can select its tab to bring it to the front.

- ▶ Detach Click the detach button in the upper right corner of the view.

- ▶ Attach Click the attach button 🔽 in the upper right corner of the view.

- Move − Click and hold a view's tab, and then drag and drop the view to a different position among the open views.

**Using a Tab Group** You can use the Window menu to split off a view and control it as a separate tab group. This allows you to examine two open views side by side. The controls work as follows:

- Split Tab Group displays two views side by side. See Figure 33.

- Move to Another Tab Group moves the selected tab to the other tab group. See Figure 34.

- ▶ Merge Tab Group merges a split tab group back into the primary view

- Switch Tab Group Position switches the positions of the two tab groups.

Figure 33: After Split Tab Group Command Used on Physical Designer

Figure 34: After Move to Another Tab Group Used on Netlist Analyzer

# **Cross-Probing**

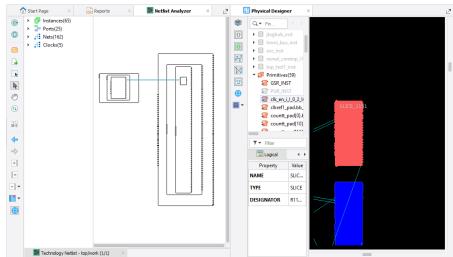

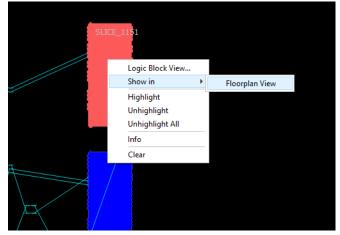

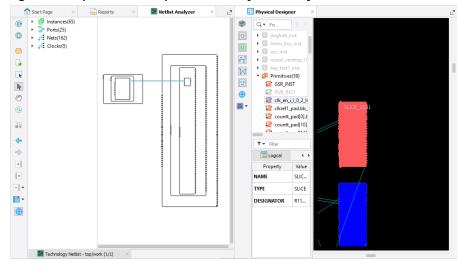

It is possible to select a data object in one view and see that same data object in a different view or views. Right-click an object to see if cross-probing is available. If it is, you will see a **Show In** sub-menu with the available views listed. If you select a view that is not yet open, the Radiant software will open it automatically. Cross-probing is available between Floorplan View and Physical View of Physical Designer, and from Netlist Analyzer to Physical Designer.

Figure 35: Show In Menu from Physical View of Physical Designer

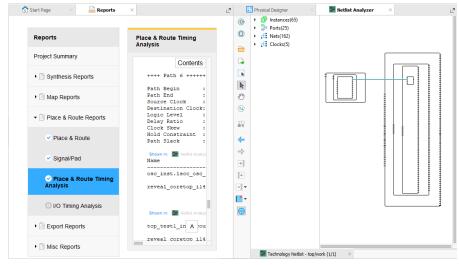

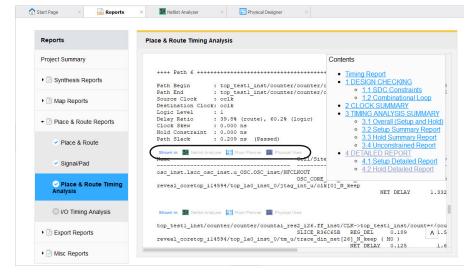

During the Radiant flow, various timing analyses and reports are created. You can view a specific path in Netlist Analyzer, Physical Designer's Floorplan View, and Physical Designer's Physical View. This allows for flexibility and reduced debugging effort.

### NOTE

Cross-probing to Netlist Analyzer is available only if the selected synthesis tool is LSE.

In the Reports tab, view any timing analysis report and identify a path to view. If cross-probing is available, the specific icon tools become visible, as shown in the following figure.

Figure 36: Available tools for Path Cross-Probing

Click on an icon and the tool opens with the selected path.

In some cases, the tool is unable to find the path. The message "Can't show the schematic of this timing path." appears. In an encrypted design, in some cases, cross-probing is not available. The message "Cannot open encrypted design." appears.

The following figures show cross-probing a path from the Place & Route Timing Analysis report to Netlist Analyzer, Physical Designer's Floorplan View, and Physical Designer's Physical View.

Figure 37: Path Cross-Probing in Reports

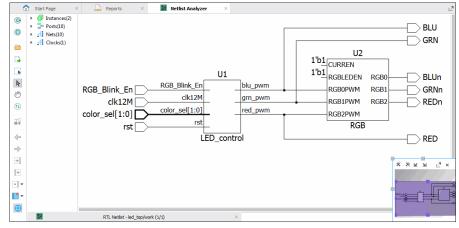

By clicking on the Netlist Analyzer icon, you can preview the data path in Netlist Analyzer.

Technology itelist - top/nork (1/1)

Figure 38: Path Cross-Probing in Netlist Analyzer

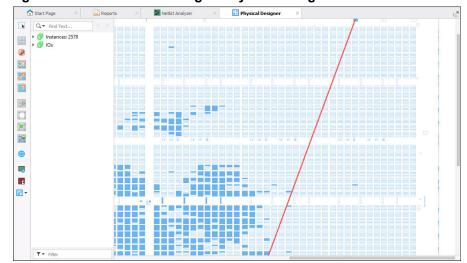

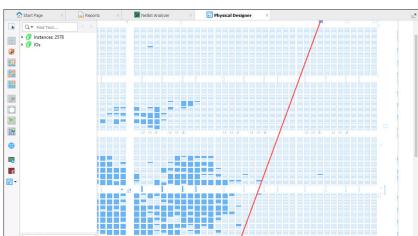

Similarly, by clicking on the Floor Planner icon, you can easily view the same path in Physical Designer's Placement Mode.

Figure 39: Path Cross-Probing in Physical Designer's Placement Mode

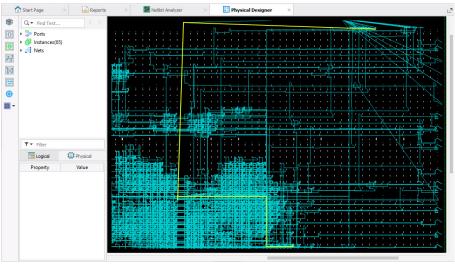

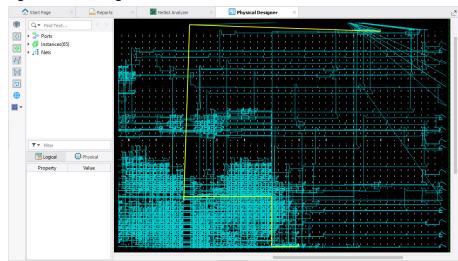

The same path is viewable in Physical Designer's Routing Mode by clicking on the Physical View icon in a timing report.

Figure 40: Path Cross-Probing in Physical Designer's Routing Mode

# Chapter 5

# **Working with Projects**

This chapter covers projects and their elements. Implementations and strategies are explained and some common project tasks are shown.

## Overview

A project is the top organizational element in the Radiant software design environment. Projects consist of design, constraint, configuration and analysis files. Only one project can be open at a time, and a single project can include multiple design structures and tool settings.

You can create, open, or import a project from the Start Page. Refer to "Getting Started" on page 11 for instructions on creating a new project.

Figure 41: Default Start Page

The File List view shows a project and its main elements.

Figure 42: Project Files in File List

The Project menu commands enable you to do the following:

- Examine the project properties.

- Change the target device.

- Change the severity level of warning messages.

- Set the synthesis tool.

- Show the active strategy tool settings.

- Set the top level design unit.

Figure 43: Project Menu

## **Implementations**

An implementation is the structure of a design and can be thought of as *what* is in the design. For example, one implementation might use inferred memory while another implementation uses instantiated memory. Implementations also define the constraint and analysis parameters for a project.

There can be multiple implementations in a project, but only one implementation can be active at a time. And there must be one active implementation. Every implementation has an associated active strategy. Strategies are a shared pool of resources for all implementations and are discussed in the next section. An implementation is created whenever you create a new project.

Implementations consist of the following files:

- Input files

- Pre-Synthesis constraint files

- Post-Synthesis constraint files

- Debug files

- Script files

- Analysis files

- Programming files

## **Adding Implementations**

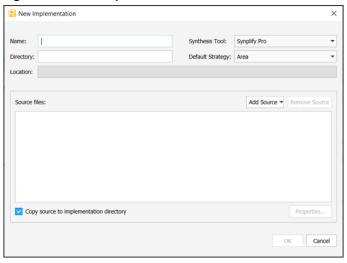

## To add a new implementation to an existing project:

1. Right-click the project name in the File List project view.

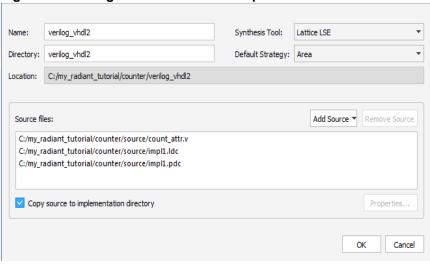

Select **Add > New Implementation**. In the New Implementation dialog box, you can set the implementation name, directory, default strategy, and add source files. When you select **Add Source** you have a choice of browsing for the source files or using a source from an existing implementation.

Figure 44: New Implementation

Notice that you have the option to "Copy source to implementation directory." If this option is selected, the source files will be copied from the existing implementation to the new implementation, and you will be working with different source files in the two implementations. If you want the two implementations to share the same source files and stay in sync, make sure that this option is not selected.

To make an implementation active, right-click its name in the File List and choose **Set as Active Implementation**.

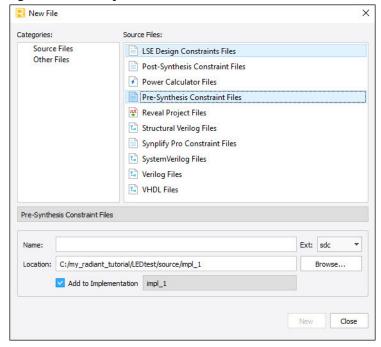

To add a file to an implementation, right-click the implementation name or any file folder in the implementation and choose **Add > New File** or **Add > Existing File**.

# **Cloning Implementations**

## To clone an implementation:

- 1. In the File List view, right-click on the name of the implementation that you want to copy and choose **Clone Implementation**.

- The Clone Implementation dialog box opens.

- 2. In the dialog box, enter a name for the new implementation. This name also becomes the default name for the folder of the implementation.

- 3. Change the name of the implementation's folder in the Directory text box, if desired.

- 4. Decide how you want to handle files that are outside of the original implementation directory. Select one of the following options:

- Continue to use the existing references

The same files will be used by both implementations.

## Copy files to new implementation source directory

The new implementation will have its own copies that can be changed without effecting the original implementation.

- The Synthesis Tool text box specifies the currently selected synthesis tool.

Go to Project > Active Implementation > Select Synthesis Tool to update your selection.

- The Default Strategy text box specifies the currently selected default strategy.

- 7. Click OK.

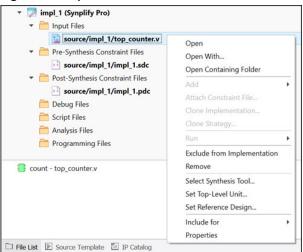

## **Input Files**

Input files are the design source files for the project. Input files can be any combination of Verilog, SystemVerilog, and VHDL.

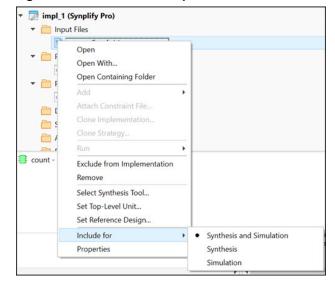

Right-click an input file name to open a pop-up menu of possible actions for that file.

Figure 45: Input File Actions

You can use the "Include for" commands to specify that a source file be included for both synthesis and simulation, synthesis only, or simulation only.

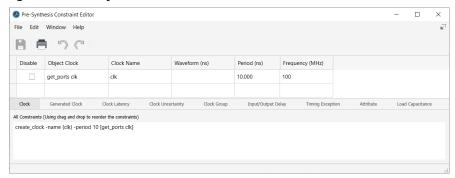

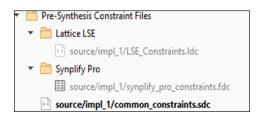

## **Pre-Synthesis Constraint Files**

Synopsys timing constraints are specified in the new .fdc file format. Legacy .sdc formats are still supported in the Radiant software and Synopsys has provided a script called sdc2fdc, which does a one-time conversion of .sdc files to the new .fdc format. More information about this script can be found in the Synplify Pro release notes.

An .fdc file can be added to an implementation if the selected synthesis tool is Synplify Pro. When using Synplify Pro or the Lattice Synthesis Engine (LSE), the constraints files can be saved as an .sdc file. If the selected synthesis tool is LSE, a Lattice design constraint (.ldc) synthesis file can be added. Constraints in the .ldc file use the Synopsys constraint format.

An implementation can have multiple synthesis constraint files. Only one synthesis constraint file can be active at a time. Unlike Post-Synthesis constraints, a synthesis constraint file must be set as active by the user.

## **Post-Synthesis Constraint Files**

Post-Synthesis constraint files (.pdc) contain both timing and non-timing constraint .pdc source files for storing logical timing/physical constraints. Constraints that are added using the Device Constraint Editor are saved to the active .pdc file. The active post-synthesis design constraint file is then used as input for post-synthesis processes.

An implementation can have multiple .pdc files, but only one can be active at a time.

Figure 46: Sample .pdc File

```

impl1.pdc

ldc_set_location -site P5 [get_ports clk]

#ldc create region -name RgnA -site R8C2D -width 18 -height 12

#ldc create group -name UgrpA [get cells counter1]

#ldc set location -region RgnA [ldc get groups UgrpB]

#ldc_create_group -name UgrpC -bbox {2 3} [get_cells counter3]

#ldc_set_location -site R8C25D [ldc_get_groups UgrpC]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[2]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[3]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[0]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[1]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[0]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[1]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[2]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[3]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[4]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[5]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[6]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[7]}]

#ldc set location -site 35 [get ports clk1]

create_clock -period 15 [get_nets counter1/clk1_c]

```

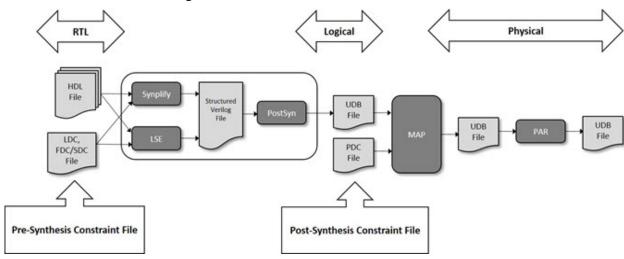

Figure 47 shows a high-level flow of how constraints from multiple sources can be used and modified in the Radiant software.

Figure 47: Radiant software Constraints Flow Chart

## **Debug Files**

The files in the Debug folder are project files for Reveal Inserter. They are used to insert hardware debug into your design. There can be multiple debug files, and one can be set as active. To insert hardware debug into your design, right-click a debug file name and choose **Set as Active Debug File** from the pop-up menu. The debug file name becomes bold, indicating that it is active. It is not required to have an active debug file.

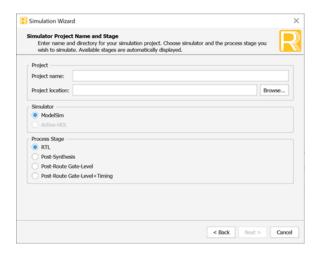

## **Script Files**

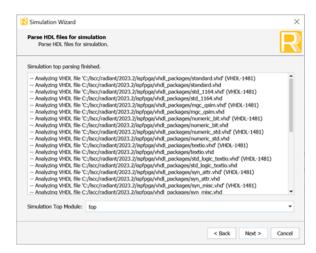

The Script Files folder contains the scripts that are generated by the Simulation Wizard. After you run the Simulation Wizard, the steps are stored in a simulation project file (.spf), which can be used to control the launching of the simulator.

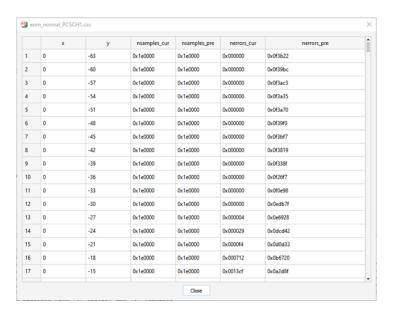

Simulation Wizard Summary Project Location: C:/sample/16bit\_counter Simulation Stage: RTL Simulation Files: C:/sample/16bit\_counter/source/impl\_1/top\_counter.v Simulation Libraries: pmi work ovi\_lifcl Simulation Top Module : count Launch Simulator GUI Design Optimization - Full Debug Add top-level signals to waveform display Run simulation Default Run 100.000 ns ▼ (0 means 'run -all') Simulator Resolution default ▼ < Back Finish Cancel

Figure 48: Simulation Script File

# **Analysis Files**

The Analysis Files folder contains Power Calculator files (.pcf). The folder can contain multiple analysis files, and one (or none) can be set as active. The active or non-active status of an analysis file affects the behavior of the associated tool view.

## **Programming Files**

Programming files (.xcf) are configuration scan chain files used by the Radiant Programmer for programming devices. The .xcf file contains information about each device, the data files targeted, and the operations to be performed.

An implementation can have multiple .xcf files, but only one can be active at a time. The file must be set as active by the user.

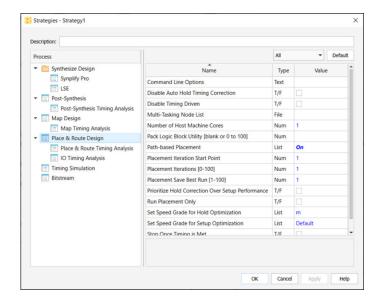

## **Strategies**

Strategies are collections of all the implementation-related tool settings in one convenient location. Strategies can be thought of as recipes for how the design will be implemented. An implementation defines what is in the design, and a strategy defines how that design will be run. There can be many strategies, but only one can be active at a time. There must be one active strategy for each implementation.

The Radiant software provides two predefined strategies: Area and Timing. It also enables you to create customized strategies. Predefined strategies cannot be edited, but they can be cloned, modified, and saved as customized user strategies. Customized user strategies can be edited, cloned, and removed. All strategies are available to all of the implementations, and any strategy can be set as the active one for an implementation.

To create a new strategy from scratch, choose File > New > Strategy. In the New Strategy dialog box, enter a name for the new strategy. Specify a file name for the new strategy and choose a directory to save the strategy file (.sty).

Figure 49: Creating a New Strategy from Scratch

The new strategy is with all the default settings of the current design. You can modify its settings in the Strategies dialog box.

If you want to save the strategy changes to your current project, choose File > Save Project from the Radiant software main window.

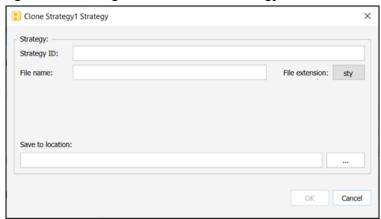

To create a new strategy from an existing one, right-click the existing strategy and choose Clone <strategy name> Strategy. Set the new strategy's ID and file name.

Figure 50: Cloning to Create a New Strategy

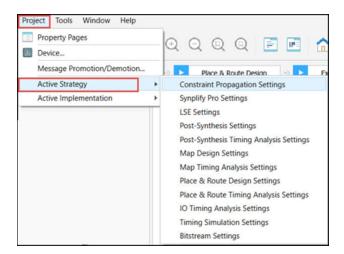

To make a strategy active, right-click the strategy name and choose Set as Active Strategy.

To change the settings in a strategy:

- 1. Double-click the strategy name in the File List view

- 2. Select the option type to modify

- 3. Double-click the Value of the option to be changed

The default values are displayed in plain blue text. Modified values are displayed in italic bold text.

Strategies are design data independent and can be exported and used in multiple projects.

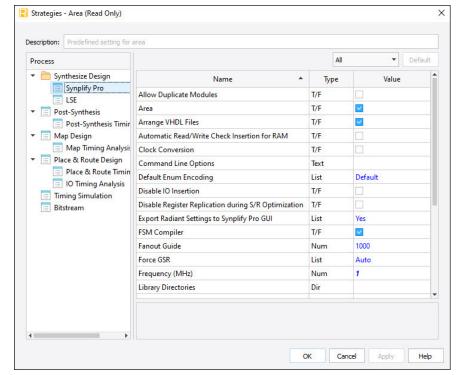

## Area

The Area strategy is a predefined strategy for area optimization. Its purpose is to minimize the total logic gates used while enabling the tight packing option available in Map.

Applying this strategy to large and dense designs might cause difficulties in the place and route process, such as longer time or incomplete routing.

Figure 51: Area Predefined Strategy

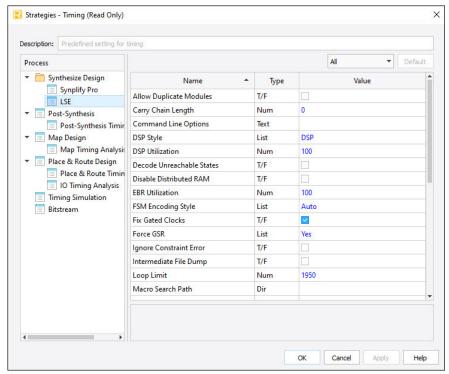

## **Timing**

The Timing strategy is a predefined strategy for timing optimization. Its purpose is to achieve timing closure. The Timing strategy uses a very high effort level in placement and routing. Use this strategy if you are trying to reach the maximum frequency on your design. If you cannot meet your timing requirements with this strategy, you can clone it and create a customized strategy with refined settings for your design. This strategy might increase your place-and-route run time compared to the Area strategy.

Figure 52: Timing Predefined Strategy

## **User-Defined**

You can define your own customized strategy by cloning and modifying any existing strategy. You can start from either a predefined or a customized strategy.

## **Constraint Propagation Options**

This page lists all the strategy options associated with the Constraint Propagation process.

### **Propagation Debug Mode**

Using Propagation Debug Mode can affect timing of other circuits and can lead to false timing reports.

# **Synplify Pro Options**

This page lists all the strategy options associated with the Synplify Pro Synthesis process. For information on their use in Synplify Pro, see the Synopsys Synplify Pro for Lattice Reference Manual.

## Allow Duplicate Modules (for Symplify Pro)

Allows the use of duplicate modules in your design.

When it is set to True, the last definition of the module is used by the software and any previous definitions are ignored. The default is False.

## Area (for Synplify Pro)

Specifies optimization preference for area reduction over timing delay reduction.

The True option specifies the area reduction mode. When set to True, this setting overrides the setting in "Frequency (MHz) (for Synplify Pro)" on page 61.

The default is False.

This option is equivalent to the "set\_option -frequency 1" command in Synplify

## Arrange VHDL Files

Allows Symplify Pro to reorder the VHDL source files for synthesis.

The default is True for VHDL or VHDL design entry type projects, and False for other projects. When this is set to False, Synplify Pro will use the file order in the Radiant software File List view.

## **Auto Compile Point**

With Automatic Compile Points, synthesis decides based on existing hierarchy and utilization estimates.

Compile Points minimize the amount of netlist changes resulting from RTL code changes. Compile points create logical boundaries where optimization will not occur. This may sacrifice some design performance for design result predictability. No user intervention is needed aside from enabling the flow.

#### Note:

Auto Compile Point only supports the LAV-AT device.

### Automatic Read/Write Check Insertion for RAM

When this option is set in the strategy, the synthesis tool inserts glue logic around inferred RAM to avoid simulation mismatches caused by indeterminate output values when the read and write addresses are same. By default this option is OFF.

You should design to make sure the read and write addresses are never the same.

### **Clock Conversion**

Controls gated and generated clock conversion.

Values are True and False.

## **Command Line Options (for Synplify Pro)**

Enables additional command line options for the Synplify Pro Synthesis process.

## To enter a command line option:

- 1. In the Strategy dialog box, select **Synplify Pro** in the Process list.

- Double-click the Value column for the Command line Options option.

- 3. Type in the option and its value (if any) in the text box.

- 4. Click Apply.

## For example:

set option -library path c:/source

## **Default Enum Encoding**

(For VHDL designs) Defines how enumerated data types are implemented.

The type of implementation affects the performance and device utilization. Available options are:

- Default Automatically assigns an encoding style based on the number of states:

- Sequential: 0-4 enumerated types

- Onehot: 5-40 enumerated types

- Gray: more than 40 enumerated types

- Gray Only one bit of the state register changes at a time, but because more than one bit can be hot, the value must be decoded to determine the state. For example: 000, 001, 011, 010, 110

- Onehot Only two bits of the state register change (one goes to 0; one goes to 1) and only one of the state registers is hot (driven by a 1) at a time. For example: 0000, 0001, 0010, 0100, 1000

- Sequential More than one bit of the state register can change at a time, but because more than one bit can be hot, the value must be decoded to determine the state. For example: 000, 001, 010, 011, 100

This option is equivalent to the "set\_option -default\_enum\_encoding default | onehot | gray | sequential" command in Synplify Pro.

## Disable IO Insertion (for Synplify Pro)

Controls whether the synthesis tool will add I/O buffers into your design.

If this is set to True, Synplify Pro will not add I/O buffers into your design. If it is set to False (default), the synthesis tool will insert I/O buffers into your design.

This option is equivalent to the "set\_option -disable\_io\_insertion 1 | 0" command in Synplify Pro.

## **Disable Register Replication During S/R Optimization**

(Not applicable for iCE40 UltraPlus): When this option is set in the strategy, the synthesis tool will NOT duplicate the registers while inferring the address pointers for the RAM during Shift-register inference. By default this option is OFF and the tool will duplicate the address pointer registers to get better performance.

## **Export Radiant Software Settings to Synplify Pro GUI**

Controls whether the strategy settings are exported to Synplify Pro during interactive synthesis (opening Synplify Pro through the Tools menu). After opening Synplify Pro, you can change settings in Synplify Pro's interface. This option has no effect with integrated or stand-alone synthesis.

Available options are:

- No − Synplify Pro opens with its own defaults, ignoring the strategy settings.

- Yes (default) Synplify Pro opens with the strategy settings every time. Options set and saved in a previous Synplify Pro session are ignored.

- Only on First Launch Synplify Pro opens with the strategy settings the first time only. After that, Synplify Pro opens with settings saved in a previous session or with its own defaults. After the first time, the strategy settings are ignored.

For more information, refer to the Radiant Software Help. See **User Guides > Implementing the Design > Synthesizing the Design > Interactive Synthesis**.

#### **FDC Constraint Files**

Specifies the Synopsys FPGA Design Constraint (FDC) files. The FDC file contains Synopsys SDC Standard timing constraints, such as create\_clock, set\_input\_delay, and set\_false\_path, along with the non-timing constraints (design constraints), such as define\_attribute, define\_scope\_collection, and define\_io\_standard.

## FSM Compiler (for Synplify Pro)

Enables or disables the FSM Compiler and controls the use of FSM synthesis for state machines.

When Synplify Pro is selected as the synthesis tool, it enables or disables the FSM Compiler and controls the use of FSM synthesis for state machines. When this is set to True (default), the FSM Compiler automatically recognizes and optimizes state machines in the design. The FSM Compiler extracts the state machines as symbolic graphs, and then optimizes them by re-encoding the state representations and generating a better logic optimization starting point for the state machines.

This option is equivalent to the "set\_option -symbolic\_fsm\_compiler 1 | 0" command in Synplify Pro.

#### **Fanout Guide**

Controls fanout during synthesis. When the specified fanout limit is achieved, logic will be duplicated.

The default is 1000.

This option is equivalent to the "set\_option -maxfan <number>" command in Synplify Pro.

## Force GSR (for Synplify Pro)

Forces Global Set/Reset Pin usage.

Available options are:

- False (default) Does not infer Global Set/Reset in your design.

- ▶ Auto Allows the software to decide whether to infer Global Set/Reset in your design.

- True Always infers Global Set/Reset in your design.

This option is equivalent to the "set\_option -force\_gsr auto | yes | no" command in Synplify Pro.

## Frequency (MHz) (for Synplify Pro)

Specifies the global design frequency (in MHz). Nothing in the Value column means "auto" and Synplify Pro will try to maximize the frequency of the clocks.

The setting is ignored when "Area (for Synplify Pro)" on page 58 is set to True.

This option is equivalent to the "set\_option -frequency <number> | auto" command in Synplify Pro.

### **Library Directories**

Specifies all the paths to the directories which contain the Verilog library files to be included in your design for the project.

You can also add custom library files with module definitions for the design in a single file. The names of files read from the library path must match module names. Mismatches result in error messages.

## Number of Critical Paths (for Symplify Pro)

Specifies the number of critical timing paths to be reported in the timing report.

This option is equivalent to the "set\_option -num\_critical\_paths <number>" command in Synplify Pro.

#### **Number of Start/End Points**

Specifies the number of start and end points you want the software to report in the critical path section of the timing report.

This option is equivalent to the "set option -num startend points <number>" command in Synplify Pro.

## **Output Netlist Format (for Synplify Pro)**

Outputs a mapped VHDL netlist for post-synthesis simulation.

Available options are: None (default) and VHDL.

This option is equivalent to the "set\_option -write\_vhdl 1 | 0" command in Synplify Pro.

### Pipelining and Retiming

Enables the pipelining and retiming features to improve design performance.

### Values are:

- None Disables the pipelining and retiming features.

- Pipelining Only (default) Runs the design at a faster frequency by moving registers into the multiplier, creating pipeline stages.

- Pipelining and Retiming When enabled, registers may be moved into combinational logic to improve performance.

This option is equivalent to the "setup option -pipe 1 | 0 -retiming 1 | 0" command in Synplify Pro.

#### **Push Tristates**

When this is set to True, the Synplify Pro compiler pushes tristates through objects such as muxes, registers, latches, buffers, nets, and tristate buffers, and propagates the high impedance state.

The high-impedance states are not pushed through combinational gates such as ANDs or ORs.

The default is False.

This option is equivalent to the "set\_option -compiler\_compatible 1 | 0" command in Synplify Pro.

## Resolve Mixed Drivers (for Symplify Pro)

If a net is driven by a VCC or GND and active drivers, setting this option to True will connect the net to the VCC or GND driver.

This option is equivalent to the "set\_option -resolve\_multiple\_driver 1 | 0" command in Synplify Pro.

## Resource Sharing (for Symplify Pro)

When this is set to True (default), the synthesis tool uses resource sharing techniques to optimize area.

With resource sharing, synthesis uses the same arithmetic operators for mutually exclusive statements; for example, with the branches of a case statement. Conversely, you can improve timing by disabling resource sharing, but at the expense of increased area.

This option is equivalent to the "set option -resource sharing 1 | 0" command in Synplify Pro.

## Resynthesize All

When this is set to True (default), Synplify Pro will resynthesize all portions, modules, or files of the RTL source. When this is set to False, Synplify Pro will synthesize only the updated portions, modules or files of the RTL source since the last run result.

If you run the "Force Run From Start' process, all portions, modules, or files of the RTL source will be resynthesized, regardless of whether this option is set to True or False.

## **Update Compile Point Timing Data**

Determines whether (True) or not (False) changes inside a compile point can cause the compile point (or top-level) containing it to change accordingly.

When this is set to False (default), Synplify Pro keeps the top level module the same, which is desired by incremental flow.

When this is set to True, changes in low level partitions will be propagated to top partitions up to top module. Synplify Pro will possibly optimize timing data and certainly will write a new timestamp onto the partition for the top level module.

This option is equivalent to the "set option -update models cp 1 | 0" command in Synplify Pro.

#### Use Clock Period for Unconstrained I/O

Controls whether to forward annotate constraints for I/O ports without explicit user-defined constraints.

When this is set to True, only explicit I/O port constraints are forward annotated. When it is set to False (the default), all I/O port constraints are forward annotated.

This option is equivalent to the "set option -auto constraint io 1 | 0" command in Synplify Pro.

## VHDL 2008 (for Synplify Pro)

When this is set to True, VHDL 2008 is selected as the VHDL standard for the project.

## **LSE Options**

This page lists all the strategy options associated with the LSE synthesis process.

## Allow Duplicate Modules (for LSE)

When set to True, allows the design to keep duplicate modules. LSE issues a warning and uses the last definition of the module. Any previous definitions are ignored. The default is False, which causes an error if there are duplicate modules.

## Allow Mixed Assignments (for LSE)

When set to True, having both blocking and non-blocking assignments to the same variable will be allowed. A warning will be issued instead of an error.

### **Carry Chain Length**

Specifies the maximum number of carry chain cells (CCUs) that get mapped to a single carry chain. Default is 0, which is interpreted as infinite length.

This option is equivalent to the "-carry\_chain\_length" option in the SYNTHESIS command.

This option is equivalent to the "-allow duplicate modules" option in the SYNTHESIS command.

## **Command Line Options (for LSE)**

Enables additional command line options for the LSE Synthesis process.

### To enter a command line option:

- 1. In the Strategy dialog box, select LSE in the Process list.

- 2. Double-click the Value column for the Command line Options option.

- 3. Type in the option and its value (if any) in the text box.

- 4. Click Apply.

For detailed description on LSE command line options, refer to the Radiant Software Help. See Reference Guides > Command Line Reference Guide

## > Command Line Tool Usage > Running SYNTHESIS from the Command Line.

## **DSP Style**

Specifies how DSP modules should be implemented: with DSP resources or with Logic (LUTs).

This option is equivalent to the "-use dsp" option in the SYNTHESIS command.

#### **DSP Utilization**

Specifies the percentage of DSP sites that LSE should try to use.

This option is equivalent to the "-dsp\_utilization" option in the SYNTHESIS command.

### **Decode Unreachable States**

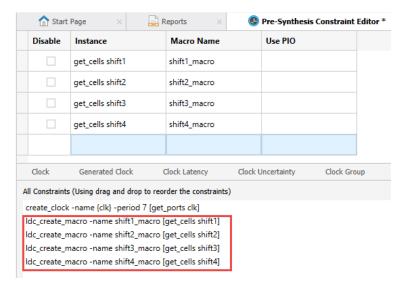

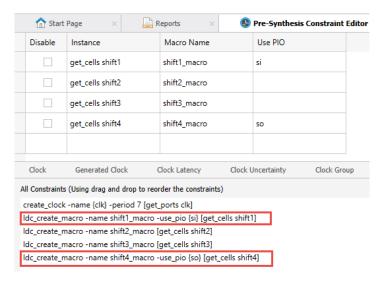

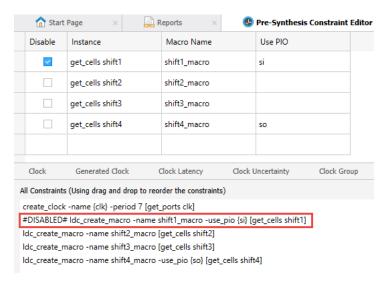

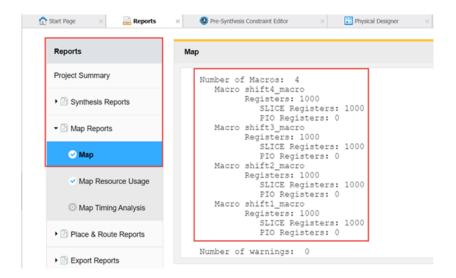

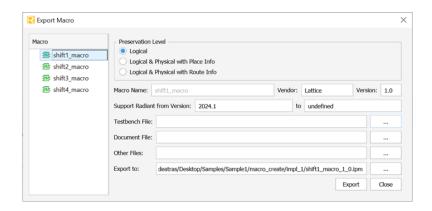

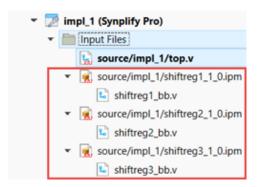

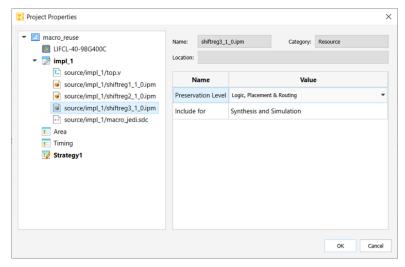

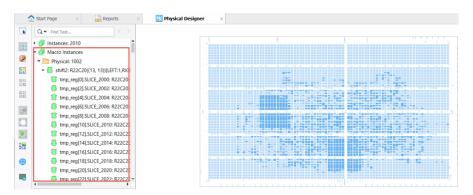

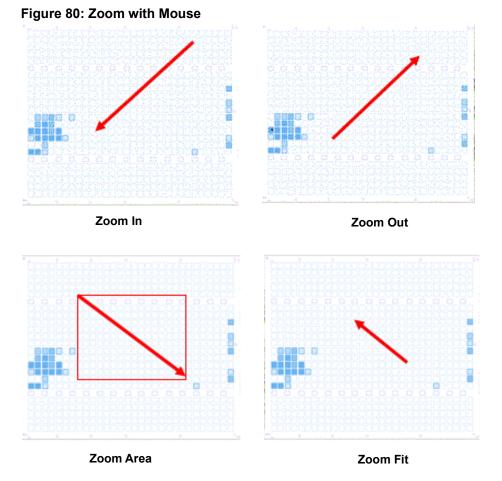

When set to True, synthesis infers safe recovery logic from unreachable states in all the state machines of the design.