# **Revision Control – Lattice Propel Builder 2025.2**

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                                                                                    | 3  |

|-------------------------------------------------------------------------------------------------------------|----|

| Abbreviations in This Document                                                                              | 4  |

| 1. Introduction                                                                                             | 5  |

| 2. Recommended Revision Control Systems                                                                     | 5  |

| 3. Lattice Propel Revision Control Strategies                                                               | 6  |

| 3.1. Lattice Propel Project Directory Structure                                                             |    |

| 3.2. Lattice Propel File Types                                                                              | 7  |

| 3.3. Files Committed to Lattice Propel Revision Control Strategies                                          |    |

| 4. Lattice Propel Revision Control Workflows                                                                |    |

| 4.1. Lattice Propel Revision Control Normal Workflow                                                        | 9  |

| 4.2. Multiple Developers Working on the Same File Workflow                                                  |    |

| 4.3. Multiple Developers Adding Files Workflow                                                              |    |

| 5. Reproduce SoC Design Using TCL Script                                                                    |    |

| 5.1. Generate TCL Script for Existing SoC Design                                                            |    |

| 5.2. Reproduce SoC Design                                                                                   |    |

| 6. References                                                                                               |    |

| Technical Support Assistance                                                                                |    |

| Revision History                                                                                            | 24 |

| Figures                                                                                                     |    |

| Figure 3.1. Source Files                                                                                    | 6  |

| Figure 3.2. Verification-related Files                                                                      | 7  |

| Figure 3.3. Verification-related Files for an Extra C/C++ Project                                           |    |

| Figure 3.4. Files Committed for Lattice Propel Revision Control Strategies                                  |    |

| Figure 3.5. Files Committed for Lattice Propel Revision Control Strategies                                  |    |

| Figure 4.1. Lattice Propel Revision Control Normal Workflow                                                 |    |

| Figure 4.2. Multiple Developers Working on the Same File Workflow                                           |    |

| Figure 4.3. Multiple Developers Adding Files Workflow                                                       |    |

| Figure 5.1. Generate TCL Script for Existing System                                                         |    |

| Figure 5.2. IP Catalog View                                                                                 |    |

| Figure 5.3. IP Catalog List Command                                                                         |    |

| Figure 5.4. Launch TCL Script to Create New Project                                                         |    |

| Figure 5.5. SoC Design View                                                                                 |    |

| Figure 5.6. Relayout Option                                                                                 |    |

| Figure 5.7. Constraint File in Source Project Figure 5.8. Rename Constraint File Copied from Source Project |    |

| Figure 5.8. Rename Constraint File Copied from Source Project<br>Figure 5.9. Radiant TCL Console            |    |

| Figure 5.9. Radiant TCL Console                                                                             |    |

| Figure 5.11. Top.v File in Source Project                                                                   |    |

| Figure 5.11. Top.v File in Source Project                                                                   |    |

| Figure 5.13. Updated Top File in New Project                                                                |    |

| Figure 5.14. Constraint File in Source Project                                                              |    |

| Figure 5.15. Rename Constraint File Copied from Source Project                                              |    |

| Figure 5.16. Diamond TCL Console                                                                            |    |

| Figure 5.17. Other Resources in Source Project                                                              | 21 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                                 |

|--------------|------------------------------------------------------------|

| FPGA         | Field Programmable Gate Array                              |

| GIT          | An open-source distributed version control system          |

| GUI          | Graphical User Interface                                   |

| IP           | Intellectual Property                                      |

| SoC          | System on Chip                                             |

| SVN          | Subversion software, an open source version control system |

| TCL          | Tool Command Language                                      |

### 1. Introduction

This user guide introduces how to use revision control for Lattice Propel<sup>™</sup> projects. Lattice Propel design environment supports revision control for your projects. You can access the revision control system to get all the change logs and switch to previous milestones if necessary. Using revision control for Lattice Propel projects, the compile time can be reduced. Compilation only starts when inputs are changed.

# 2. Recommended Revision Control Systems

The following revision control systems are recommended to be used with Lattice Propel software:

- GIT

- GIT is an open-source distributed version control system.

- SVN

- Subversion Software is an open-source version control system.

- Perforce

- Perforce is a centralized version control system.

## 3. Lattice Propel Revision Control Strategies

The Lattice Propel design environment is friendly to revision control systems. There are many revision control systems available. You do not need to consider version compatibility. The Lattice Propel design environment does not directly integrate specific revision control into it. You can select different revision control systems to work with the Lattice Propel design environment.

Only the necessary files that constitute the project are managed by the revision control system. Other files, including some intermediate files and your configuration files, are only used in your own project and are not submitted to the version control system.

#### 3.1. Lattice Propel Project Directory Structure

In the Lattice Propel design environment, it is recommended that all source codes and IP designs be placed under the same disk partition instead of being used across partitions.

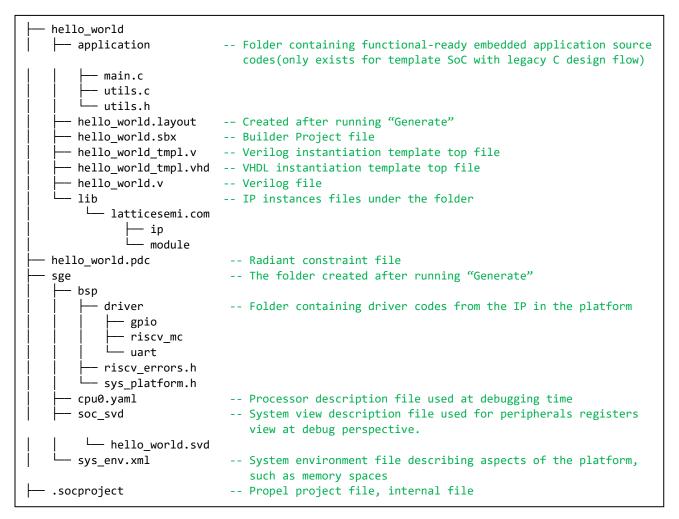

Lattice Propel projects use one directory to put all source and project files. After creating a project, the directory structure of the project is shown in Figure 3.1 and Figure 3.2.

All source files are stored in the folder named as the project name, such as the hello\_world folder shown in Figure 3.1.

Figure 3.1. Source Files

If the Propel project has a verification design, all related files are placed in a verification directory, as shown in Figure 3.2.

Figure 3.2. Verification-related Files

If there is an extra C/C++ project, all typical files are shown in Figure 3.3.

```

riscv xx helloworld

settings

-- C/C++ project setting

- Debug

-- Project building output files

- Release

-- Project building output files

-- Source files including c, head and link files

- src

-- SoC drive files

- bsp

-- C/C++ project main file

main.c

platform init.h

-- C/C++ project head file

-- C/C++ project file

.cproject

.project

-- Project file (link C and SoC project)

- riscv nano helloworld.launch -- C/C++ project launch file

```

Figure 3.3. Verification-related Files for an Extra C/C++ Project

#### 3.2. Lattice Propel File Types

The project and constraint file types under a Lattice Propel project directory include:

- .socproject file: Propel project file, internal file

- .pdc file: Radiant constraint file

- .rdf file: Radiant project file

- .lpf file: Diamond constraint file

- .ldf file: Diamond project file

- .sty file: Diamond/Radiant strategy file

The basic source or design file types include:

- .v file: Verilog file

- .vhd file: VHDL file

- .sv file: System Verilog file

- .sbx file: Builder Project file

#### 3.3. Files Committed to Lattice Propel Revision Control Strategies

The following files are committed to revision control strategies of the Lattice Propel design environment:

- The .socproject project file and .pdc/.lpf constraint file

- All the source files under the directory named project name

- Verification directory files

- All files under the C/C++ project except the Debug and Release folder

8

For an SoC project named hello\_world, the files committed are shown in Figure 3.4.

Figure 3.4. Files Committed for Lattice Propel Revision Control Strategies

For a C/C++ project named riscv\_nano\_helloworld, the files committed are shown in Figure 3.5.

```

(Propel C/C++ Project)

── .settings

── src

── .cproject

── .project

── riscv_nano_helloworld.launch

```

Figure 3.5. Files Committed for Lattice Propel Revision Control Strategies

## 4. Lattice Propel Revision Control Workflows

The Lattice Propel revision control workflows are presented in the following sections.

#### 4.1. Lattice Propel Revision Control Normal Workflow

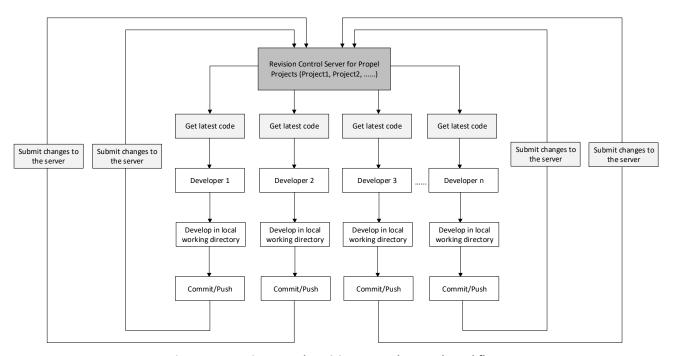

Each developer has a working directory. You can get the latest code from the Lattice Propel version server and develop in your own development environment. Later, you can submit the modified code or new design to the Propel version server if needed.

Figure 4.1. Lattice Propel Revision Control Normal Workflow

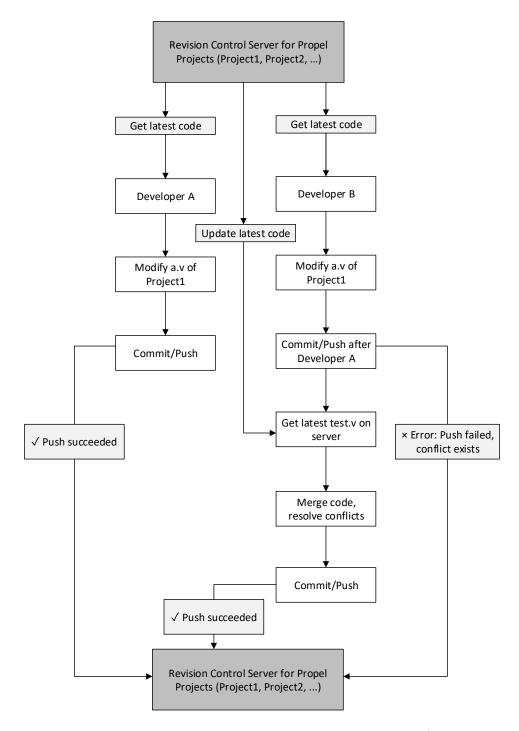

## 4.2. Multiple Developers Working on the Same File Workflow

Most of the time, developers have their own code changes, and may modify the same source file or design. If developer A submits a file and developer B has updated the file, then developer A gets an error. At this time, developer A needs to update the latest code locally from the server, integrate it with his own modifications, and submit it again. This is the collaborative operation of multiple developers for revision control.

Figure 4.2. Multiple Developers Working on the Same File Workflow

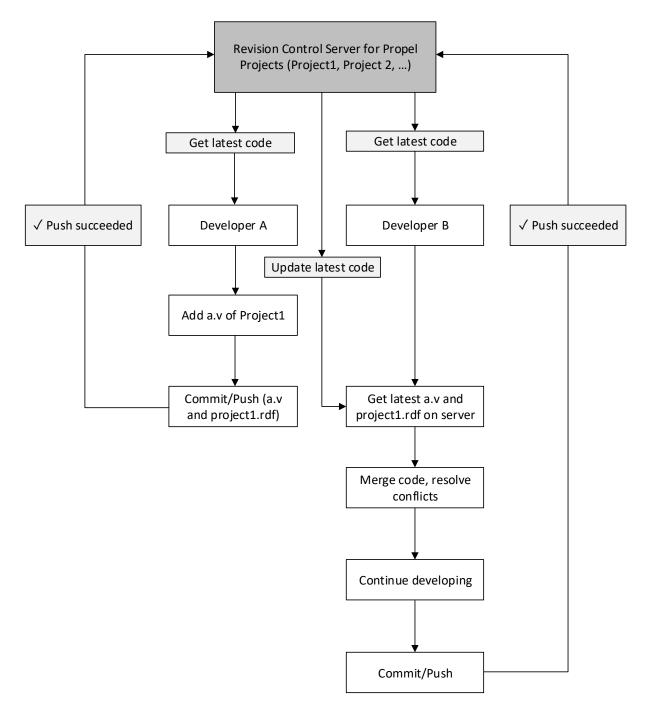

## 4.3. Multiple Developers Adding Files Workflow

Developer A may add a new file a.v to the design, submitting this file and the Propel project file to the revision control server. After that, Developer B can get the latest code from the server, merge the local code, resolve the conflict, and continue the subsequent development.

Figure 4.3. Multiple Developers Adding Files Workflow

# 5. Reproduce SoC Design Using TCL Script

You can generate a TCL script from the current SoC project, and then set up a new project by launching this TCL script in the new environment.

Any Propel Builder project can be exported as a TCL script. The generated TCL script contains the required TCL commands to recreate the SoC design from scratch, generate all of its IP, and make the required interface and port connections. This script can be used to create a new project from its source project entirely from scratch.

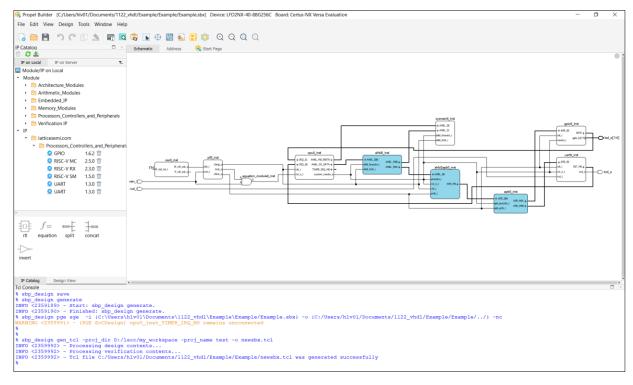

#### 5.1. Generate TCL Script for Existing SoC Design

To generate the TCL script:

- 1. In Lattice Propel Builder, save the current SoC project by clicking the icon.

- 2. Type the following command in the TCL console with corresponding options:

sbp\_design gen\_tcl -proj\_dir cproject directory> -proj\_name cproject name>

[-propel\_dir cpropel directory>] [-o <output name of the generated script>]

An example is given below:

sbp\_design gen\_tcl -proj\_dir D:/lscc/my\_workspace -proj\_name test -o newsbx.tcl

The output of this command shows the location of the TCL script, as shown in the following example (Figure 5.1):

Tcl file C:/lscc/workspace/Example/Example/newsbx.tcl was generated successfully.

Figure 5.1. Generate TCL Script for Existing System

#### 5.2. Reproduce SoC Design

You can use the TCL script generated for the existing SoC project to reproduce a new SoC project.

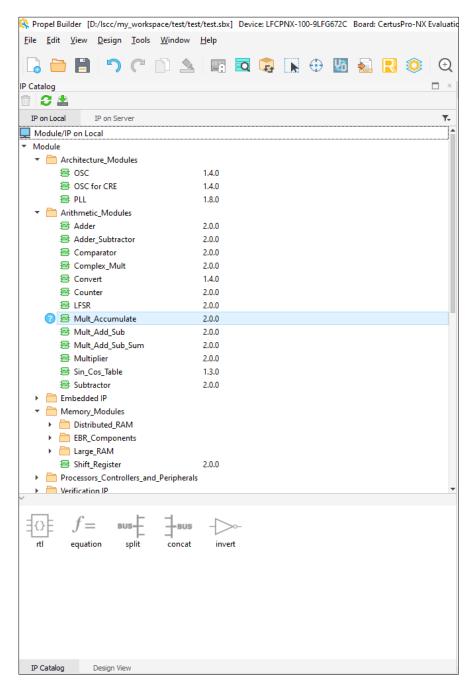

1. Before launching this TCL script in a new environment, make sure all the IPs mentioned in the script are installed in the new environment. Both name and version of the IPs should match.

You can check all IPs from the IP Catalog view (Figure 5.2).

Figure 5.2. IP Catalog View

Or you can check all IPs by typing the following command in TCL console (Figure 5.3): ip\_catalog\_list

Figure 5.3. IP Catalog List Command

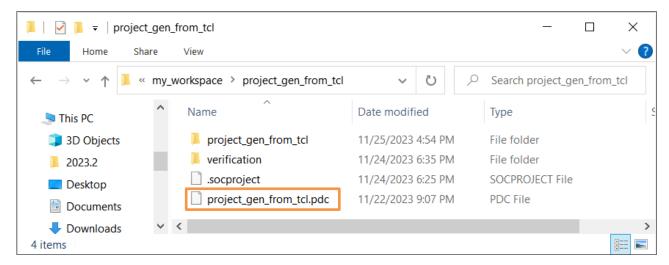

- 3. Fetch the TCL script and if needed, change corresponding settings in the script to use in the new environment:

- targetDir: The new project directory. Make sure this directory already exists before launching TCL.

- projectName: Project name.

- propelRegenLsccBase: The Propel installation path. Make sure this directory exists.

**Note:** If there is any file configuration in the sbp\_config\_ip command, update the file path to the correct path on local setup. For example, update INIT\_FILE in the System Memory IP.

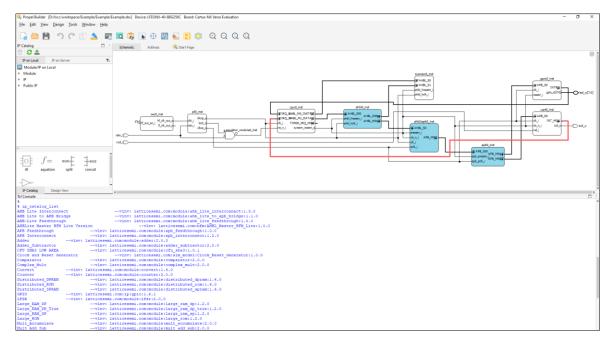

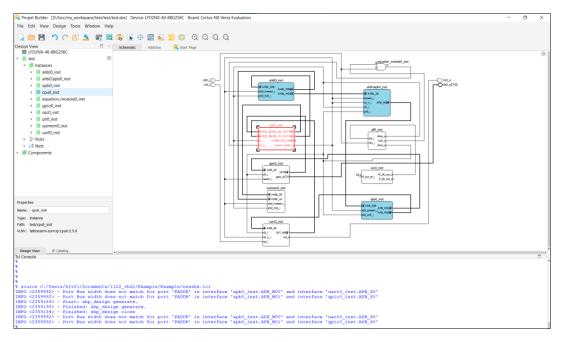

4. To launch this TCL script to create a new project, make sure no design is currently open in Lattice Propel Builder. Type source <tcl\_path> in the TCL console, as shown in the example below (Figure 5.4):

source D:/lscc/workspace/Example/Example/newsbx.tcl

Figure 5.4. Launch TCL Script to Create New Project

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

5. Now you can click the 💹 icon from Propel Builder toolbar to switch back to SoC Design project.

Figure 5.5. SoC Design View

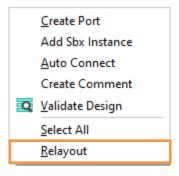

(Optional) Right-click on the Schematic view and select Relayout, if the new design is out of proportion (Figure 5.6).

Figure 5.6. Relayout Option

7. Some files need to be added/modified to fully reproducing the original SoC design.

#### For devices supported in Lattice Radiant software:

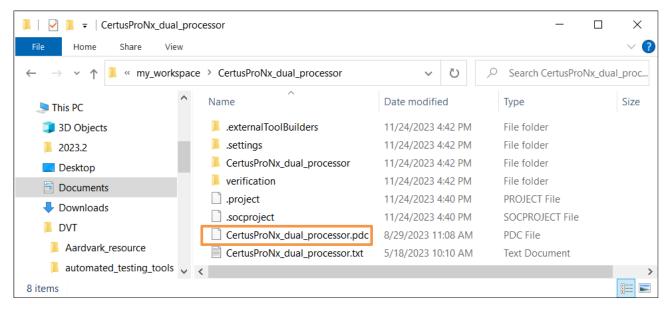

If the SoC is on board level, copy the Lattice Radiant constraint file from the source project (Figure 5.7).

The path is <workspace>/<project\_dir>/<project\_name>.pdc.

Figure 5.7. Constraint File in Source Project

b. Rename the copied constraint file with the new project name, as shown in Figure 5.8.

Figure 5.8. Rename Constraint File Copied from Source Project

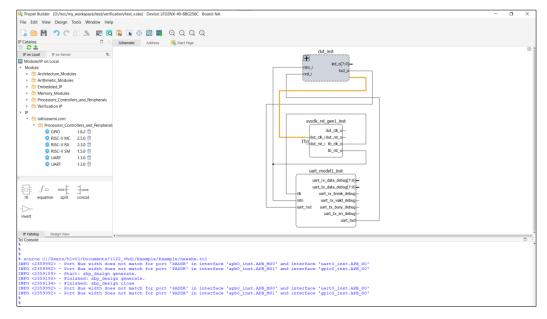

- c. Open Lattice Radiant software by clicking on the circum icon on Propel Builder GUI toolbar.

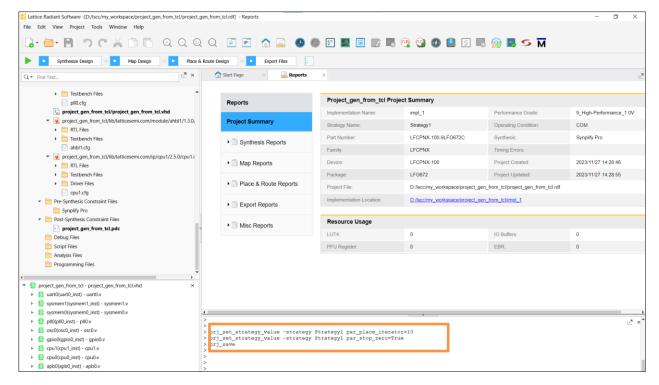

- d. Type the following commands in the Radiant TCL console (Figure 5.9).

prj\_set\_strategy\_value -strategy Strategy1 par\_place\_iterator=10

prj\_set\_strategy\_value -strategy Strategy1 par\_stop\_zero=True

prj\_save

Figure 5.9. Radiant TCL Console

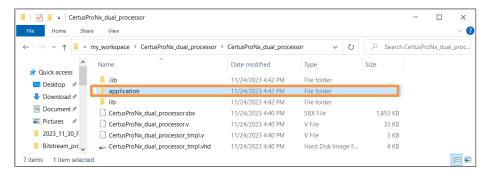

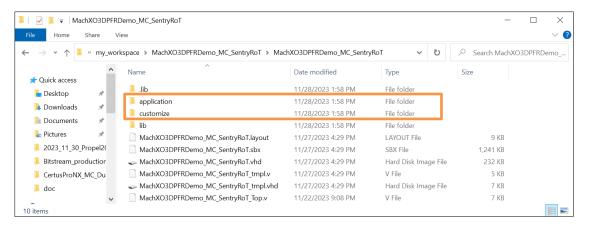

e. For some templates, there is an application folder inside the project directory (Figure 5.10). This folder is used for creating C project in Propel SDK. Copy it from the source project.

The path is <workspace>/<project\_dir>/<project\_name>/application.

Figure 5.10. Application Folder in Source Project

f. Edit the .socproject file to add the ConstraintFile and AddResources entries if there is an application folder in step e, as shown in the example below.

The file path is <workspace>/<project dir>/.socproject.

#### For devices supported in Lattice Diamond software:

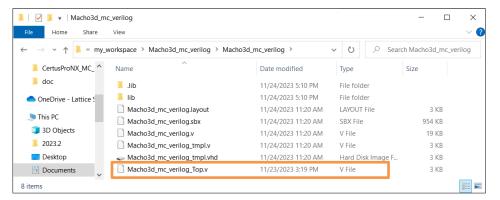

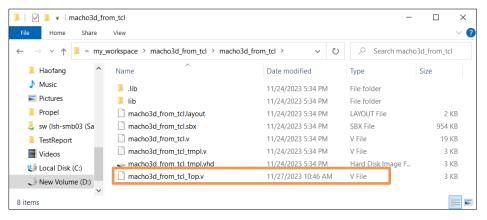

a. Copy top.v from the source project, which is used for the Diamond flow (Figure 5.11). The file path is <workspace>/<project\_dir>/<project\_name>/<project\_name>\_Top.v.

Figure 5.11. Top.v File in Source Project

Rename the file to <new project name> Top.v (Figure 5.12).

Figure 5.12. Rename Top File Copied from Source Project

c. Edit contents of the file, replacing the project name with the new one (Figure 5.13).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

```

module HelloWorld Top (

input rstn_i,

input rxd_i,

output txd_o,

inout [7:0] led_o

);

GSR GSR_INST(.GSR(rstn_i));

wire sys_clk /*synthesis syn_keep = 1*/;

wire esb_oscclk;

OSCJ #(.Nom_FReQ("38.0")) OSCJ (.STDBY(1"b0), .OSC(sys_clk), .SEDSTDBY(),.OSCESB(esb_oscclk));

test macho3d mc tcl HelloWorld_inst (

.clk_i(sys_clk),

.rstn_i(rstn_i),

.rxd_i(rxd_i),

.txd_o(txd_o),

.gpio_io(led_o)

);

endmodule

```

Figure 5.13. Updated Top File in New Project

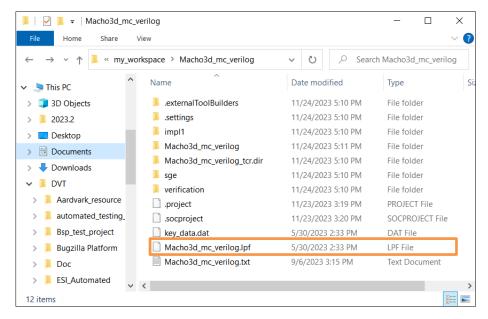

d. For board level SoC project, copy the Diamond constraint .lpf file from the source project (Figure 5.14). The path is <workspace>/<project\_dir>/<project\_name>.lpf.

Figure 5.14. Constraint File in Source Project

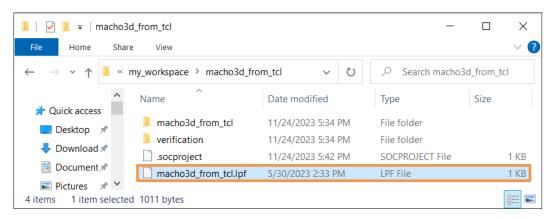

e. Rename the file with new project name (Figure 5.15).

Figure 5.15. Rename Constraint File Copied from Source Project

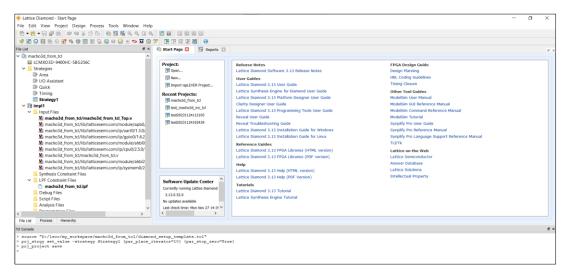

f. Open Lattice Diamond software by clicking on the icon in Propel Builder GUI toolbar. Type the following command in the Diamond TCL console (Figure 5.16):

```

prj_strgy set_value -strategy Strategy1 {par_place_iterator=10}

{par_stop_zero=True}

prj_project save

```

Figure 5.16. Diamond TCL Console

g. Check <workspace>/<project\_dir>/<project\_name> directory. If there are any other resource, copy them into the same directory under the new project without modification (Figure 5.17).

Figure 5.17. Other Resources in Source Project

h. Edit the .socproject file to add the ConstraintFile entry. If there are other resources in step g, add them to the AddResources entry, as shown in the example below.

The file path is <workspace>/<project\_dir>/.socproject.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 6. References

- Lattice Propel 2025.2 SDK User Guide (FPGA-UG-02244)

- Lattice Propel 2025.2 Builder User Guide (FPGA-UG-02243)

- Lattice IP Packager 2025.2 User Guide (FPGA-UG-02242)

- Lattice Propel 2025.2 Installation for Windows User Guide (FPGA-AN-02106)

- Lattice Propel 2025.2 Installation for Linux User Guide (FPGA-AN-02105)

#### For more information, refer to:

- Lattice Propel software web page

- Lattice Insights for training series and learning plans

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

For frequently asked questions, refer to the Lattice Answer Database at www.latticesemi.com/Support/AnswerDatabase.

# **Revision History**

#### Revision 1.0, December 2025

| Section | Change Summary      |

|---------|---------------------|

| All     | Production release. |

www.latticesemi.com