# **Lattice Propel 2025.2 Builder**

## **User Guide**

FPGA-UG-02243-1.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| 20 | intents   |                                                                      | 3   |

|----|-----------|----------------------------------------------------------------------|-----|

| ٩b | breviatio | ns in This Document                                                  | 10  |

| L. | Introd    | uction                                                               | 11  |

|    | 1.1. F    | Purpose                                                              | 11  |

|    | 1.2. A    | Audience                                                             | 11  |

| 2. | Lattice   | Propel Builder Design                                                | 12  |

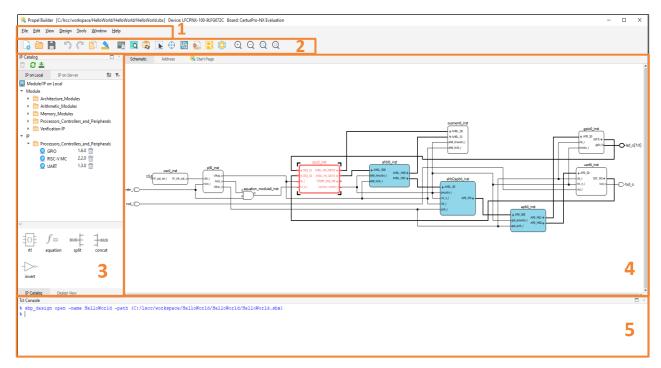

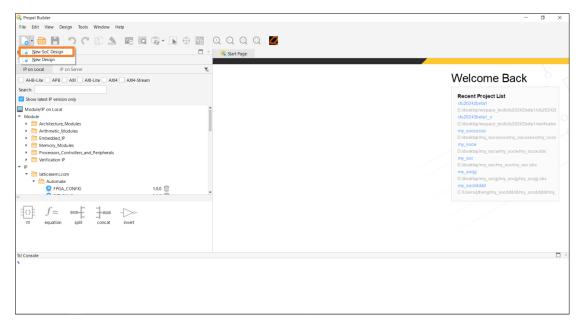

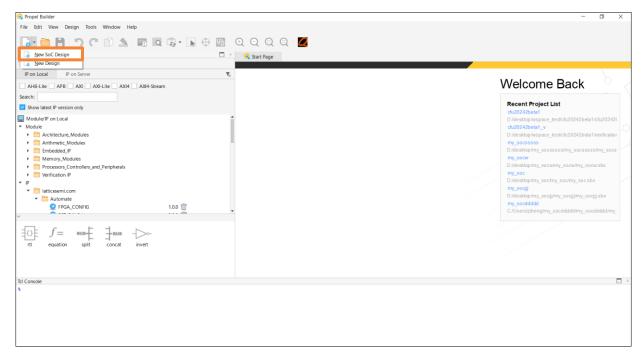

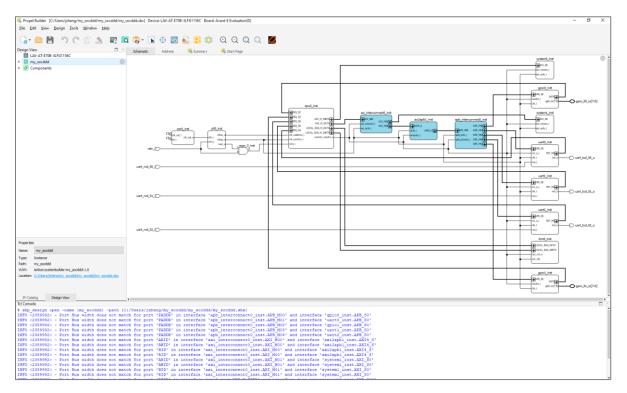

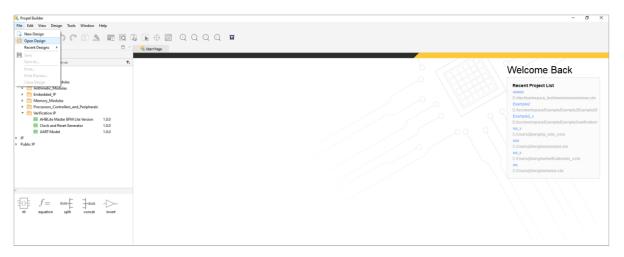

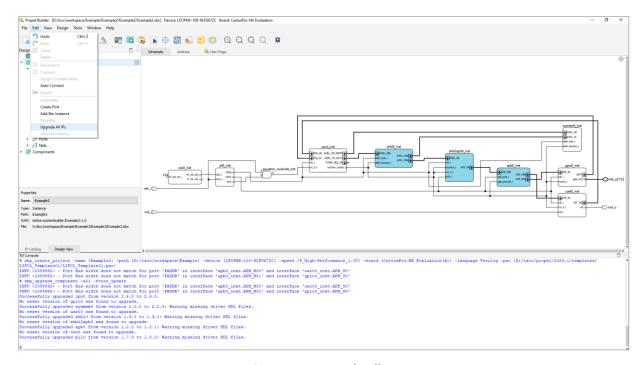

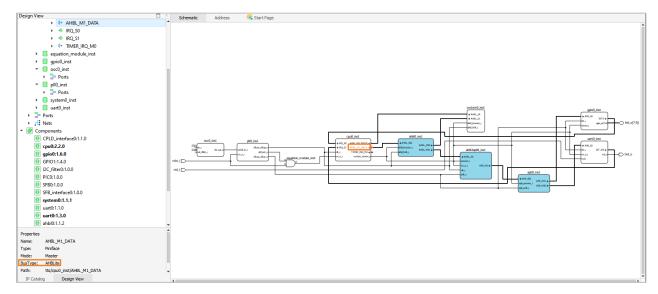

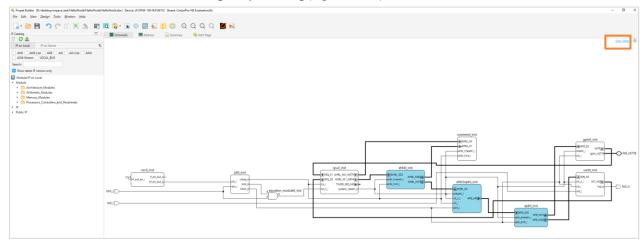

|    | 2.1. E    | Builder Environment                                                  | 12  |

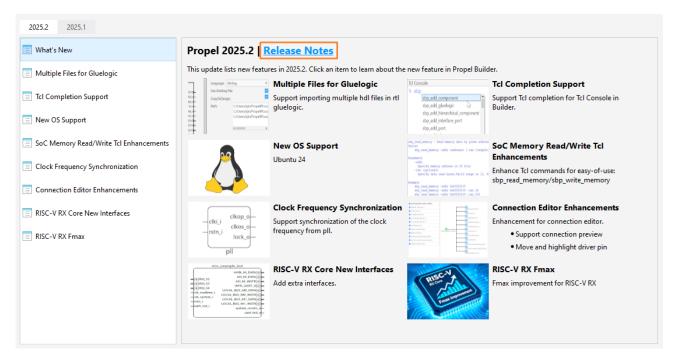

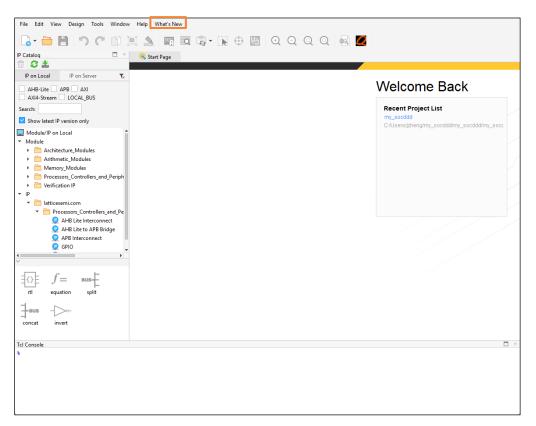

|    | 2.2.      | Check Out What's New                                                 | 13  |

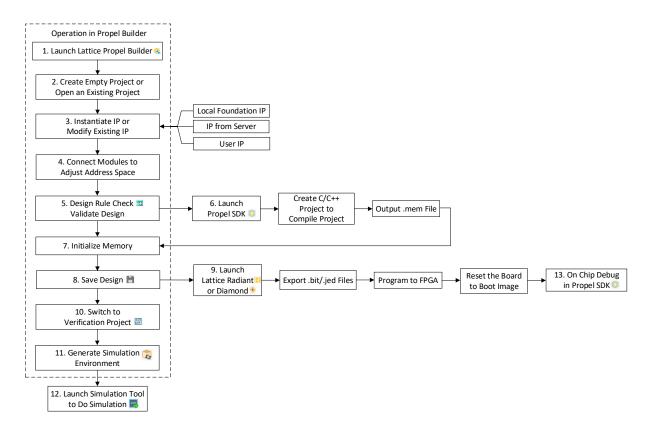

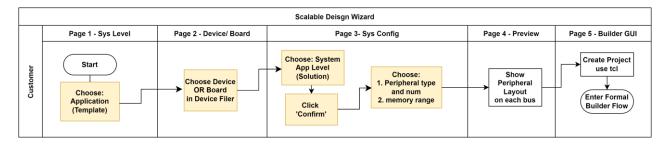

|    | 2.3. F    | Project Design Flow                                                  | 15  |

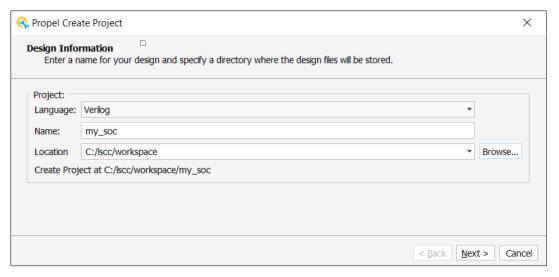

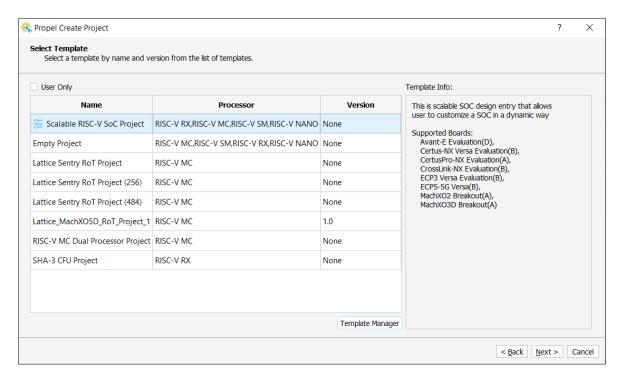

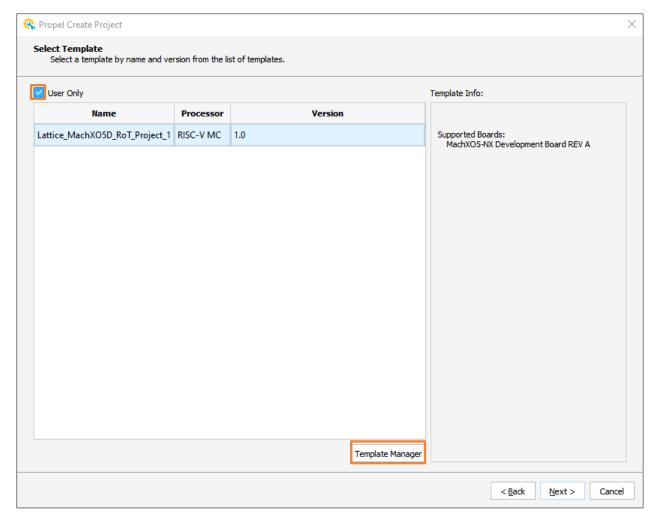

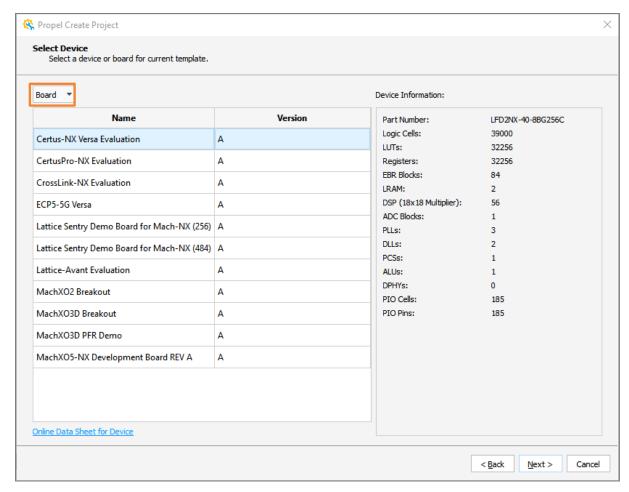

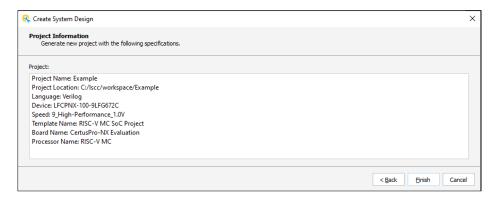

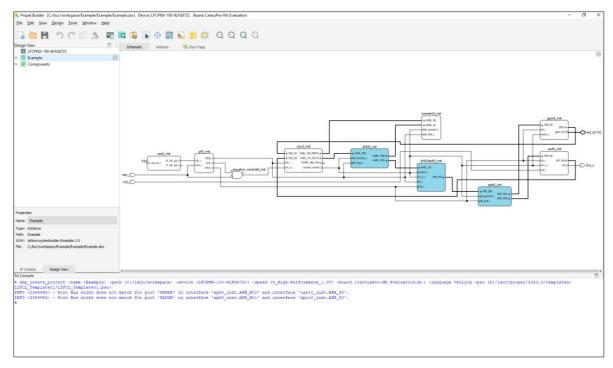

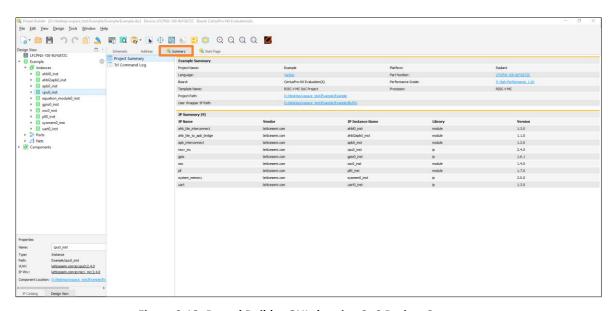

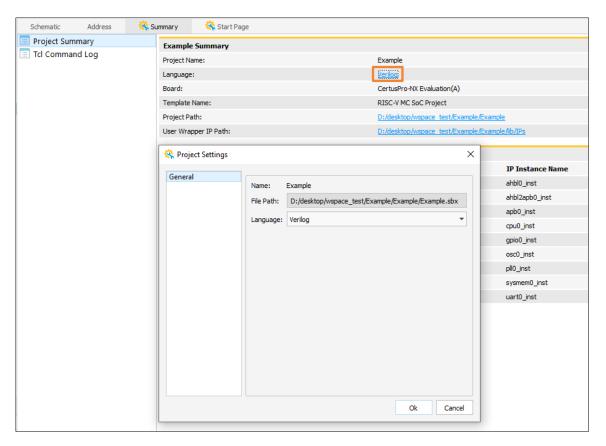

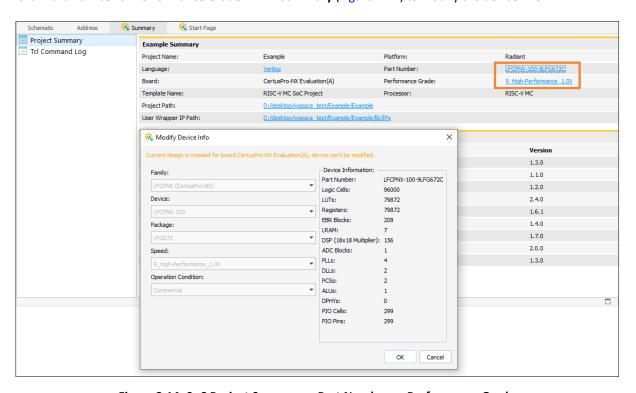

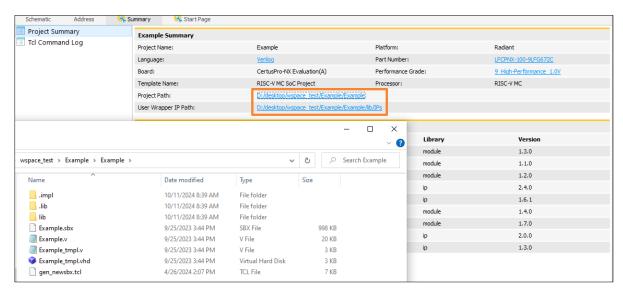

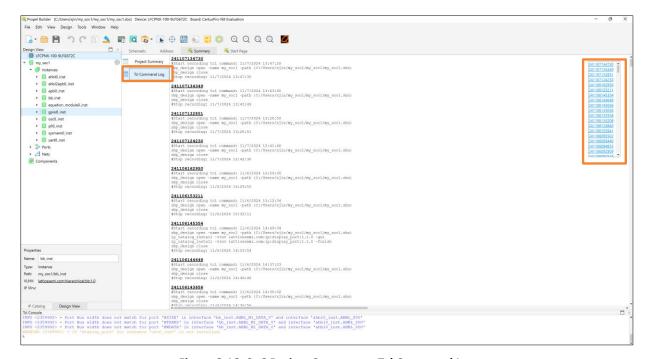

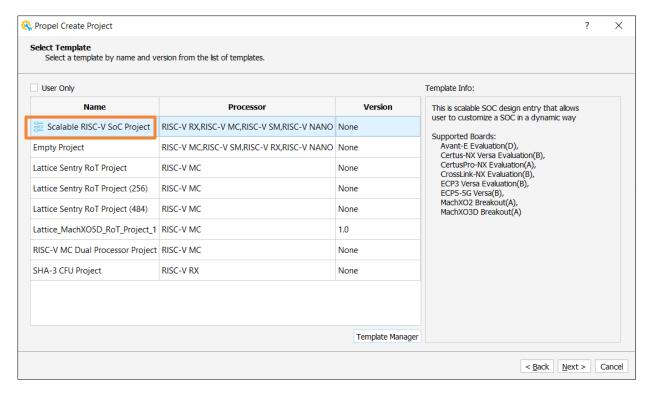

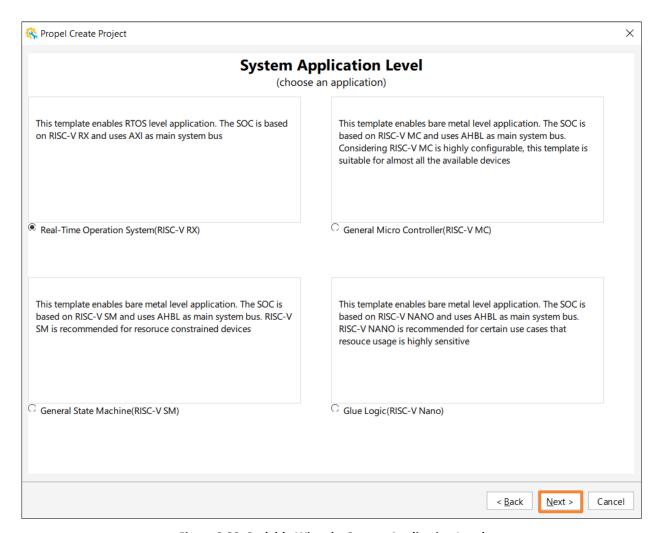

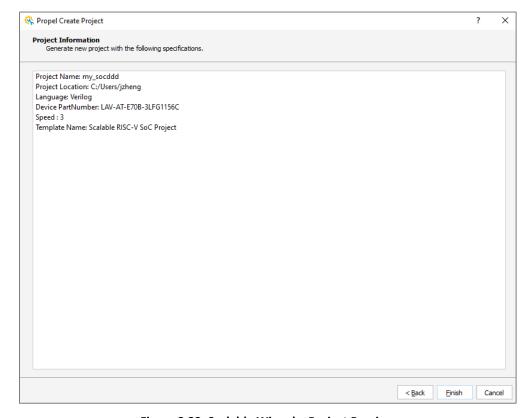

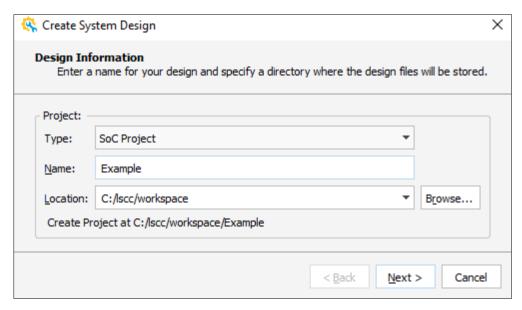

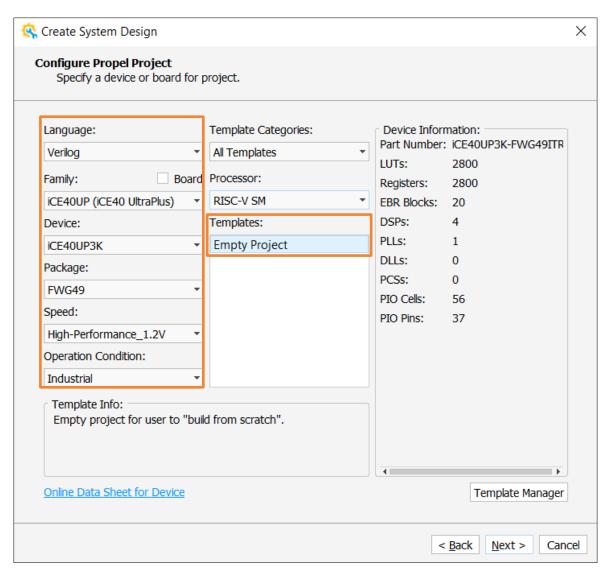

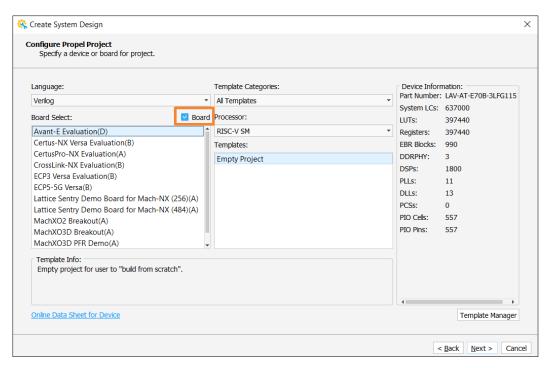

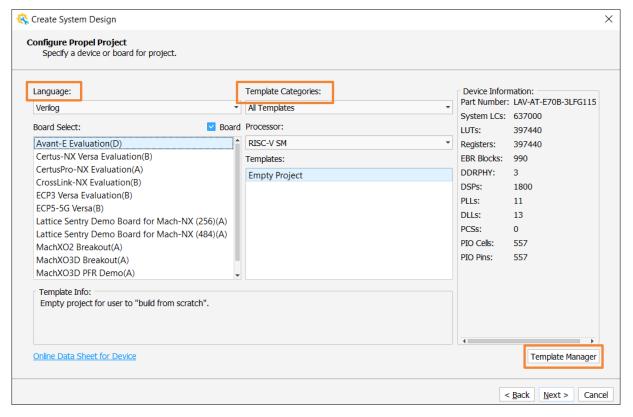

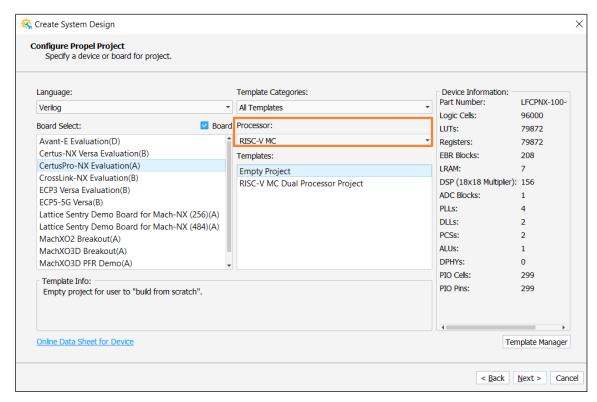

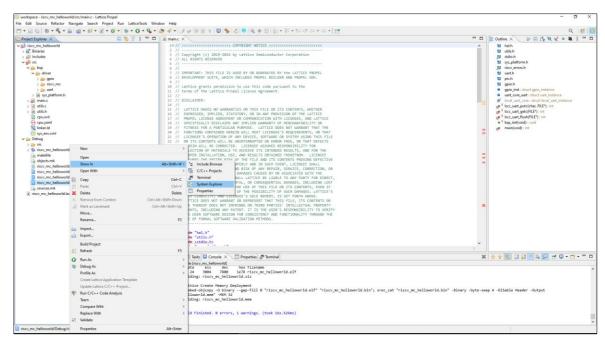

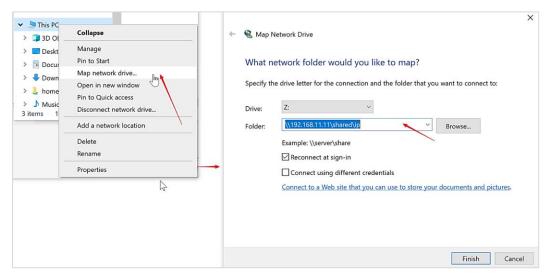

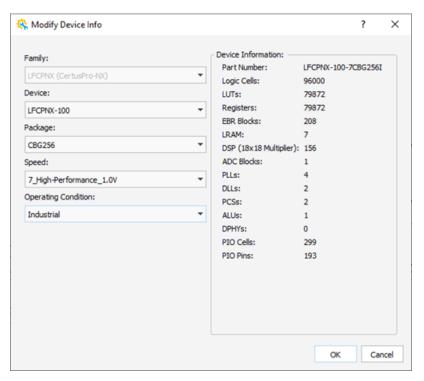

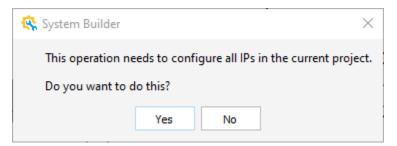

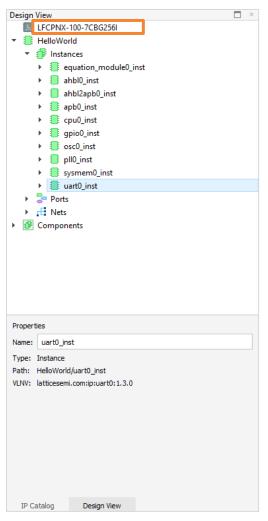

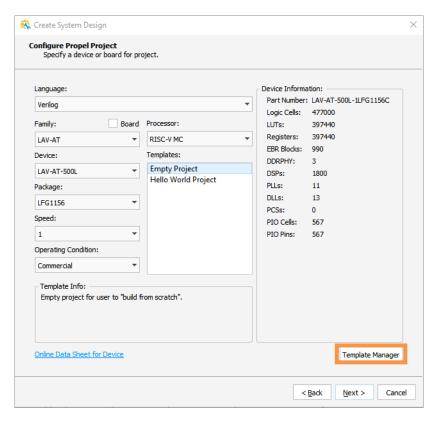

|    | 2.3.1.    | Creating SoC Project                                                 | 15  |

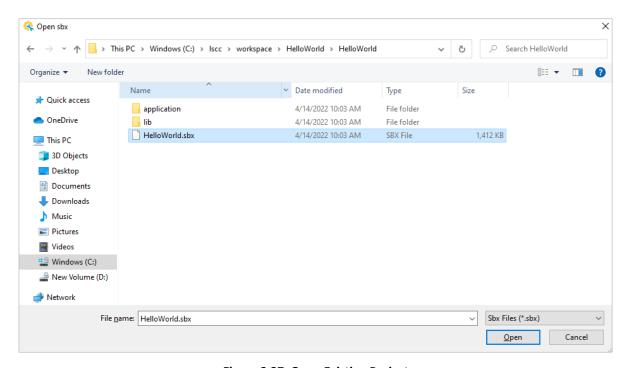

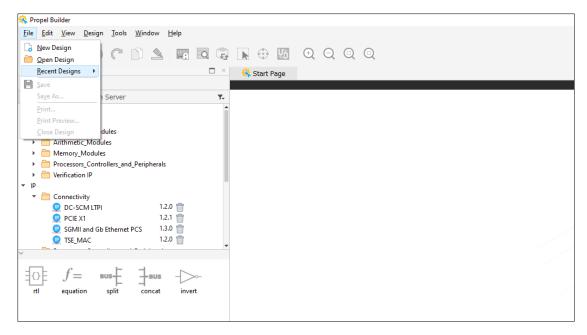

|    | 2.3.2.    | Opening an Existing SoC Project                                      | 34  |

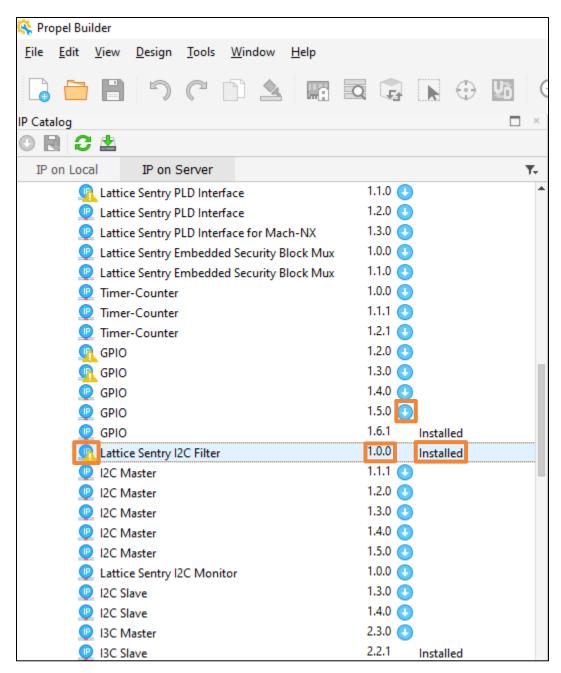

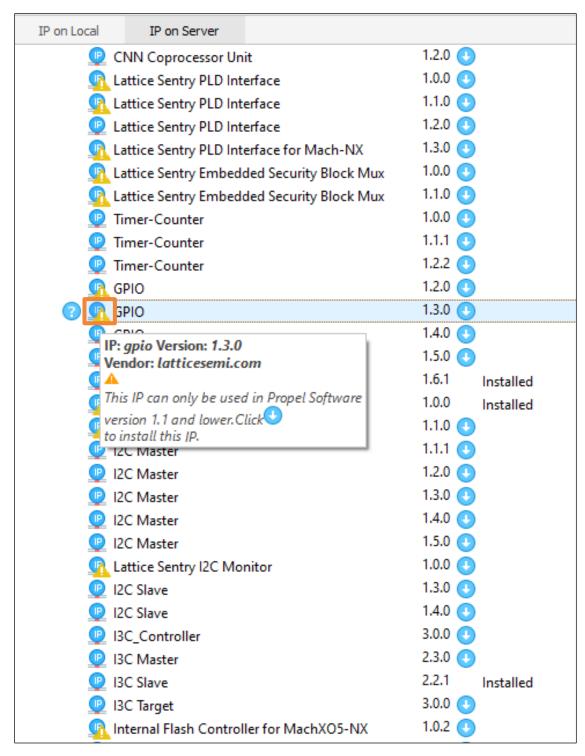

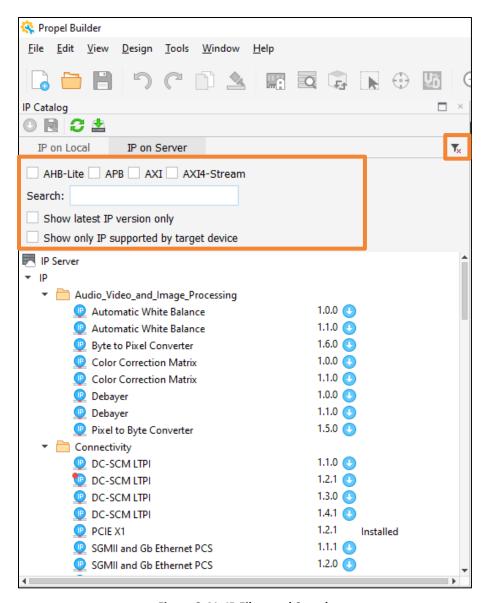

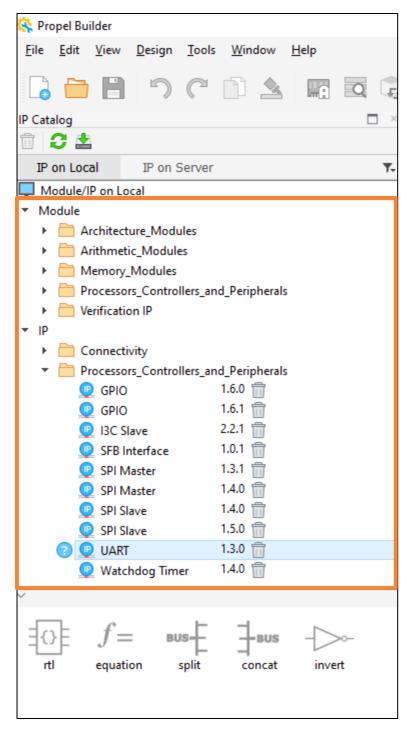

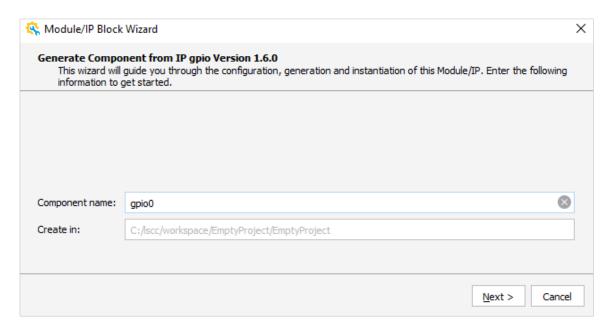

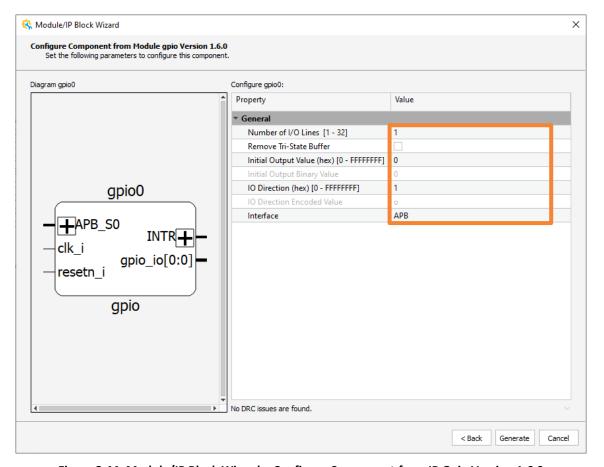

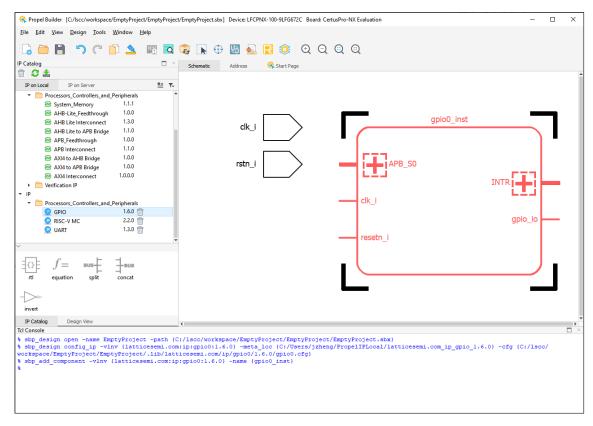

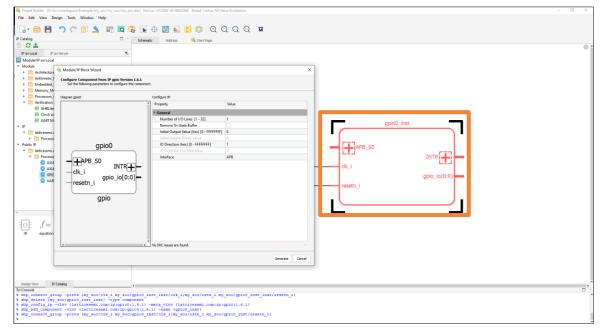

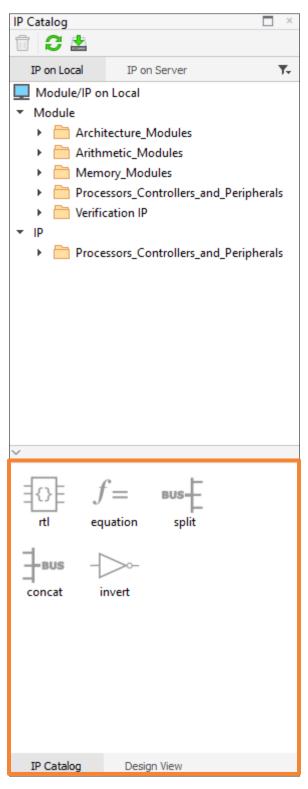

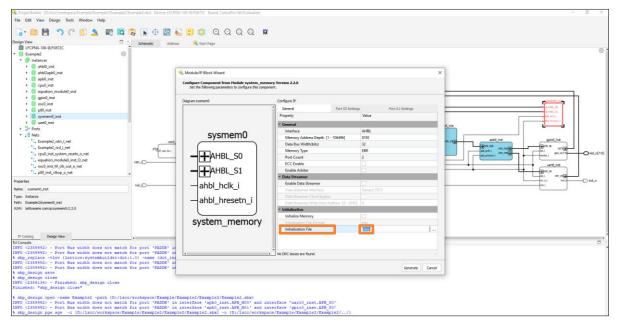

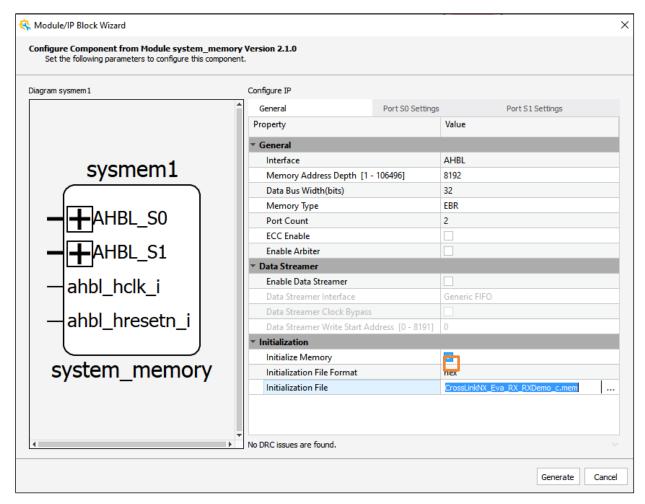

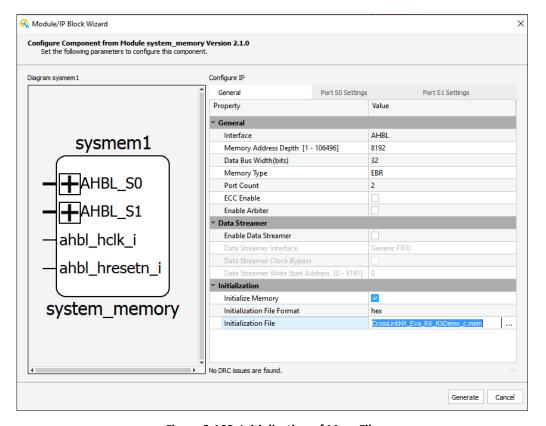

|    | 2.3.3.    | Generating and Instantiating IP/Module                               | 36  |

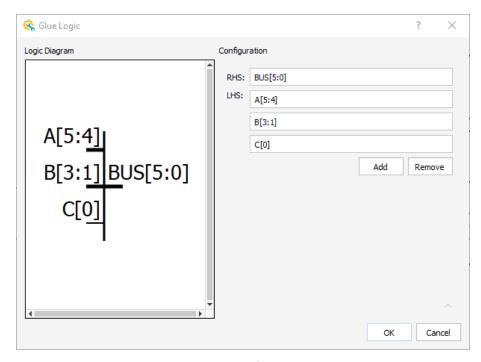

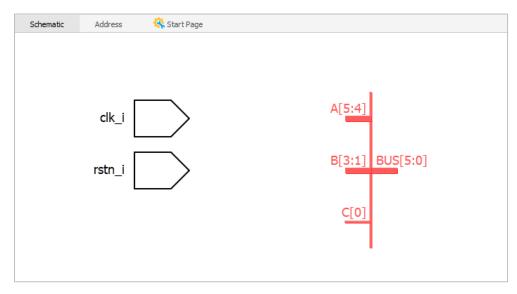

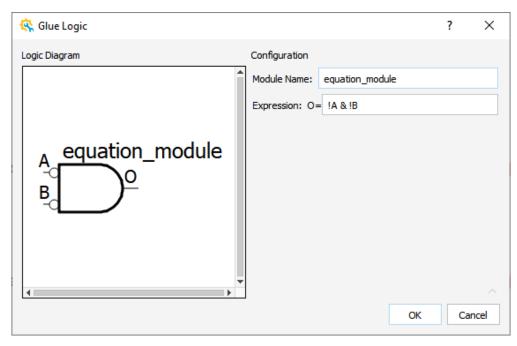

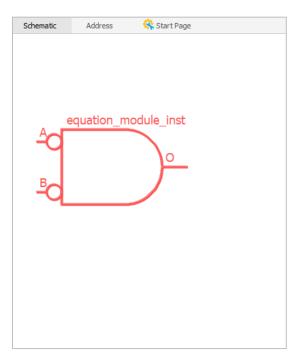

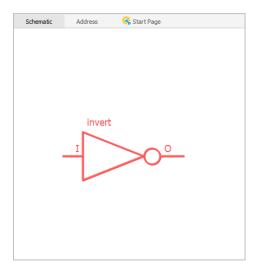

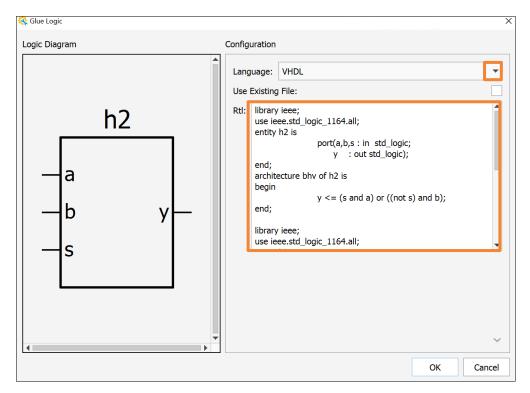

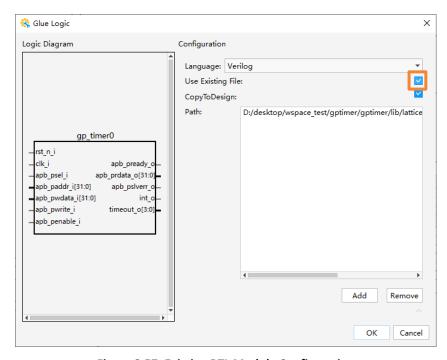

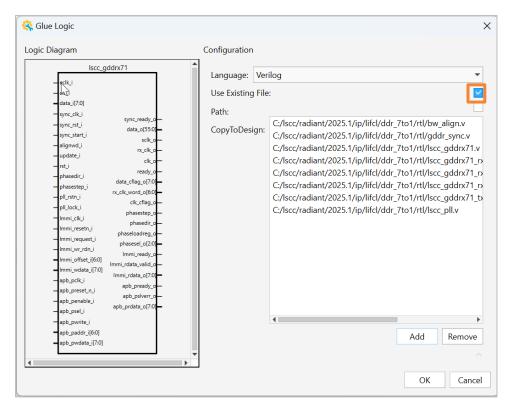

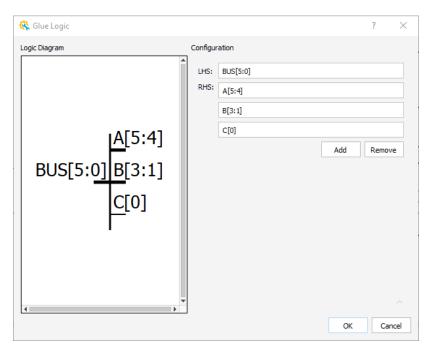

|    | 2.3.4.    | Adding Glue Logic                                                    | 44  |

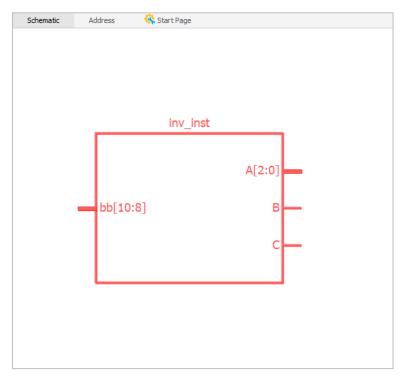

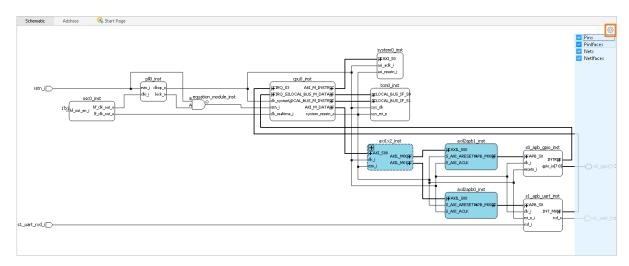

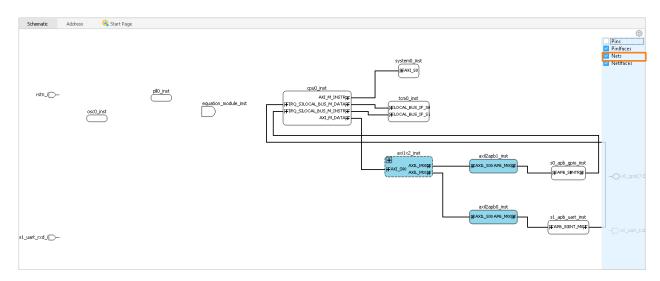

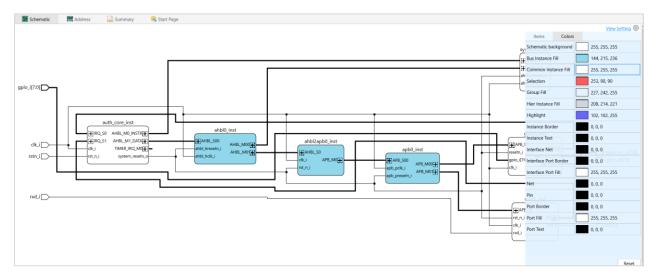

|    | 2.3.5.    | Working with the Schematic View                                      | 52  |

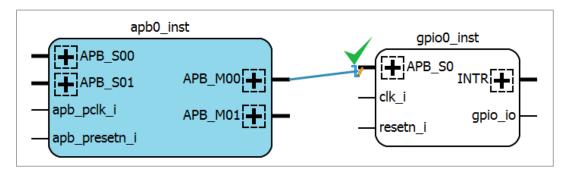

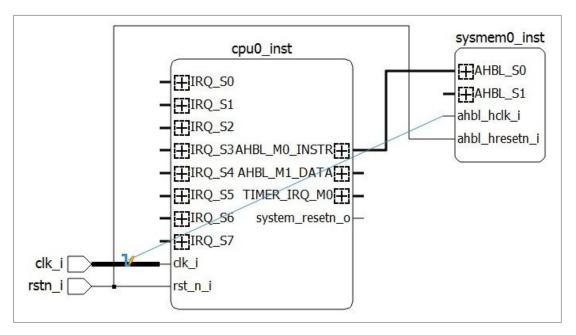

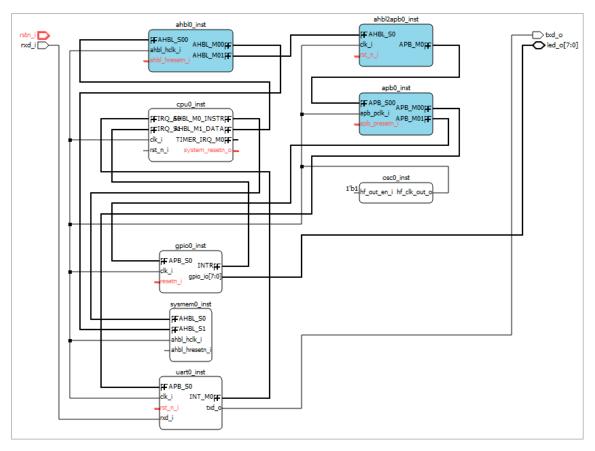

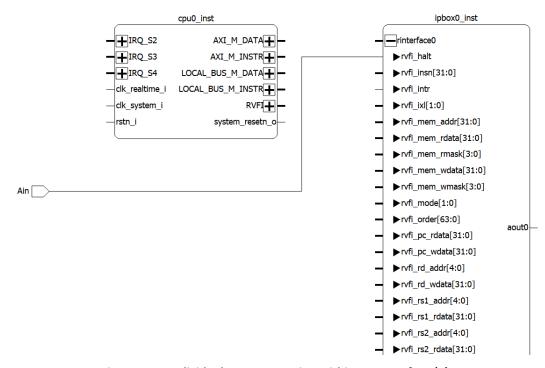

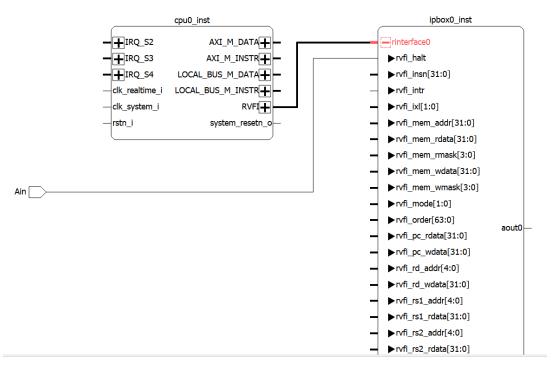

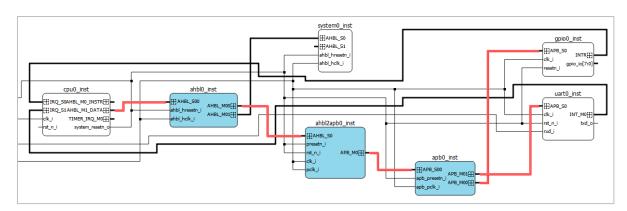

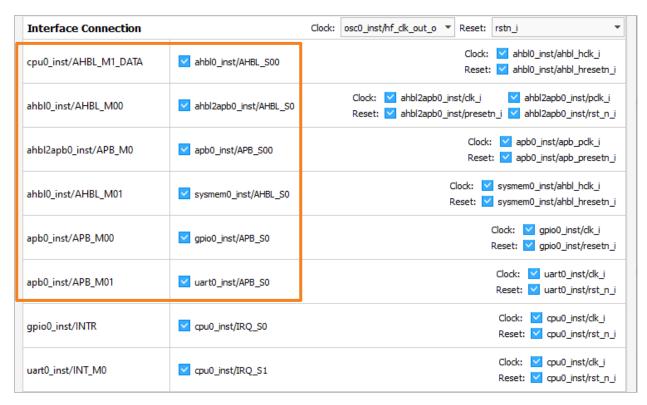

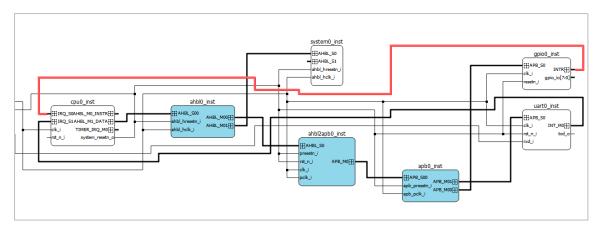

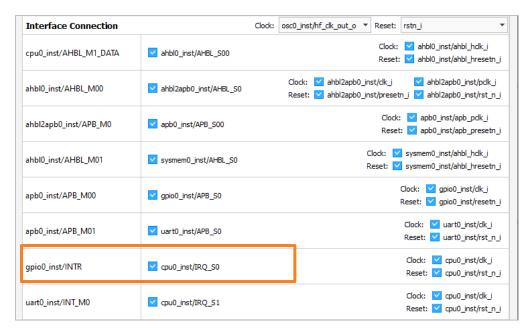

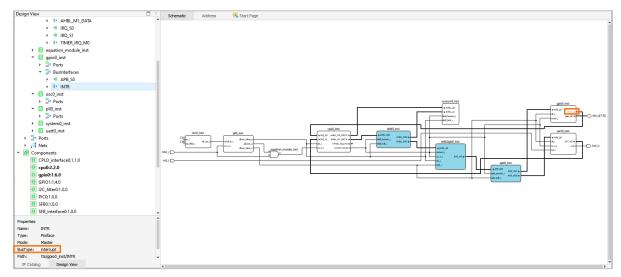

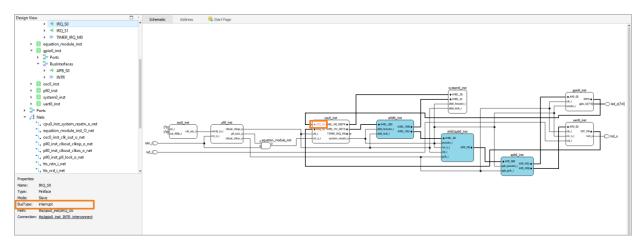

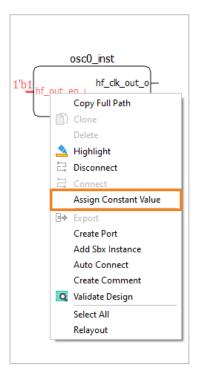

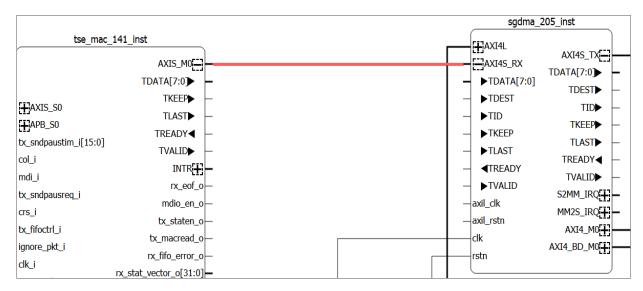

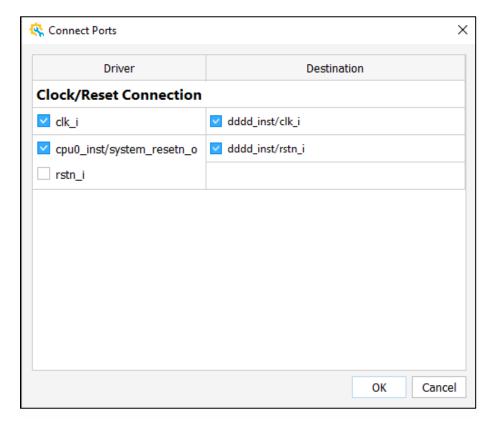

|    | 2.3.6.    | Connecting Modules                                                   | 65  |

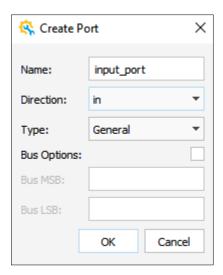

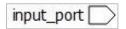

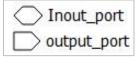

|    | 2.3.7.    | Creating Top-level Ports                                             | 79  |

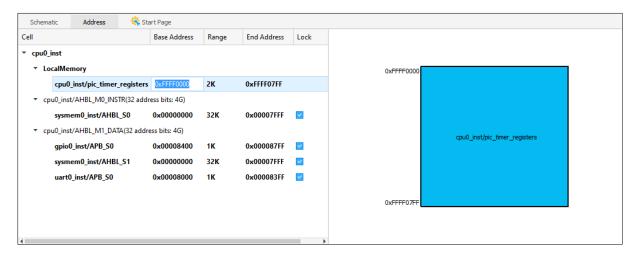

|    | 2.3.8.    | Adjusting Address Spaces                                             | 83  |

|    | 2.3.9.    | Validating the Design                                                | 84  |

|    | 2.3.10    | Generating the Propel Design                                         | 85  |

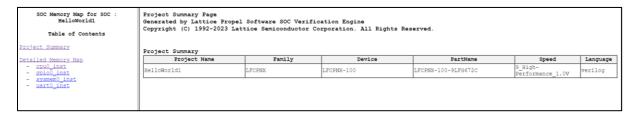

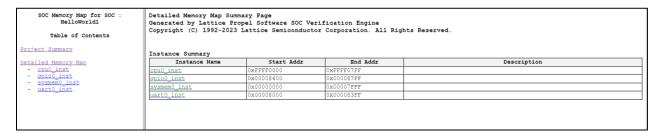

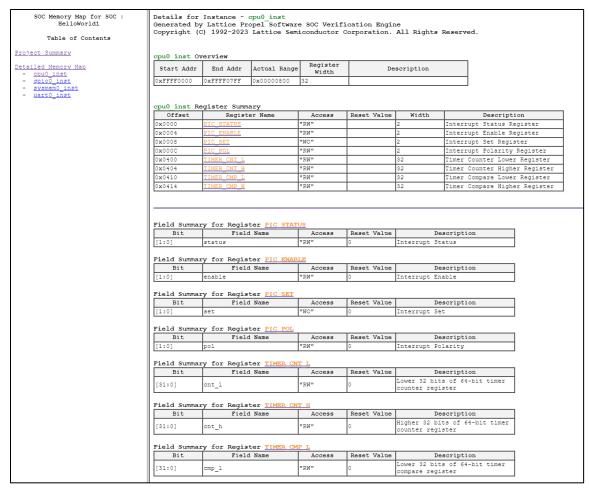

|    | 2.3.11    | Generating the Memory Report                                         | 86  |

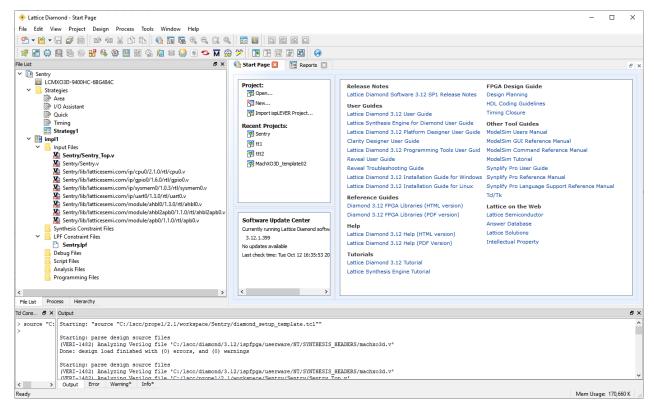

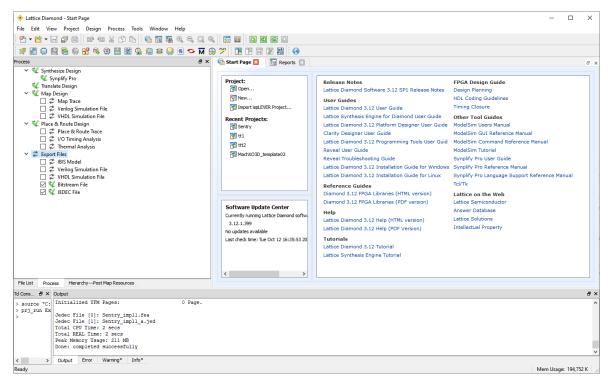

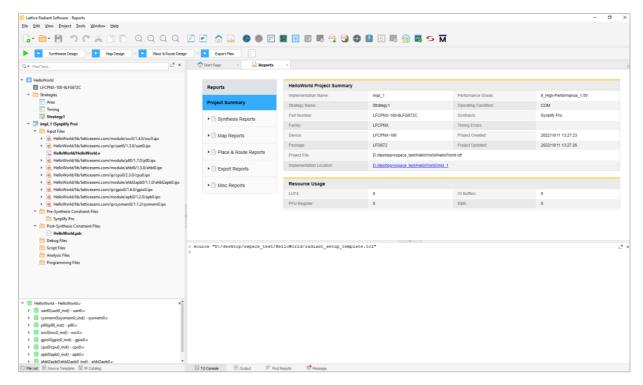

|    | 2.3.12    | Launching Project in Diamond or Radiant Software                     | 87  |

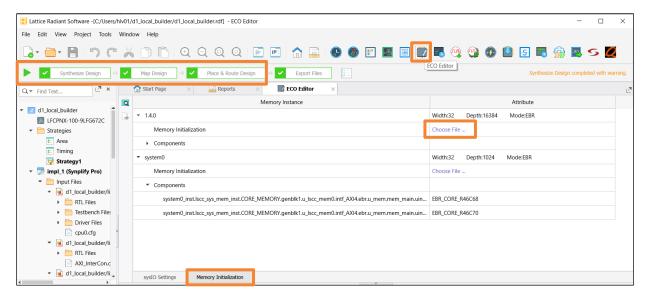

|    | 2.3.13    | Launching SDK and Generate Mem File                                  | 92  |

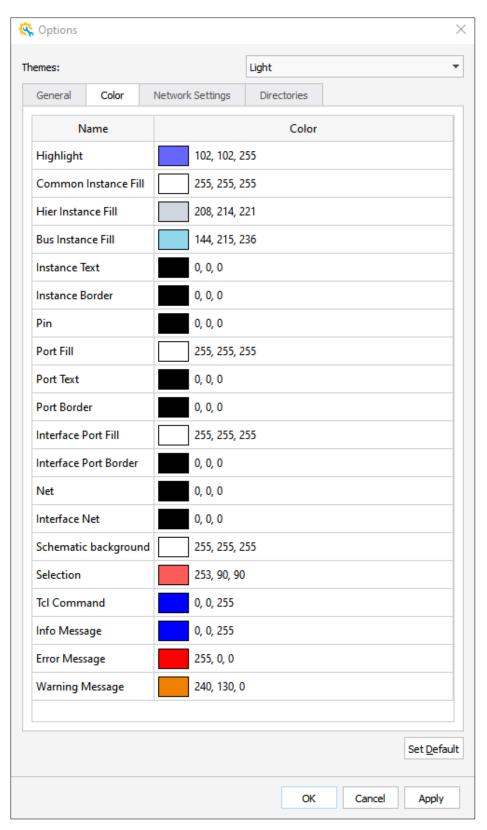

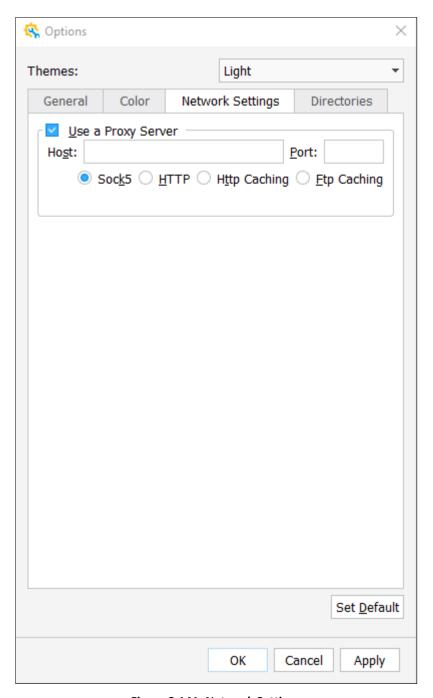

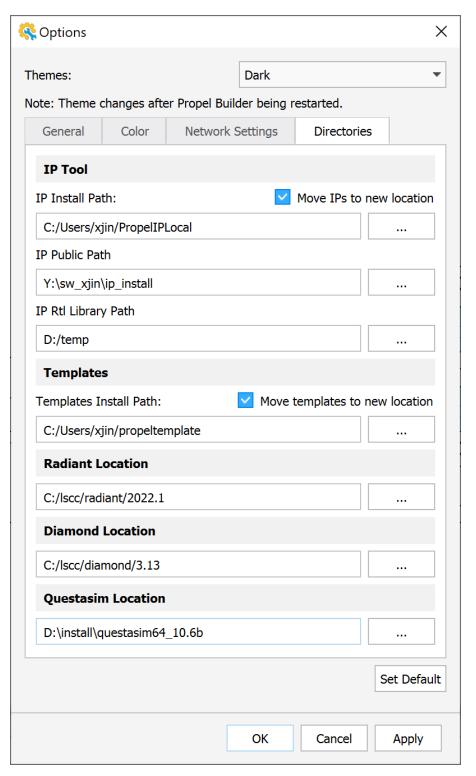

|    | 2.3.14    | Tools                                                                | 98  |

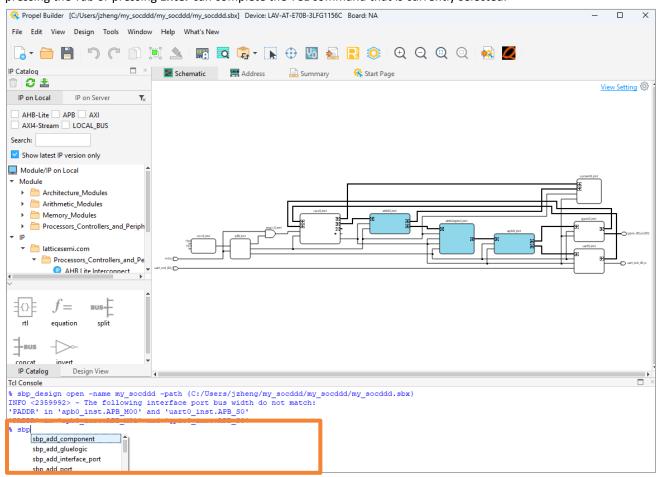

|    | 2.3.15    | TCL Console Auto-suggestion/Completion                               | 112 |

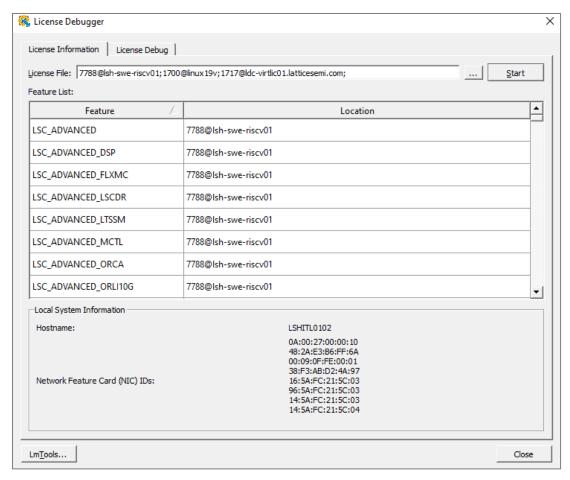

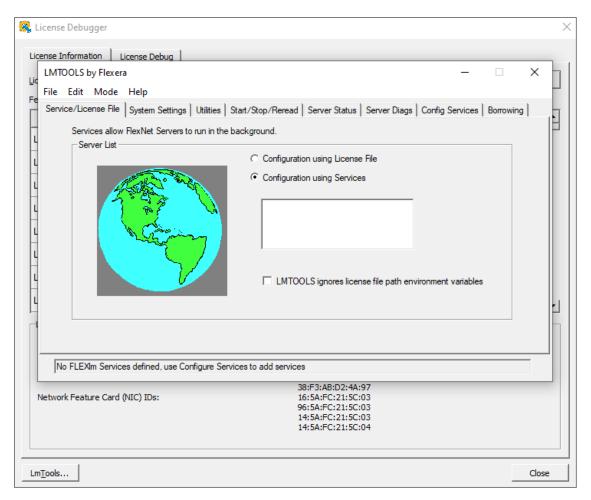

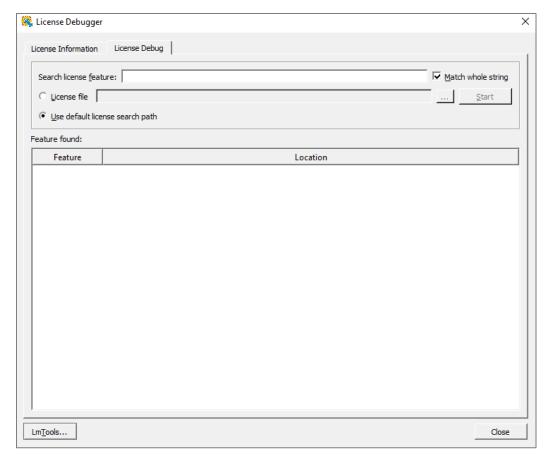

|    | 2.3.16    | License Debugger Tool                                                | 112 |

|    | 2.3.17    | Others                                                               | 115 |

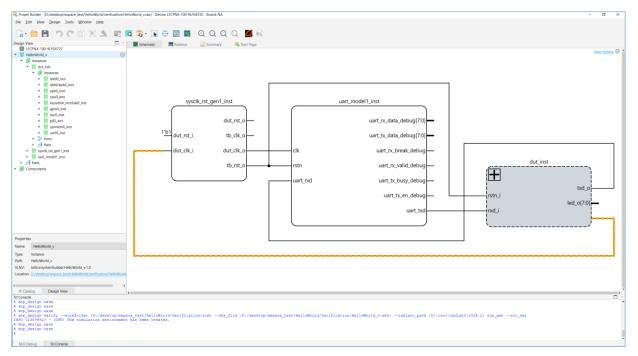

|    | 2.4.      | /erification Project Flow                                            | 119 |

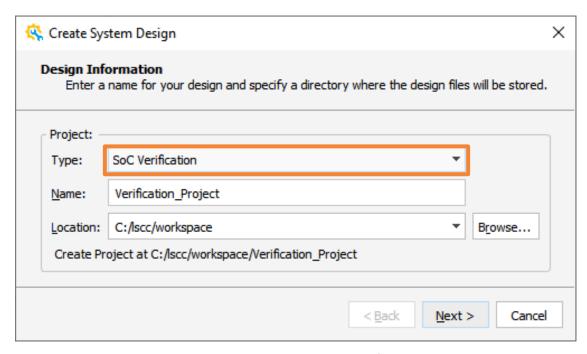

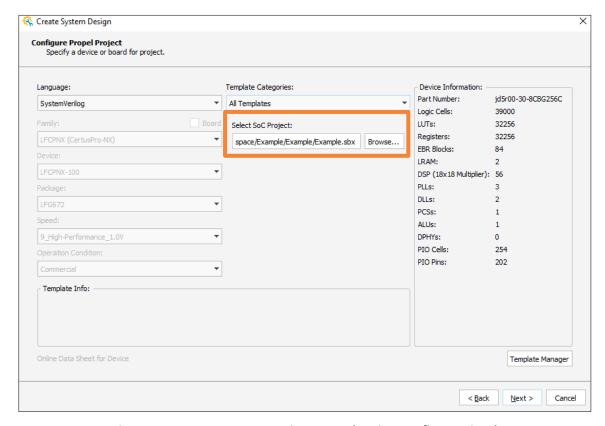

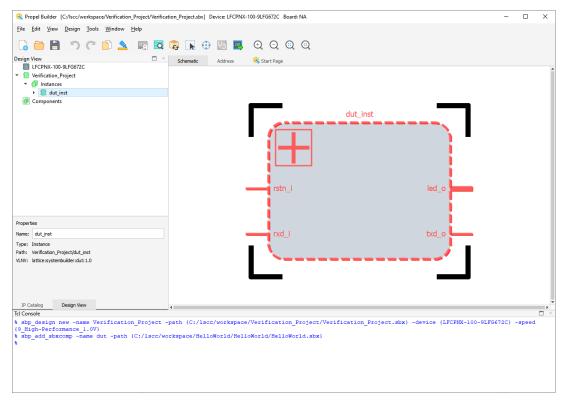

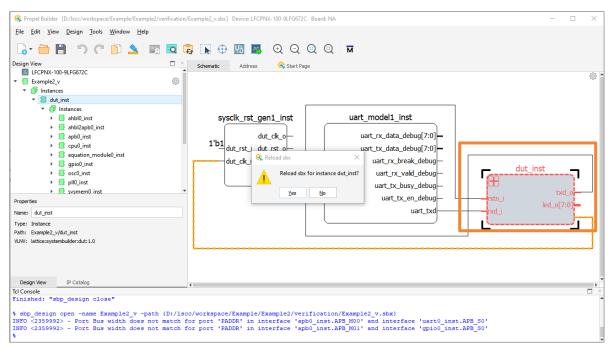

|    | 2.4.1.    | Creating a Verification Project                                      | 119 |

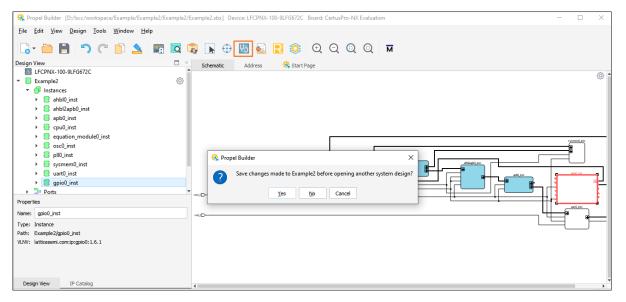

|    | 2.4.2.    | Switching from SoC Design Project to Verification Project            | 122 |

|    | 2.4.3.    | Opening a Verification Project                                       | 124 |

|    | 2.4.4.    | Adding Modules, IP and VIPs                                          | 124 |

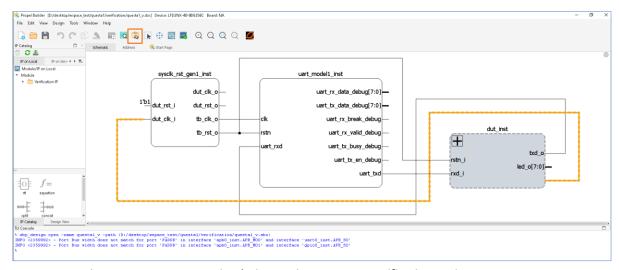

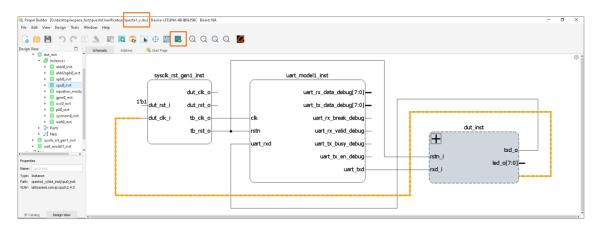

|    | 2.4.5.    | Working with the Schematic View                                      | 124 |

|    | 2.4.6.    | Connecting Modules                                                   | 124 |

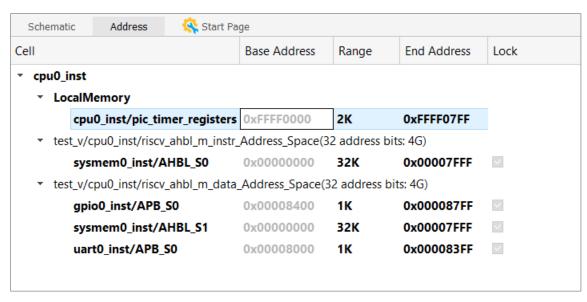

|    | 2.4.7.    | Viewing Address Maps                                                 | 124 |

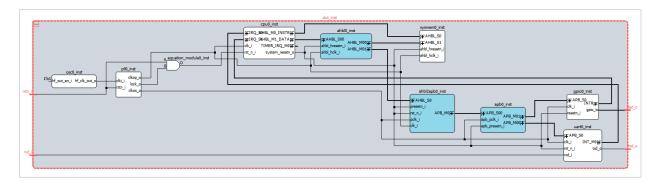

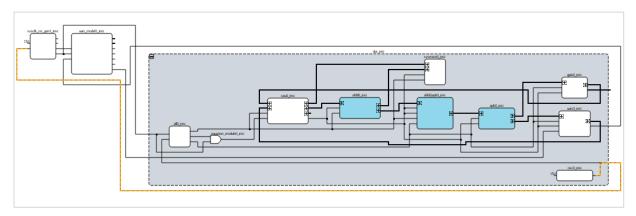

|    | 2.4.8.    | Monitoring DUT                                                       | 125 |

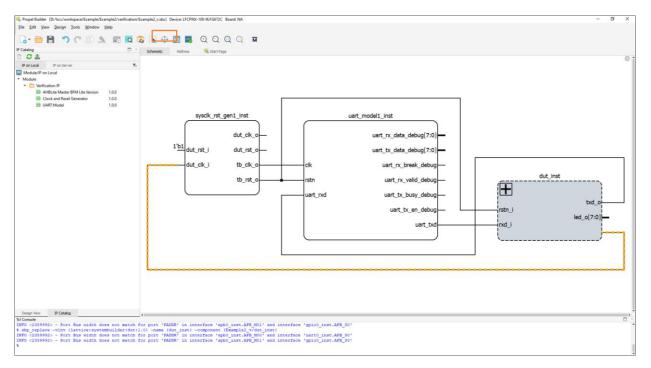

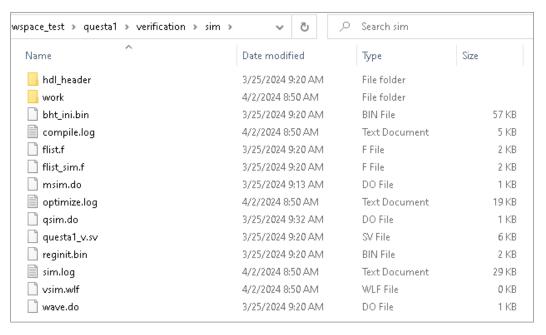

|    | 2.4.9.    | Generating Simulation Environment                                    | 126 |

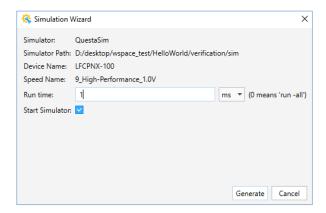

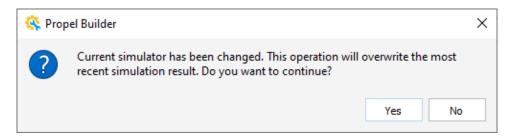

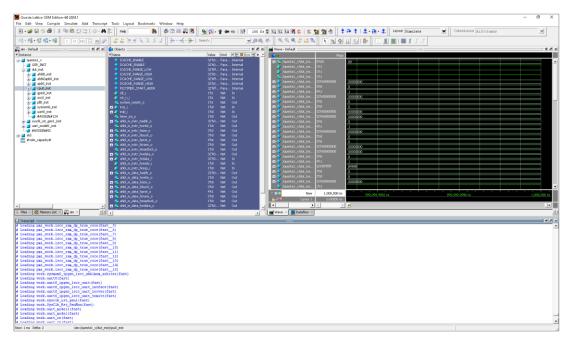

|    | 2.4.10    | Launching Simulation                                                 | 129 |

|    | 2.5. A    | Advanced Usage                                                       | 131 |

|    | 2.5.1.    | Supported Interface                                                  | 131 |

|    | 2.5.2.    | Supported Language                                                   | 131 |

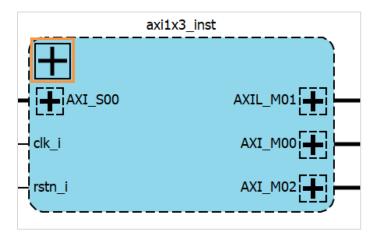

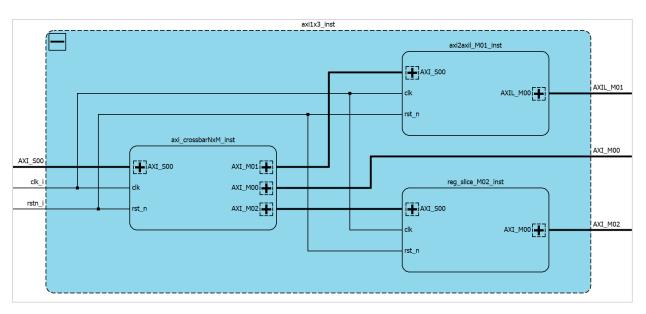

|    | 2.5.3.    | Supported Hierarchical IP                                            | 131 |

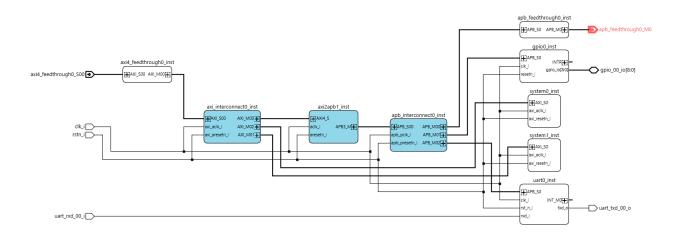

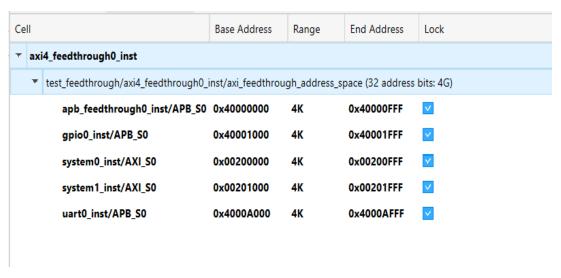

|    | 2.5.4.    | Address Mapping External IPs (CPU or APB, AHBL, and AXI Peripherals) | 132 |

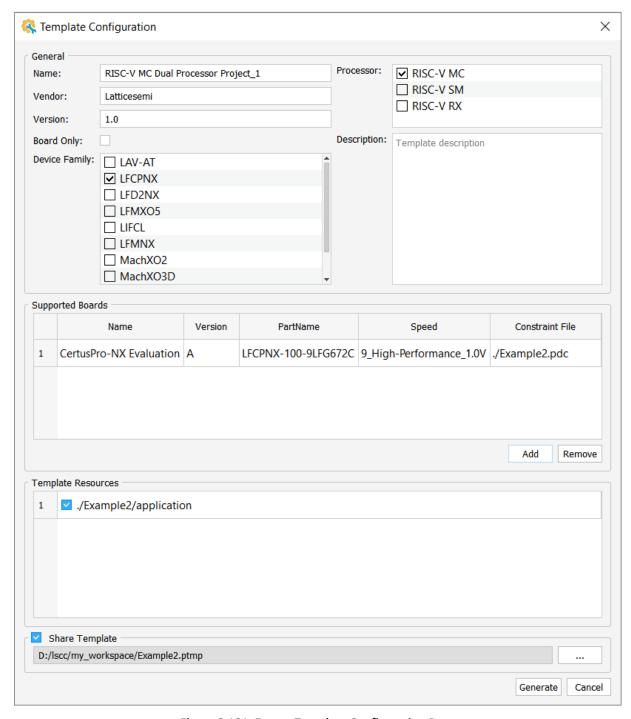

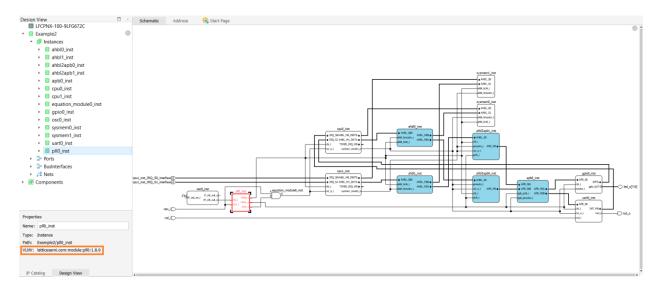

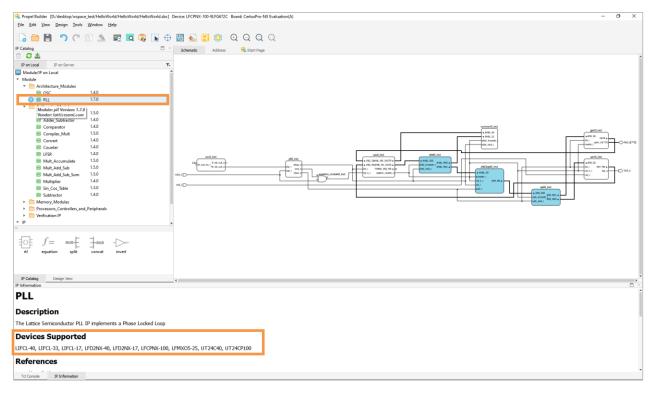

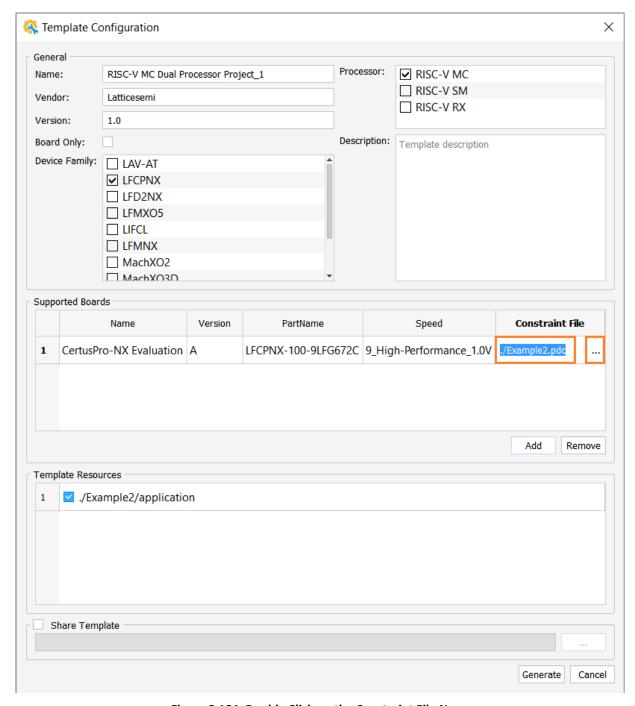

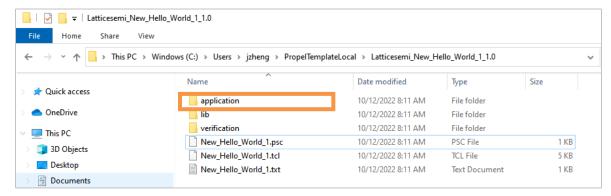

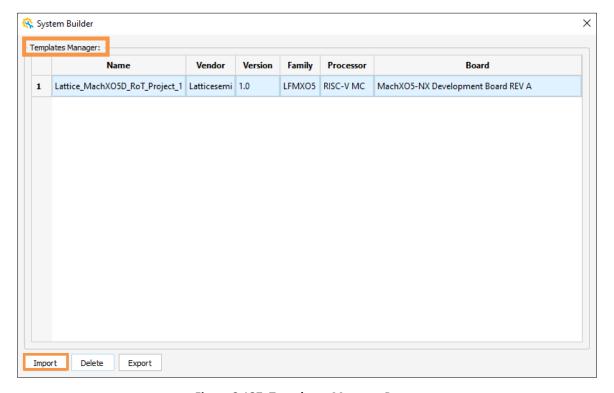

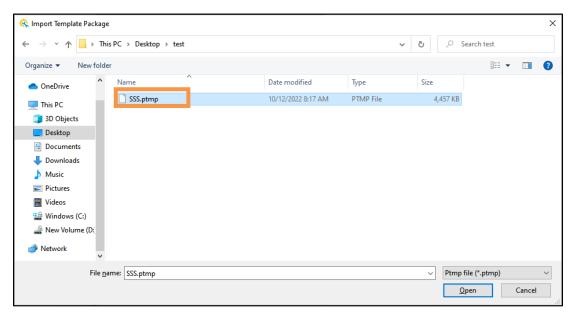

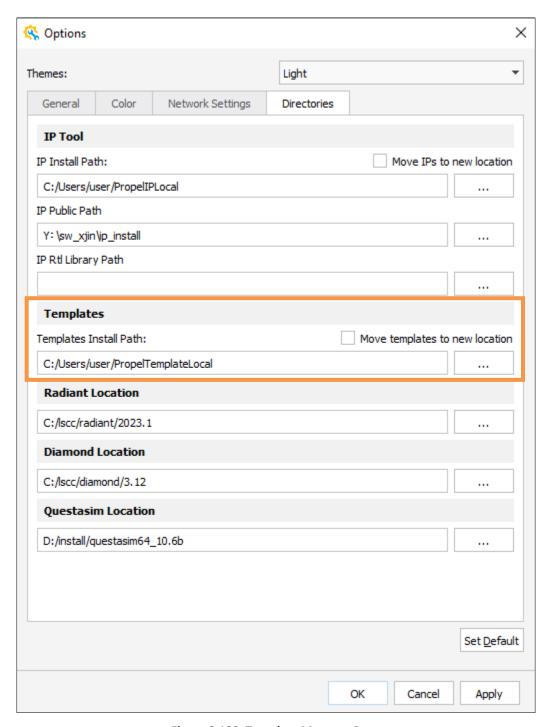

|    | 2.5.5.    | Define Custom Template                                               | 134 |

|    | 2.5.6.    | Include Sub Sbx File                                                 | 143 |

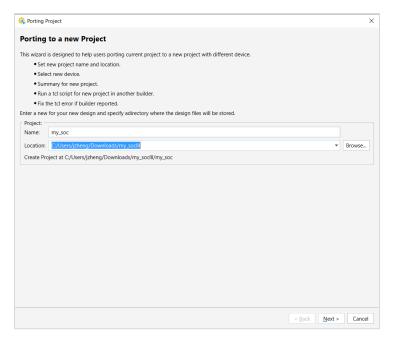

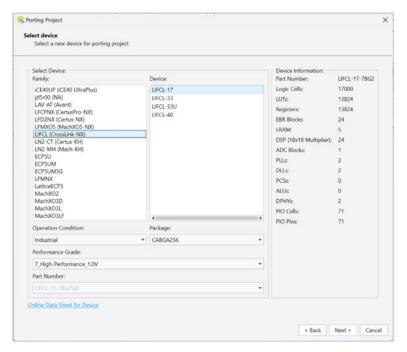

|    | 2.5.7.    | Porting Design                                                       | 145 |

| 3. | TCL Co    | mmands                                                               | 147 |

|    | 3.1.      | bp_design Commands                                                   | 147 |

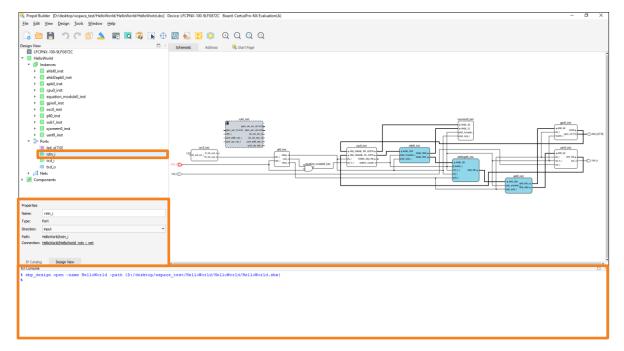

|    | 3.1.1.    | Open                                                                 | 147 |

|    | 3.1.2.    | Close                                                                | 147 |

|    | 3.1.3.    | New                                                                  | 147 |

|    | 3.1.4.    | Save                                                                 | 147 |

|    | 3.1.5.    | Drc                                                                  | 147 |

|    |           |                                                                      |     |

| 3.1.6.  | Generate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 148 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1.7.  | Auto Assign Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 148 |

| 3.1.8.  | Verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 148 |

| 3.1.9.  | PGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 148 |

| 3.1.10. | Undo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149 |

| 3.1.11. | Redo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149 |

| 3.1.12. | Set Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149 |

| 3.1.13. | Set Project Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 149 |

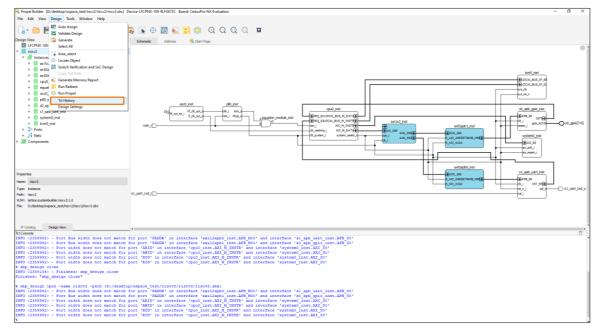

|         | Generate Design Project TCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|         | ther TCL Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 3.2.1.  | sbp create project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 3.2.2.  | sbp add component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 3.2.3.  | sbp add sbxcomp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 3.2.4.  | sbp config ip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 3.2.5.  | ip catalog list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 3.2.6.  | ip catalog install                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 3.2.7.  | ip catalog uninstall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 3.2.8.  | sbp upgrade component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 3.2.9.  | sbp add gluelogic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|         | sbp_create_glue_logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|         | sbp_creconfig_gluelogicsbp_reconfig_gluelogic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

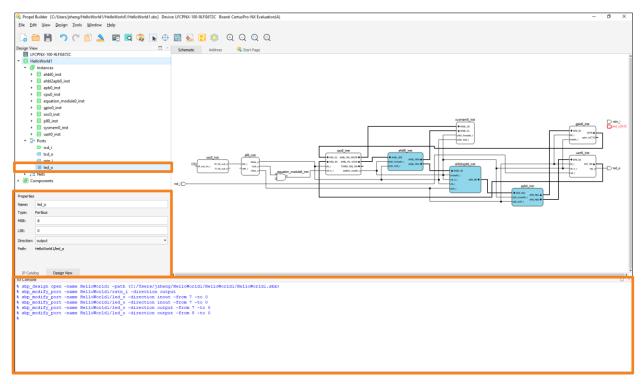

|         | sbp add port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

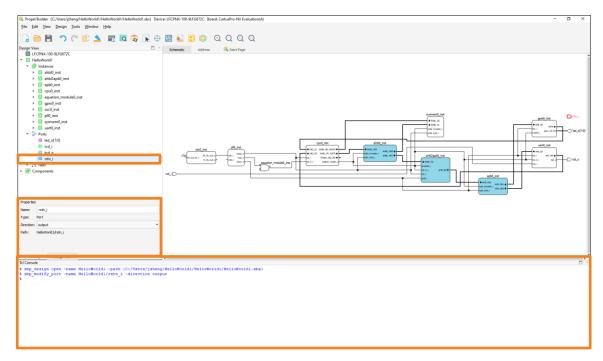

|         | sbp modify port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|         | sbp connect net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|         | sbp_connect_interface_netsbp_connect_interface_net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|         | sbp_connect_interrace_net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|         | sbp_connect_whitebox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|         | sbp_connect_ group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|         | sbp_disconnect_whitebox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|         | sbp_disconnect_whiteboxsbp_disconnect_interface_net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|         | sbp_disconnect_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interridec_interri |     |

|         | sbp_assign_addr_segsbp_assign_addr_seg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

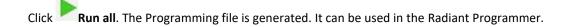

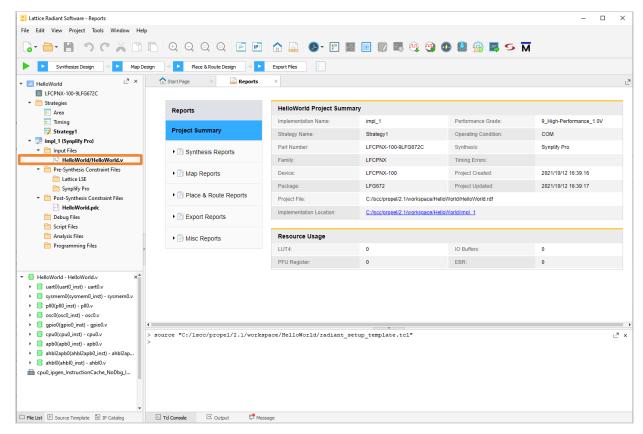

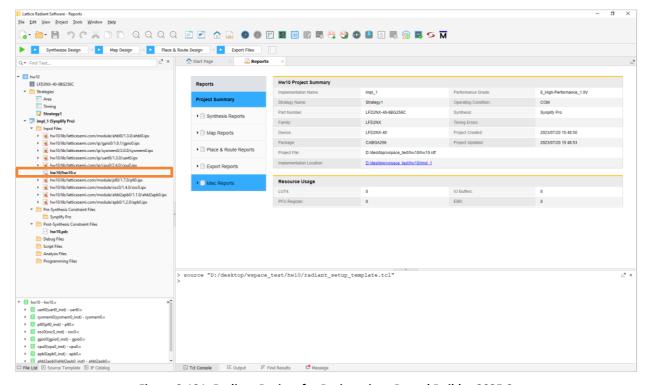

|         | sbp unassign addr seg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |