# **Lattice Propel 2025.2 SDK**

# **User Guide**

FPGA-UG-02244-1.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| C  | ontents    |                                                    | 3   |

|----|------------|----------------------------------------------------|-----|

| Α  | bbreviatic | ns in This Document                                | 9   |

| 1. | Introd     | uction                                             | .11 |

|    | 1.1.       | Purpose                                            | .11 |

|    | 1.2.       | Audience                                           | .11 |

| 2. | . Lattice  | Propel Development Suite                           | .12 |

|    | 2.1.       | Eclipse IDE                                        | .12 |

|    | 2.2.       | Lattice Propel Builder                             | .12 |

|    | 2.3.       | Lattice Propel SDK                                 |     |

| 3. | . Lattice  | Propel Tool Flows                                  |     |

|    |            | Lattice Propel Environment                         |     |

|    | 3.1.1.     | Running Lattice Propel                             | .13 |

|    | 3.1.2.     | Importing Lattice SoC Design Projects              |     |

|    | 3.1.3.     | Importing Lattice C/C++ Projects                   |     |

|    | 3.1.4.     | Creating Customized C/C++ Templates                |     |

|    | 3.1.5.     | Exporting and Deploying Customized C/C++ Templates |     |

|    | 3.2.       | SoC Project Design Flow                            |     |

|    | 3.2.1.     | <i>,</i>                                           |     |

|    | 3.2.2.     | Opening an SoC Design in Lattice Propel Builder    |     |

|    | 3.2.3.     | Opening a Design in Lattice FPGA Design Software   |     |

|    | 3.2.4.     | Generating System Environment by Building Project  |     |

|    | 3.2.5.     | About SoC Design Project                           |     |

|    |            | C/C++ Project Design Flow                          |     |

|    | 3.3.1.     | Creating a Lattice C/C++ Project                   |     |

|    | 3.3.2.     | Updating a Lattice C/C++ Project                   |     |

|    | 3.3.3.     | Building a Lattice C/C++ Project                   |     |

|    | 3.3.4.     | About Lattice C/C++ Project                        |     |

|    | 3.3.5.     | Assisting in Developing Code                       |     |

|    | 3.3.6.     | Advanced Tool Chain Setting                        |     |

|    |            | System Simulation Flow                             |     |

|    | 3.4.1.     | Launching Simulation                               |     |

|    | 3.4.2.     | Simulation Details                                 |     |

|    | 3.5.       | Programming and On-Chip Debugging Flow             |     |

|    | 3.5.1.     |                                                    |     |

|    | 3.5.2.     | Starting a Debug Session                           |     |

|    | 3.5.3.     | Peripherals Registers View                         |     |

|    | 3.5.4.     | Serial Terminal Tool – Windows                     |     |

|    | 3.5.5.     | Serial Terminal Tool – Linux                       |     |

| 4. |            | o Start with Lattice FPGA Board                    |     |

|    | 4.1.       | Board Introduction                                 | .50 |

|    | 4.2.       | Creating an SoC Project                            | .51 |

|    | 4.3.       | Creating a C/C++ Project                           | .52 |

|    | 4.4.       | Memory Initialization (Optional)                   |     |

|    | 4.5.       | Generating and Programing a Bit File               |     |

|    | 4.6.       | On-Chip Debugging                                  | .52 |

| 5. |            | al Application Templates                           |     |

|    | 5.1.       | Template List and Requirements                     |     |

|    | 5.2.       | Hello World                                        |     |

|    | 5.3.       | RTOS                                               |     |

|    | 5.4.       | Single Function                                    |     |

|    | 5.4.1.     | Hardware Interrupt Project (PIC)                   |     |

|    | 5.4.2.     | Mtimer Project                                     |     |

|    | **         | •                                                  | _   |

| 5.4.3.     | Hardware Interrupt Project (PLIC)                                   |     |

|------------|---------------------------------------------------------------------|-----|

| 5.4.4.     | Real Timer Project                                                  | 58  |

| 5.4.5.     | Software Interrupt Project                                          |     |

| 5.4.6.     | Watchdog Timer Project                                              |     |

| 5.5.       | IP Usage Reference                                                  |     |

| 5.5.1.     | I2C Communication Project                                           | 60  |

| 5.5.2.     | SPI Controller Project                                              |     |

| 5.5.3.     | I3C Communication Project                                           |     |

| 5.5.4.     | General-Purpose Timer Project                                       |     |

| 5.6.       | Profiling Tool                                                      |     |

| 5.6.1.     | Code Coverage Project                                               |     |

| 5.6.2.     | How to Add Code Coverage Function to an Existing C Project          |     |

| 5.6.3.     | 0 - 0 -7                                                            |     |

| 5.6.4.     |                                                                     |     |

|            | e Propel Tutorial – Hello World                                     |     |

| 6.1.       | Creating an SoC Design Project and Preparing Hardware Design        |     |

| 6.2.       | Creating a Hello World C Project                                    |     |

| 6.3.       | Memory Initialization (Optional)                                    |     |

| 6.4.       | Launching Lattice Diamond Software                                  |     |

| 6.5.       | Programming the Target Device                                       |     |

| 6.6.       | Running Demo on the MachXO3D Breakout Board                         |     |

|            | e Propel Tutorial – CXU Demo                                        |     |

| 7.1.       | Preparing the Hardware and Programming the Target Device – CXU Demo |     |

| 7.2.       | Creating a CXU C Project                                            |     |

| 7.3.       | Compiling and Running Demo – CXU Demo                               |     |

| 7.3.1.     | P 8                                                                 |     |

| 7.3.2.     | · · · · · · · · · · · · · · · · · · ·                               |     |

| 7.4.       | Using the Timing Profiling Function                                 |     |

| 7.5.       | Using the Code Coverage Function                                    |     |

|            | e Propel Tutorial – QEMU                                            |     |

| 8.1.       | Creating QEMU Hello World C Project                                 |     |

| 8.2.       | Running QEMU C Project                                              |     |

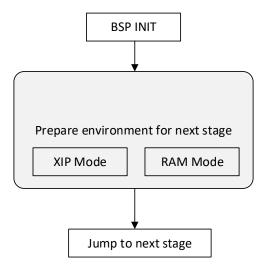

|            | e Propel Tutorial – Bootloader                                      |     |

| 9.1.       | Bootloader for RAM Mode                                             |     |

| 9.1.1.     |                                                                     |     |

| 9.1.2.     | -p                                                                  |     |

| 9.1.3.     | ,                                                                   |     |

| 9.2.       | Bootloader for XIP Mode                                             |     |

| 9.2.1.     | -p <b></b>                                                          |     |

| 9.2.2.     |                                                                     |     |

| 9.2.3.     |                                                                     |     |

|            | A. Linker Script and System Memory Deployment                       |     |

|            | tion                                                                |     |

|            | Fix the Region Overflowed Error                                     |     |

|            | 3. Standard C Library Support                                       |     |

|            | d Scanf Levels in Lattice Propel SDK                                |     |

|            | Library Interfaces Used in Lattice Propel SDK                       |     |

|            | C. Third-party Command-line Tools in Lattice Propel SDK             |     |

|            | D. Command-Line Environment Setting Script in Lattice Propel SDK    |     |

|            | Debugging with Attach to Running Target                             |     |

| -          | Initialization to SoC Project                                       |     |

|            | o Running Targetg. Pack to Default Mode                             |     |

|            | g Back to Default Mode                                              |     |

| Appendix f | negister Access rest                                                | 130 |

| Generating Test Code                                               | 130 |

|--------------------------------------------------------------------|-----|

| Enabling Test Code                                                 | 133 |

| Running Test                                                       | 134 |

| Appendix G. Stack Overflowed Check                                 | 136 |

| Introduction                                                       |     |

| How to Enable the Stack Overflowed Check Function                  | 137 |

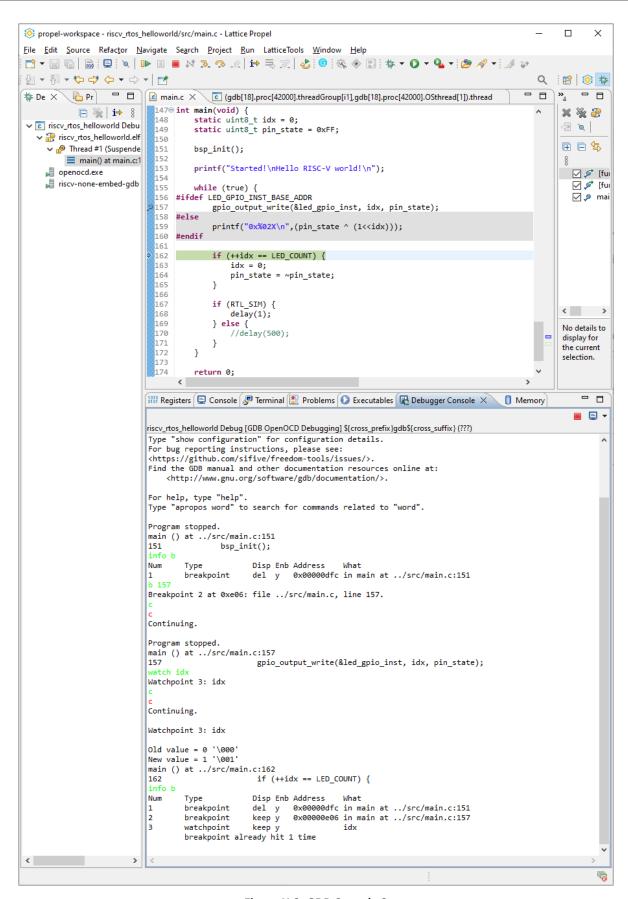

| Appendix H. Breakpoint and Watchpoint Introduction                 | 140 |

| How to Use Breakpoint                                              | 140 |

| How to Use Watchpoint                                              | 141 |

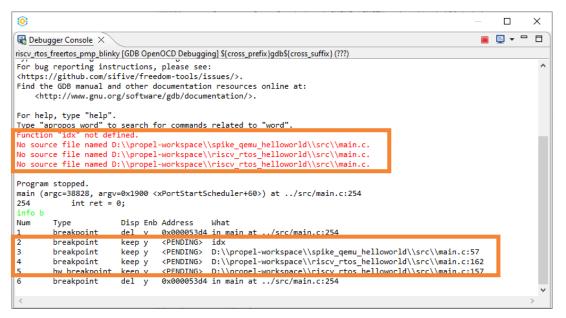

| Limitation of Software Watchpoint                                  | 141 |

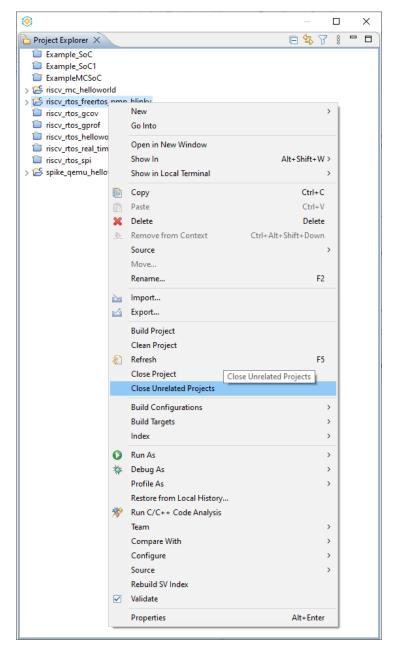

| Tips for Using Breakpoint or Watchpoint                            | 143 |

| References                                                         | 145 |

| Technical Support Assistance                                       |     |

| Revision History                                                   | 147 |

| Figures                                                            |     |

| Figure 3.1. Select Workspace Dialog                                | 13  |

| Figure 3.2. Lattice Propel Workbench Window                        |     |

| Figure 3.3. Select Wizard – Import Lattice SoC Design Projects     |     |

| Figure 3.4. Import Lattice SoC Design Projects Wizard              |     |

| Figure 3.5. Select Wizard – Import Lattice C/C++ Projects          |     |

| Figure 3.6. Import Lattice C/C++ Projects Wizard                   |     |

| Figure 3.7. Create Application Template – General                  |     |

| Figure 3.8. Create Application Template – IP Settings              |     |

| Figure 3.9. Select Wizard for Lattice Application Templates        |     |

| Figure 3.10. Export Lattice Application Templates Wizard           |     |

| Figure 3.11. Lattice Propel Setting Page                           |     |

| Figure 3.12. Specify a Device for Template SoC Project             |     |

| Figure 3.13. Specify a Board for Template SoC Project              |     |

| Figure 3.14. LatticeTools Menu                                     |     |

| Figure 3.15. Project Explorer Pop-up Menu                          |     |

| Figure 3.16. Lattice Propel Builder Window                         |     |

| Figure 3.17. Lattice Propel Preferences Dialog                     |     |

| Figure 3.18. Lattice Diamond Software Project                      |     |

| Figure 3.19. Lattice Radiant Software Project                      |     |

| Figure 3.20. Generate Programming File in Lattice Diamond Software |     |

| Figure 3.21. Generate Programming File in Lattice Radiant Software |     |

| Figure 3.22. Build Result of SoC Project                           |     |

| Figure 3.23. Contents of SoC Project                               |     |

| Figure 3.24. Load System and BSP Page 1                            |     |

| Figure 3.25. Load System and BSP Page 2                            |     |

| Figure 3.26. Lattice Toolchain Setting Dialog 1                    |     |

| Figure 3.27. Update System and BSP Dialog                          |     |

| Figure 3.28. Update System and BSP Confirm Dialog                  |     |

| Figure 3.29. Manage Configurations Dialog                          |     |

| Figure 3.30. Build Result of C/C++ Project                         |     |

| Figure 3.31. Contents of C/C++ Project                             |     |

| Figure 3.32. Lattice System Platform                               |     |

| Figure 3.33. Linker Editor                                         |     |

| Figure 3.34. Properties of C/C++ Project                           |     |

| Figure 3.35. Configuring System Memory Module 1                    |     |

| Figure 3.36. SoC Verification Project                              | 40  |

| Figure 3.37. Questa Simulation GUI                                                             |    |

|------------------------------------------------------------------------------------------------|----|

| Figure 3.38. Debug Configurations Dialog 1                                                     |    |

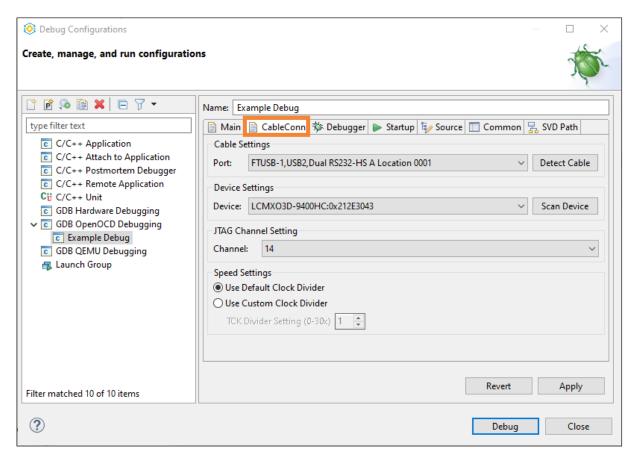

| Figure 3.39. CableConn Tab of Debug Configurations                                             | 43 |

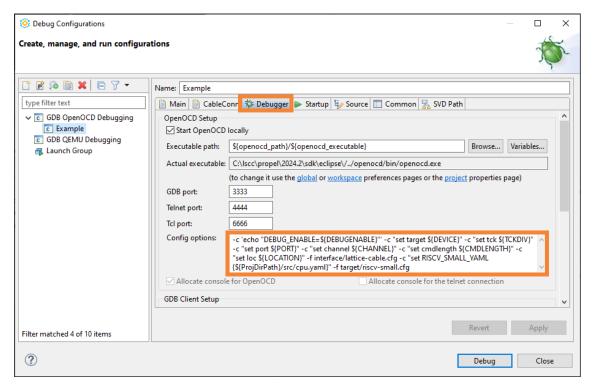

| Figure 3.40. Debugger Tab of Debug Configurations                                              | 44 |

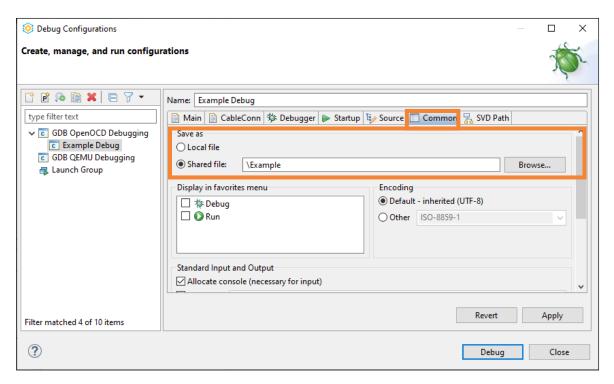

| Figure 3.41. Common Tab of Debug Configurations                                                |    |

| Figure 3.42. Launch Configurations                                                             | 45 |

| Figure 3.43. Debug Icon on Toolbar                                                             | 46 |

| Figure 3.44. Debug Perspective 1                                                               | 46 |

| Figure 3.45. Peripherals View in Debug Perspective                                             | 47 |

| Figure 3.46. Launch Terminal Dialog 1                                                          | 47 |

| Figure 3.47. Terminal View                                                                     | 48 |

| Figure 3.48. Launch Terminal Dialog 2                                                          | 48 |

| Figure 3.49. Terminal cli                                                                      | 49 |

| Figure 3.50. On-Chip Debug with UART Output                                                    | 49 |

| Figure 4.1. CertusPro-NX Evaluation Board                                                      |    |

| Figure 4.2. Select Template GUI                                                                |    |

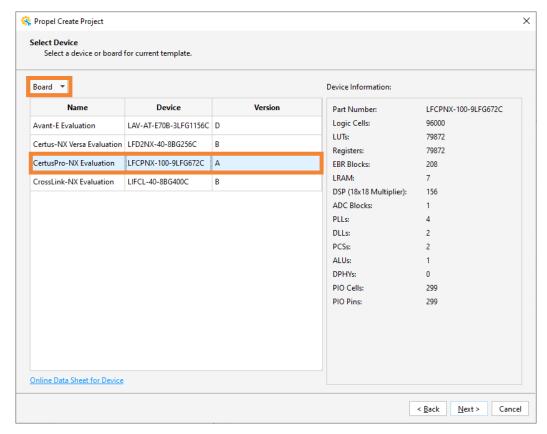

| Figure 4.3. Select Device GUI                                                                  |    |

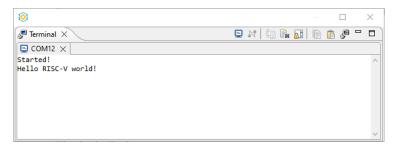

| Figure 5.1. Hello World Project Terminal                                                       |    |

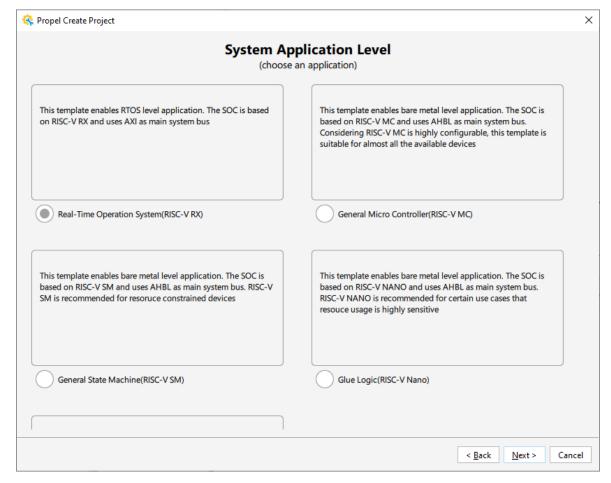

| Figure 5.2. Scalable SoC Project – Real-Time Operation System (RISC-V RX)                      |    |

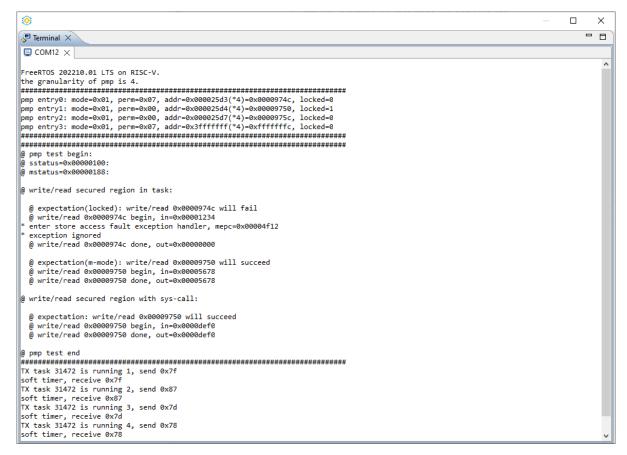

| Figure 5.3. FreeRTOS-LTS PMP-Blinky Project Terminal Print-out                                 |    |

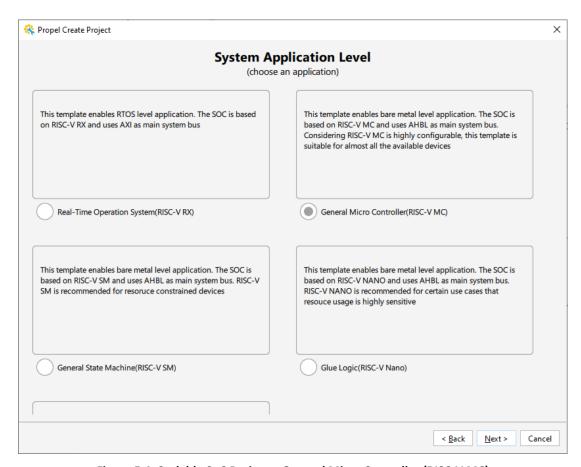

| Figure 5.4. Scalable SoC Project – General Micro Controller (RISC-V MC)                        |    |

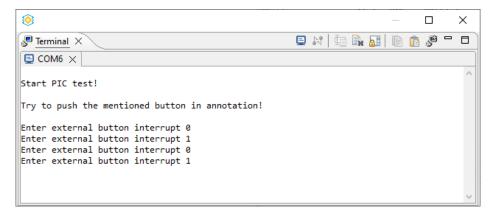

| Figure 5.5. Hardware Interrupt Project (PIC) Project Terminal Print-out                        |    |

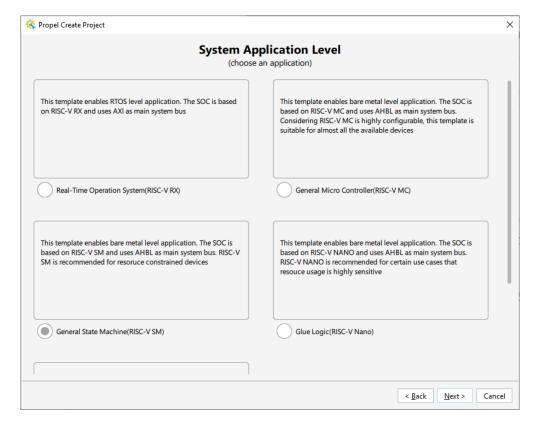

| Figure 5.6. Scalable SoC Project – General State Machine (RISC-V SM)                           |    |

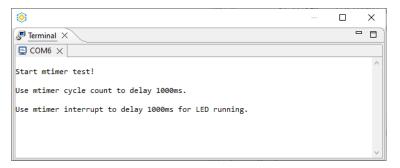

| Figure 5.7. Mtimer Project                                                                     |    |

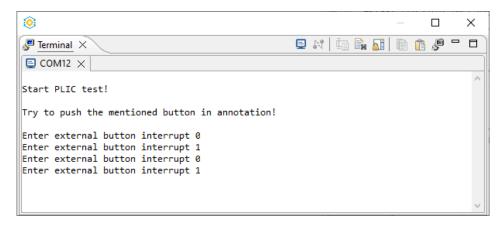

| Figure 5.8. Hardware Interrupt Project (PLIC) Project Terminal Print-out                       |    |

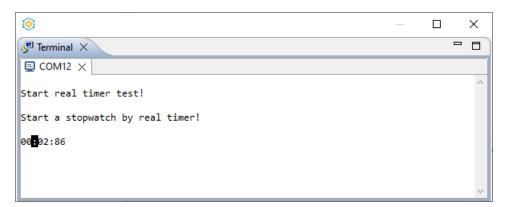

| Figure 5.9. Real Timer Project                                                                 |    |

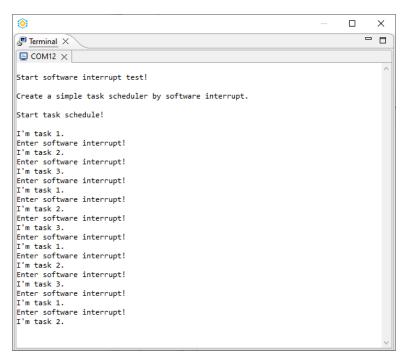

| Figure 5.10. Software Interrupt Project                                                        |    |

| Figure 5.11. Watchdog Timer Project                                                            |    |

| Figure 5.12. I2C Communication Project                                                         |    |

| Figure 5.13. Selecting Default for System Library                                              |    |

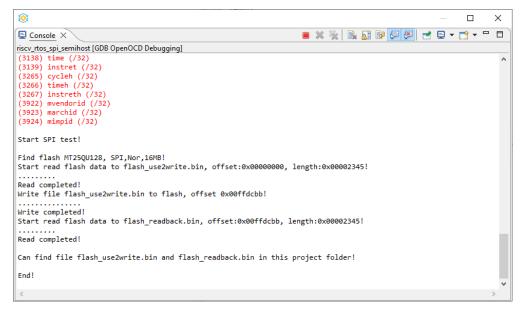

| Figure 5.14. Read or Write between the RAM and the Flash                                       |    |

| Figure 5.15. Selecting Semihosting System Library                                              |    |

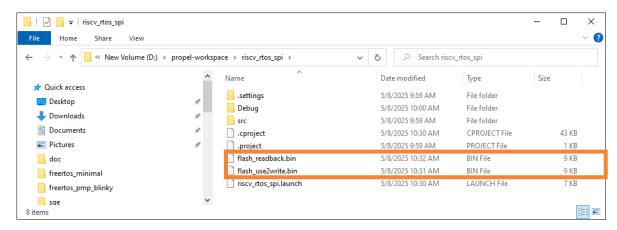

| Figure 5.16. Read or Write between File and Flash                                              |    |

| Figure 5.17. Project Folder                                                                    |    |

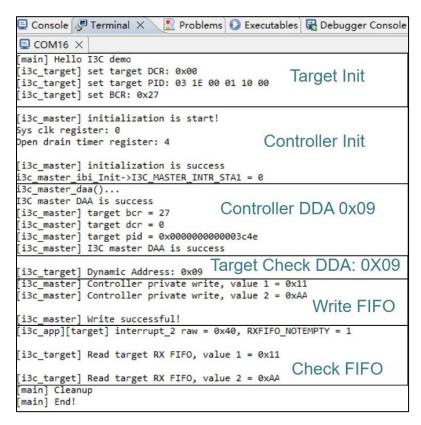

| Figure 5.18. I3C Communication                                                                 |    |

|                                                                                                |    |

| Figure 5.19. General Purpose Timer Project                                                     |    |

|                                                                                                |    |

| Figure 5.21. Code Coverage Files                                                               |    |

| Figure 5.22. Open Coverage Results                                                             |    |

| Figure 5.23. Code Coverage Information                                                         |    |

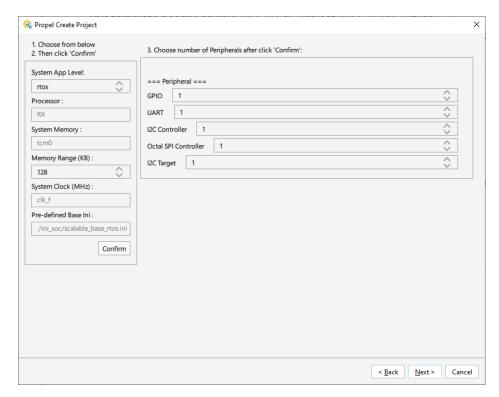

| Figure 5.24. Scalable RISC-V SoC Project – Real-Time Operation System (RISC-V RX) Confirm Page |    |

| Figure 5.25. LSCC_COVERAGE Symbol                                                              |    |

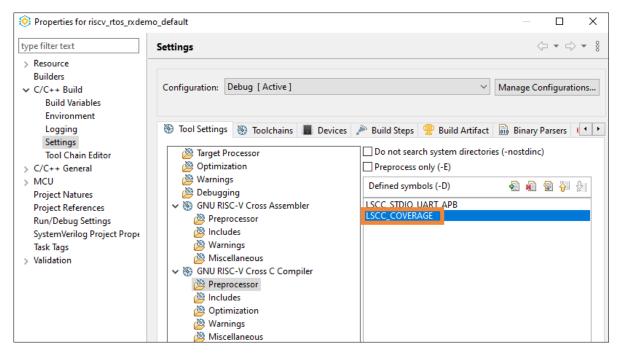

| Figure 5.26fprofile-arcs -ftest-coverage Compiler Flag                                         |    |

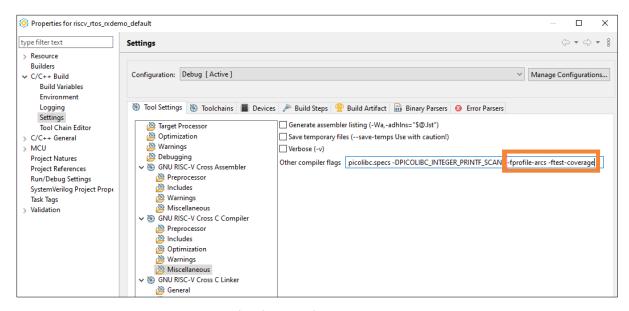

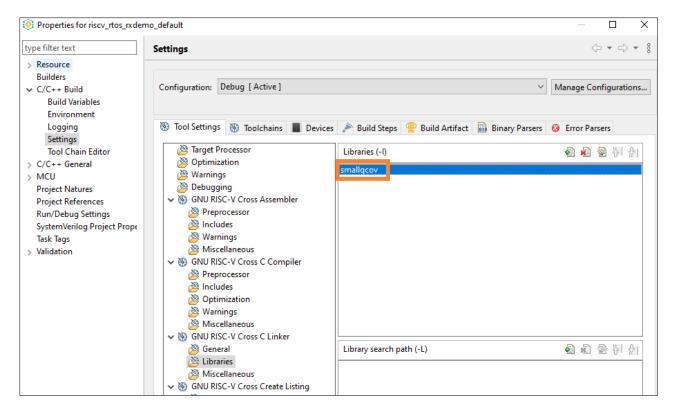

| Figure 5.27. smallgcov Library                                                                 |    |

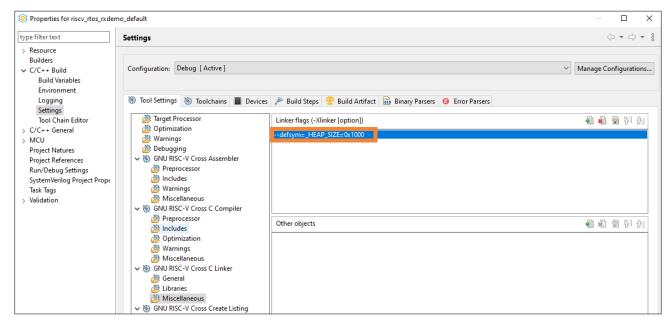

| Figure 5.28defsym=_HEAP_SIZE=0x1000 Linker Flag                                                |    |

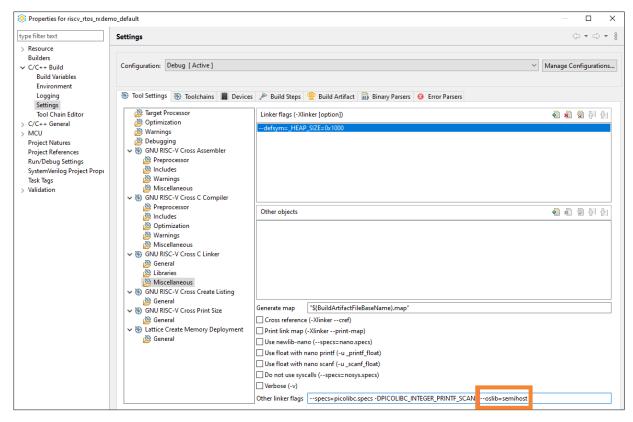

| Figure 5.29oslib=semihost Linker Flag                                                          |    |

| Figure 5.30. Timing Profiling Project                                                          |    |

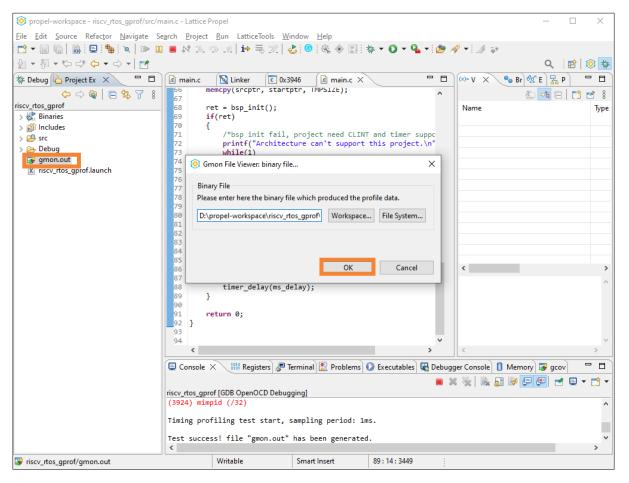

| Figure 5.31. gmon File Viewer                                                                  |    |

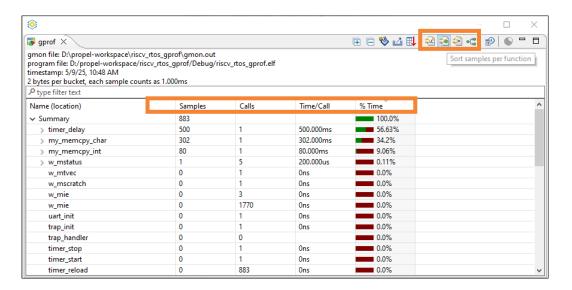

| Figure 5.32. gprof Viewer                                                                      |    |

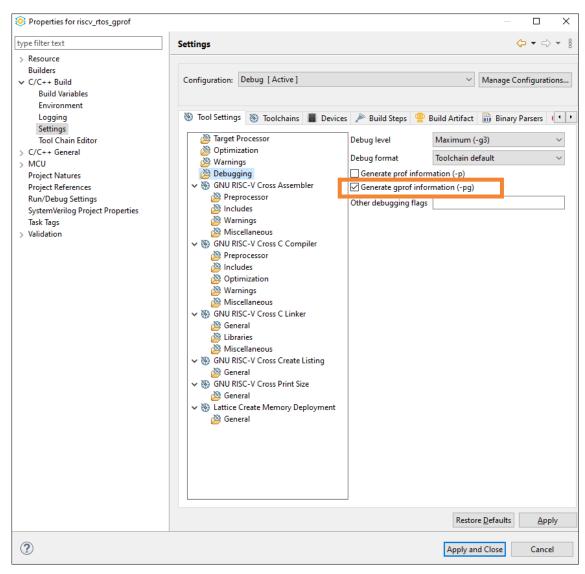

| Figure 5.33. Generate gprof Information Checkbox                                               |    |

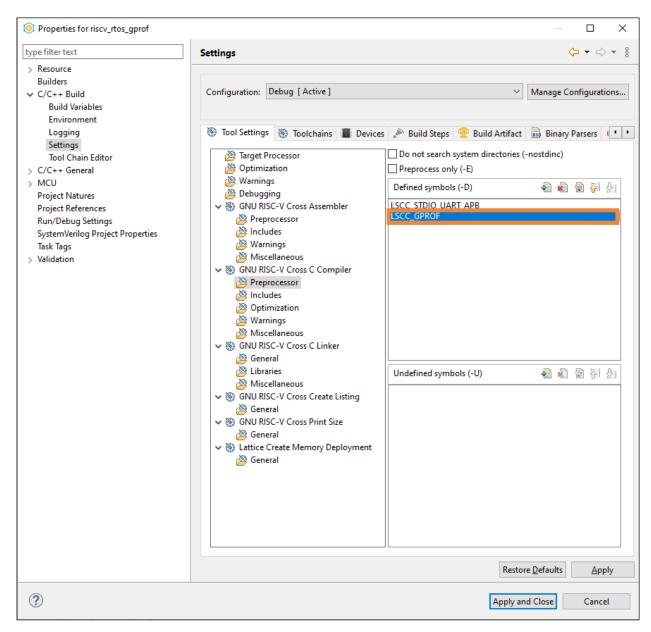

| Figure 5.34. LSCC_GPROF Symbol                                                                 |    |

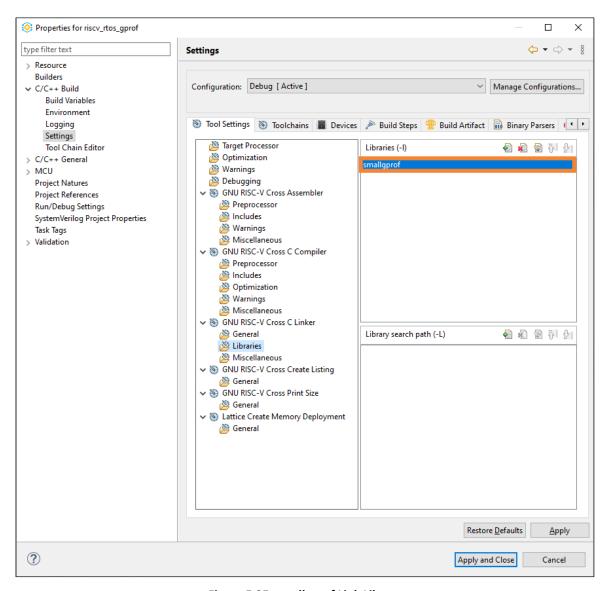

| Figure 5.35. smallgprof Link Library                                                           |    |

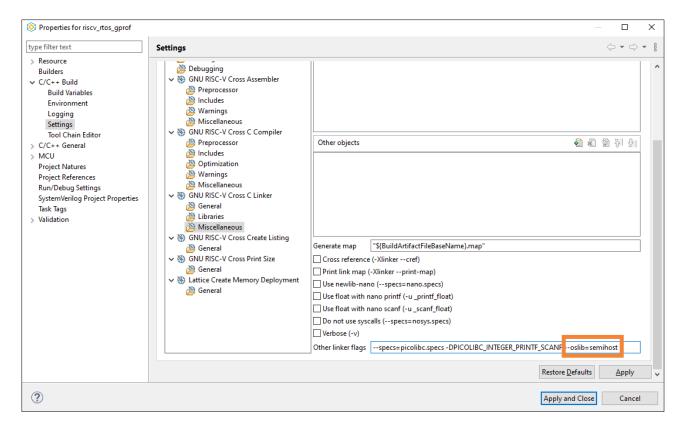

| Figure 5.36oslib=semihost Linker Flag                                                          |    |

| Figure 5.37HEAP_SIZE in Linker Script File                                                     | 77 |

|                                                                                                |    |

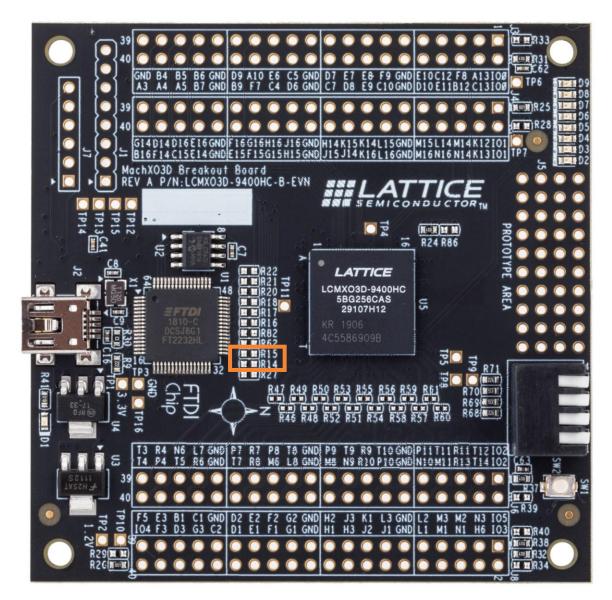

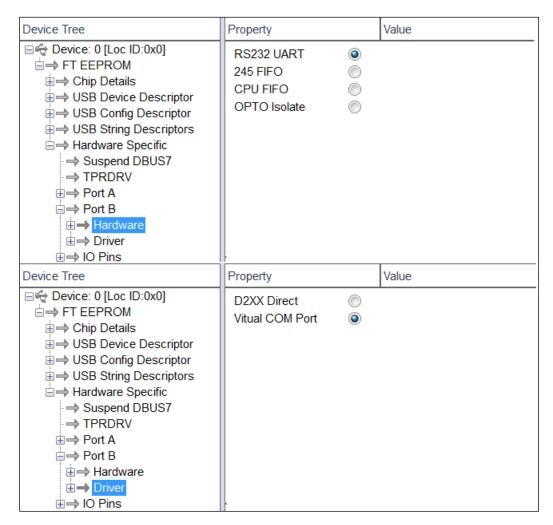

| Figure 6.1. MachXO3D Breakout Board                                                   | 78  |

|---------------------------------------------------------------------------------------|-----|

| Figure 6.2. Configuring the FTDI Device                                               | 79  |

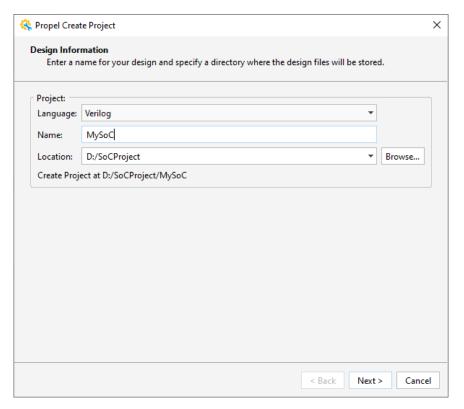

| Figure 6.3. Design Information Settings                                               | 80  |

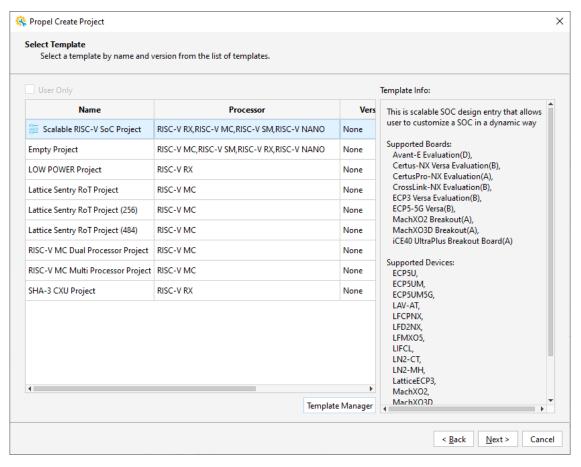

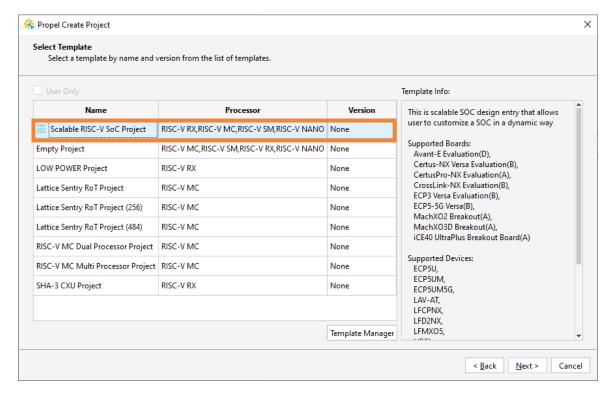

| Figure 6.4. Select Template Page                                                      |     |

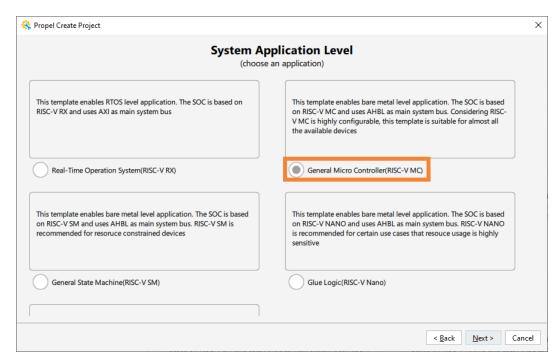

| Figure 6.5. Selecting General Micro Controller RISC-V MC for System Application Level | 81  |

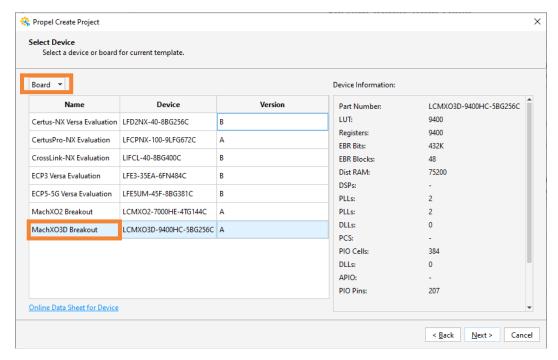

| Figure 6.6. Selecting MachXO3D Breakout Board                                         | 81  |

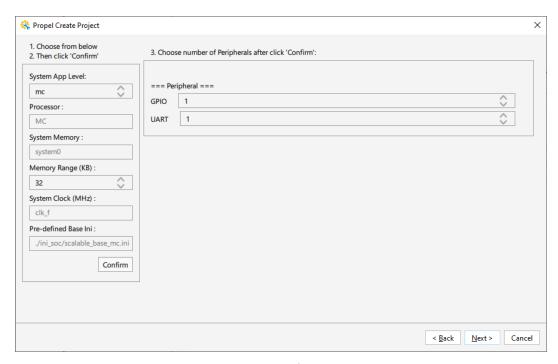

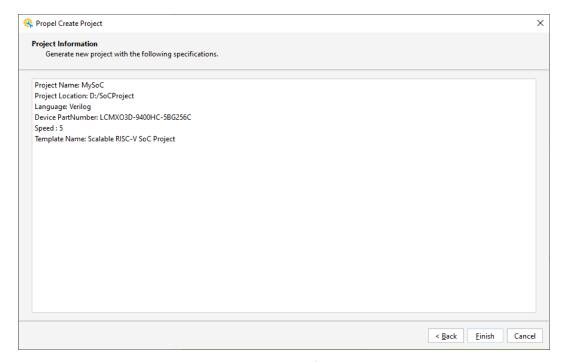

| Figure 6.7. Confirm Page                                                              | 82  |

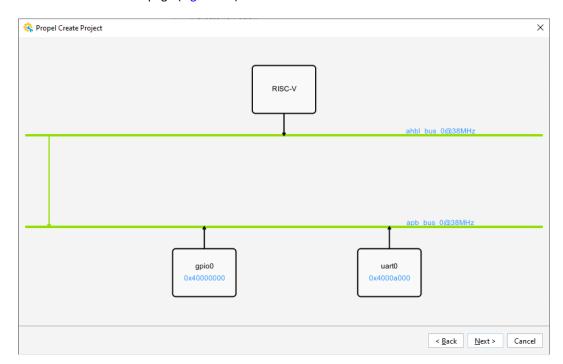

| Figure 6.8. Architecture Page                                                         | 82  |

| Figure 6.9. Project Information                                                       | 83  |

| Figure 6.10. Project Workbench                                                        | 83  |

| Figure 6.11. Creating a C/C++ Project                                                 | 84  |

| Figure 6.12. Build Result of HelloWorld C Project                                     |     |

| Figure 6.13. Configuring System Memory Module 2                                       |     |

| Figure 6.14. Generating the Programming File                                          |     |

| Figure 6.15. Generating the Programming File Successfully                             |     |

| Figure 6.16. Programmer Getting Started Dialog                                        | 87  |

| Figure 6.17. Programmer Window                                                        | 87  |

| Figure 6.18. Debug Configurations Dialog 2                                            |     |

| Figure 6.19. Run Result of Hello World Project                                        | 88  |

| Figure 7.1. Create SoC Project Wizard                                                 |     |

| Figure 7.2. Load System and BSP Page 3                                                | 90  |

| Figure 7.3. Debug Configurations Dialog 3                                             | 91  |

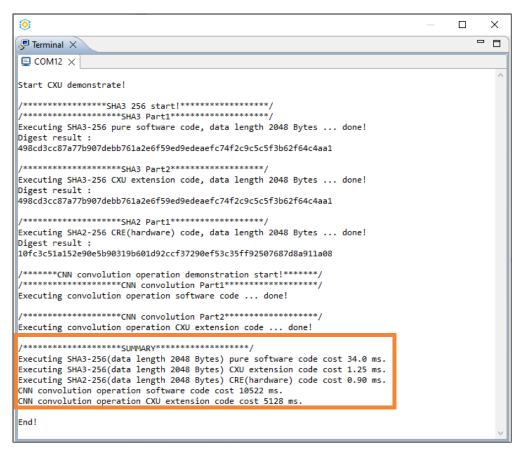

| Figure 7.4. Terminal Logs                                                             | 92  |

| Figure 7.5. Console Logs 1                                                            | 93  |

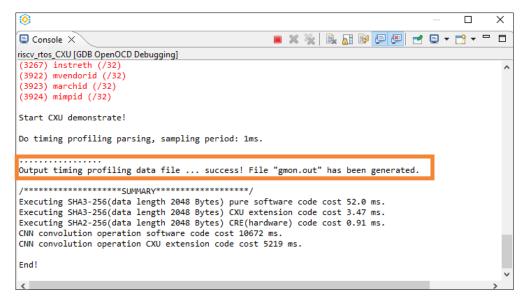

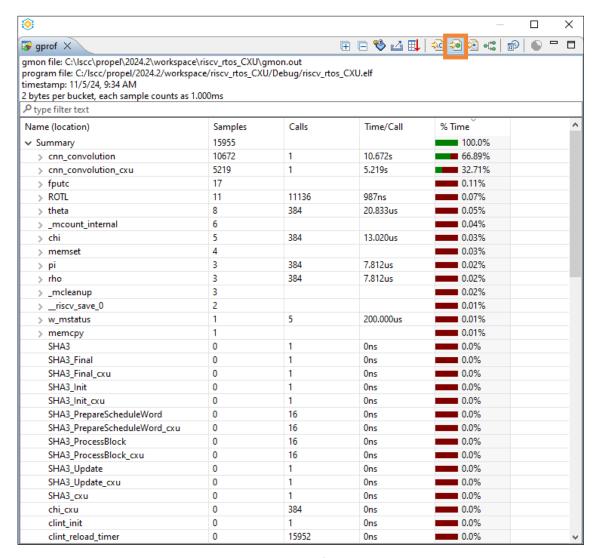

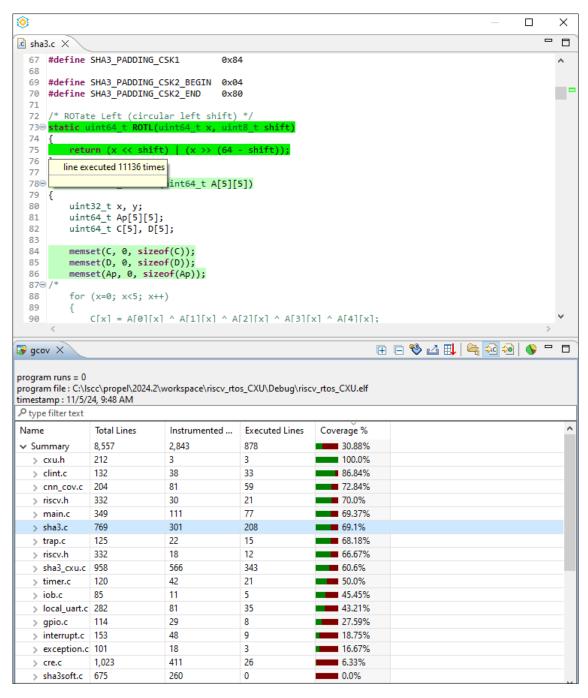

| Figure 7.6. gprof Viewer                                                              | 93  |

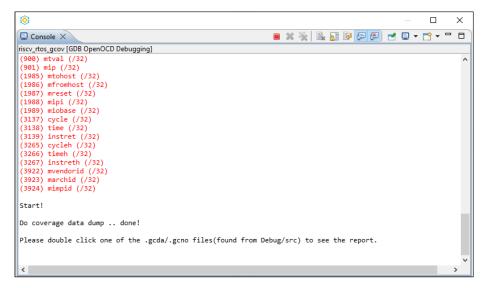

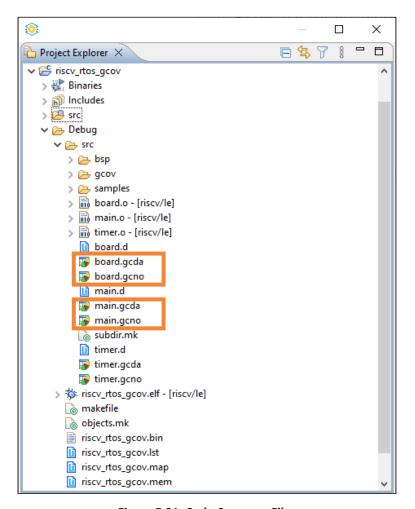

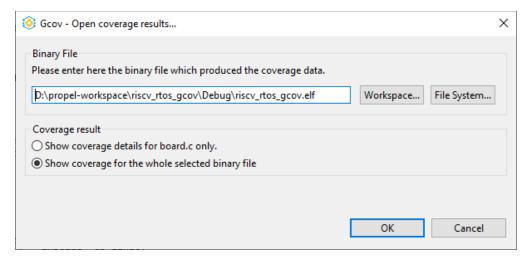

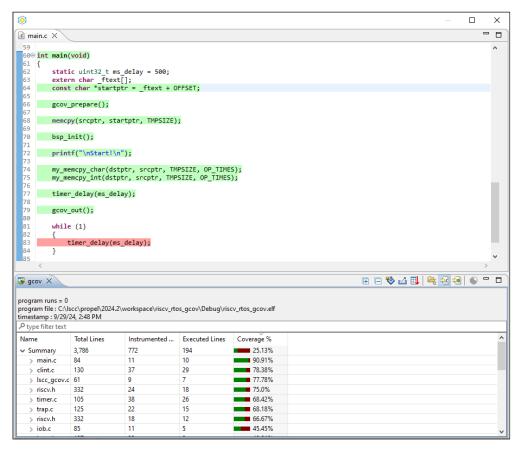

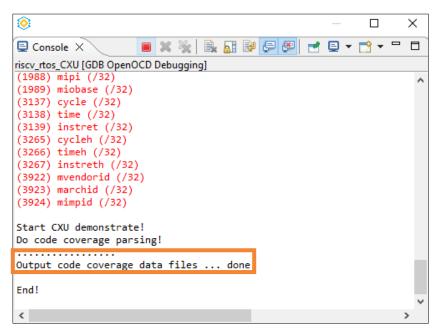

| Figure 7.7. Console Logs 2                                                            | 94  |

| Figure 7.8. gcov Viewer                                                               | 95  |

| Figure 8.1. Load System and BSP Page 4                                                | 96  |

| Figure 8.2. Build Console                                                             | 97  |

| Figure 8.3. Debug Configurations Dialog 4                                             | 98  |

| Figure 8.4. QUMU C Project Running Windows                                            |     |

| Figure 9.1. Bootloader Purpose                                                        | 99  |

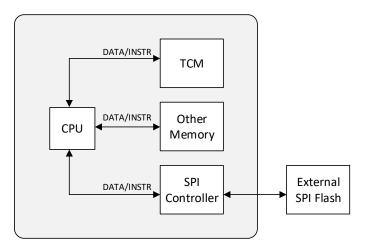

| Figure 9.2. SoC Architecture                                                          |     |

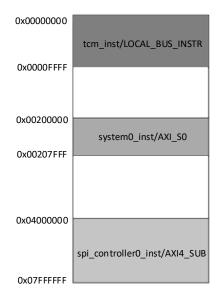

| Figure 9.3. SoC Memory Space                                                          |     |

| Figure 9.4. Create the Firmware for RAM Mode – List                                   |     |

| Figure 9.5. Create the Firmware for RAM Mode – linker.ld                              | 101 |

| Figure 9.6. Create the Firmware – Settings                                            | 102 |

| Figure 9.7. Create the Firmware for RAM Mode – Firmware File                          | 103 |

| Figure 9.8. Create the Firmware for RAM Mode – Program Bin File                       | 103 |

| Figure 9.9. Bootloader for RAM Mode – List                                            | 104 |

| Figure 9.10. Bootloader for RAM Mode – Log                                            | 104 |

| Figure 9.11. Create the Firmware for XIP Mode – List                                  | 105 |

| Figure 9.12. Create the Firmware for XIP Mode – linker.ld 1                           |     |

| Figure 9.13. Create the Firmware for XIP Mode – linker.ld 2                           |     |

| Figure 9.14. Create the Firmware for XIP Mode – Firmware File                         | 107 |

| Figure 9.15. Create the Firmware for XIP Mode – Program Bin File                      | 107 |

| Figure 9.16. Bootloader for XIP Mode – List                                           | 108 |

| Figure 9.17. Bootloader for XIP Mode – Log                                            | 109 |

| Figure A.1. Memory Regions in Linker Script                                           |     |

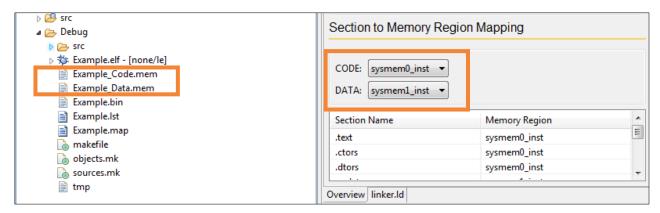

| Figure A.2. Section to Memory Region Mapping                                          |     |

| Figure A.3. Linker Script and Generated Memory Files                                  |     |

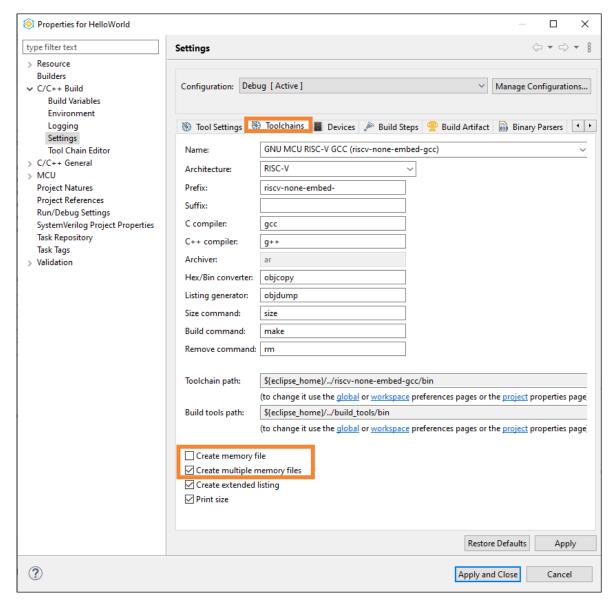

| Figure A.4. Toolchains Tab of C/C++ Build Settings                                    |     |

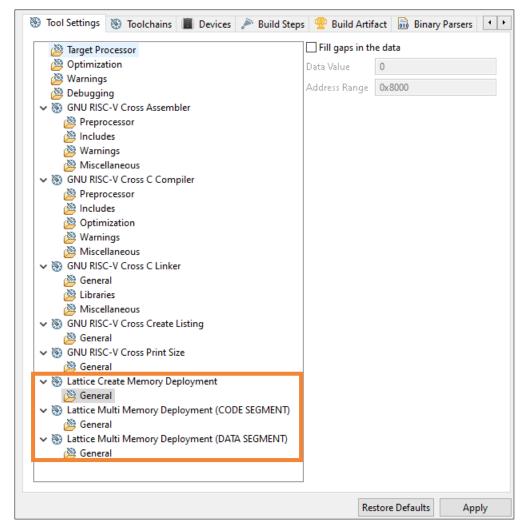

| Figure A.5. Tool Settings Tab of C/C++ Build Settings                                 |     |

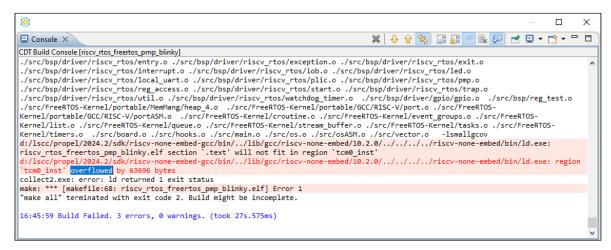

| Figure A.6. Build Project Console 1                                                   | 113 |

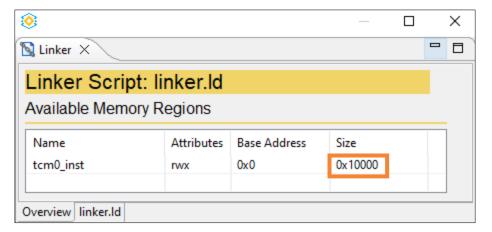

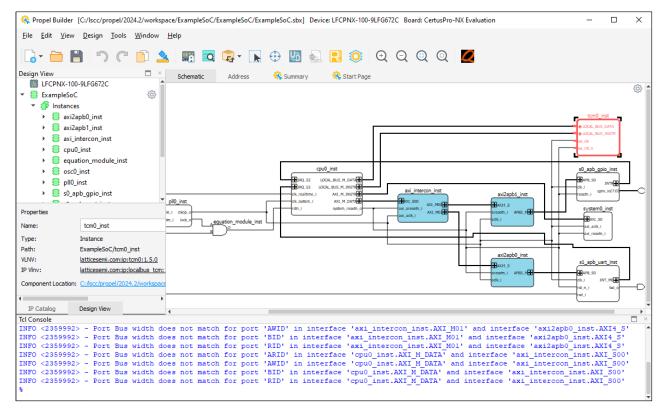

| Figure A.7. Linker Script                                       | 114 |

|-----------------------------------------------------------------|-----|

| Figure A.8. Corresponding SoC Project                           | 115 |

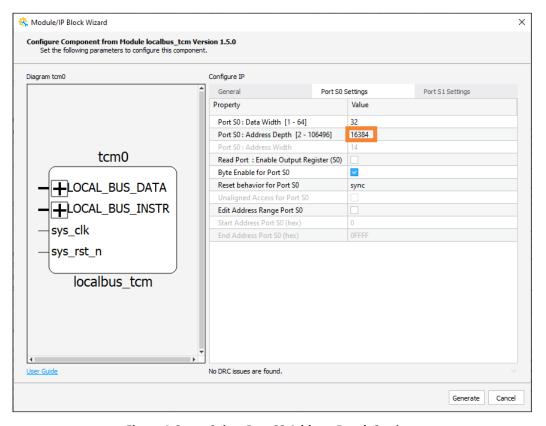

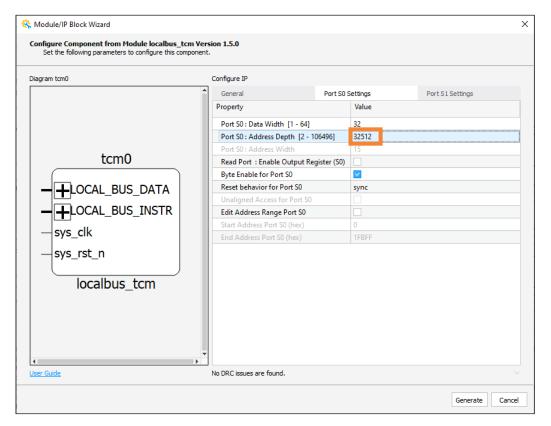

| Figure A.9. tcm0_inst Port S0 Address Depth Settings            | 115 |

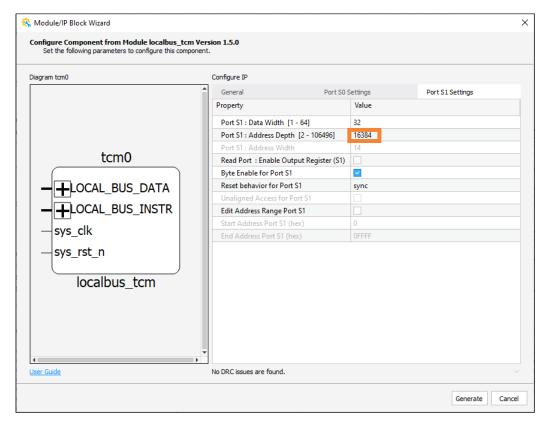

| Figure A.10. tcm0_inst Port S1 Address Depth Settings           | 116 |

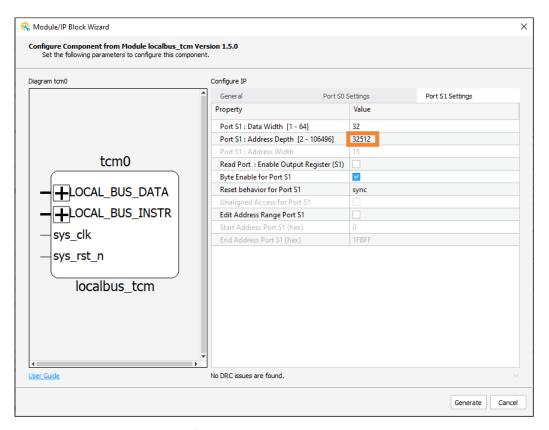

| Figure A.11. Modifying tcm0_inst Port SO Address Depth Settings | 116 |

| Figure A.12. Modifying tcm0_inst Port S1 Address Depth Settings |     |

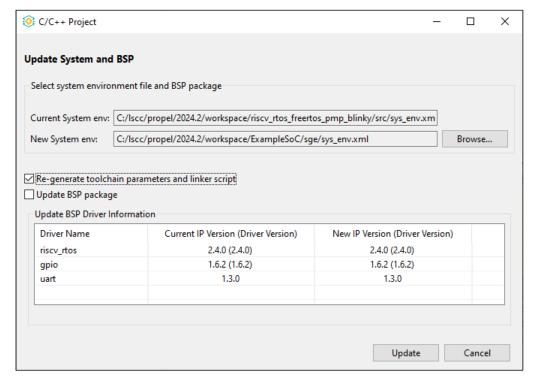

| Figure A.13. Updating System and BSP                            | 117 |

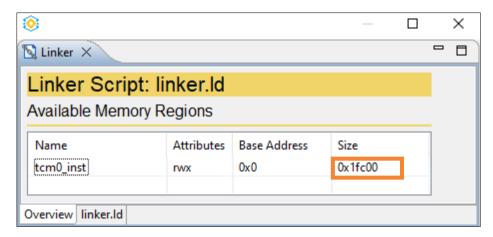

| Figure A.14. Updated Linker Script                              | 118 |

| Figure A.15. Build Project Console 2                            | 118 |

| Figure B.1. Lattice Toolchain Setting Dialog 2                  | 120 |

| Figure B.2. Properties of C/C++ Project – Compiler Options      | 120 |

| Figure B.3. Properties of C/C++ Project – Linker Options        | 121 |

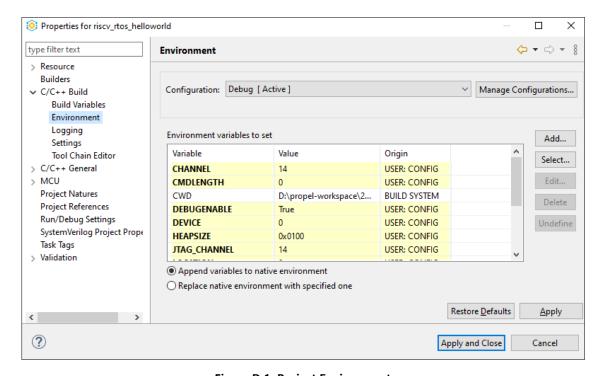

| Figure D.1. Project Environment                                 | 123 |

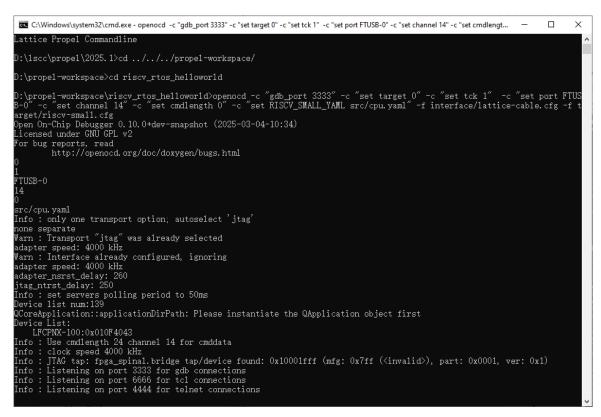

| Figure D.2. Launching openOCD                                   | 124 |

| Figure D.3. Launching GDB                                       |     |

| Figure D.4. GDB Debugging Window                                | 125 |

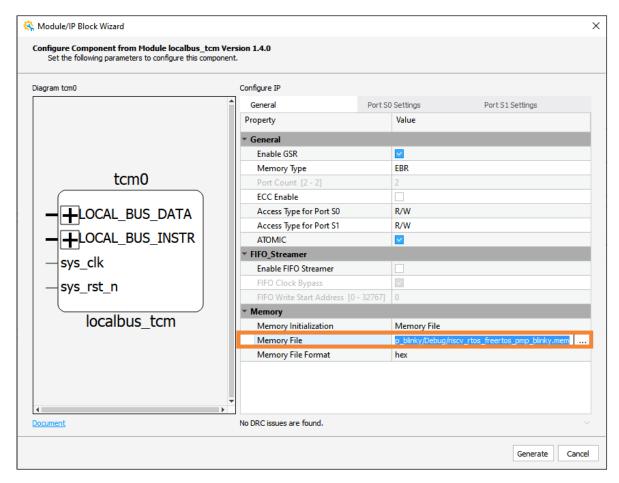

| Figure E.1. Setting Memory Initialization File                  | 126 |

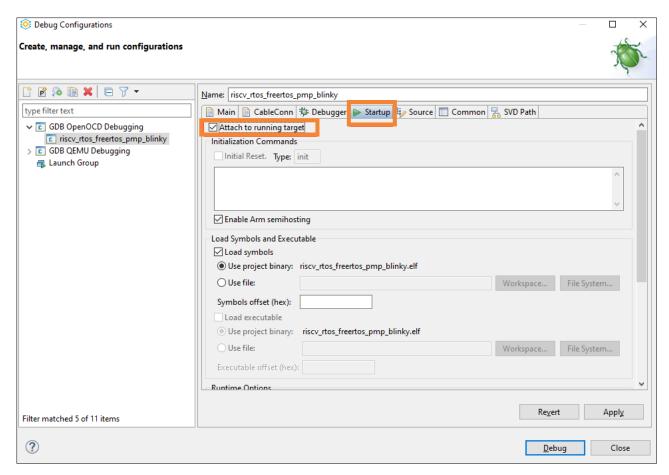

| Figure E.2. Debug Configurations Dialog 5                       | 127 |

| Figure E.3. Debug Perspective 2                                 | 128 |

| Figure E.4. Restore Defaults Operation                          | 129 |

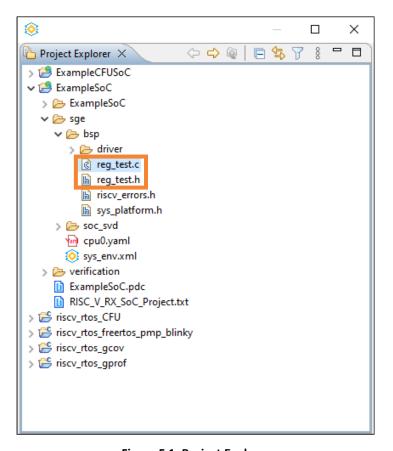

| Figure F.1. Project Explorer                                    | 130 |

| Figure F.2. Register Test Code                                  | 131 |

| Figure F.3. Load System and BSP Page 5                          | 132 |

| Figure F.4. Test Entrance                                       |     |

| Figure F.5. Enabling Test Code                                  | 134 |

| Figure F.6. Success Log                                         | 134 |

| Figure F.7. Failure Log                                         | 135 |

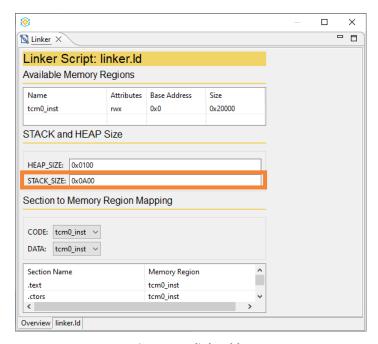

| Figure G.1. linker.ld 1                                         | 136 |

| Figure G.2. C Code                                              | 136 |

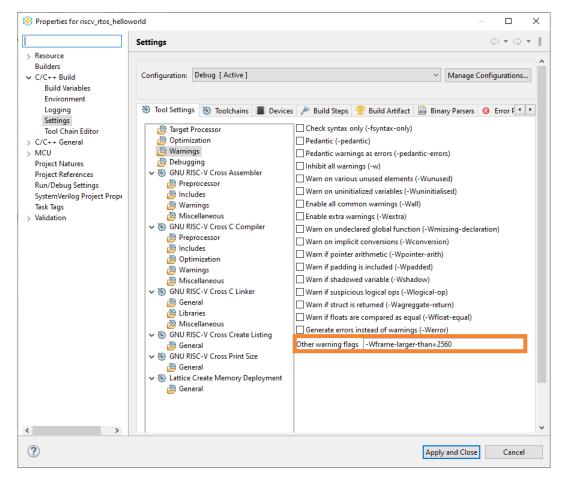

| Figure G.3. Warnings Settings 1                                 | 137 |

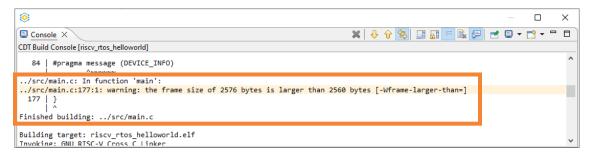

| Figure G.4. Warning Message                                     | 137 |

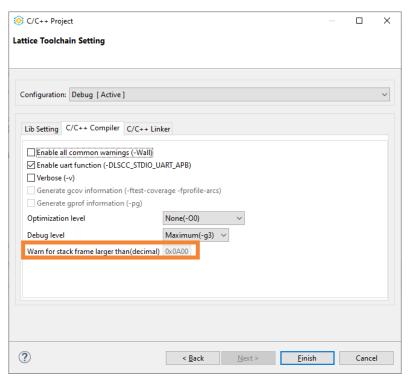

| Figure G.5. Toolchain Setting GUI 1                             | 138 |

| Figure G.6. Toolchain Setting GUI 2                             |     |

| Figure G.7. Warnings Settings 2                                 | 139 |

| Figure G.8. linker.ld 2                                         | 139 |

| Figure H.1. GDB Console 1                                       |     |

| Figure H.2. GDB Console 2                                       | 142 |

| Figure H.3. GDB Console 3                                       | 143 |

| Figure H.4. Closing Unrelated Projects                          | 144 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                                                                                                                                             |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASCII        | American Standard Code for Information Interchange                                                                                                                     |

| BSP          | Board Support Package. The layer of software containing hardware-specific drivers and libraries to function in a particular hardware environment.                      |

| CXU          | Composable Extension Unit                                                                                                                                              |

| CDT          | C/C++ Development Tools                                                                                                                                                |

| CLINT        | Core Local Interruptor                                                                                                                                                 |

| CNN          | Convolutional Neural Network                                                                                                                                           |

| CPU          | Central Processing Unit                                                                                                                                                |

| DUT          | Design Under Test                                                                                                                                                      |

| GUI          | Graphical User Interface                                                                                                                                               |

| XIP          | Execute in Place                                                                                                                                                       |

| FD-SOI       | Fully-Depleted Silicon On Insulator                                                                                                                                    |

| FMC          | FPGA Mezzanine Card                                                                                                                                                    |

| FPGA         | Field Programmable Gate Array                                                                                                                                          |

| FreeRTOS     | A market-leading RTOS for microcontrollers and small microprocessors                                                                                                   |

| FTDI         | Future Technology Devices Intl.Ltd                                                                                                                                     |

| GPTIMER      | General-Purpose Timer                                                                                                                                                  |

| GRUB         | Grand Unified Bootloader                                                                                                                                               |

| HDL          |                                                                                                                                                                        |

| HPC          | Hardware Description Language                                                                                                                                          |

| IBIS         | High Pin Connector                                                                                                                                                     |

|              | Input Output Buffer Information System                                                                                                                                 |

| IDE          | Integrated Development Environment                                                                                                                                     |

| I2C          | Inter-Integrated Circuit                                                                                                                                               |

| IP ICP       | Intellectual Property                                                                                                                                                  |

| ISR          | Interrupt Service Routine                                                                                                                                              |

| JEDEC        | Joint Electron Device Engineering Council                                                                                                                              |

| JTAG         | Joint Test Action Group                                                                                                                                                |

| MSIP         | Micro-Controller Unit                                                                                                                                                  |

|              | Machine-Mode Software Interrupt                                                                                                                                        |

| OCD          | On-Chip-Debugging                                                                                                                                                      |

| OEM          | Original Equipment Manufacturer                                                                                                                                        |

| OpenOCD      | Open On-Chip Debugger                                                                                                                                                  |

| OS           | Operation System                                                                                                                                                       |

| PC           | Personal Computer                                                                                                                                                      |

| PIC          | Programmable Interrupt Controller                                                                                                                                      |

| PLIC         | Platform-Level Interrupt Controller                                                                                                                                    |

| PMOD         | Peripheral Module                                                                                                                                                      |

| QEMU         | A generic and open-source machine emulator and virtualizer                                                                                                             |

| RAM          | Random-Access Memory                                                                                                                                                   |

| RISC-V       | Reduced Instruction Set Computer-V. A free and open instruction set architecture (ISA) enabling a new era of processor innovation through open standard collaboration. |

| RISC-V MC    | Lattice RISC-V for Micro-Controller Soft IP                                                                                                                            |

| RISC-V RX    | Lattice RISC-V for RTOS Soft IP                                                                                                                                        |

| RISC-V SM    | Lattice RISC-V for State-Machine Soft IP                                                                                                                               |

| RTOS         | Real Time Operating System                                                                                                                                             |

| Abbreviation | Definition                                                                                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX           | RISC-V for RTOS applications                                                                                                                                  |

| SDK          | Software Development Kit. A set of software development tools that allows the creation of applications for software package on the Lattice embedded platform. |

| SHA          | Secure Hash Algorithm                                                                                                                                         |

| SoC          | System-on-Chip. An integrated circuit that integrates all components of a computer or other electronic systems.                                               |

| SPI          | Serial Peripheral Interface                                                                                                                                   |

| SRAM         | Static Random Access Memory                                                                                                                                   |

| UART         | Universal Asynchronous Receiver/Transmitter                                                                                                                   |

| UFM          | User Flash Memory                                                                                                                                             |

| UI           | User Interface                                                                                                                                                |

| VHDL         | Very-High-Speed Integrated Circuit Hardware Description Language                                                                                              |

| WDT          | Watch Dog Timer                                                                                                                                               |

# 1. Introduction

Lattice Propel™ design environment is a complete set of graphical and command-line tools to create, analyze, compile, and debug both FPGA-based hardware and software processor systems.

# 1.1. Purpose

Embedded system solutions play an important role in FPGA system design, allowing you to develop software for a processor in an FPGA device. It provides the flexibility for you to control various peripherals from a system bus.

To develop an embedded system on an FPGA, you need to design the System-on-Chip (SoC) with an embedded processor and develop system software on the processor. Lattice Propel helps you develop your system with a RISC-V processor, peripheral IP, and a set of tools.

The purpose of this document is to introduce Lattice Propel SDK tool and flow to help you quickly get started to build a small demo system. You can find recommended flows of using Lattice Propel SDK in this document as well.

#### 1.2. Audience

The intended audience for this document includes embedded system designers and embedded software developers using Lattice FPGA devices. The complete list of supported devices can be found in Lattice Propel Release Notes. The technical guidelines assume readers have expertise in the embedded system area and FPGA technologies.

# 2. Lattice Propel Development Suite

Lattice Propel development suite includes:

- an integrated development environment (IDE), which is the framework of the Lattice Propel design suite;

- Lattice Propel Builder, which is for SoC design;

- Lattice Propel SDK, which is for system software development.

# 2.1. Eclipse IDE

Eclipse IDE provides the Lattice Propel development suite a platform to manage the SoC project and the Embedded C/C++ Project in the same workspace.

The SoC project, which extends from the Lattice Propel Builder project, provides easy interaction with other Lattice design tools, such as the Lattice Diamond™ software within Lattice Propel design environment.

The Embedded C/C++ Project provides a platform for developing or debugging application code within Eclipse IDE. The project can be created directly from the SoC project with a pre-set Board Support Package (BSP) and applications by using the Lattice Propel development suite.

# 2.2. Lattice Propel Builder

Lattice Propel Builder allows you to assemble the larger functional blocks of the design hierarchy. Lattice Propel Builder enables you to instantiate modules and IP from the IP Catalog in a schematic view, and can easily connect the modules. Lattice Propel Builder also helps you customize address spaces within modules, such as a processor. In the Lattice Propel development suite, Lattice Propel Builder is used to create a microprocessor integrated platform for both hardware and software development.

Refer to Lattice Propel Builder 2025.2 User Guide (FPGA-UG-02243) for more detailed information.

# 2.3. Lattice Propel SDK

Lattice Propel SDK is based on Eclipse Embedded C/C++ Development Tools (CDT). It allows you to create, build, and debug software application projects that drive the platform within the Eclipse framework.

The main features are:

- Create, build, debug, or manage embedded applications for Lattice RISC-V CPU or SoC solution.

- Provide extra build steps to generate the binary and memory files required for deployment.

- Build using the latest industry standard open-source components and tools for RISC-V firmware development and debugging.

- Support Picolibc for RISC-V and provide lightweight standard library implementation.

- Provide fully-configurable toolchain definitions.

13

#### **Lattice Propel Tool Flows** 3.

The Lattice Propel tool flows including SoC project design flow, C/C++ project design flow, system simulation flow, and programming and On-Chip-Debugging (OCD) flow, are discussed in detail in the following sections.

# 3.1. Lattice Propel Environment

#### 3.1.1. Running Lattice Propel

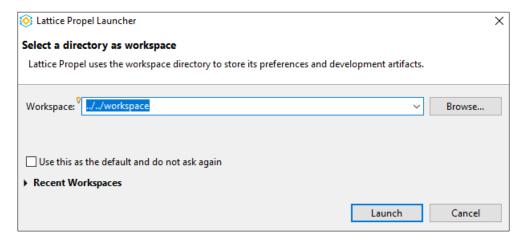

After installing the Lattice Propel software, you can launch Lattice Propel SDK from the desktop shortcut icon or from the Windows Start menu. When Lattice Propel SDK is invoked, a dialog (Figure 3.1) pops up. You can browse to select where to locate the workspace. For normal needs, simply click Launch to pick the default location and continue running Lattice Propel SDK.

Figure 3.1. Select Workspace Dialog

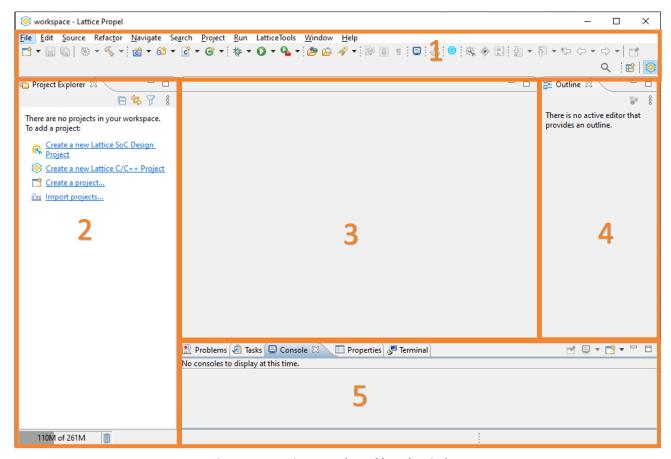

After the workspace location is chosen, a single workbench window is displayed using default Lattice Propel SDK perspective. The default Lattice Propel SDK perspective contains the following five functional areas (Figure 3.2).

Note: A perspective is a group of views and editors in the Workbench window. A workspace is the directory where stores your work and it is used as the default content area for your projects as well as for holding any required metadata. A workbench is the desktop development environment in Eclipse IDE platform.

- Menu bar and Toolbar, including: File menu, Edit menu, Source menu, Refactor menu, Navigate menu, Search menu, Project menu, Run menu, LatticeTools menu, Window menu, and Help menu.

- 2. Project Explorer view: displays projects in the workspace.

- 3. Editor view: provides capability of editing source files.

- 4. Outline view: displays an outline of a file that is currently open in the editor area.

- 5. Log area includes these views: Problem view, Tasks view, Console view, Properties view, and Terminal view.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.2. Lattice Propel Workbench Window

# 3.1.2. Importing Lattice SoC Design Projects

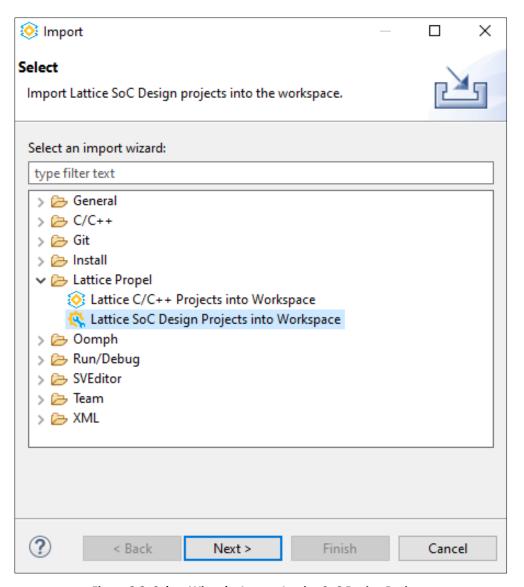

In Lattice Propel SDK, you can use the Import Wizard to import Lattice SoC design projects into workspace. Existing SoC design projects created by either Lattice Propel SDK or Lattice Propel Builder can also be imported into Workspace by choosing **Lattice Propel > Lattice SoC Design Projects**.

From Lattice Propel SDK, choose File > Import....

The Select wizard opens (Figure 3.3).

Figure 3.3. Select Wizard – Import Lattice SoC Design Projects

Select Lattice Propel > Lattice SoC Design Projects into Workspace. Click Next.

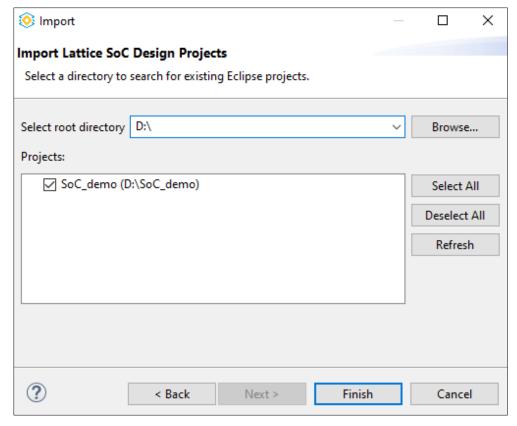

The Select wizard switches to Import Lattice SoC Design Projects wizard page (Figure 3.4).

Figure 3.4. Import Lattice SoC Design Projects Wizard

- 3. Locate the directory containing the projects by clicking the **Browse** button.

- 4. In **Projects** area, select the SoC design project or projects you want to import.

- 5. Click **Finish** to start the importing process.

## 3.1.3. Importing Lattice C/C++ Projects

In Lattice Propel SDK, you can use the Import Wizard to import existing Lattice C/C++ projects created by Lattice Propel SDK 2023.2 or later into workspace by choosing Lattice Propel > Lattice C/C++ Projects.

From Lattice Propel SDK, choose File > Import....

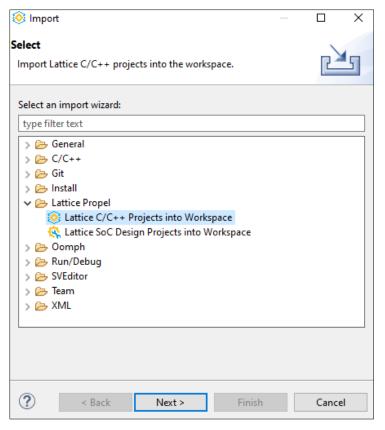

The Select wizard opens (Figure 3.5).

Figure 3.5. Select Wizard – Import Lattice C/C++ Projects

Select Lattice Propel > Lattice C/C++ Projects into Workspace. Click Next.

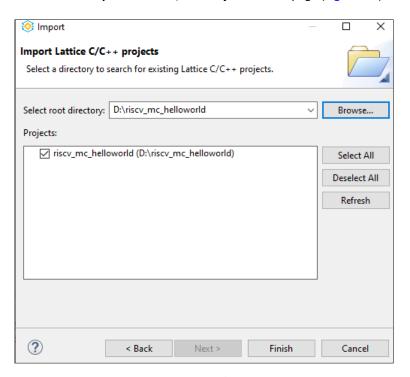

The Select wizard switches to the Import Lattice C/C++ Projects wizard page (Figure 3.6).

Figure 3.6. Import Lattice C/C++ Projects Wizard

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.1.4. Creating Customized C/C++ Templates

In Lattice Propel SDK, you can select a Lattice C/C++ project in the current workspace to create a user application template for creating new Lattice C/C++ project.

Note: You must use this template management function on Lattice Propel SDK 2024.2 or later.

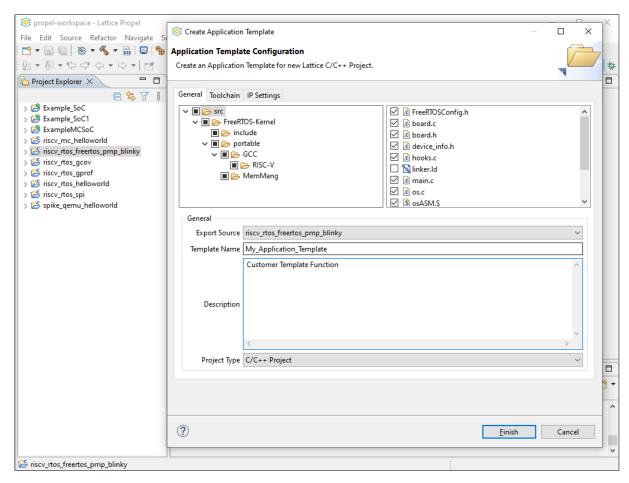

From Lattice Propel SDK, select a C/C++ project and choose Project > Create Lattice Application Template. The Create Application Template wizard opens Figure 3.7.

Figure 3.7. Create Application Template - General

2. You can input Template name, Description, Toolchain Configurations, IP Settings, and so on, and select files for creating template.

#### Notes:

- Under the General tab (Figure 3.7), select project code files, all files except linker.ld are checked. It is recommended to keep these selections to avoid potential errors in building.

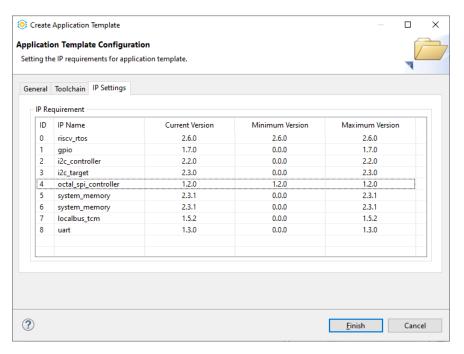

- Under the IP Settings tab (Figure 3.8), Propel SDK generates a filter according to your settings. This means if you create a C/C++ project using this C/C++ template, the corresponding SoC project should include the versions of IPs shown in the IP Settings tab. Be careful when modifying the IP-related settings under this tab. If these settings are not set properly, you might encounter errors when using these templates on other versions of Lattice Propel SDK.

- 3. Click Finish.

Figure 3.8. Create Application Template - IP Settings

# 3.1.5. Exporting and Deploying Customized C/C++ Templates

In Lattice Propel SDK, you can export customized C/C++ templates into a single ZIP archive that is ready for deployment in other users' Lattice Propel SDK environments.

**Note:** You must use this template management function on Propel SDK 2024.2 or later.

1. From Lattice Propel SDK, choose File > Export....

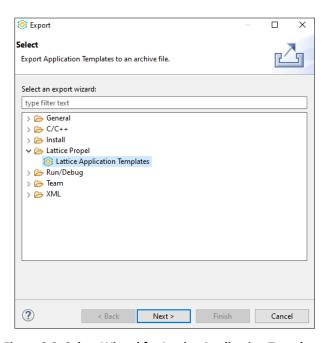

The **Select** wizard opens (Figure 3.9).

Figure 3.9. Select Wizard for Lattice Application Templates

2. Select Lattice Propel > Lattice Application Templates. Click Next.

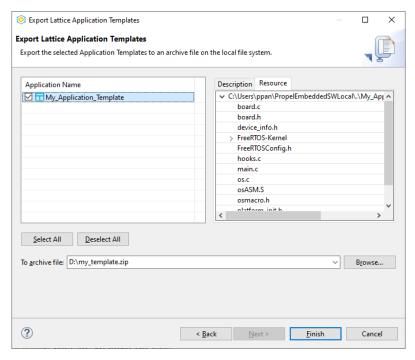

The Select wizard switches to the Export Lattice Application Templates wizard page (Figure 3.10).

Figure 3.10. Export Lattice Application Templates Wizard

- 3. You can locate the destination directory by clicking the **Browse** button.

- 4. In the Application Name area, select the application templates you want to export.

- Click Finish to start the exporting process.

The exported zip archive file is ready to be delivered to other Lattice Propel SDK users.

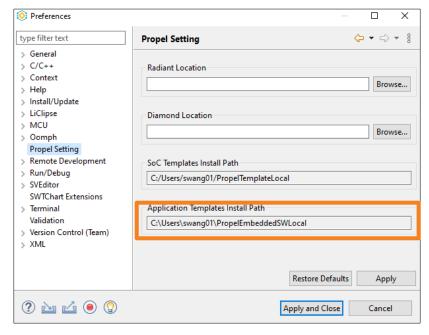

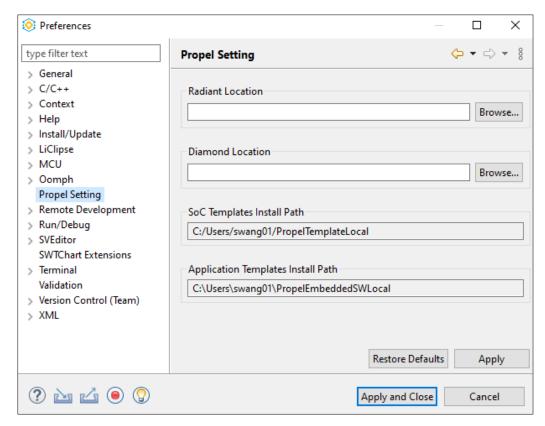

- 6. With this zip archive file, extract it to the **Application Templates Install Path** in the user's environment. Select **Window** > **Preferences** > **Propel Setting** to find this setting (Figure 3.11).

Figure 3.11. Lattice Propel Setting Page

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.2. SoC Project Design Flow

A new SoC design project including a Lattice Propel Builder design can be started from the Lattice Propel sets. Follow steps below to create a new SoC design project.

**Note:** The SoC project templates are gradually being migrated to the new scalable SoC project templates that are only available from Lattice Propel Builder. If the following flow for creating an SoC design project is unreachable, create it from Lattice Propel Builder. See Lattice Propel Builder 2025.2 User Guide (FPGA-UG-02243) for more details.

## 3.2.1. Creating an SoC Design Project (Deprecated)

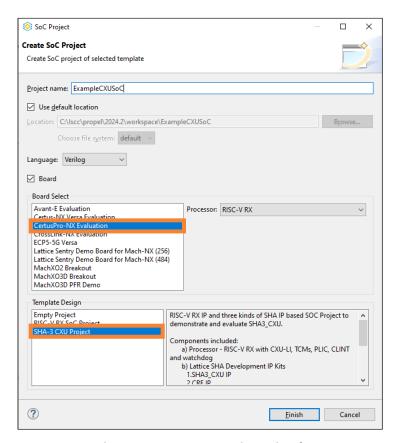

To start a Lattice SoC design project from Lattice Propel SDK:

- In Lattice Propel SDK, choose File > New > Lattice SoC Design Project.

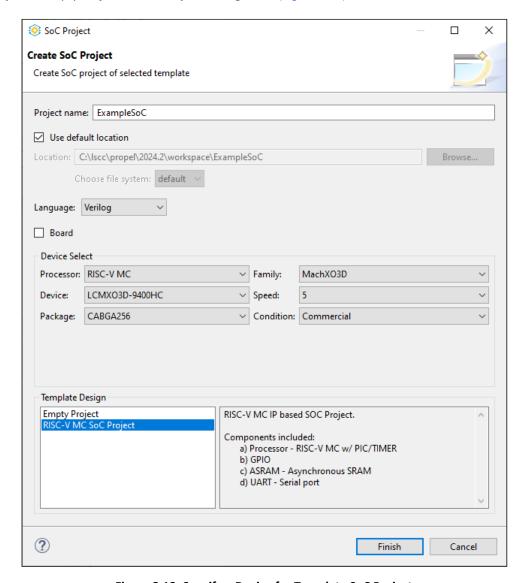

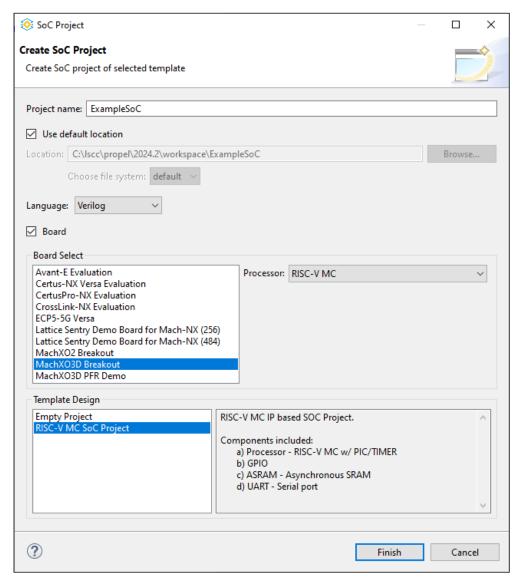

The Create SoC Project wizard opens (Figure 3.12). In the Create SoC Project wizard, you can specify a device or a board for a Template SoC project.

- To specify a device for your new Template SoC project, use the drop-down menu to select the desired device

information, including Processor, Family, Device, Package, Speed, and Condition. Also, select RISC-V SoC

Project or Empty Project in the Template Design field (Figure 3.12).

Figure 3.12. Specify a Device for Template SoC Project

Or, to specify a board for a new Template SoC project, check the Board checkbox (Figure 3.13).

Note: You can choose VHDL/Verilog in the Language field.

Figure 3.13. Specify a Board for Template SoC Project

- 2. From the **Board Select** area, select the desired board, such as the MachXO3D™ Breakout Board.

- 3. Enter a project name.

- **Note:** Do not include periods, colons, or spaces in the project name.

- 4. (Optional) To change the default location, clear the **Use default location** option, then browse for another location. Choose a file system.

- 5. Select a desired platform template design. In particular, select **Empty Project** for building system from scratch.

- 6. Click Finish.

- The SoC design project is created in the workbench, and its design is opened and displayed in Lattice Propel Builder (Figure 3.16).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 3.2.2. Opening an SoC Design in Lattice Propel Builder

Within an SoC project, there is a Lattice Propel Builder design.

To open Lattice Propel Builder for an SoC project:

- 1. In the **Project Explorer** view, select an SoC project.

- 2. Open the SoC project in one of the following ways from Lattice Propel SDK:

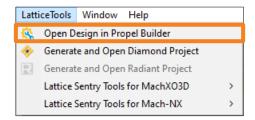

- Choose LatticeTools > Open Design in Propel Builder (Figure 3.14).

Figure 3.14. LatticeTools Menu

- Click the Lattice Propel Builder icon the toolbar.

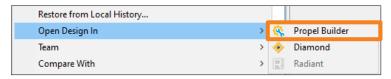

- Right-click the SoC project from Project Explorer. Choose Open Design In > Propel Builder from the pop-up menu (Figure 3.15).

Figure 3.15. Project Explorer Pop-up Menu

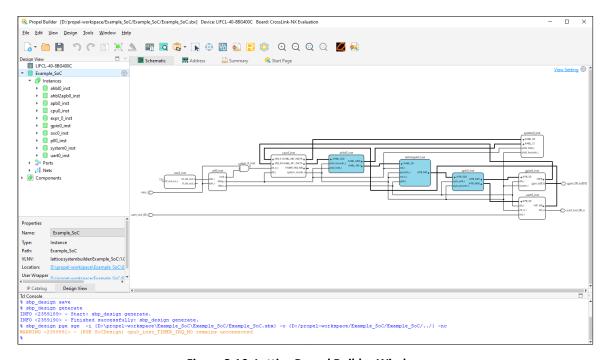

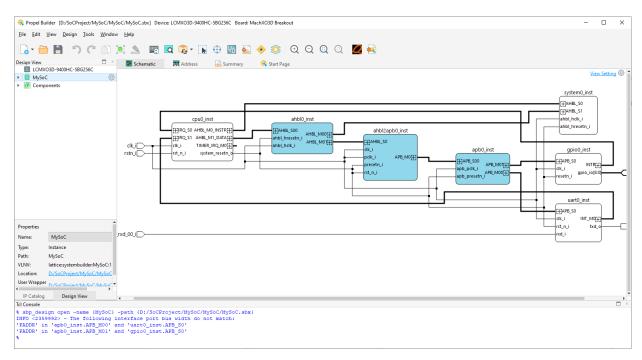

3. The SoC Design is opened and displayed in Lattice Propel Builder (Figure 3.16).

Figure 3.16. Lattice Propel Builder Window

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

4. (Optional) Modify the design in Lattice Propel Builder as desired. Most of the templates include a functional-ready SoC design.

**Note:** You can only create an SoC design using the **Empty Project** template inside Lattice Propel Builder. Refer to Lattice Propel 2025.2 Builder User Guide (FPGA-UG-02243) for more details on how to create an SoC design using the **Empty Project** template.

#### 3.2.3. Opening a Design in Lattice FPGA Design Software

Within an SoC project, you can create a Lattice FPGA design project including a Lattice Propel Builder design, and then open the FPGA design project in an appropriate software. There are two FPGA Design software available, the Lattice Diamond software and Lattice Radiant™ software. Depending on the device family used in the SoC project, only one of the FPGA Design software can be selected from the User Interface (UI), and the other is grayed out. If the MachXO3D or Mach™-NX device family is used, the Lattice Diamond software related menu items are active from the Lattice Propel UI. If the CrossLink™-NX or Certus™-NX device family is used, the Lattice Radiant software related menu items are active from the Lattice Propel UI.

To open FPGA Design Software for an SoC project from Lattice Propel SDK:

1. (Optional) Set Lattice FPGA design software installation location from Lattice Propel SDK. By default, Lattice Propel SDK can find the proper Lattice FPGA design software installation location, usually the latest version installed on the PC. You can overwrite it following steps below.

Choose Window > Preferences. The Preferences dialog opens (Figure 3.17).

Select **Propel Setting** from the left pane. Click the **Browse** button to pick up the installation location of the Lattice Diamond software or Lattice Radiant software. Or, leave the **Radiant Location** and **Diamond Location** fields blank, as default. Lattice Propel SDK can find the location automatically.

Figure 3.17. Lattice Propel Preferences Dialog

- 2. In the **Project Explorer** view from the Lattice Propel main Graphical User Interface (GUI), select an SoC project.

- 3. Open the SoC project in one of the following ways:

- Choose LatticeTools > Generate and Open Diamond Project. Or, choose LatticeTools > Generate and Open Radiant Project.

- Click the Lattice Diamond software icon or the Lattice Radiant software icon from the toolbar.

- Right-click an SoC project from the **Project Explorer**. Choose **Open Design In** > Diamond. Or, choose **Open Design In** > Radiant from the right-click menu.

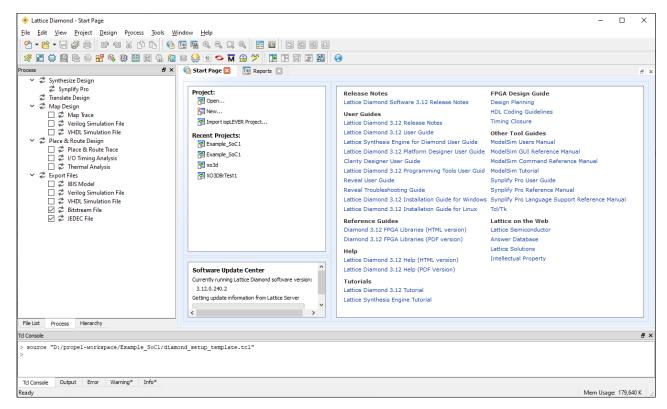

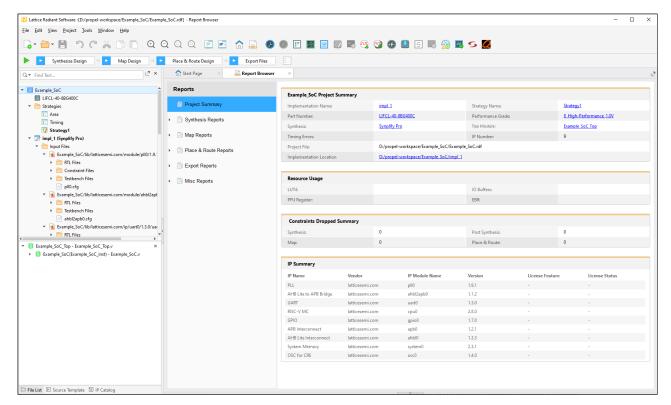

- 4. The Lattice Diamond or Radiant project for SoC is generated at background and is launched (Figure 3.18/ Figure 3.19).

Figure 3.18. Lattice Diamond Software Project

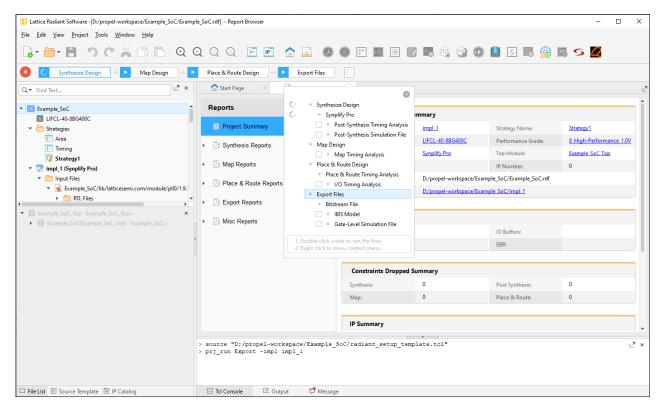

Figure 3.19. Lattice Radiant Software Project

- 5. (Optional) From the File List view of the Lattice Diamond or Radiant software:

- modify the top-level RTL file (<proj\_name>\_Top.v) to match the SoC design, presupposition of which is that there is a top-level RTL file in your SoC design; or

- create a top-level RTL file (<proj\_name>\_Top.v) to match the SoC design, if the SoC design is created from an Empty Project template and there is no top-level RTL file in your SoC design.

- 6. (Optional) Modify constraint file (<proj\_name>.lpf/<proj\_name>.pdc) to match the SoC design, if you have modified the SoC design.

- **Note:** This step is a must for the SoC design created from the Empty Project template.

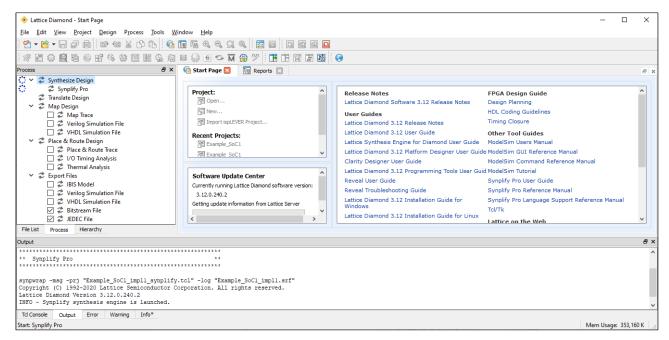

- 7. Process the design in the Lattice Diamond or Radiant software.

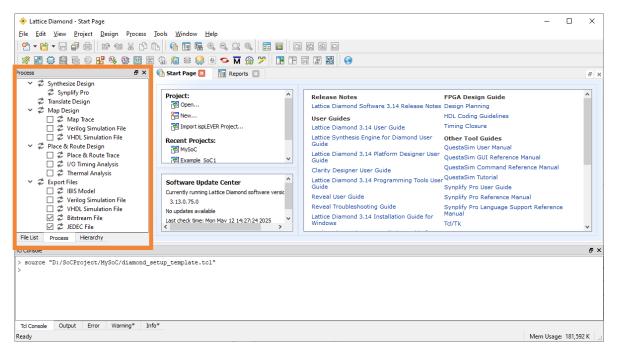

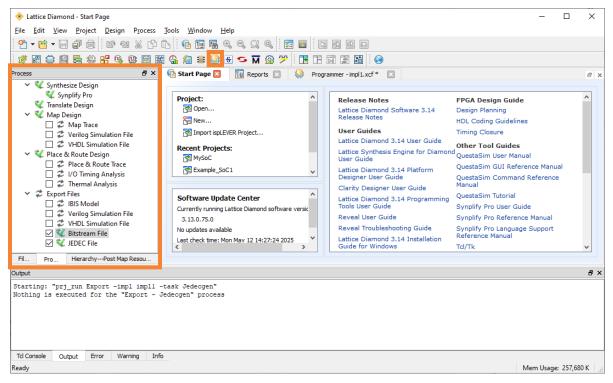

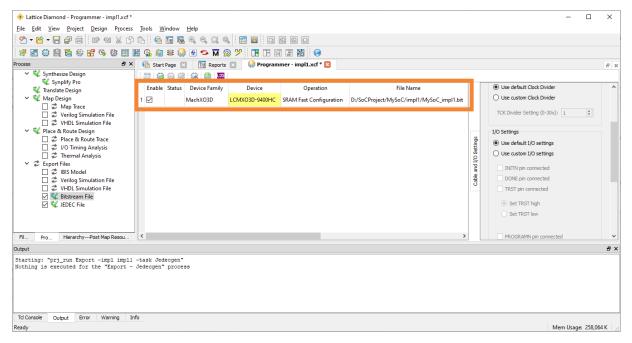

- In the Lattice Diamond software, switch to the **Process** view of the project (Figure 3.20). Make sure at least one file, IBIS Model, Verilog Simulation File, VHDL Simulation File, Bitstream File, or JEDEC file, is checked in the **Export Files** section for programming. Choose **Process** > Run.

Figure 3.20. Generate Programming File in Lattice Diamond Software

In Lattice Radiant software, from the Process Toolbar, click Export Files (Figure 3.21).

Figure 3.21. Generate Programming File in Lattice Radiant Software

The Programming file is generated. The programming file can be used in Programmer.

**Note:** Programmer is a tool that can program Lattice FPGA SRAM and external SPI Flash through various interfaces, such as JTAG, SPI, and I2C.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 3.2.4. Generating System Environment by Building Project

System environment package including the system environment file and the BSP package is required for the embedded C/C++ project.

To generate system environment package from Lattice Propel SDK:

- 1. In the **Project Explorer** view, select an SoC project.

- 2. Choose Project > Build Project.

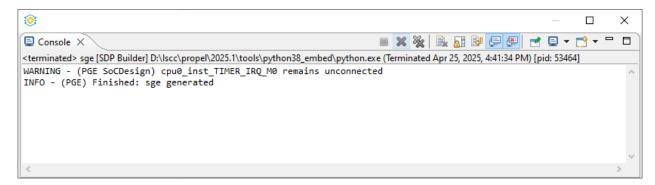

- 3. Check the building result in the **Console** view (Figure 3.22).

Figure 3.22. Build Result of SoC Project

#### 3.2.5. About SoC Design Project

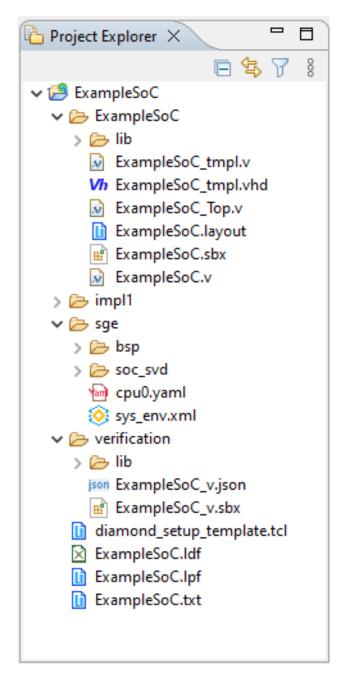

The SoC project creating starts with a functional-ready SoC design and a default simulation environment. In the **Project Explorer** view, open an SoC project folder and all its sub-folders. The project contains but is not limited to the following files (Figure 3.23), some of which may vary upon opening the SoC design project in the Lattice Diamond or Radiant software:

- roj\_name>: folder containing a Lattice Propel Builder design including the .sbx file.

- impl1: folder containing the implementation of the Lattice Diamond or Radiant project.

- sge: folder containing generated package necessary for creating a C/C++ project.

- verification: folder containing the SoC verification project.

- verification/sim: folder containing the simulation environment.

- <proj name>.ldf: Lattice Diamond project file.

- proj name>.lpf: Lattice Diamond project logical preference file.

- <proj name>.rdf: Lattice Radiant project file.

- <proj\_name>.pdc: Lattice Radiant project post-synthesis constraints.

- <proj\_name>.txt: description file from the template.

Figure 3.23. Contents of SoC Project

# 3.3. C/C++ Project Design Flow

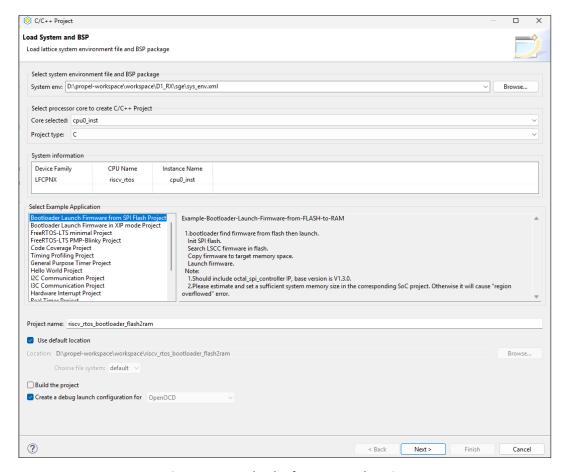

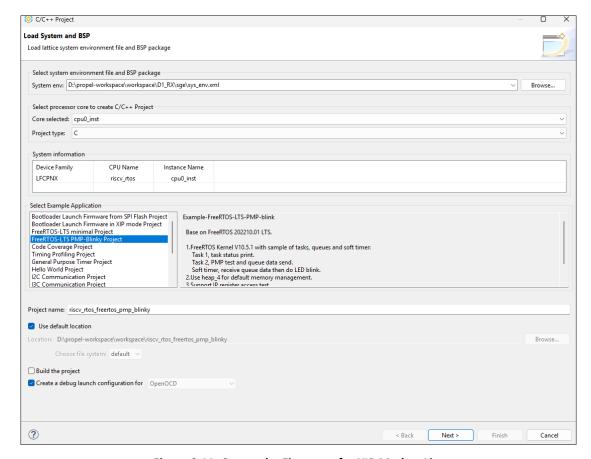

# 3.3.1. Creating a Lattice C/C++ Project

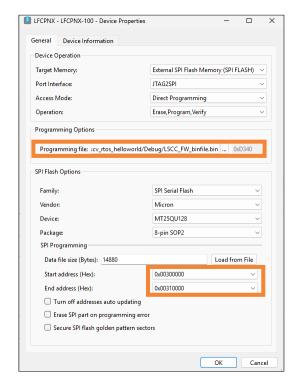

To start a Lattice C/C++ Project from Lattice Propel SDK:

Choose File > New > Lattice C/C++ Project.

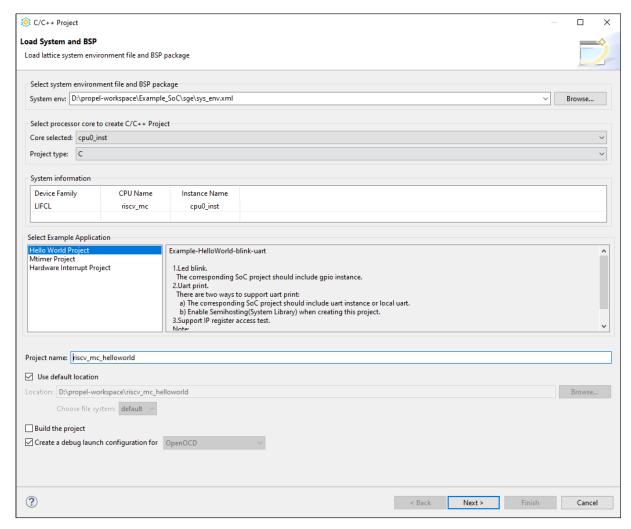

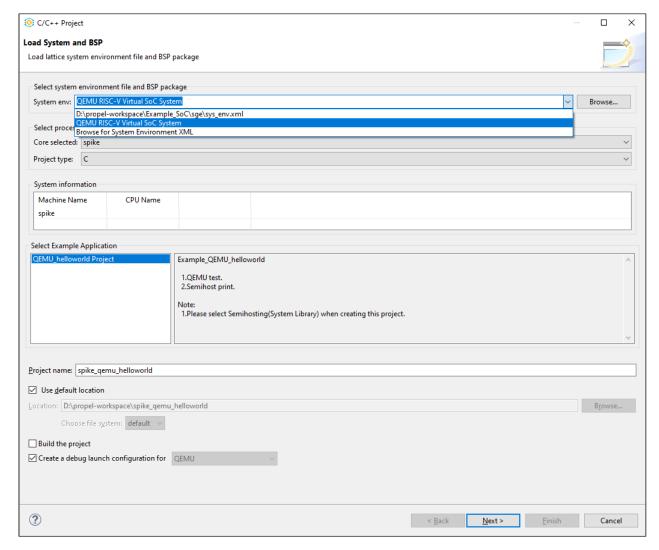

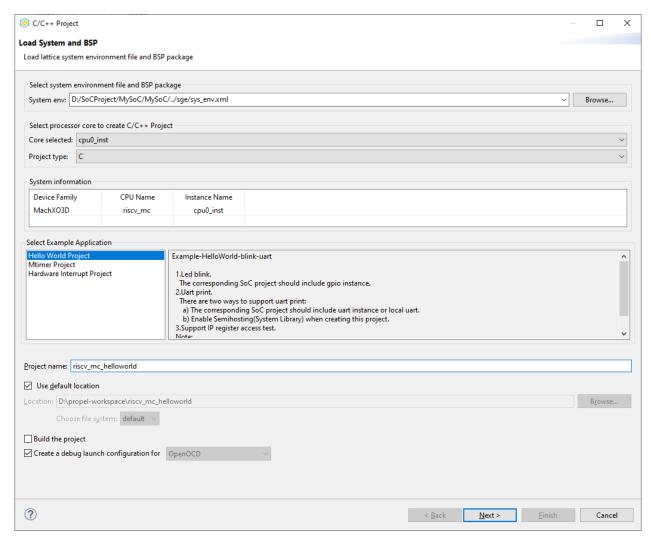

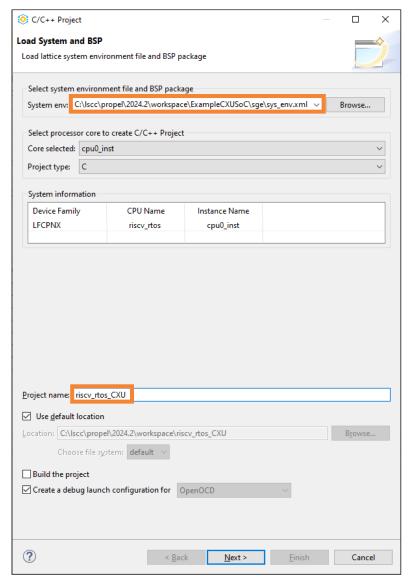

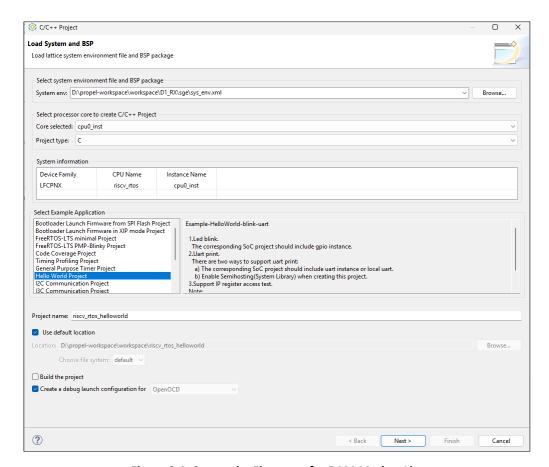

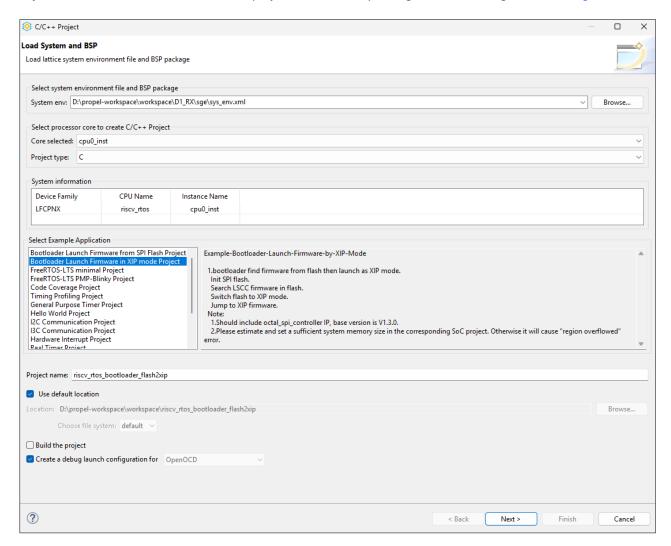

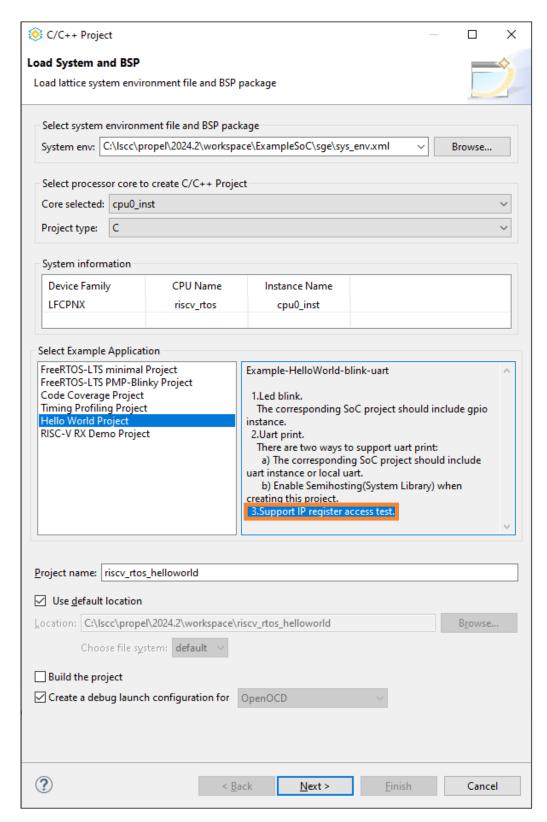

The C/C++ Project wizard opens with the Load System and BSP page (Figure 3.24).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.24. Load System and BSP Page 1

2. Browse to the SoC project folder and select the system environment file sys\_env.xml.

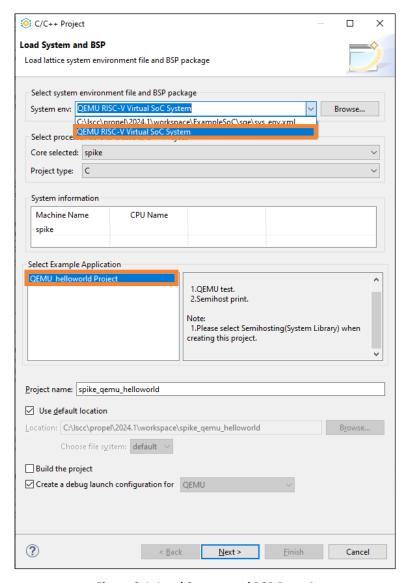

All system environment files available in the current workspace can be selected from the **System env** drop-down menu. If you select or enter **QEMU RISC-V Virtual SoC System**, you can select the QEMU application template to create a project (Figure 3.25).

Figure 3.25. Load System and BSP Page 2

- 3. If the platform has more than one processor, choose one core.

- 4. Select the project type, C or C++.

- 5. Select the application from the Example application list.

- 6. There is a default project name. You need to check it. Suggest not using periods, colons, or spaces in your project name. Though space is allowed, they may cause certain issues with some tools.

- 7. By default, the **Use default location** option is checked. The default file system is selected automatically. Suggest using the default location unless you have special need to a special location.

- 8. The **Build the project** option is unchecked by default. If you want to build the project automatically, you can check the option.

- By default, the Create a debug launch configuration for option is checked and a default launch configuration is created accordingly.

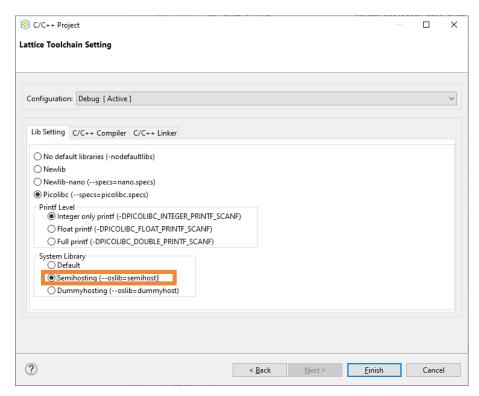

- 10. Click Next. The Lattice Toolchain Setting dialog opens (Figure 3.26).

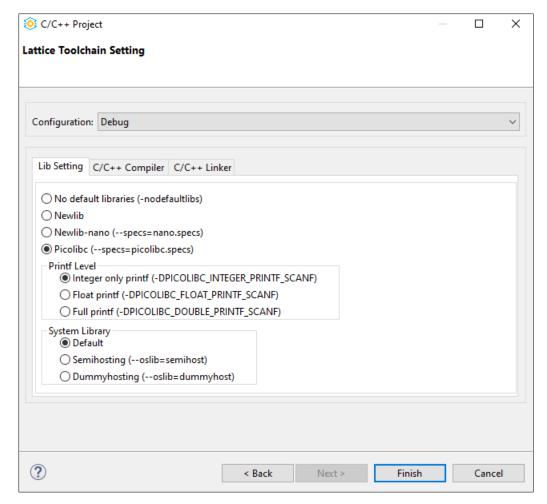

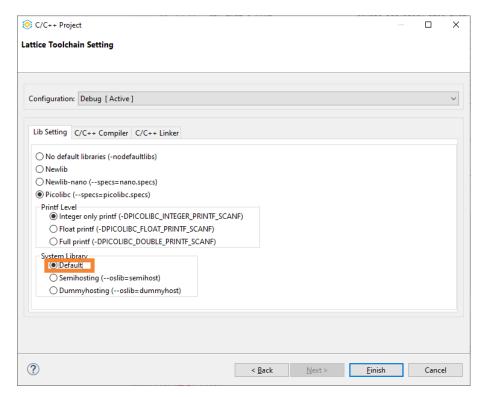

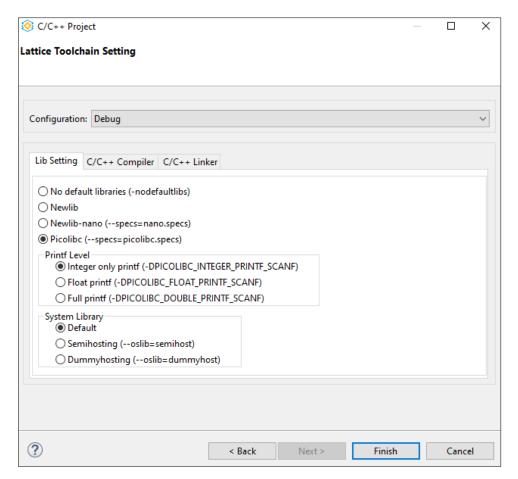

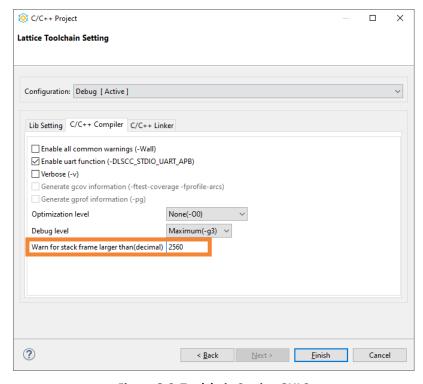

Figure 3.26. Lattice Toolchain Setting Dialog 1

- 11. By default, two toolchain configuration modes, **Debug** and **Release**, can be chosen from the Configuration drop-down menu.

- Debug configuration creates executables containing additional debug information that lets the debugger make direct associations between the source code and the binary files generated from the original source.

- Release configuration provides the tools with options setting to create an application with the best performance.

You can modify frequently-used library, compiler, and linker options for each configuration. For a complete toolchain setting, go to project properties after creating the project. Refer to the Advanced Tool Chain Setting section.

- In the **Lib Setting** tab, standard C library can be reconfigured. Picolibc (C Libraries for Smaller Embedded Systems) is selected by default and it supports different printf levels.

- In the **C/C++ Compiler** tab, optimization level and debug level can be reconfigured for each toolchain configuration.

- In the **C/C++ Linker** tab, Remove unused code (--gc-sections) is checked by default for garbage collection of unused code.

#### 12. Click Finish.

The Lattice C/C++ project is created and is displayed using the Lattice Propel SDK perspective. A perspective is a collection of tool views for a particular purpose. The Lattice Propel SDK perspective is for creating Lattice C/C++ programs.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 3.3.2. Updating a Lattice C/C++ Project

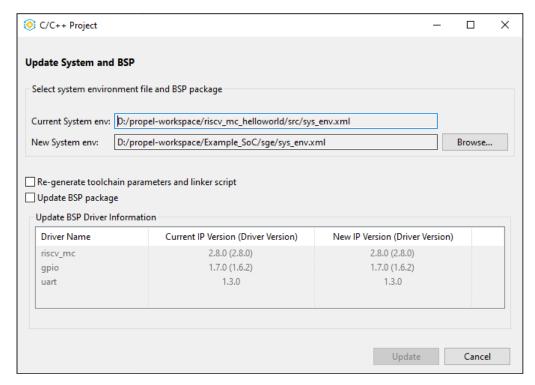

When you make changes to an SoC project, sometimes you want to synchronize the changes to an existing Lattice C/C++ project instead of creating a new Lattice C/C++ project. In this case, you can use the update C/C++ project feature.

**Note:** This feature overwrites the corresponding files or settings of your existing C/C++ project. Be sure to back up your C/C++ project before using this feature.

To update a Lattice C/C++ Project from Lattice Propel SDK:

- 1. Generate the latest system environment package according to the Generating System Environment by Building Project section.

- 2. In the **Project Explorer** view, select a C/C++ project.

- Choose Project > Update Lattice C/C++ Project....

The C/C++ Project wizard opens for updating system and BSP (Figure 3.27).

Figure 3.27. Update System and BSP Dialog

- 4. Browse to the SoC project folder and select the system environment file sys env.xml.

- 5. Select the checkbox for what you can update:

- Re-generate toolchain parameters and linker script: check this option if you want to modify CPU or memory in the system.

- Update BSP package: check this option if you want to add additional IP components into the system.

- 6. Click **Update** to make changes for the selected C/C++ project.

- 7. Click Yes (Figure 3.28).

34

Figure 3.28. Update System and BSP Confirm Dialog

#### 3.3.3. Building a Lattice C/C++ Project

To build a Lattice C/C++ project in Lattice Propel SDK:

- 1. In the **Project Explorer** view, select a C/C++ project.

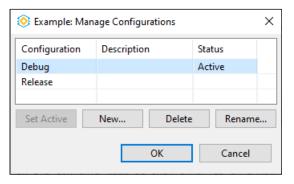

- 2. Follow steps below if you want to change the active build configuration:

- a. Choose **Project > Build Configurations > Manage...**. Or, click the **Configuration** icon 👺 on the toolbar.

- b. The Manage Configurations dialog opens (Figure 3.29) for choosing active configuration. By default, a Debug configuration creates executables containing additional debug information that lets the debugger make direct associations between the source code and the binary files generated from the original source. A Release configuration provides the tools with options setting to create an application with the best performance.

Figure 3.29. Manage Configurations Dialog

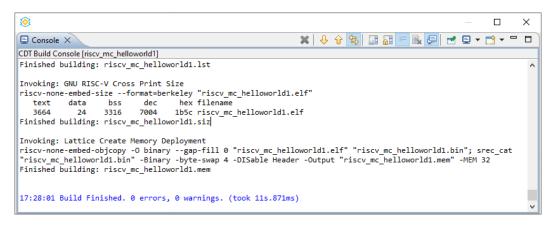

- 3. Choose **Project** > **Build Project**. Or, click the Build icon on the toolbar.

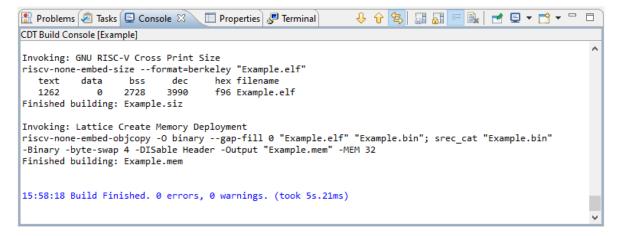

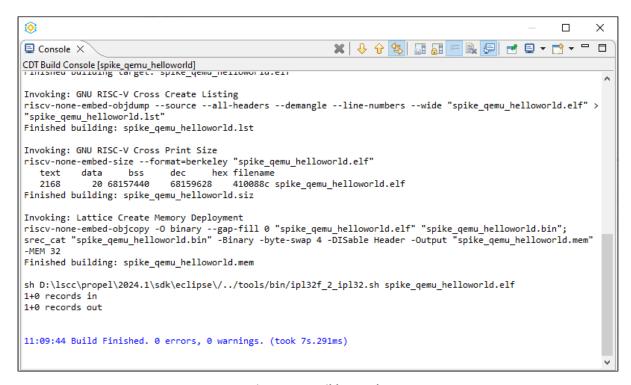

- The results of the build command are displayed in the **Console** view (Figure 3.30).

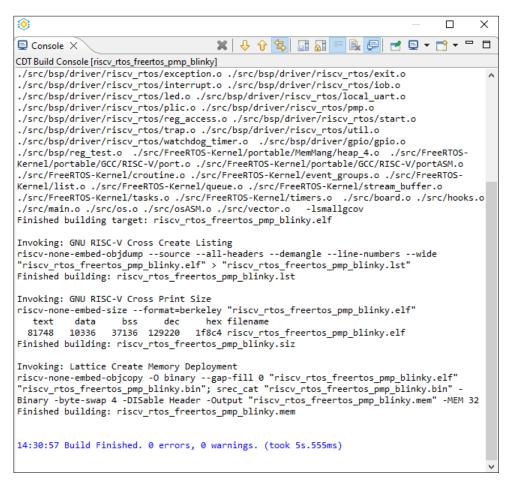

Figure 3.30. Build Result of C/C++ Project

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-UG-02244-1.0

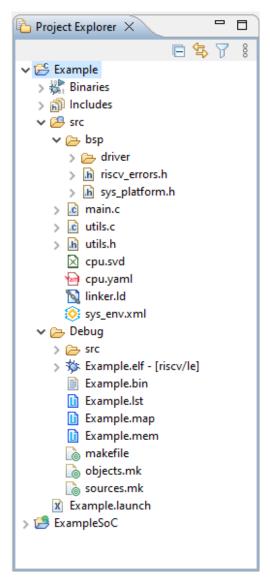

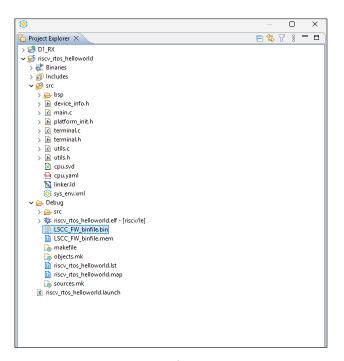

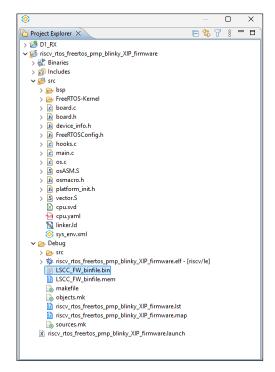

#### 3.3.4. About Lattice C/C++ Project

The Lattice C/C++ project starts with source code. In the **Project Explorer** view, open a C/C++ project folder and all its sub-folders. The project contains:

- src/bsp/driver: folder containing driver codes from the IP in the platform.

- src/bsp/sys\_platform.h: header file that defines DEVICE\_FAMILY (the Lattice FPGA), address mapping, and any IP parameters that can be used by the drivers.

- src/main.c: source file containing the main routine, which is the entry-point of a C/C++ program.

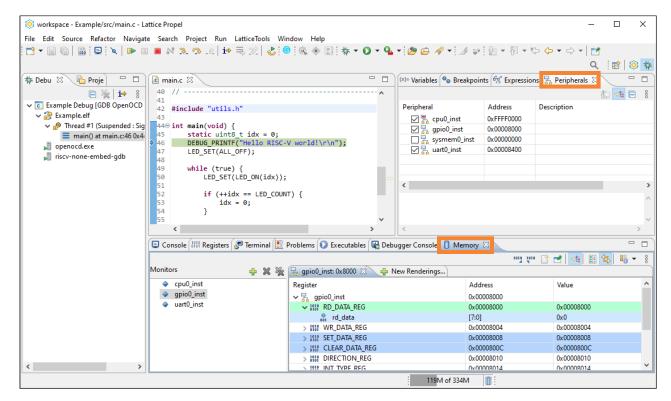

- src/cpu.svd: system view description file used for peripherals registers view at debug perspective.

- src/cpu.yaml: processor description file used when debugging.

- src/linker.ld: linker script file.

- src/sys\_env.xml: system environment file describing aspects of the platform, such as memory spaces.

After building the project, the build output can be found in each build configuration folder, the **Debug** folder or the **Release** folder (Figure 3.31). The Debug or Release folder contains:

- proj name.elf: executable file used in on-chip debugging.

- <proj name>.bin: binary file used in deploying the application to flash memory.

- <proj name>.lst: extended listing file generated by tool objdump.

- proj name>.map: linker map file.

- roj\_name>.mem: Lattice system memory initialization file used in the System Memory IP.

- roj name.launch: Debug launch configuration.

Note: Some of the files listed in Figure 3.31 are intermediate files that you do not need to take care of.

Figure 3.31. Contents of C/C++ Project

#### 3.3.5. Assisting in Developing Code

Lattice Propel SDK is based on Eclipse IDE. You can write application code following the process and usage of the same tools as any in Eclipse IDE. You can get more detailed information regarding Eclipse IDE from the Lattice Propel online help.

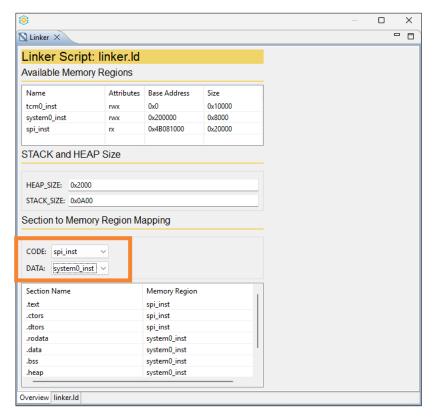

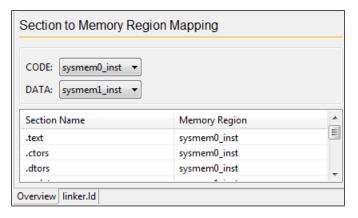

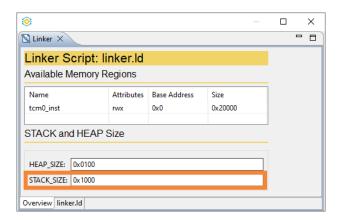

For writing code, Lattice Propel SDK provides two extra aids:

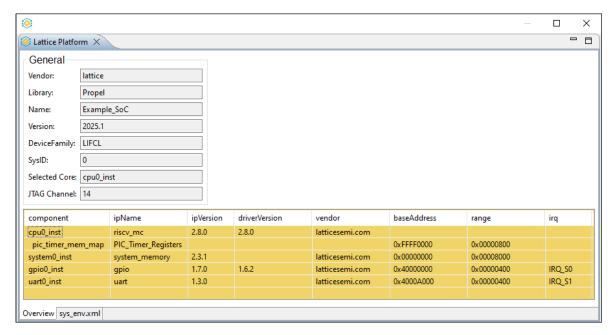

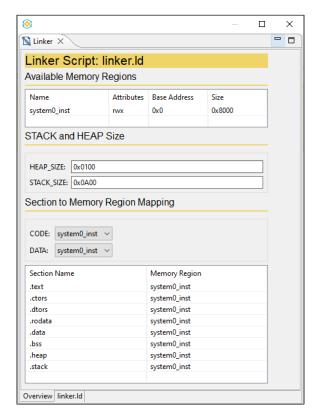

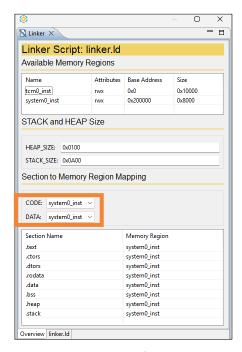

- Lattice System Platform: An overview of the processor platform can be displayed (Figure 3.32).

- Linker Editor: An overview of the memory regions of linker script can be displayed. You can modify key linker parameters through the graphical interface (Figure 3.33).

Figure 3.32. Lattice System Platform

Figure 3.33. Linker Editor

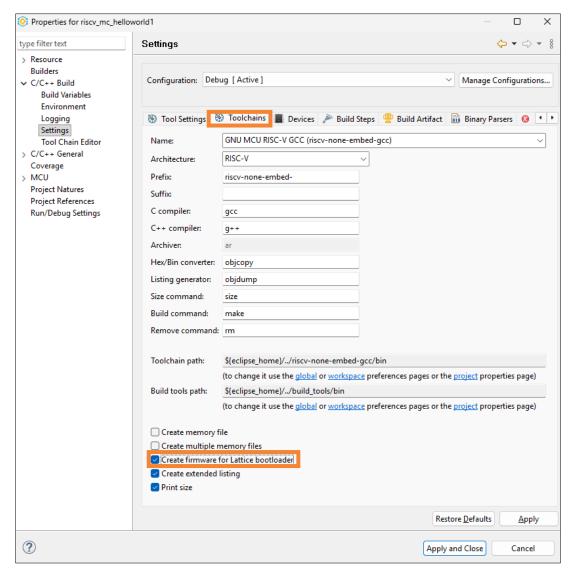

#### 3.3.6. Advanced Tool Chain Setting

Follow the process below to modify the tool chain settings of a C/C++ project.

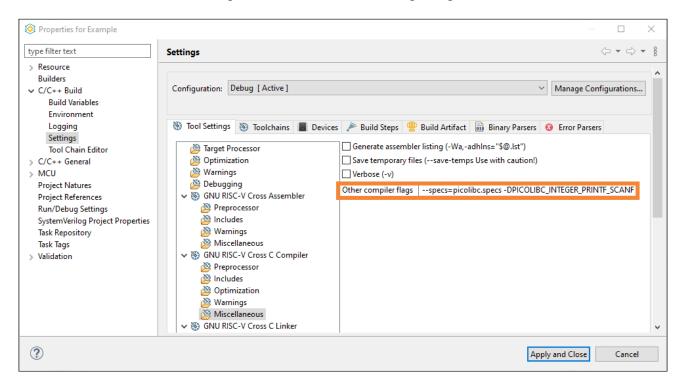

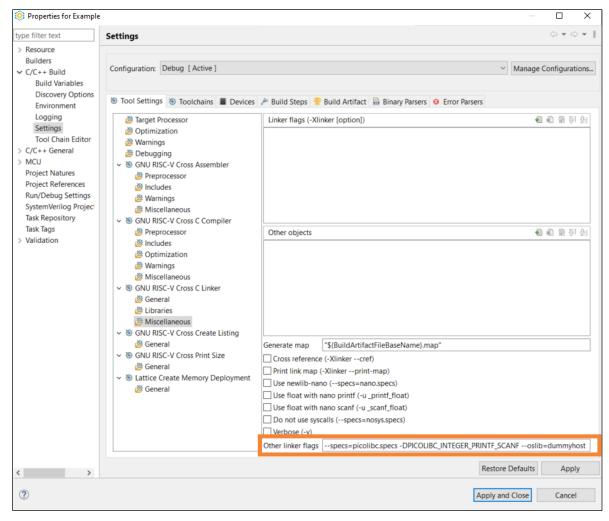

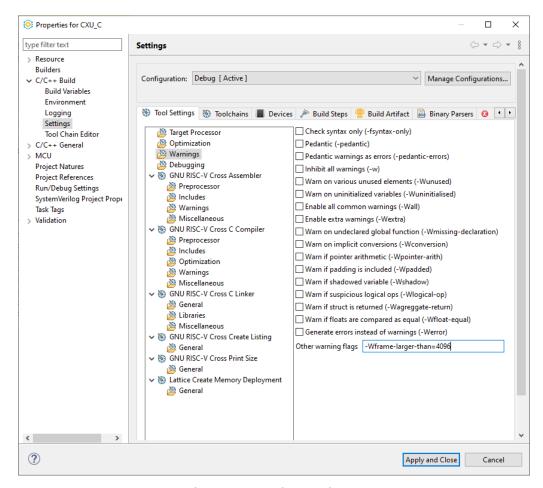

To change tool chain setting in Project Properties in Lattice Propel SDK:

- 1. In the **Project Explorer** view of Lattice Propel SDK, select a C/C++ project.

- Choose Project > Properties. The Properties for the current project opens (Figure 3.34).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

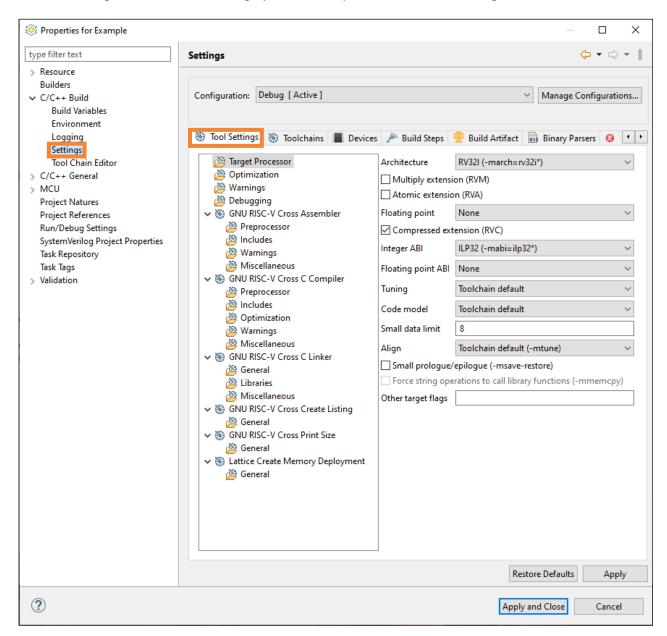

3. Select Settings of the C/C++ Build category from the left pane. Select the Tool Settings tab.

Figure 3.34. Properties of C/C++ Project

- 4. Customize the tools and tool options. All your customization can be made in the build configuration in the **Tool Settings** properties tab. The build configuration is used during your C/C++ project building.

- **Note:** The setting for each configuration, **Debug** or **Release**, is independent.

- 5. Click **Apply and Close** to save the change.

- **Note:** You may need to clean the project to make the new settings take effect for the whole project.

### 3.4. System Simulation Flow

The SoC Project created from template has a default simulation environment for you to set up and start functional simulation. It is generated automatically along with the SoC project creation. You can use it as a start point and customize accordingly.

39

The default simulation environment is with the following features:

- Provides similar user experience as real board-level debugging, such as for Hello World SoC, key components including RISC-V MC, System Memory, and UART.

- Simulates user-modified template SoC with extended HDL designs.

- Simulates the whole system using real C/C++ projects as stimulus with the necessary modification and with all the details for debugging.

- Supports user extension with a friendly and flexible approach.

### 3.4.1. Launching Simulation

To launch simulation:

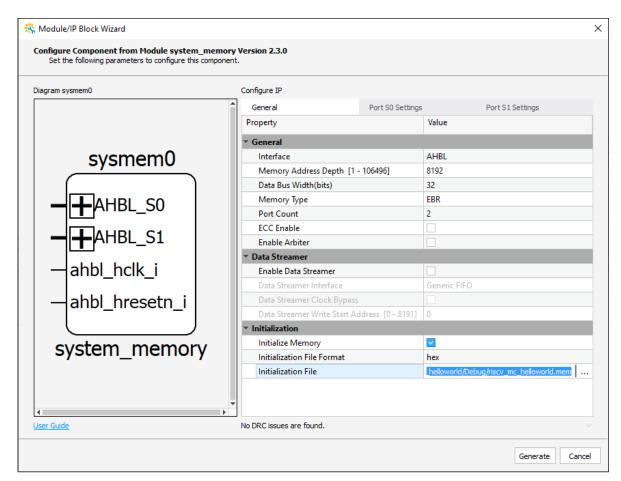

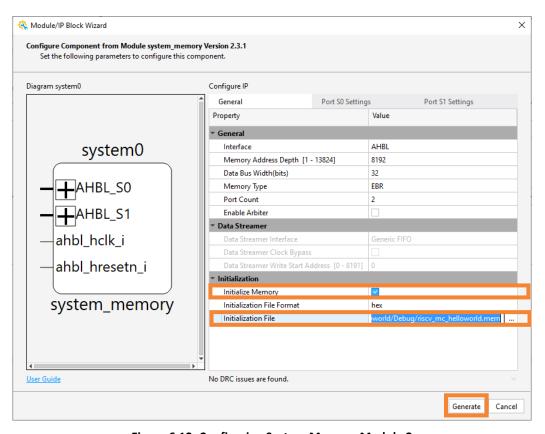

1. In Lattice Propel Builder, update the SoC design to enable simulation features. Enable the checkbox for Initialize Memory for the System Memory module from the Initialization area of the General tab. Then, set the Initialization File generated from the corresponding C/C++ project (Figure 3.35).

Figure 3.35. Configuring System Memory Module 1

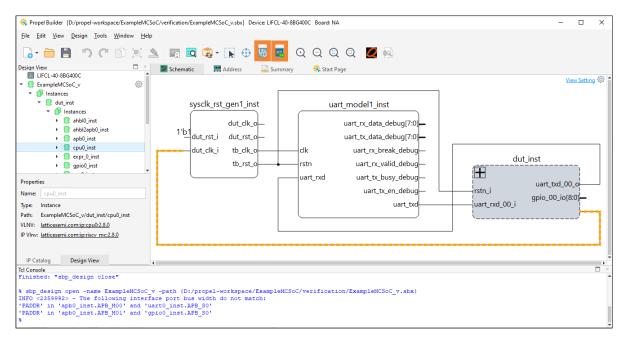

- 2. Click the **Switch** icon on the toolbar to switch between SoC design and SoC verification project (Figure 3.36).

- 3. After the SoC design is switched to an SoC verification project, click the **Generate** icon **Generate** to generate the simulation environment. Click the Launch Simulation icon (Figure 3.36).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.36. SoC Verification Project

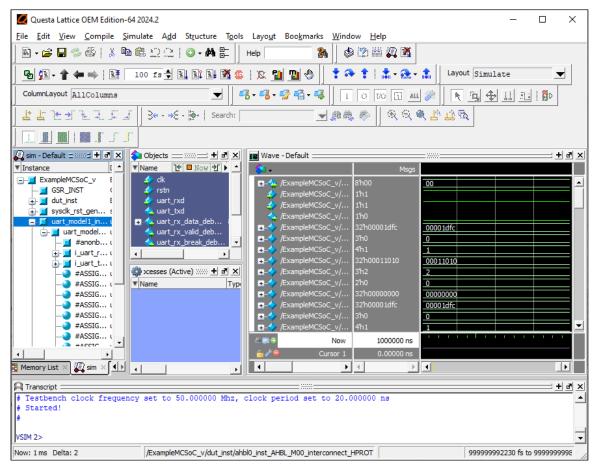

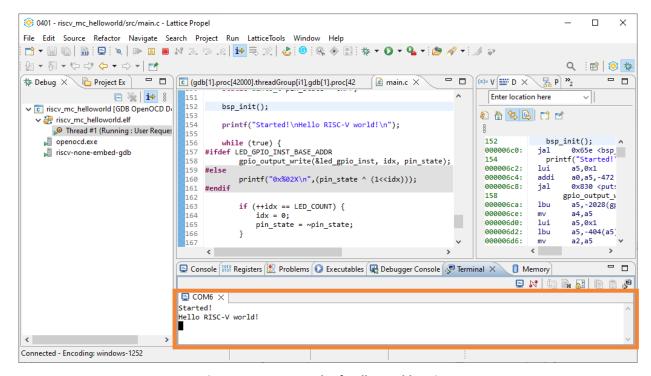

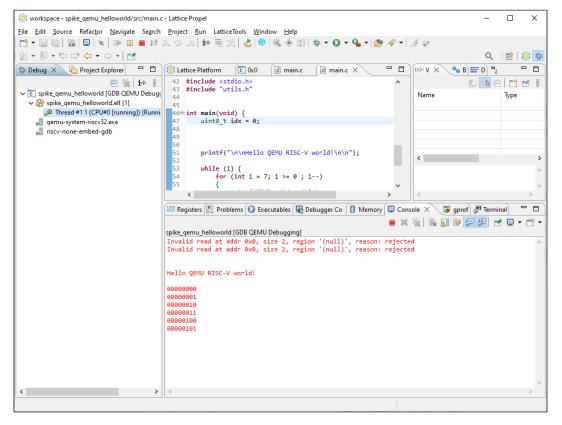

4. QuestaSim is launched running simulation for the SoC verification project. The corresponding waveform of the SoC verification project for the Hello World project is shown (Figure 3.37). Check the waveform.

Figure 3.37. Questa Simulation GUI

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 3.4.2. Simulation Details

The default simulation environment is located at the generated sim folder inside the SoC verification project in Lattice Propel SDK. It contains:

```

-- [sim]

-- Generated simulation environment folder

+--- [hdl_header]

+--- soc regs.v

-- Register definitions of all the components in DUT/SOC

+--- sys_platform.v

-- Base address, user settings of all the components in DUT/SOC

- [misc]

-- All the mem, hex, txt files are copied here

- flist.f

-- File list for HDLs

+--- flist sim.f

-- File list for all files used in simulation

+--- qsim.do

-- Do script for simulator,

qsim.do: QuestaSim.

This file compiles project and invokes simulator with

some default settings using the generated testbench.

-- Do script for adding signals in waveform window

+--- wave.do

+--- <project_name>_v.sv -- Top testbench, it is SystemVerilog based.

```

You can extend more verification features in the top testbench.

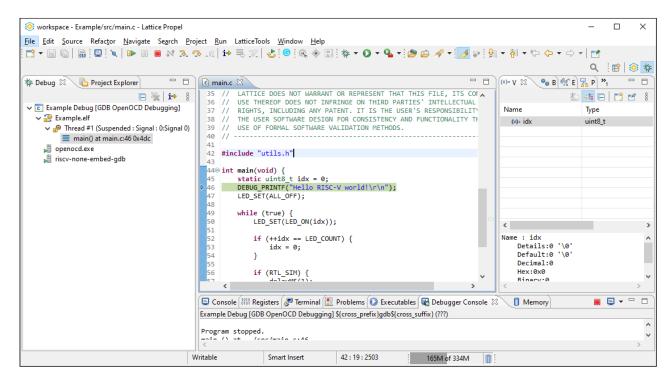

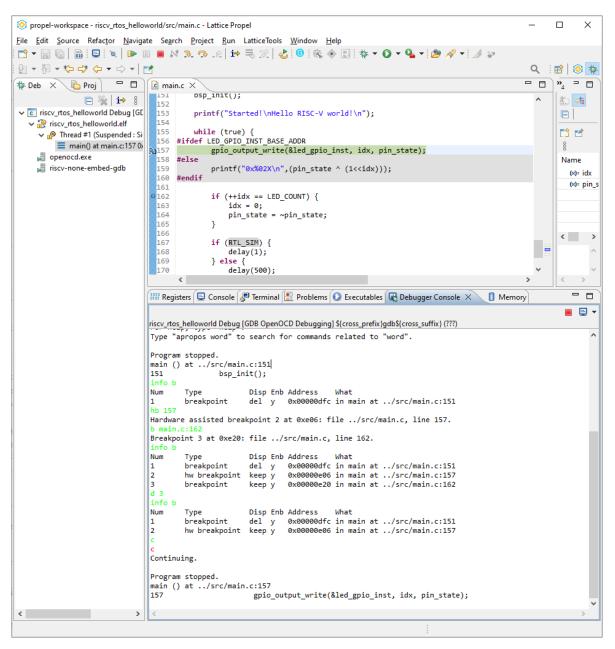

### 3.5. Programming and On-Chip Debugging Flow

This section describes the process of testing and debugging application code on the actual hardware including the Lattice FPGA with the hardware design installed. Debugging with Lattice Propel SDK follows the same process and uses of the same tools in Eclipse IDE.

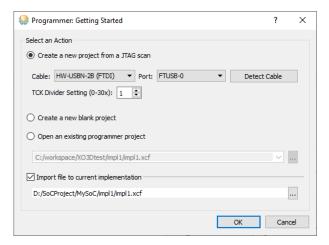

Before debugging, download the hardware design created from the Lattice Diamond or Radiant Programmer. Refer to the User Guide of the specific evaluation board for more details on the evaluation board.

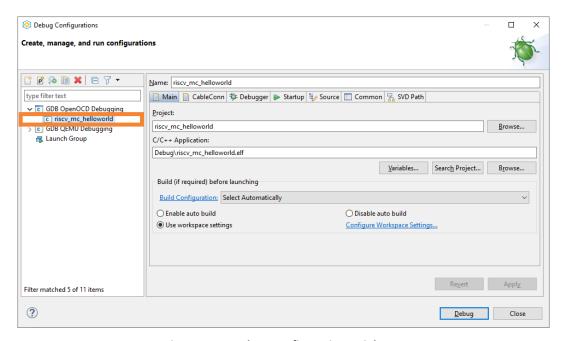

### 3.5.1. Creating a Debug Launch Configuration

To debug a program, a debug launch configuration must be created. Most of the settings for a debug launch configuration can be automatically entered. Only a few settings need to be manually configured.

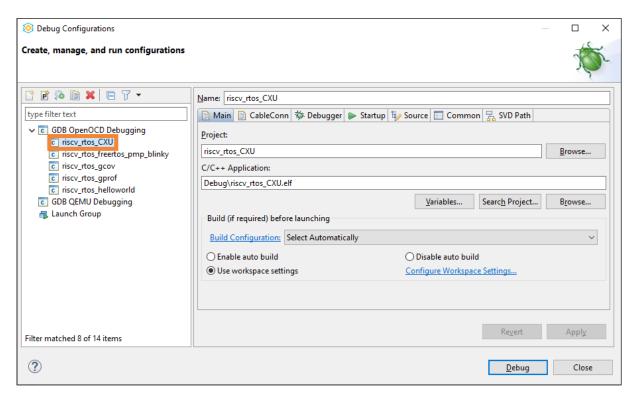

To create a debug launch configuration:

- 1. In the **Project Explorer** view of Lattice Propel SDK, select a C/C++ project.

- 2. Build the project and ensure the executable file is available. Refer to the Building a Lattice C/C++ Project section for details on the process.

- 3. Choose Run > Debug Configurations....

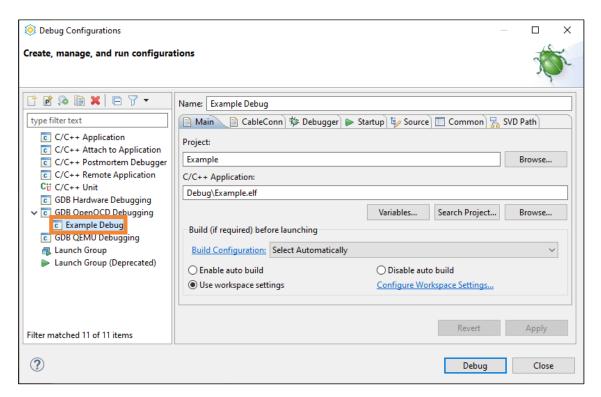

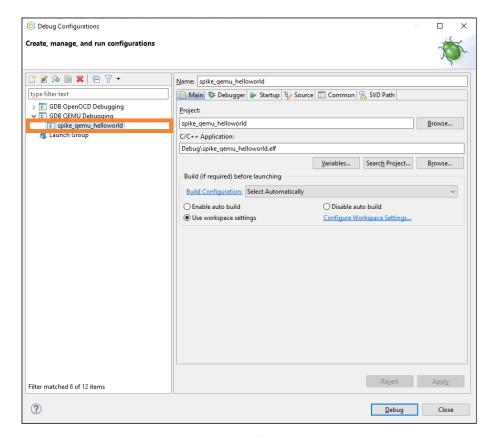

The **Debug Configurations** dialog opens (Figure 3.39).

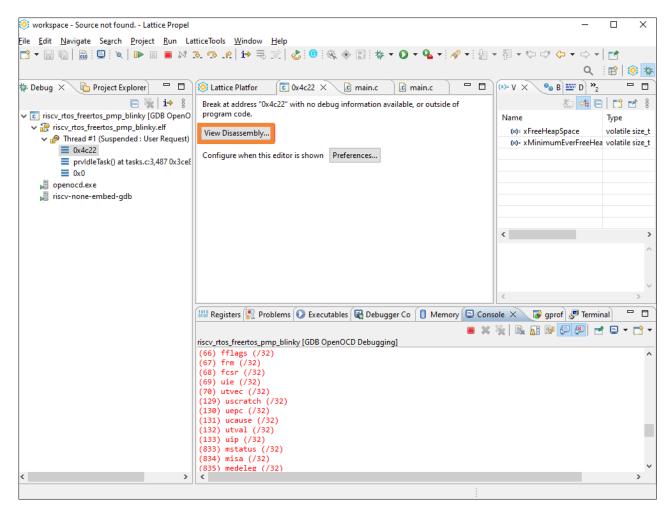

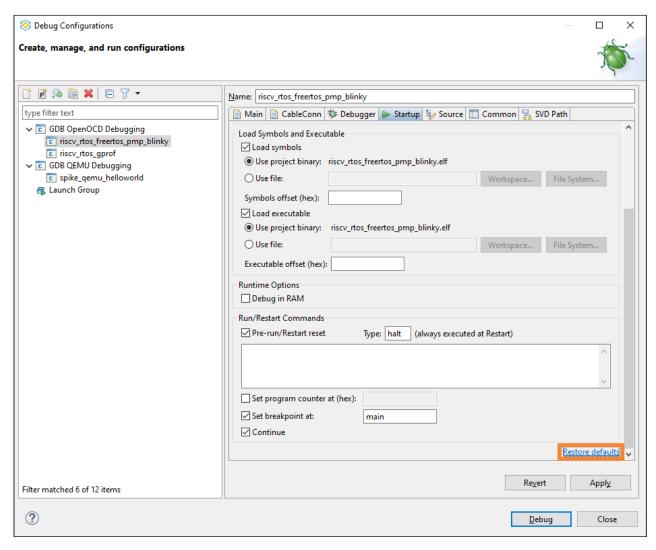

Figure 3.38. Debug Configurations Dialog 1

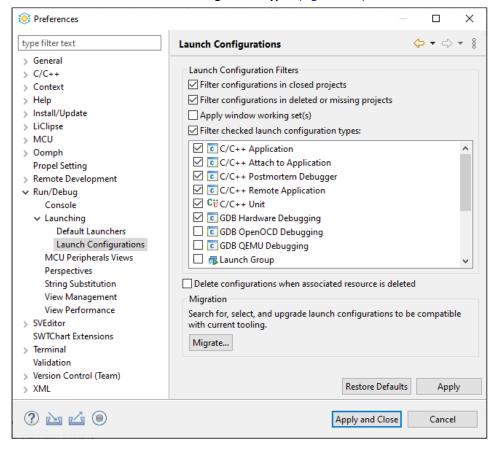

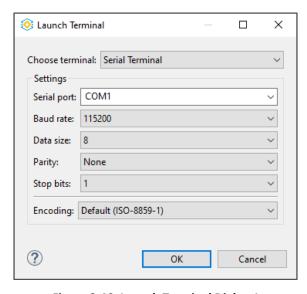

- 4. Double-click **GDB OpenOCD Debugging** to create a new launch configuration.

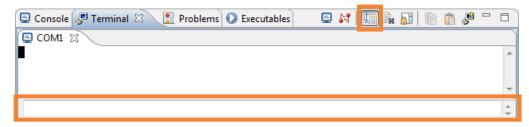

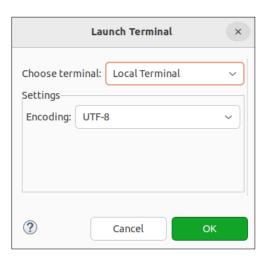

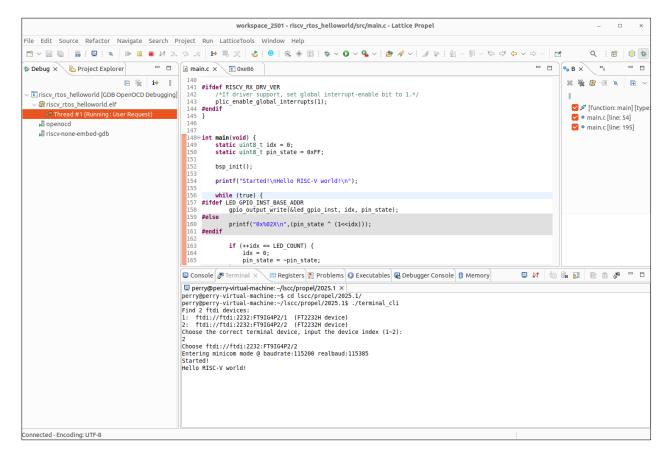

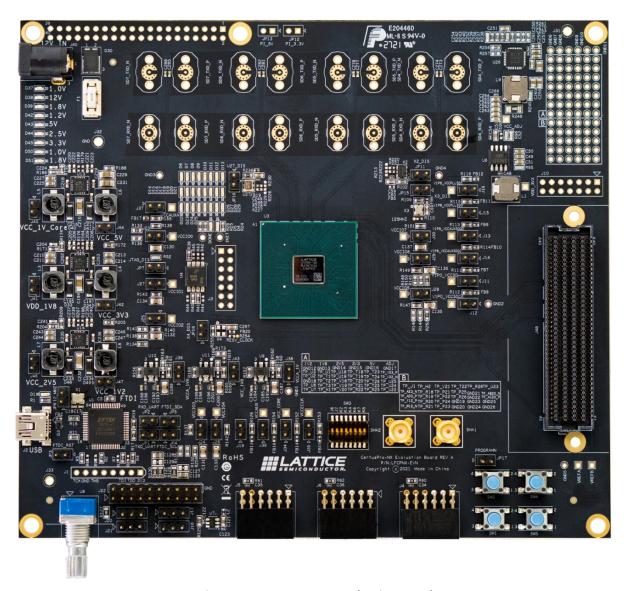

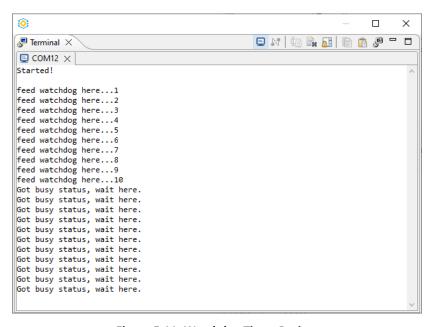

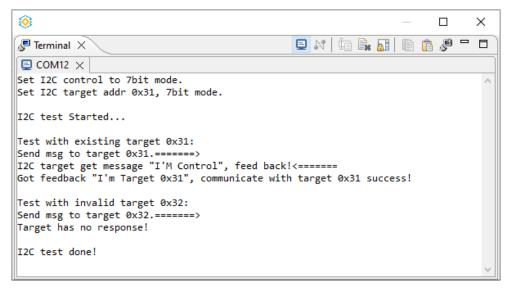

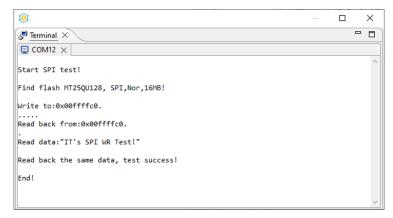

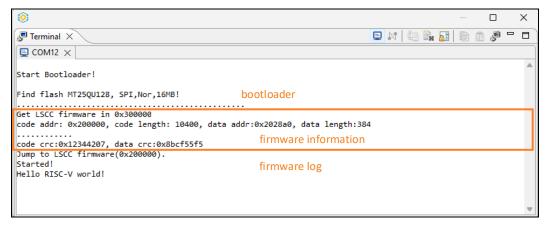

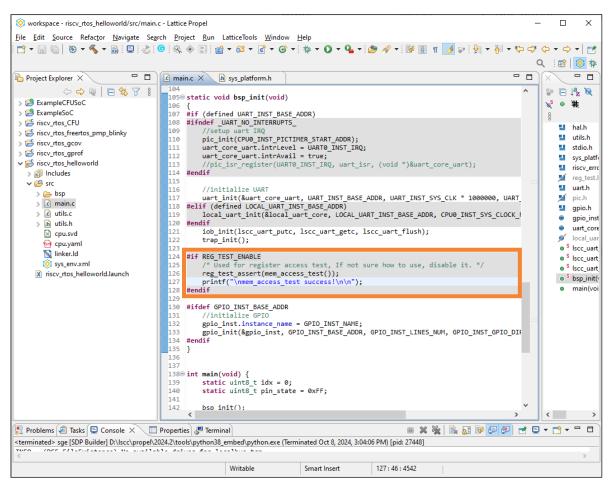

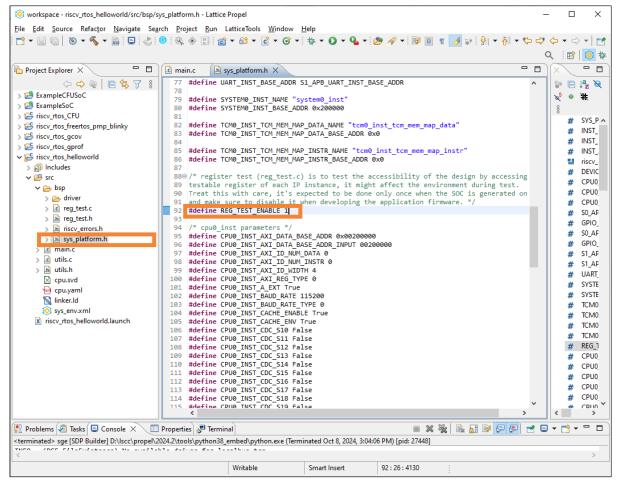

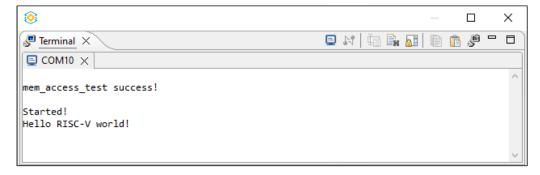

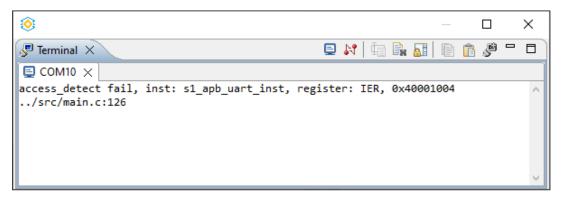

- A multi-tab page is displayed. The **Main** tab should already be filled in with the project name, application file name, and location.