# RISC-V MC CPU IP – Lattice Propel Builder 2025.2

IP Version: v2.8.1

# **User Guide**

FPGA-IPUG-02300-1.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents                                | 3  |

|-----------------------------------------|----|

| Abbreviations in This Document          |    |

| 1. Introduction                         | €  |

| 1.1. What's New in This IP Release      | 6  |

| 1.2. Quick Facts                        | 6  |

| 1.3. Features                           | 6  |

| 1.4. Conventions                        |    |

| 1.4.1. Nomenclature                     |    |

| 1.4.2. Signal Names                     |    |

| 1.5. Licensing and Ordering Information |    |

| 2. Functional Descriptions              | 8  |

| 2.1. Overview                           |    |

| 2.2. Modules Description                | 8  |

| 2.2.1. RISC-V Processor Core            |    |

| 2.2.2. Submodule                        |    |

| 2.3. Signal Description                 | 19 |

| 2.3.1. Clock and Reset                  | 20 |

| 2.3.2. Instruction and Data Interface   | 20 |

| 2.3.3. Interrupt Interface              | 21 |

| 2.3.4. CXU-LI Interface                 | 21 |

| 2.3.5. RVFI Interface                   | 21 |

| 2.4. Attribute Summary                  | 23 |

| 3. RISC-V MC CPU IP Generation          | 27 |

| Appendix A. Resource Utilization        | 30 |

| Appendix B. Debug with Soft JTAG        |    |

| References                              |    |

| Technical Support Assistance            |    |

| Revision History                        |    |

| Figure 2.1. RISC-V MC Soft IP Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 2.2. RISC-V MC Processor Core Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9              |

| Figure 2.3. General Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10             |

| Figure 2.4. Debug Configuration Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11             |

| Figure 2.5. mcx_selector CSR 0xBC0 Version 0: Legacy Custom Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13             |

| Figure 2.6. mcx_selector CSR 0xBC0 Version 1: Extension Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13             |

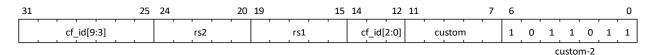

| Figure 2.7. CXU R-type Instruction Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14             |

| Figure 2.8. CXU I-type Instruction Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14             |

| Figure 2.9. CX Flex-type Instruction Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14             |

| Figure 2.10. CX Flex-type Instruction Alternate Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15             |

| Figure 2.11. Execution of a Custom Function Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15             |

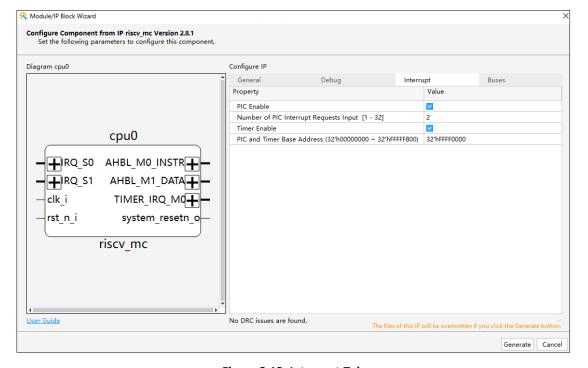

| Figure 2.12. Interrupt Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16             |

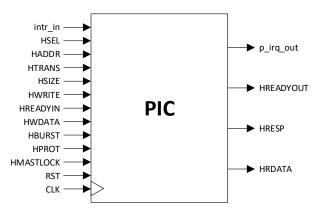

| Figure 2.13. PIC Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17             |

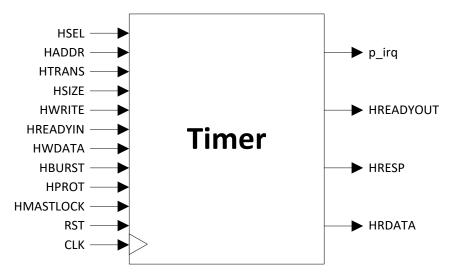

| Figure 2.14. Timer Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19             |

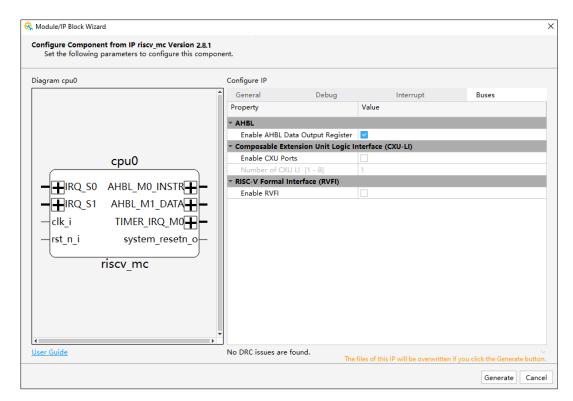

| Figure 2.15. Buses Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20             |

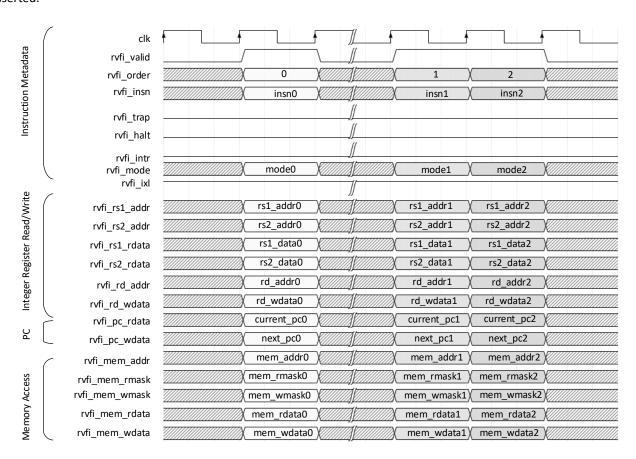

| Figure 2.16. RVFI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22             |

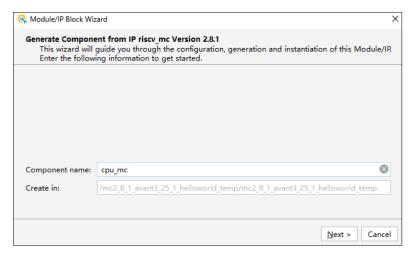

| Figure 3.1. Entering Component Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27             |

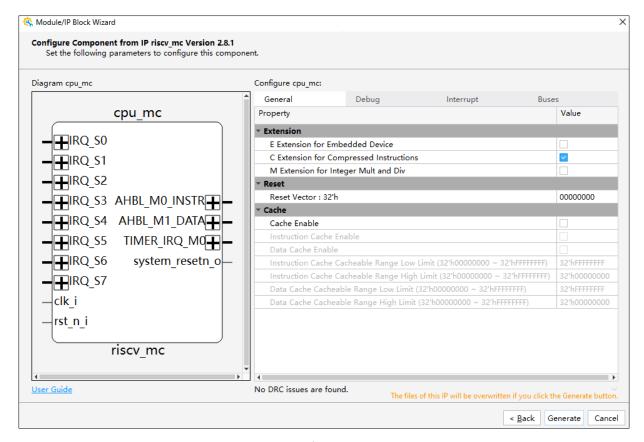

| Figure 3.2. Configuring Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27             |

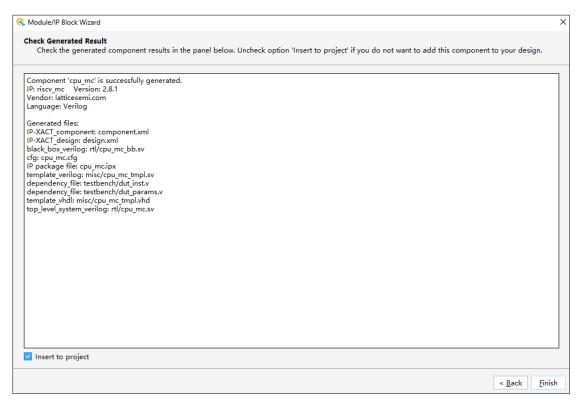

| Figure 3.3. Verifying Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28             |

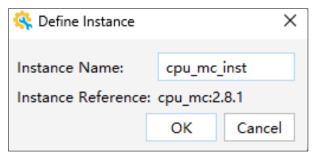

| Figure 3.4. Specifying Instance Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28             |

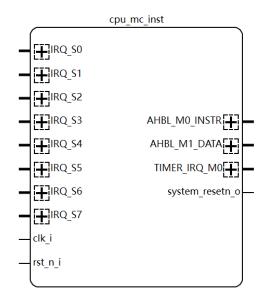

| Figure 3.5. Generated Instance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29             |

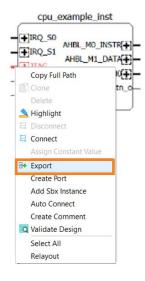

| Figure B.1. Exporting Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32             |

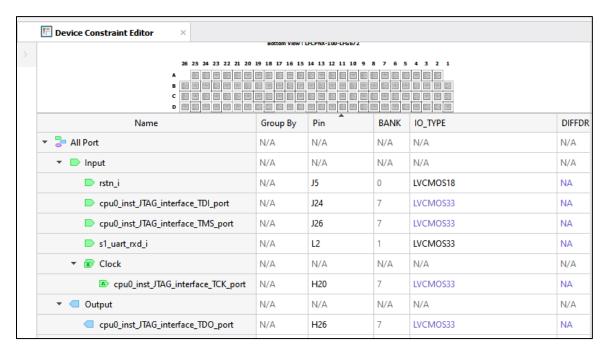

| Figure B.2. Assigning Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32             |

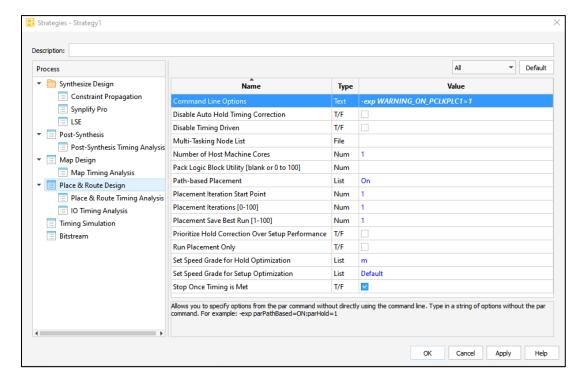

| Figure B.3. Setting Environment Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| Table 1.1. RISC-V MC CPU IP Quick Facts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6              |

| Table 1.2. DMIPS Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Table 1.3. Fmax for MC CPU IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Table 2.1. RISC-V Processor Core Control and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Table 2.2. PIC Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| Table 2.3. Timer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| Table 2.4. Clock and Reset Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20             |

| Table 2.5. Instruction Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20<br>20       |

| Table 2.5. Instruction Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20<br>20<br>21 |

| Table 2.5. Instruction Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Table 2.5. Instruction Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20<br>21<br>21 |

| Table 2.5. Instruction Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description                                                                                                                                                                                                                                                                                                                                                                                         |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description Table A.1. Resource Utilization in MachXO3D Device, with Cache Disabled                                                                                                                                                                                                                                                                                                                 |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description Table A.1. Resource Utilization in MachXO3D Device, with Cache Disabled Table A.2. Resource Utilization in CrossLink-NX Device, with Cache Disabled                                                                                                                                                                                                                                     |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description Table A.1. Resource Utilization in MachXO3D Device, with Cache Disabled Table A.2. Resource Utilization in CrossLink-NX Device, with Cache Enabled                                                                                                                                                                                                                                      |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description Table 2.11. Resource Utilization in MachXO3D Device, with Cache Disabled Table A.2. Resource Utilization in CrossLink-NX Device, with Cache Disabled Table A.3. Resource Utilization in CrossLink-NX Device, with Cache Enabled Table A.4. Resource Utilization in Lattice Avant Device, with Cache Disabled                                                                            |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description Table A.1. Resource Utilization in MachXO3D Device, with Cache Disabled Table A.2. Resource Utilization in CrossLink-NX Device, with Cache Disabled Table A.3. Resource Utilization in CrossLink-NX Device, with Cache Enabled Table A.4. Resource Utilization in Lattice Avant Device, with Cache Disabled Table A.5. Resource Utilization in Lattice Avant Device, with Cache Enabled |                |

| Table 2.5. Instruction Ports Table 2.6. Data Ports Table 2.7. Interrupt Ports Table 2.8. CXU-LI Ports, Optional Table 2.9. RVFI Ports, Optional Table 2.10. Configurable Attributes Table 2.11. Attributes Description Table A.1. Resource Utilization in MachXO3D Device, with Cache Disabled Table A.2. Resource Utilization in CrossLink-NX Device, with Cache Enabled                                                                                                                                                                                                                                      |                |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                                  |  |  |  |

|--------------|-------------------------------------------------------------|--|--|--|

| AHB-Lite     | Advanced High-performance Bus – Lite                        |  |  |  |

| AMO          | Atomic Memory Operation                                     |  |  |  |

| CX           | Composable Extension                                        |  |  |  |

| CXU          | Composable Extension Unit                                   |  |  |  |

| CXU-LI       | Composable Extension Unit Logic Interface                   |  |  |  |

| CF           | Custom Function                                             |  |  |  |

| CFU          | Custom Function Unit                                        |  |  |  |

| CFU-LI       | Custom Function Unit Logic Interface                        |  |  |  |

| CI           | Custom Interface                                            |  |  |  |

| CPU          | Central Processing Unit                                     |  |  |  |

| CSR          | Control and Status Register                                 |  |  |  |

| DMIPS        | Dhrystone MIPS (Million Instructions per Second)            |  |  |  |

| FPGA         | Field Programmable Gate Array                               |  |  |  |

| GDB          | Gnu Debugger                                                |  |  |  |

| HDL          | Hardware Description Language                               |  |  |  |

| IP           | Intellectual Property                                       |  |  |  |

| IRQ          | Interrupt Request                                           |  |  |  |

| ISA          | Instruction Set Architecture                                |  |  |  |

| JTAG         | Joint Test Action Group                                     |  |  |  |

| LUT          | Lookup-Table                                                |  |  |  |

| MC           | Micro-Controller (RISC-V for Micro-Controller applications) |  |  |  |

| OpenOCD      | Open On-Chip Debugger                                       |  |  |  |

| PIC          | Programmable Interrupt Controller                           |  |  |  |

| RISC-V       | Reduced instruction set computer-V (Five)                   |  |  |  |

| RVFI         | RISC-V Formal Interface                                     |  |  |  |

| RV32IMC      | RISC-V Integer, M and Compressed Instruction Sets           |  |  |  |

| WFI          | Wait For Interrupt                                          |  |  |  |

# 1. Introduction

The Lattice Semiconductor RISC-V MC CPU soft IP contains a 32-bit RISC-V processor core and optional submodules – Timer and Programmable Interrupt Controller (PIC). The CPU core has optional instruction and data caches. The CPU core supports the RV32IMCE instruction set, external interrupts, and debug feature that is JTAG – IEEE 1149.1 compliant. The Timer submodule is a 64-bit real-time counter, which compares a real-time register with another register to assert the timer interrupt. The PIC submodule aggregates up to eight external interrupt inputs into one interrupt to the CPU core. The submodule registers are accessed by the processor core using a 32-bit Advanced High-performance Bus – Lite (AHB-Lite) interface.

The design is implemented using Verilog HDL, and it can be configured and generated using the Lattice Propel™ Builder software. It supports MachXO4™, Certus™-N2, Lattice Avant™, MachXO5™-NX, CrossLinkU™-NX, CrossLink™-NX, CertusPro™-NX, Certus-NX, MachXO3D™, MachXO3™, and MachXO2™ FPGA devices.

#### 1.1. What's New in This IP Release

- Improved Fmax of the MC CPU core with caches enabled.

- Fixed a bug related to the CSR MEPC value.

- Added support for MachXO4 devices.

## 1.2. Quick Facts

Table 1.1 presents a summary of the RISC-V MC CPU IP.

Table 1.1. RISC-V MC CPU IP Quick Facts

| IP Requirements        | Supported FPGA Family     | MachXO4, Certus-N2, Lattice Avant, MachXO5-NX, CrossLinkU-NX, CrossLink-NX, Certus-NX, MachXO3D, MachXO3L™, MachXO3LF™, MachXO2 |

|------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Resource               | Supported User Interfaces | AHB-Lite Interface, Composable Extension Unit Logic Interface (CXU-LI), RISC-V Formal Interface (RVFI)                          |

| Utilization            | Resources                 | See Table A.1, Table A.2, Table A.3, Table A.4, Table A.5, Table A.6, and Table A.7.                                            |

| Design Tool            | Lattice Implementation    | IP v2.8.1 – Lattice Propel Builder 2025.2, Lattice Radiant™ 2025.2                                                              |

| Design Tool<br>Support | Simulation                | For a list of supported simulators, see the Lattice Radiant and Lattice Diamond™ software user guide.                           |

#### 1.3. Features

The RISC-V MC soft IP has the following features:

- RV32IMCE instruction set

- Five stage pipeline

- Supports the AHB-Lite bus standard for instruction and data ports.

- Supports CXU-LI

- Supports RVFI

- Supports dynamic branch target prediction.

- Optional caches including a 4 KB two-way instruction cache and a 4 KB two-way data cache, for Certus-N2, Lattice Avant, MachXO5-NX, Certus-NX, Certus-Pro-NX, and CrossLink-NX devices only

- Optional debug using Gnu Debugger (GDB) and Open On-Chip Debugger (OpenOCD)

- Optional PIC module

- Optional Timer module

- Interrupt and exception handling under Machine Mode

- Supports the DMIPS performance listed in Table 1.2.

- Supports Fmax shown in Table 1.3.

- Configurable reset vector

#### **Table 1.2. DMIPS Performance**

| RISC-V Core | RISC-V Configuration                                       | DMIPS          |

|-------------|------------------------------------------------------------|----------------|

| MC          | RV32IMC, no cache, with AHBL Data Output Register disabled | 0.83 DMIPS/MHz |

| MC          | RV32IMC, with cache                                        | 1.25 DMIPS/MHz |

#### Notes:

- The System Memory IP in the SoC used to measure DMIPS is v.2.3.0, and its output register is disabled.

- The C optimizations flags used are listed below.

-DPREALLOCATE=1 -mcmodel=medany -static -std=gnu99 -O2 -ffast-math -fno-common -fno-builtin-printf -fno-tree-loop-distribute-patterns

#### Table 1.3. Fmax for MC CPU IP

| Configuration  | Lattice Avant Device<br>Speed 2 |           | Lattice Avant Device<br>Speed 3 |           |           | NX Device<br>ed 8 |           | -NX Device<br>ed 9 |

|----------------|---------------------------------|-----------|---------------------------------|-----------|-----------|-------------------|-----------|--------------------|

|                | Best                            | Average   | Best                            | Average   | Best      | Average           | Best      | Average            |

| RV32I no cache | 224.8 MHz                       | 205.5 MHz | 245.6 MHz                       | 234.2 MHz | 140.6 MHz | 135.1 MHz         | 148.9 MHz | 140.6 MHz          |

#### Notes:

- The Fmax data is measured using the Lattice Radiant software version 2025.1.0.39 with the default configuration across 10 seeds, upon a hello world SoC design. The hello world SoC design features an MC IP with AHBL Data Output Register enabled, PIC enabled, and Timer enabled, and a System Memory IP with its Output Register enabled.

- Fmax depends on the SoC IP version and configuration, the FPGA device, and the Lattice Radiant software version and configuration.

#### 1.4. Conventions

#### 1.4.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.4.2. Signal Names

- \_n are active low, asserted when value is logic 0.

- i are input signals.

- \_o are output signals.

- \_io are bidirectional signals.

## 1.5. Licensing and Ordering Information

The MC CPU IP is provided at no additional cost with the Lattice Propel design environment. The IP can be fully evaluated in hardware without requiring an IP license string.

# 2. Functional Descriptions

#### 2.1. Overview

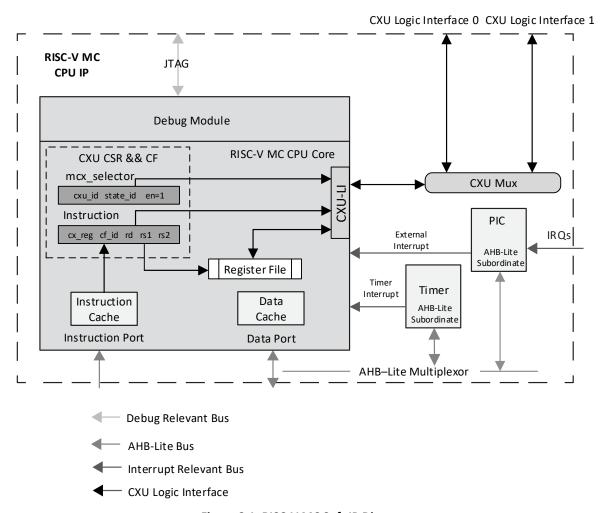

The RISC-V MC CPU IP processes data and instructions while monitoring external interrupts. As shown in Figure 2.1, the CPU IP has a 32-bit processor core and optional submodules. It uses a read-only AHB-Lite interface for instruction fetch and another AHB-Lite interface with read/write access for data access. See Table 2.5 and Table 2.6 for the AHB-Lite Instruction Fetch and Data Accessing ports definition. The CPU core, PIC, Timer, and AHB-Lite multiplexor run in the system clock domain. The Core Debug runs in both system clock domain and JTAG clock domain.

Figure 2.1. RISC-V MC Soft IP Diagram

## 2.2. Modules Description

#### 2.2.1. RISC-V Processor Core

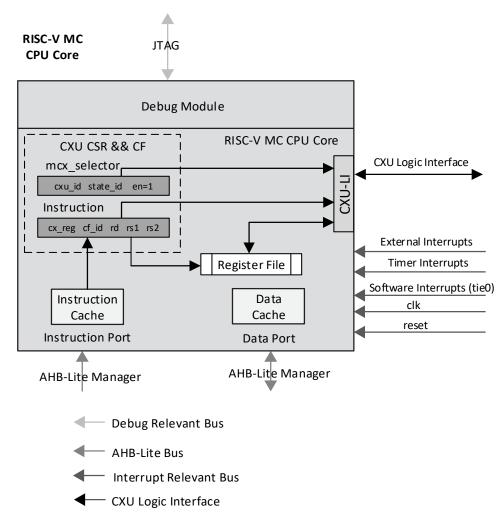

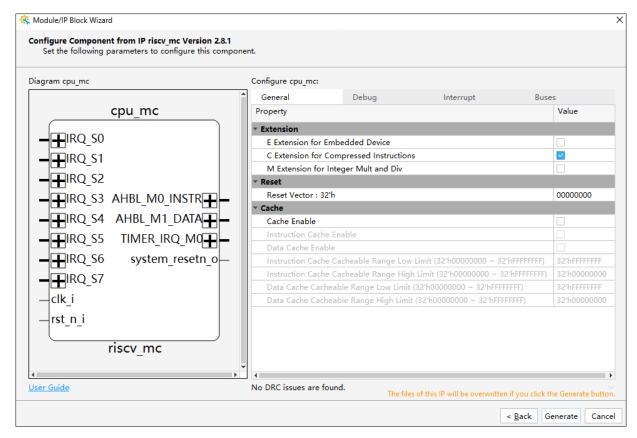

The processor core follows the RV32IMCE instruction set and the M, C, and E extensions are optional in Module/IP Block Wizard GUI General Tab, as shown in Figure 2.3. Figure 2.2 shows the processor core block diagram.

9

Figure 2.2. RISC-V MC Processor Core Block Diagram

#### 2.2.1.1. Reset Vector

The reset vector of the processor is configurable through the Reset Vector attribute, which is under the General tab in the Module/IP Block Wizard GUI (Figure 2.3).

Figure 2.3. General Tab

#### 2.2.1.2. Instruction and Data Caches

The processor core supports optional instruction and data caches.

The instruction and data caches are both 4 KB two-way set associative, and each cache line contains 32 bytes. The cache strategy for data cache is write through, and the cache eviction policy of both caches is round robin.

As shown in Figure 2.3, the instruction and data caches can be enabled or disabled together by checking or unchecking the Cache Enable option when instantiating the CPU in the Lattice Propel design environment, and the cacheable address range can be configured by setting the Instruction/Data Cache Cacheable Address Range Low Limit and Instruction/Data Cache Cacheable Address Range High Limit parameters according to application demands.

To flush the caches, refer to annotations of cache.h in the driver codes. The cache invalidates the corresponding cache line and reloads it from memory the next time it is accessed. Those instructions are accepted only if the cache is enabled. If the cache is not enabled, those instructions raise an illegal instruction exception.

It should be noted that the instruction and data caches should only be enabled for Certus-N2, Lattice Avant, MachXO5-NX, CrossLink-NX, CertusPro-NX, and Certus-NX devices, as they have enough resources to support the caches.

#### 2.2.1.3. Branch Prediction

Processors with caches use dynamic target prediction for branches and processors without caches do not implement branch prediction.

#### 2.2.1.4. Debug

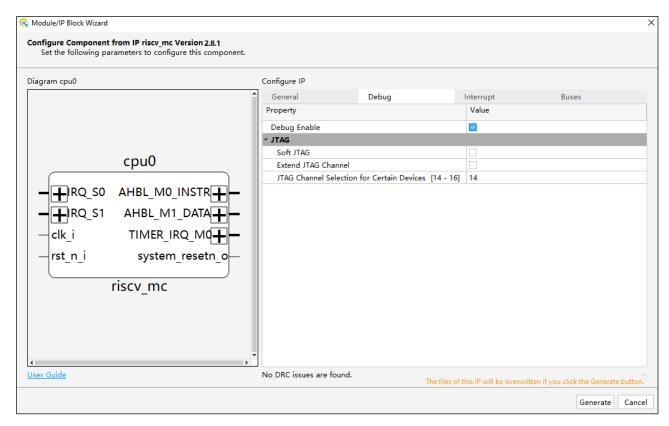

The processor core supports the IEEE-1149.1 JTAG debug logic with two hardware breakpoints.

To use the debug module, it is required to allow writes from the data port to the instruction memory in the SoC. Single-port instruction memory is not allowed to debug.

The JTAG channel is configurable in the Module/IP Block Wizard GUI, as shown in Figure 2.4. The channel range depends on the kind of FPGA device family. For Certus-N2 and Lattice Avant and Nexus family devices, the default JTAG channel range is 14–16. When enabling the Extend JTAG Channel attribute, the channel range enlarges from 14–16 to 14–24 for Certus-N2 and Lattice Avant family devices. For Nexus family devices, the channel range enlarges from 14–16 to 10–18. The soft JTAG is available on Certus-N2, Lattice Avant, MachXO5-NX, CrossLink-NX, CertusPro-NX, and Certus-NX devices. For more information, refer to Appendix B.

Figure 2.4. Debug Configuration Tab

#### 2.2.1.5. Interrupt

The core CPU's interrupts are level sensitive and high active. A given interrupt should remain asserted until cleared by the corresponding interrupt service routine.

#### 2.2.1.6. Exception

If an exception occurs, the processor core stops the corresponding instruction. It flushes the exception instruction and instructions in the pipeline fetched after the exception. Then, the core waits until all the flushed instructions reach the writeback stage before jumping to the exception service routine.

**Note:** In the firmware, the exception handler return address is fixed at mepc + 4. For the C compressed code, the exception recovery is not guaranteed.

Starting from version 2.7.0, the MC core supports the write response. A write error on the local and AXI bus on the processor causes the Store/Atomic Memory Operation (AMO) access fault exception of the core, with exception ID 7.

#### 2.2.1.7. WFI for Low Power

The processor core enters into low power mode with Wait For Interrupt (WFI) instruction. The program counter halts during low power mode, and the processor wakes up if there is an external or timer interrupt.

#### 2.2.1.8. Control and Status Registers

The processor core supports the Control and Status Registers (CSRs) listed in Table 2.1.

Table 2.1. RISC-V Processor Core Control and Status Registers

| CSR No. | CSR Name                                    | Access                            | Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x300   | Machine Status<br>(mstatus)                 | read/write                        | bit[12:11]: mpp, privilege mode before entering a trap, should always be 2'b11 in machine mode in this CPU core. bit[7]: mpie, mie before entering a trap, updates to mie value when entering a trap. bit[3]: mie, global interrupt enable.                                                                                                                                                                                                                                                                                                          |

| 0x301   | Machine ISA (misa)                          | read-only                         | bit[31:30]: base, hardwired 0x1, stands for RV32.<br>bit[25:0]: extension, stands for the supported ISAs.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x304   | Machine Interrupt<br>Enable (mie)           | read/write                        | bit[11]: meie, machine mode external interrupt enable. bit[7]: mtie, machine mode timer interrupt enable. bit[3]: msie, machine mode software interrupt enable.                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x305   | Machine Trap-Vector<br>Base-Address (mtvec) | read/write<br>initialized to 0x20 | bit[31:2]: trap vector base address, 4-byte aligned. bit[0]: trap vector mode, all traps set the program counter to the base address in the RISC-V MC CPU core. Bit[1] is not supported. Only 1'0 – direct mode and 1'b1 – vectored mode are available.                                                                                                                                                                                                                                                                                              |

| 0x340   | Machine Scratch<br>(mscratch)               | read/write                        | bit[31:0]: in machine mode, it is used to hold a pointer to a machine-mode hart-local context space and is swapped with a user register upon entry to a machine mode trap handler.                                                                                                                                                                                                                                                                                                                                                                   |

| 0x341   | Machine Exception<br>Program Counter (mepc) | read/write                        | bit[31:0]: when a trap is taken into machine mode, mepc is used to store the address of the instruction that encounters the exception.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x342   | Machine Cause (mcause)                      | read-only                         | bit[31]: 1'b1 – interrupt, 1'b0 – exception bit[3:0]: exception code for interrupt:  • 3 – machine software interrupt  • 7 – machine timer interrupt  • 11 – machine external interrupt for exception:  • 0 – instruction address misaligned  • 1 – instruction access fault  • 2 – illegal instruction  • 4 – load address misaligned  • 5 – load access fault                                                                                                                                                                                      |

| 0x343   | Machine Trap Value<br>(mtval)               | read-only                         | <ul> <li>mtval stores the bad address when an exception occurs in machine mode. The source of bad address can be:</li> <li>exceptions on dbus, such as access error, mmu exception, or unaligned access. In this condition, it contains dbus address.</li> <li>exceptions from CSRs, such as ecall and ebreak. In this condition, it contains the execute instruction.</li> <li>exceptions by fetch. It contains fetch pc.</li> <li>exceptions by decode. It contains the decoded instruction itself, not the address of the instruction.</li> </ul> |

| 0x344   | Machine Interrupt<br>Pending (mip)          | read/write                        | bit[11]: meip, machine mode external interrupt pending, read-only. bit[7] mtip, machine mode timer interrupt pending, read-only. bit[3] msip, machine mode software interrupt pending, readable and writable.                                                                                                                                                                                                                                                                                                                                        |

| 0xB00   | Machine Cycle (mcycle)                      | read/write                        | bit[31:0]: Machine cycle counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0xB02   | Machine Instructions-<br>Retired (minstret) | read/write                        | bit[31:0]: Machine instructions-retired counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CSR No. | CSR Name                                                         | Access     | Fields                               |

|---------|------------------------------------------------------------------|------------|--------------------------------------|

| 0xB80   | Upper 32 bits of<br>Machine Cycle (mcycleh)                      | read/write | bit[31:0]: Upper 32 bits of mcycle   |

| 0xB82   | Upper 32 bits of<br>Machine Instructions-<br>Retired (minstreth) | read/write | bit[31:0]: Upper 32 bits of minstret |

#### 2.2.1.9. Composable Extension Unit Logic Interface

CXU-LI defines a set of hardware logic signal interfaces that enable you to connect CPUs and composable extension units (CXU) easily. The term CXU is revised from Custom Function Unit (CFU). In Version 0.91.230803, 2023-08-03 of the RISC-V Composable Custom Extensions Specification, the term Custom Interface (CI) is replaced by Composable Extension (CX). The term CFU is replaced by CXU.

The composable extension unit is a kind of light-weight and customized arithmetic accelerator. With the support of CXU-LI, you can integrate CXUs into your SoC and insert custom functions (CF) to deploy CXU hardware, upon actual solution demand.

In the CXU-LI system, the CPU is the requester and the CXU is the responder. The CPU sends the CXU a request and eventually receives the CXU response. For each request, there is exactly one response.

The CXU-LI is stratified into four separate feature levels:

- L0: combinational;

- L1: fixed latency;

- L2: variable latency;

- L3: reordering.

You can choose an appropriate interface level and design the responder interface of the CXU. For user-friendliness and in compliance with the official spec, the MC core only supports one kind of interface level, L2. It has downward compatibility to support L0 or L1 as well. You can set some signal constant 0 or 1 to degrade L2 to L1 or L0.

The MC core is a -Zicx compatible core, with a mcx\_selector CSR added and can repurpose three custom function instruction formats. To deploy the resource of CXU, you only need two steps: interface multiplexing and executing CF instructions.

1. The first step is interface multiplexing, which requires writing a specific selector value to mcx\_selector CSR 0xBC0 to select the active CXU and state context.

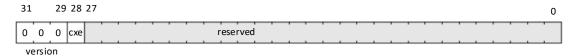

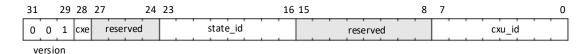

The mcx\_selector CSR 0xBC0 has the following fields:

Figure 2.5. mcx\_selector CSR 0xBC0 Version 0: Legacy Custom Instructions

Figure 2.6. mcx\_selector CSR 0xBC0 Version 1: Extension Multiplexing

- version: extension multiplexing version

- cxe: custom operation exception enable

- When version=0, disables composable extension multiplexing. When cxe=0, custom-0/1/2/3 instructions execute the CPU's built-in custom instructions and select the CPU's built-in custom CSRs. When cxe=1, custom-0/1/2/3 instruction accesses raise an illegal-instruction exception.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

- When version=1, enables version-1 composable extension multiplexing. The cxu\_id and state\_id fields select the current CXU and state context. When cxe=0, custom-0/1/2 instructions issue CXU requests of the CXU and state context identified by cxu\_id and state\_id. When cxe=1, custom-0/1/2 instruction accesses raise an illegal instruction exception.

- version values 2-7 are reserved.

- state\_id: selects the hart's current CXU's current state context.

- cxu id: selects the hart's current CXU's current state context.

- 2. The second step is the CPU issuing custom function instructions. When mcx\_selector.version=1, the specific function of a CF is defined by customers and identified by custom function identifier, CF\_ID. Each CXU packages a set of relevant custom functions. Each CF needs to be implemented by the hardware logic in the CXU. You can design the CXU according to specific scenarios.

In terms of CF instruction format, three CF formats/major opcodes are reused: custom-0, custom-1, and custom-2. These correspond to three different instructions encoding types: R-type, I-type, and flex-type.

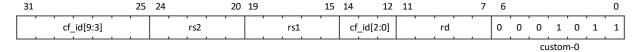

- Custom-0 R-type encoding

- Pseudo assembly code: cx reg cf id, rd, rs1, rs2

- An R-type CF instruction issues a CXU request for a zero-extended 10-bit CF\_ID cf\_id with two source register operands identified by rs1 and rs2. The CXU response data is written to the destination register rd.

Figure 2.7. CXU R-type Instruction Encoding

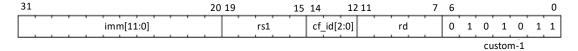

- Custom-1 I-type encoding

- Pseudo assembly code: cx\_imm cf\_id, rd, rs1, imm

- An I-type CF instruction issues a CXU request for a zero-extended 3-bit CF\_ID cf\_id with one source register operand identified by rs1 and a sign-extended 12-bit immediate value imm. The CXU response is written to the destination register rd.

Figure 2.8. CXU I-type Instruction Encoding

- Custom-2 flex-type encoding

- Pseudo assembly code: cx\_flex cf\_id, rs1, rs2

- Pseudo assembly code: cx flex25 custom

- A flex-type CF instruction issues a CXU request for a zero-extended 10-bit CF\_ID cf\_id with two source register operands identified by rs1 and rs2. There is no destination register and CXU response data is discarded. The instruction is executed purely for its effect upon the selected state context of the selected CXU.

Figure 2.9. CX Flex-type Instruction Encoding

Alternatively, the cx\_flex25 form of instruction issues an arbitrary 25-bit custom instruction.

Figure 2.10. CX Flex-type Instruction Alternate Encoding

A flex-type CF instruction may be used with a CXU-L2 request raw instruction field req\_insn to provide an arbitrary 25-bit custom request to a CXU. The absence of an integer destination register field is a feature that provides added, CPU-uninterpreted, custom instruction bits to a CXU.

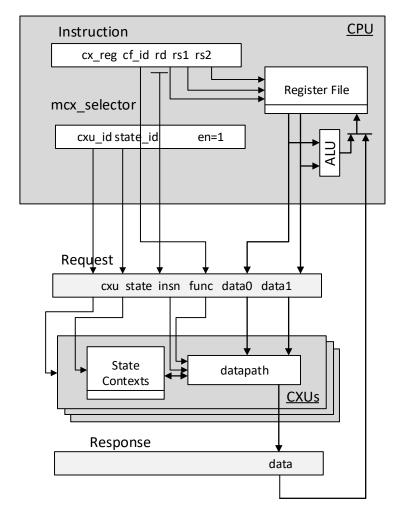

When the CPU issues a custom instruction, it produces a CXU request which has three sources: the fields of instruction, two source operands from the register file and/or an immediate field of instruction, and the cxu\_id and state\_id fields of mcx\_selector (Figure 2.11. ). The CXU request may include the CXU\_ID, STATE\_ID, raw instruction, CF\_ID, and operands. The CXU\_ID identifies which CXU must process the request. The CXU includes state context(s) and a data path. The STATE\_ID selects the state context to use for this request. For custom-0 and custom-1 instructions, the CXU processes the request, possibly updating this state context, and produces a CXU response, which may include the response data. The CPU commits the custom function instructions by writing the response data to the destination register. For custom-2 instructions that do not write response data to the CPU register, the CXU only processes the request, possibly updating this state context. The response data is invalid for the CPU. The CPU commits all the custom-2 instructions by default.

Figure 2.11. Execution of a Custom Function Instruction

Following is a pseudocode example illustrating CPU issuing stateful CF instructions f0 and f1 to CXU0, f2 and f3 to CXU1, and f4 to CXU0 again.

```

csrw mcx_selector,x20 ; version=1, cxe=0, select CXU_ID=0 and STATE_ID=0

cxu_reg 0,x3,x1,x2 ; u0.f0

cxu_reg 1,x6,x5,x4 ; u0.f1

csrw mcx_selector,x21 ; version=1, cxe=0, select CXU_ID=1 and STATE_ID=0

cxu_reg 2,x9,x7,x8 ; u1.f2

cxu_reg 3,x12,x11,x10 ; u1.f3

csrw mcx_selector,x20 ; version=1, cxe=0, select CXU_ID=0 and STATE_ID=0 again

cxu_reg 4,x15,x13,x14 ; u0.f4

```

- 1. Write mcx\_selector for CXU\_ID=0 and STATE\_ID=0. Issue two CF instructions to CXU0.

- 2. Write mcx selector for CXU ID=1 and STATE ID=0. Issue two CF instructions to CXU1.

- 3. Write mcx selector for CXU ID=0 and STATE ID=0. Issue one CF instruction to CXU0.

#### 2.2.1.10. System Reset Output

The system\_resetn\_o signal is driven in two ways. When debug is not enabled or if debug reset is not issued, system\_resetn\_o is the passed value from the input reset signal rst\_n\_i. It is asynchronous with input clock. When the debugger is enabled and debug reset is issued, the debug reset signal is synchronized to system clock domain and the system resetn o is the output of the synchronized signal.

#### 2.2.1.11. RISC-V Formal Interface

The RISC-V Formal Interface is supported. This interface can help you get many important information directly, including the privilege mode, trap, instruction, and so on.

#### 2.2.2. Submodule

The CPU soft IP contains two submodules: PIC and Timer. The PIC and Timer share the same start address in the memory map and a fixed 2 KB address range is allocated, if either the PIC or Timer attribute is enabled under the Interrupt tab in the Module/IP Block Wizard GUI (Figure 2.12).

Figure 2.12. Interrupt Tab

#### 2.2.2.1. PIC

The PIC aggregates up to eight external interrupt inputs (IRQs) into one interrupt output to the processor core. The interrupt status register can be used to read the values of IRQs. Individual IRQs can be configured by programming the corresponding PIC\_STATUS, PIC\_ENABLE, PIC\_SET, and PIC\_POL registers. All registers can be accessed through the CPU's internal AHB-Lite interface, as shown in Figure 2.13.

Figure 2.13. PIC Block Diagram

Table 2.2 provides the description of PIC registers.

**Table 2.2. PIC Registers**

| Offset                                                                                                                                                                                                 | Name       | Descriptio                                            | n                                                                         |        |                |                     |                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------|---------------------------------------------------------------------------|--------|----------------|---------------------|----------------|

|                                                                                                                                                                                                        |            | Access: rea                                           | tatus Register ad-write izable width: min=2, ma he pending interrupt at o |        | interrupt requ | uest port (irq[i] : | at top level). |

|                                                                                                                                                                                                        |            | [N-1]                                                 | PIC_STATUS [N-1]                                                          | RW     | 1              | 0x0                 |                |

|                                                                                                                                                                                                        |            |                                                       |                                                                           |        |                |                     |                |

|                                                                                                                                                                                                        |            | [1]                                                   | PIC_STATUS [1]                                                            | RW     | 1              | 0x0                 |                |

| 0x000                                                                                                                                                                                                  | PIC_STATUS | [0]                                                   | PIC STATUS [0]                                                            | RW     | 1              | 0x0                 |                |

|                                                                                                                                                                                                        |            | <ul><li>Write</li><li>0 − No</li><li>1 − Cl</li></ul> | terrupt pending at irq[i]  o effect ear interrupt status for i            | -q[i]  |                |                     |                |

| Interrupt Enable Register  Access: read-write Parameterizable width: min=2, max=32 Indicates whether the processor responds to the interrupt from corr request port (irq[i]) or not.  0x004 PIC_ENABLE |            |                                                       |                                                                           |        |                | n corresponding     | interrupt      |

|                                                                                                                                                                                                        | _          | Field                                                 | Name                                                                      | Access | Width          | Reset               |                |

|                                                                                                                                                                                                        |            | [N-1]                                                 | PIC_ENABLE[N-1]                                                           | RW     | 1              | 0x0                 |                |

|                                                                                                                                                                                                        |            |                                                       |                                                                           |        |                |                     | _              |

|                                                                                                                                                                                                        |            | [1]                                                   | PIC_ENABLE[1]                                                             | RW     | 1              | 0x0                 |                |

|                                                                                                                                                                                                        |            | [0]                                                   | PIC_ENABLE[0]                                                             | RW     | 1              | 0x0                 |                |

| 0 – irq[i] disabled    |  |  |  |  |  |  |  |

|------------------------|--|--|--|--|--|--|--|

| • 1 – irq[i] enabled   |  |  |  |  |  |  |  |

| Write                  |  |  |  |  |  |  |  |

| • 0 – Disable irq[i]   |  |  |  |  |  |  |  |

| • 1 – Enable irq[i]    |  |  |  |  |  |  |  |

| Interrupt Set Register |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

| I                      |  |  |  |  |  |  |  |

| PIC_SET[i]:            |  |  |  |  |  |  |  |

| Read                   |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

| I                      |  |  |  |  |  |  |  |

| PIC_POL[i]:            |  |  |  |  |  |  |  |

| Read                   |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |

**Note**: The register definition of PIC follows Lattice Interrupt Interface (LINTR) Standard, refer to Lattice Memory Mapped Interface and Lattice Interrupt Interface User Guide (FPGA-UG-02039) for more information.

#### 2.2.2.2 Timer

The Timer module provides a 64-bit real-time counter register, mtime, and time compare register, mtimecmp. An output interrupt signal notifies the RISC-V processor core when the value of mtime is greater than or equal to the value of mtimecmp. All registers can be accessed through the CPU's internal AHB-Lite interface, as shown in Figure 2.14.

Figure 2.14. Timer Block Diagram

Table 2.3 provides the description of Timer registers.

**Table 2.3. Timer Registers**

| Offset | Name        | Descriptio                                             | Description                                                                                                             |                                                                       |                 |                           |  |

|--------|-------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|---------------------------|--|

|        |             | Lower 32 bits of Timer counter register.               |                                                                                                                         |                                                                       |                 |                           |  |

|        |             | Field                                                  | Name                                                                                                                    | Access                                                                | Width           | Reset                     |  |

| 0x400  | TIMER_CNT_L | [63:0]                                                 | mtime                                                                                                                   | RW                                                                    | 64              | 0x0                       |  |

|        |             |                                                        | mtime A 64-bit real-time counter register. You must set the register to a non-zero value to start the counting process. |                                                                       |                 |                           |  |

| 0x404  | TIMER_CNT_H | Higher 32                                              | Higher 32 bits of Timer counter register.                                                                               |                                                                       |                 |                           |  |

|        |             | Lower 32 l                                             |                                                                                                                         |                                                                       |                 |                           |  |

|        |             | Field                                                  | Name                                                                                                                    | Access                                                                | Width           | Reset                     |  |

|        |             | [62.61                                                 |                                                                                                                         |                                                                       |                 |                           |  |

|        |             | [63:0]                                                 | mtimecmp                                                                                                                | RW                                                                    | 64              | 0x0                       |  |

| 0x410  | TIMER_CMP_L | mtimecmp<br>This regist<br>value of m<br>register, The | •                                                                                                                       | or clear the time<br>er than or equal to<br>rted.<br>ntil mtimecmp be | r interrupt, mi | tip. When the<br>mtimecmp |  |

## 2.3. Signal Description

Table 2.4 to Table 2.7 list the ports of the CPU soft IP in different categories. As shown in Figure 2.15, the AHB-Lite, CXU-LI, and RVFI interfaces can be configured and enabled under the Buses tab in the Module/IP Block Wizard. The Interrupt Interface can be configured under the Interrupt tab, as shown in Figure 2.12.

Figure 2.15. Buses Tab

#### 2.3.1. Clock and Reset