## **LTP1 Hardware Checklist**

### **Technical Note**

FPGA-TN-02417-1.0

September 2025

## Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Inclusive Language

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language [FAQ 6878](#) for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## Contents

|                                                           |    |

|-----------------------------------------------------------|----|

| Contents .....                                            | 3  |

| Abbreviations in This Document.....                       | 4  |

| 1. Introduction.....                                      | 5  |

| 2. DC-SCM 2.0 Requirements .....                          | 6  |

| 3. FPGA Pin Assignments .....                             | 7  |

| 3.1.    MachXO3 and MachXO3D Devices .....                | 7  |

| 3.2.    MachXO5-NX Devices.....                           | 7  |

| 4. PCB Trace Length .....                                 | 8  |

| 5. Computing and Measuring Input Setup and Hold time..... | 9  |

| 6. Clock Oscillator Supply Filtering .....                | 11 |

| 7. Checklist.....                                         | 12 |

| References .....                                          | 13 |

| Technical Support Assistance .....                        | 14 |

| Revision History .....                                    | 15 |

## Figures

|                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. AC-Coupled LVDS Link.....                                                                                 | 6  |

| Figure 2.2. LVDS Link Resistor Value.....                                                                             | 6  |

| Figure 5.1. Measuring the Input Data Setup before EClk ( $t_{SU}$ ) and Input Data Hold after EClk ( $t_{HO}$ ) ..... | 9  |

| Figure 5.2. Measuring the Input Data Valid after CLK ( $t_{DVA}$ ) and Input Data Hold after CLK ( $t_{DVE}$ ) .....  | 10 |

| Figure 6.1. Clock Oscillator Bypassing .....                                                                          | 11 |

## Tables

|                                                                      |    |

|----------------------------------------------------------------------|----|

| Table 2.1. LVDS Electrical Requirements .....                        | 6  |

| Table 5.1. MachXO3 and MachXO3D DDRX4 Setup and Hold Time .....      | 9  |

| Table 5.2. MachXO5-NX DDRX5 Setup and Hold Time .....                | 9  |

| Table 5.3. MachXO3 and MachXO3D DDRX4 Data Valid and Hold Time ..... | 10 |

| Table 5.4. MachXO5-NX DDRX5 Data Valid and Hold Time .....           | 10 |

| Table 7.1. Hardware Checklist .....                                  | 12 |

## Abbreviations in This Document

A list of abbreviations used in this document.

| Abbreviation | Definition                                                          |

|--------------|---------------------------------------------------------------------|

| AC           | Alternating Current                                                 |

| BGA          | Ball Grid Array                                                     |

| CPLD         | Complex Programmable Logic Device                                   |

| DC           | Direct Current                                                      |

| DC-SCM       | Data Center – Secure Control Module                                 |

| DDR          | Dual Data Rate                                                      |

| FPGA         | Field-Programmable Gate Array                                       |

| HPM          | Host Processor Module                                               |

| I/O          | Input/Output                                                        |

| LVDS         | Low-Voltage Differential Signaling                                  |

| LTP1         | Low-Voltage Differential Signaling Tunneling Protocol and Interface |

| OCP          | Open Compute Project                                                |

| OSC          | Oscillator                                                          |

| PCB          | Printed Circuit Board                                               |

| RTT          | LVDS termination resistor                                           |

| Rx           | Receiver                                                            |

| SCM          | Secure Control Module                                               |

| Tx           | Transmitter                                                         |

## 1. Introduction

This technical note provides key hardware implementation guidelines for deploying the LVDS Tunnelling Protocol and Interface (LTPI) in an OCP Ready™ environment. This technical note includes a high-level checklist to verify that the LTPI-LVDS port supports the maximum data rate for the target device, complies with the latest OCP specifications, and ensures hardware interoperability with other OCP-compliant vendors.

Developed after evaluation boards, hardware checklists incorporate optimized designs that supersede the circuitry of the evaluation boards. If you copy circuits from evaluation boards, ensure that you optimize your design according to hardware checklists.

Refer to the following documents for detailed recommendations:

- [MachXO3 Hardware Checklist \(FPGA-TN-02061\)](#)

- [MachXO3D Hardware Checklist \(FPGA-TN-02104\)](#)

- [MachXO5-NX Hardware Checklist \(FPGA-TN-02274\)](#)

- [PCB Layout Recommendations for BGA Packages \(FPGA-TN-02024\)](#)

- [High-Speed PCB Design Considerations \(FPGA-TN-02178\)](#)

- [Implementing High-Speed Interfaces with MachXO3 Devices \(FPGA-TN-02057\)](#)

- [Implementing High-Speed Interfaces with MachXO3D Usage Guide \(FPGA-TN-02065\)](#)

- [MachXO5-NX High-Speed I/O Interface \(FPGA-TN-02286\)](#)

- [LVDS Tunneling Protocol and Interface \(LTPI\) User Guide \(FPGA-RD-02247\)](#)

## 2. DC-SCM 2.0 Requirements

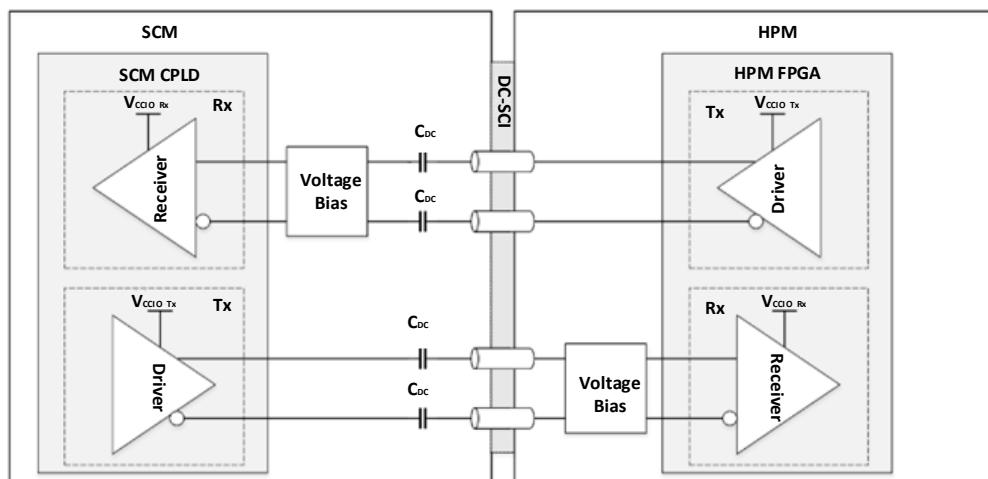

As defined in the [DC-SCM 2.0 Specification](#), the LVDS link is AC-coupled. As such, the following components are required on the hardware:

- DC Blocking Capacitor – placed on the SCM only.

- Voltage Bias Circuit – placed close to the LVDS Rx I/O Buffer.

To ensure these specifications are met within the board design, it is highly recommended that both the DC blocking capacitors and the voltage bias circuit be added externally on any user board design.

Figure 2.1. AC-Coupled LVDS Link

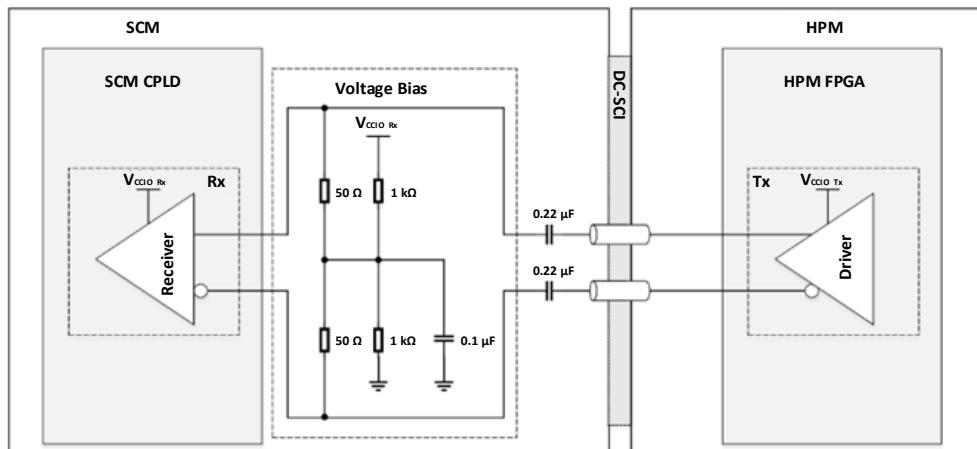

Figure 2.2. LVDS Link Resistor Value

Table 2.1. LVDS Electrical Requirements

| Parameter   | Minimum    | Maximum              | Description                                                                                        |

|-------------|------------|----------------------|----------------------------------------------------------------------------------------------------|

| VOD         | 100 mV     | 800 mV               | Output differential voltage swing                                                                  |

| VID         | 100 mV     | 800 mV               | Input differential voltage swing                                                                   |

| VCCIO Rx/Tx | 2.5 V      | 3.3 V                | LVDS VCCIO voltage. For more information, refer to the MachXO3, MachXO3D, or MachXO5-NX checklist. |

| VICM        | —          | (VCCIO RX / 2) + 20% | Input common mode voltage on LVDS I/O pins                                                         |

| CDC         | 0.22 μF    | —                    | DC blocking capacitor                                                                              |

| RTT         | 100 Ω – 5% | 100 Ω + 5%           | LVDS termination resistor, which can be set internally on the device.                              |

## 3. FPGA Pin Assignments

This section provides guidance on the FPGA pin assignments for the input and output LVDS link.

### 3.1. MachXO3 and MachXO3D Devices

The FPGA pin assignments for MachXO3™ and MachXO3D™ devices are as follows:

- Input LVDS: These signals are assigned only to A/B pairs (PBxxA/PBxxB) on Bank 2. In addition, the LVDS clock is assigned to a PCLK pin (PCLKT2\_x /PCLKC2\_x).

- Output LVDS: These signals are assigned only to A/B pairs (PTxxA/PTxxB) on Bank 0.

### 3.2. MachXO5-NX Devices

For MachXO5™-NX devices, the FPGA pin assignments for the LVDS pairs (both input and output) are mapped to high-performance I/O banks, specifically the bottom banks.

## 4. PCB Trace Length

PCB length differences on the LTP1 LVDS link must be managed to ensure DDR timing parameters are met:

- The PCB trace length difference between the LVDS pair (\*\_DN and \*\_DP) is less than 5 mil.

- The PCB trace length difference between CLK and Data for each lane is less than 200 mil.

## 5. Computing and Measuring Input Setup and Hold time.

By default, the LTPi LVDS link uses:

- GDDR4\_RX\_CENTERED for MachXO3 or MachXO3D devices

- GDDR5\_RX\_ECLK\_CENTERED for MachXO5-NX devices

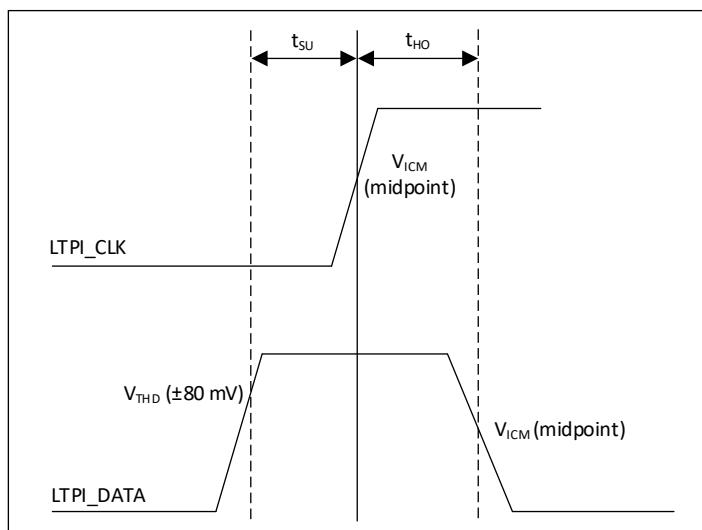

To ensure the link meets the maximum LTPi speed, the measured Input Data Setup before ECLK ( $t_{SU}$ ) and Input Data Hold after ECLK ( $t_{HO}$ ) must exceed the minimum values specified in [Table 5.1](#) and [Table 5.2](#).

Timing measurements for  $t_{SU}$  and  $t_{HO}$  are defined as follows:

- $t_{SU}$  is measured from  $V_{THD}$  ( $\pm 80$  mV) of the LTPi\_DATA signal to  $V_{ICM}$  of LTPi\_CLK.

- $t_{HO}$  is measured from  $V_{ICM}$  of LTPi\_CLK to  $V_{ICM}$  of LTPi\_DATA, as shown in [Figure 5.1](#).

**Table 5.1. MachXO3 and MachXO3D DDRX4 Setup and Hold Time**

| Parameter                                                                                    | Description                  | Device   | Speed Grade – 6 | Speed Grade – 5 | Units |

|----------------------------------------------------------------------------------------------|------------------------------|----------|-----------------|-----------------|-------|

| <b>Generic DDR4 Inputs with Clock and Data Centered – GDDR4_RX.ECLK.Centered<sup>1</sup></b> |                              |          |                 |                 |       |

| $t_{SU}$                                                                                     | Input Data Setup before ECLK | MachXO3  | 0.233           | 0.233           | ns    |

| $t_{HO}$                                                                                     | Input Data Hold after ECLK   | MachXO3D | 0.287           | 0.287           | ns    |

**Note:**

1. The duty cycle is  $\pm 5\%$  for system usage.

**Table 5.2. MachXO5-NX DDRX5 Setup and Hold Time**

| Parameter                                                                            | Description                  | Device     | Speed Grade – 9 | Speed Grade – 8 | Speed Grade – 7 | Units |

|--------------------------------------------------------------------------------------|------------------------------|------------|-----------------|-----------------|-----------------|-------|

| <b>Generic DDRX5 Inputs with Clock and Data Centered – GDDR5_RX/TX.ECLK.CENTERED</b> |                              |            |                 |                 |                 |       |

| $t_{SU}$                                                                             | Input Data Setup before ECLK | MachXO5-NX | 0.231           | 0.231           | 0.224           | ns    |

| $t_{HO}$                                                                             | Input Data Hold after ECLK   |            | 0.289           | 0.229           | 0.224           | ns    |

**Figure 5.1. Measuring the Input Data Setup before EClk ( $t_{SU}$ ) and Input Data Hold after EClk ( $t_{HO}$ )**

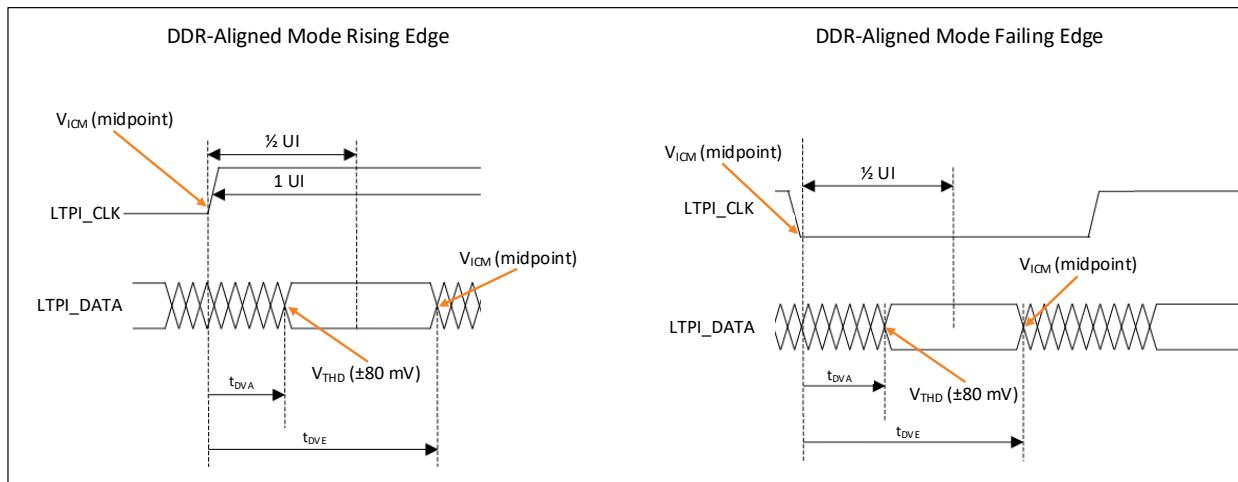

Aside from the default DDR gearing, the LVDS link can be set to GDDR4\_RX.ECLK.Centered for MachXO3 or MachXO3D devices and GDDR5\_RX/TX.ECLK.Centered for MachXO5-NX devices. To ensure it meets the maximum LTPi speed, the measured Input Data Valid after CLK ( $t_{DVA}$ ) and Input Data Hold after CLK ( $t_{DVE}$ ) must not exceed the maximum value, while the Input Data Hold after CLK ( $t_{DVE}$ ) must also exceed the minimum value specified in [Table 5.3](#) and [Table 5.4](#).

Timing measurements for  $t_{SU}$  and  $t_{HO}$  are defined as follows:

- $t_{DVA}$  is measured from  $V_{ICM}$  of the LTPi\_CLK signal to  $V_{THD}$  of LTPi\_DATA.

- $t_{DVE}$  is measured from  $V_{THD}$  of LTPi\_DATA to  $V_{ICM}$  of LTPi\_DATA, as shown in [Figure 5.2](#).

**Table 5.3. MachXO3 and MachXO3D DDRX4 Data Valid and Hold Time**

| Parameter                                                                      | Description                | Device   | Speed Grade – 6 | Speed Grade – 5 | Units |

|--------------------------------------------------------------------------------|----------------------------|----------|-----------------|-----------------|-------|

| <b>Generic DDR4 Inputs with Clock and Data Aligned – GDDR4_RX.ECLK.Aligned</b> |                            |          |                 |                 |       |

| $t_{DVA}$                                                                      | Input Data Valid after CLK | MachXO3  | 0.384 (max)     | 0.4 (max)       | ns    |

| $t_{DVE}$                                                                      | Input Data Hold after CLK  | MachXO3D | 0.9775 (min)    | 0.874 (min)     | ns    |

**Table 5.4. MachXO5-NX DDRX5 Data Valid and Hold Time**

| Parameter                                                                           | Description                | Device     | Speed Grade – 9 | Speed Grade – 8 | Speed Grade – 7 | Units |

|-------------------------------------------------------------------------------------|----------------------------|------------|-----------------|-----------------|-----------------|-------|

| <b>Generic DDRX5 Inputs with Clock and Data Centered – GDDR5_RX/TX.ECLK.Aligned</b> |                            |            |                 |                 |                 |       |

| $t_{DVA}$                                                                           | Input Data Valid after CLK | MachXO5-NX | 0.18 (max)      | 0.188 (max)     | 0.225 (max)     | ns    |

| $t_{DVE}$                                                                           | Input Data Hold after CLK  |            | 0.62 (min)      | 0.646 (min)     | 0.775 (min)     | ns    |

**Figure 5.2. Measuring the Input Data Valid after CLK ( $t_{DVA}$ ) and Input Data Hold after CLK ( $t_{DVE}$ )**

## 6. Clock Oscillator Supply Filtering

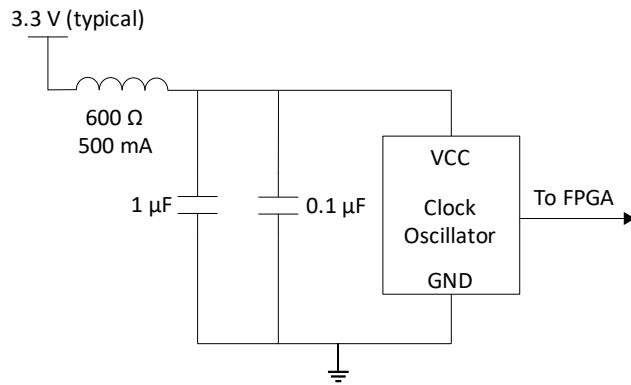

Use a low-ppm (less than 1%) reference clock for LTP1. Ensure the oscillator's power supply is properly isolated and decoupled. A typical bypassing circuit is shown in [Figure 6.1](#).

**Figure 6.1. Clock Oscillator Bypassing**

## 7. Checklist

**Table 7.1. Hardware Checklist**

| Section | Item                                                                | OK | N/A |

|---------|---------------------------------------------------------------------|----|-----|

| 1       | DC Blocking Capacitor                                               |    |     |

| 2       | Voltage Bias Circuit                                                |    |     |

| 3       | LTP1 LVDS Pin Assignment                                            |    |     |

| 2.2     | PCB Trace Length difference between LTP1 LVDS pair                  |    |     |

| 2.3     | PCB Trace Length difference between CLK to Data for each lane       |    |     |

| 2.3.1   | Computing and Measuring Input Setup and Hold time in LTP1 LVDS port |    |     |

| 2.4     | Clock OSC low ppm                                                   |    |     |

## References

- [MachXO3 Hardware Checklist \(FPGA-TN-02061\)](#)

- [MachXO3D Hardware Checklist \(FPGA-TN-02104\)](#)

- [MachXO5-NX Hardware Checklist \(FPGA-TN-02274\)](#)

- [PCB Layout Recommendations for BGA Packages \(FPGA-TN-02024\)](#)

- [High-Speed PCB Design Considerations \(FPGA-TN-02178\)](#)

- [Implementing High-Speed Interfaces with MachXO3 Devices \(FPGA-TN-02057\)](#)

- [Implementing High-Speed Interfaces with MachXO3D Usage Guide \(FPGA-TN-02065\)](#)

- [MachXO5-NX High-Speed I/O Interface \(FPGA-TN-02286\)](#)

- [LVDS Tunneling Protocol and Interface \(LTP1\) User Guide \(FPGA-RD-02247\)](#)

- [Open Compute Project web page](#)

- [MachXO3 web page](#)

- [MachXO3D web page](#)

- [MachXO5-NX web page](#)

- [Lattice Solutions IP Cores web page](#)

- [Lattice Solutions Reference Designs web page](#)

- [Lattice Insights web page for Lattice Semiconductor training courses and learning plans](#)

## Technical Support Assistance

Submit a technical support case through [www.latticesemi.com/techsupport](http://www.latticesemi.com/techsupport).

For frequently asked questions, please refer to the Lattice Answer Database at [www.latticesemi.com/Support/AnswerDatabase](http://www.latticesemi.com/Support/AnswerDatabase).

## Revision History

### Revision 1.0, September 2025

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

[www.latticesemi.com](http://www.latticesemi.com)