# **Golden System Reference Design and Demo User Guide v1.0 for Lattice Avant-E Devices**

**Lattice Propel 2024.1**

**Lattice Radiant 2024.1.1**

## **Reference Design**

FPGA-RD-02296-1.1

December 2025

## Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Inclusive Language

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language [FAQ 6878](#) for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# Contents

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Contents .....                                                                                    | 3  |

| Abbreviations in This Document.....                                                               | 9  |

| 1. Introduction .....                                                                             | 10 |

| 1.1. Overview of the System.....                                                                  | 10 |

| 1.2. Quick Facts .....                                                                            | 10 |

| 1.3. Features .....                                                                               | 11 |

| 1.4. Naming Conventions .....                                                                     | 11 |

| 1.4.1. Nomenclature.....                                                                          | 11 |

| 1.4.2. Signal Names .....                                                                         | 11 |

| 2. Functional Description.....                                                                    | 12 |

| 2.1. System Architecture Overview.....                                                            | 12 |

| 2.1.1. Avant-AT-E.....                                                                            | 12 |

| 2.2. Clocking .....                                                                               | 13 |

| 2.2.1. Clocking Overview for Avant-AT-E.....                                                      | 13 |

| 2.3. Reset Scheme.....                                                                            | 14 |

| 2.4. IP Configurations.....                                                                       | 14 |

| 2.4.1. RISC-V RX CPU Core .....                                                                   | 14 |

| 2.4.2. LPDDR4 Memory Controller .....                                                             | 17 |

| 2.4.3. QSPI Flash Controller.....                                                                 | 18 |

| 2.4.4. Tri-Speed Ethernet MAC.....                                                                | 18 |

| 2.4.5. Scatter-Gather DMA.....                                                                    | 19 |

| 2.4.6. UART.....                                                                                  | 20 |

| 2.4.7. GPIO .....                                                                                 | 20 |

| 2.4.8. Multi-Boot Configuration Module.....                                                       | 21 |

| 2.4.9. System Memory .....                                                                        | 21 |

| 2.5. System Level Interfaces.....                                                                 | 22 |

| 2.6. SoC Memory/Address Map .....                                                                 | 22 |

| 2.7. Functional Operation .....                                                                   | 23 |

| 3. Signal Description .....                                                                       | 24 |

| 4. Software Components .....                                                                      | 25 |

| 4.1. Primary and Golden Bootloader .....                                                          | 25 |

| 4.2. Primary and Golden Application .....                                                         | 25 |

| 5. Design Constraints.....                                                                        | 26 |

| 5.1. I/O Constraints .....                                                                        | 26 |

| 6. Resource Utilization.....                                                                      | 31 |

| 7. Demo User Guide .....                                                                          | 32 |

| 7.1. Boot-Up Sequence .....                                                                       | 32 |

| 7.2. Prerequisites .....                                                                          | 34 |

| 7.2.1. Software Requirements.....                                                                 | 34 |

| 7.2.2. Avant-AT-E Requirements .....                                                              | 34 |

| 7.3. Implementing the GHRD/GSRD Demo .....                                                        | 36 |

| 7.3.1. Setting up the UART Terminal .....                                                         | 36 |

| 7.3.2. Setting up the Non-Volatile Memory Register .....                                          | 37 |

| 7.3.3. Programming the Standalone Golden or Primary GSRD Bitstream and Application Software ..... | 37 |

| 7.3.4. Programming the Golden, Primary Software and MCS file .....                                | 49 |

| 8. Compiling the Reference Design .....                                                           | 61 |

| 8.1. Building the Bootloader and FreeRTOS Binary Files Using Lattice Propel SDK .....             | 61 |

| 8.2. Validating and Generating the GSRD Design using Propel Builder .....                         | 76 |

| 8.3. Synthesizing the RTL Files and Generating the Bitstream using Lattice Radiant .....          | 80 |

| 8.4. Generating the Multi-Boot MCS File .....                                                     | 85 |

| 9. Customizing the IP in the GSRD Design .....                                                    | 90 |

| 9.1. Changing QSPI Flash Controller User Interface Parameters .....                               | 90 |

|                                    |    |

|------------------------------------|----|

| References .....                   | 94 |

| Technical Support Assistance ..... | 95 |

| Revision History.....              | 96 |

## Figures

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

| Figure 2.1. GHRD Architecture on Avant-AT-E.....                                                   | 12 |

| Figure 2.2. Clocking Structure for Avant-AT-E GSRD .....                                           | 13 |

| Figure 2.3. Reset Structure for Avant-AT-E GSRD.....                                               | 14 |

| Figure 2.4. CPU Configuration – General.....                                                       | 15 |

| Figure 2.5. CPU Configuration – Debug .....                                                        | 15 |

| Figure 2.6. CPU Configuration – Buses .....                                                        | 16 |

| Figure 2.7. CPU Configuration – Interrupt.....                                                     | 16 |

| Figure 2.8. CPU Configuration – UART.....                                                          | 17 |

| Figure 2.9. LPDDR4 MC Configuration .....                                                          | 17 |

| Figure 2.10. QSPI Flash Controller Configuration .....                                             | 18 |

| Figure 2.11. TSE MAC Configuration.....                                                            | 19 |

| Figure 2.12. SGDMA Configuration.....                                                              | 19 |

| Figure 2.13. UART Configuration .....                                                              | 20 |

| Figure 2.14. GPIO Configuration.....                                                               | 20 |

| Figure 2.15. Multi-Boot Configuration.....                                                         | 21 |

| Figure 2.16. System Memory Configuration.....                                                      | 21 |

| Figure 6.1. GSRD Resource Utilization on Avant-AT-E70                                              | 31 |

| Figure 7.1. GSRD Boot-Up Sequence .....                                                            | 33 |

| Figure 7.2 .Avant-AT-E70 Evaluation Board.....                                                     | 34 |

| Figure 7.3.Ethernet PHY FMC Card.....                                                              | 35 |

| Figure 7.4. Connections and Buttons needed for Demonstration.....                                  | 35 |

| Figure 7.5. UART Terminal Icon on Propel SDK Window .....                                          | 36 |

| Figure 7.6. UART Launch Terminal Window .....                                                      | 37 |

| Figure 7.7. Device Manager Window on PC .....                                                      | 37 |

| Figure 7.8. Launch Radiant Programmer from Windows Start.....                                      | 38 |

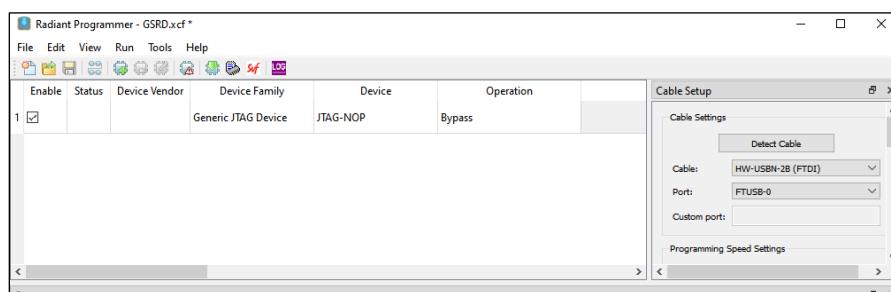

| Figure 7.9. Radiant Programmer Start Window .....                                                  | 38 |

| Figure 7.10. Radiant Programmer .xcf Window .....                                                  | 38 |

| Figure 7.11. Scan Device Icon on Radiant Programmer.....                                           | 39 |

| Figure 7.12. Select Device for Programming .....                                                   | 39 |

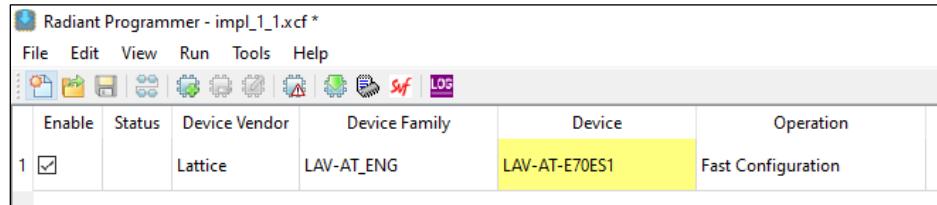

| Figure 7.13. Device Selected for Programmer.....                                                   | 39 |

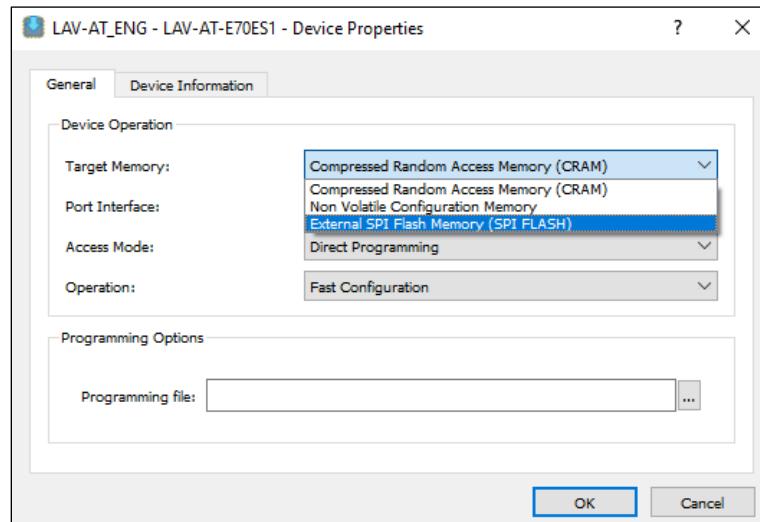

| Figure 7.14. Select the Target Memory for Programming.....                                         | 39 |

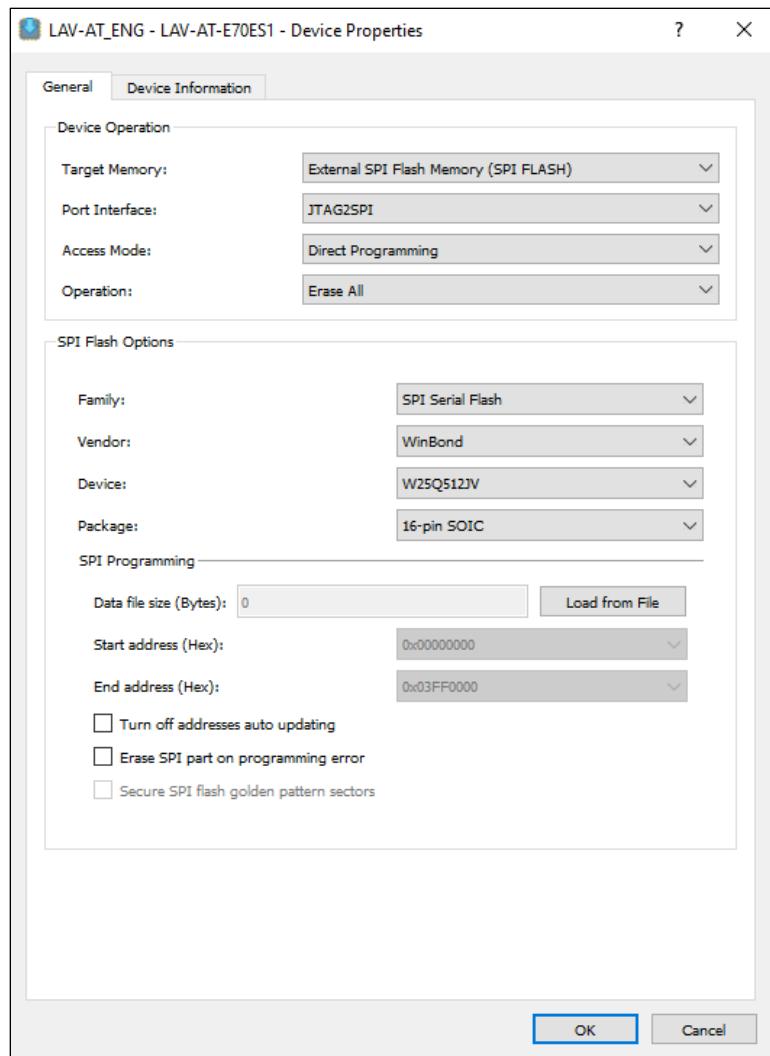

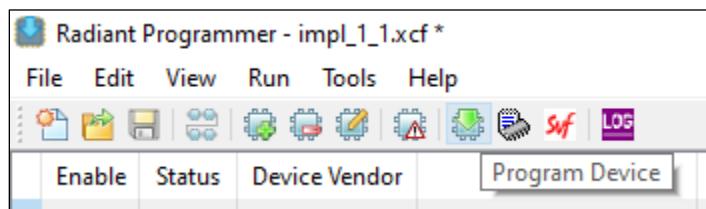

| Figure 7.15. Device Properties to Erase the SPI Flash .....                                        | 40 |

| Figure 7.16. Program Button to Program the SPI Flash .....                                         | 40 |

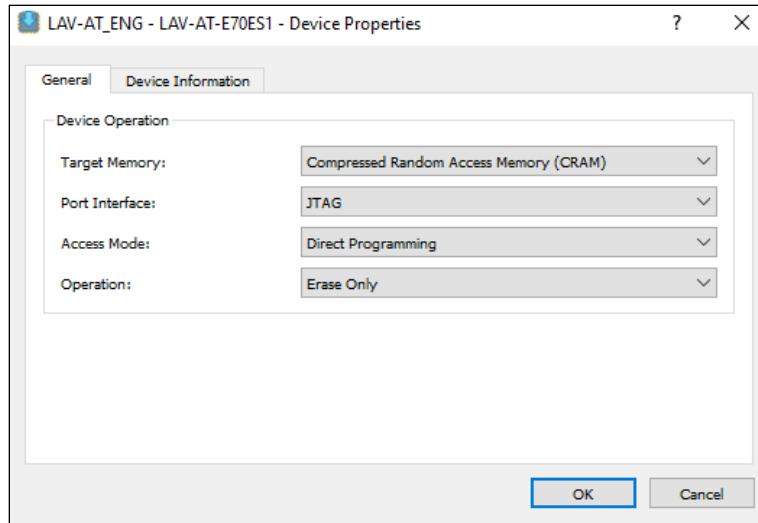

| Figure 7.17. Erase Only Operation for CRAM Programming.....                                        | 41 |

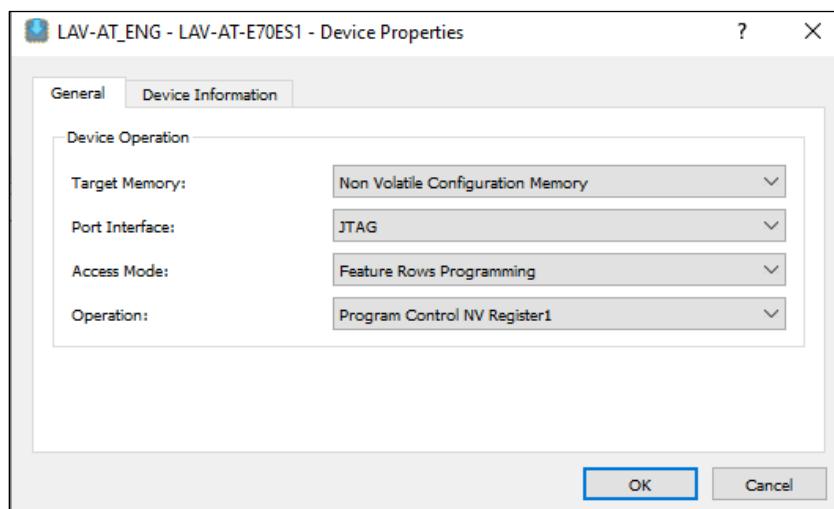

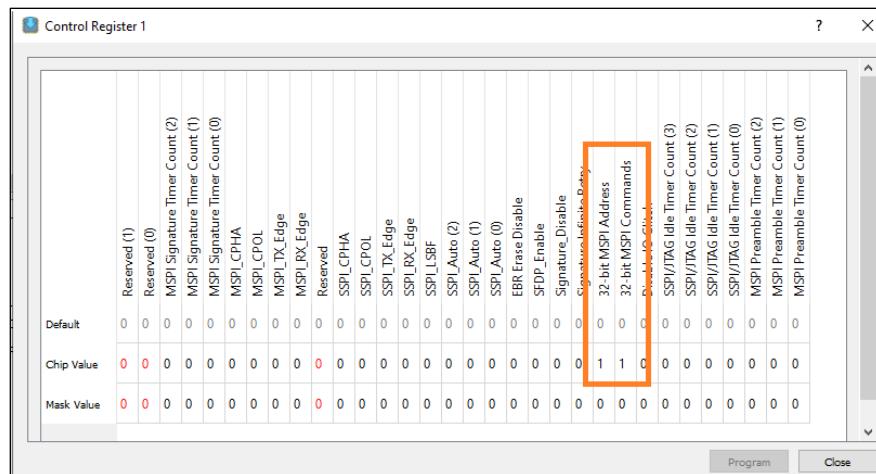

| Figure 7.18. One-Time Programmable Control NV Register1.....                                       | 41 |

| Figure 7.19. Settings to Select Chip Value .....                                                   | 42 |

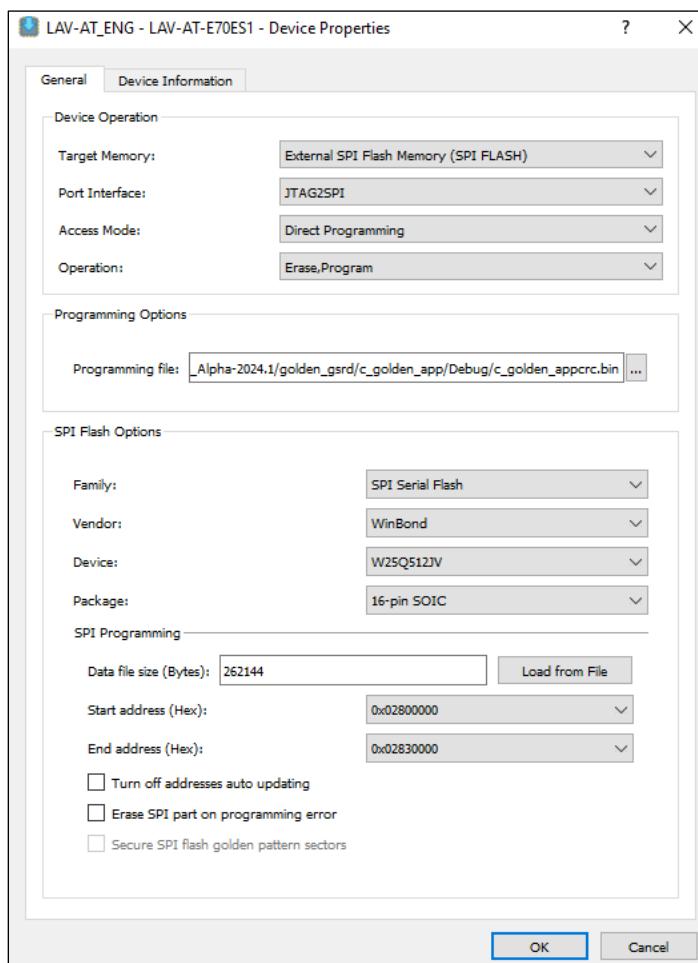

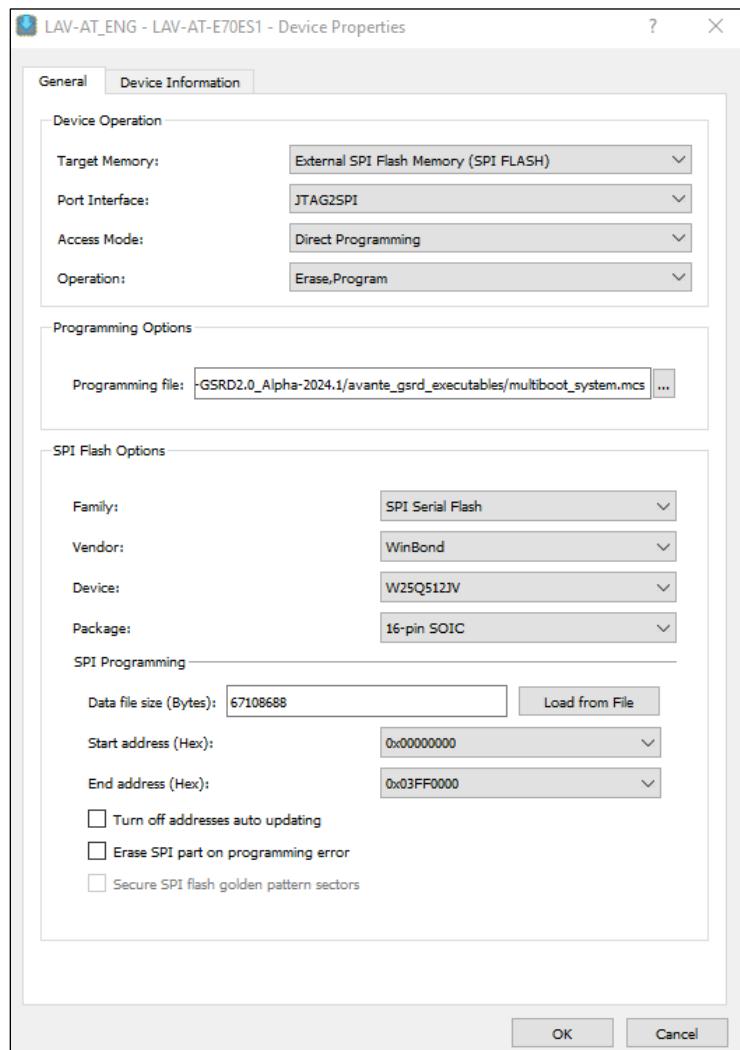

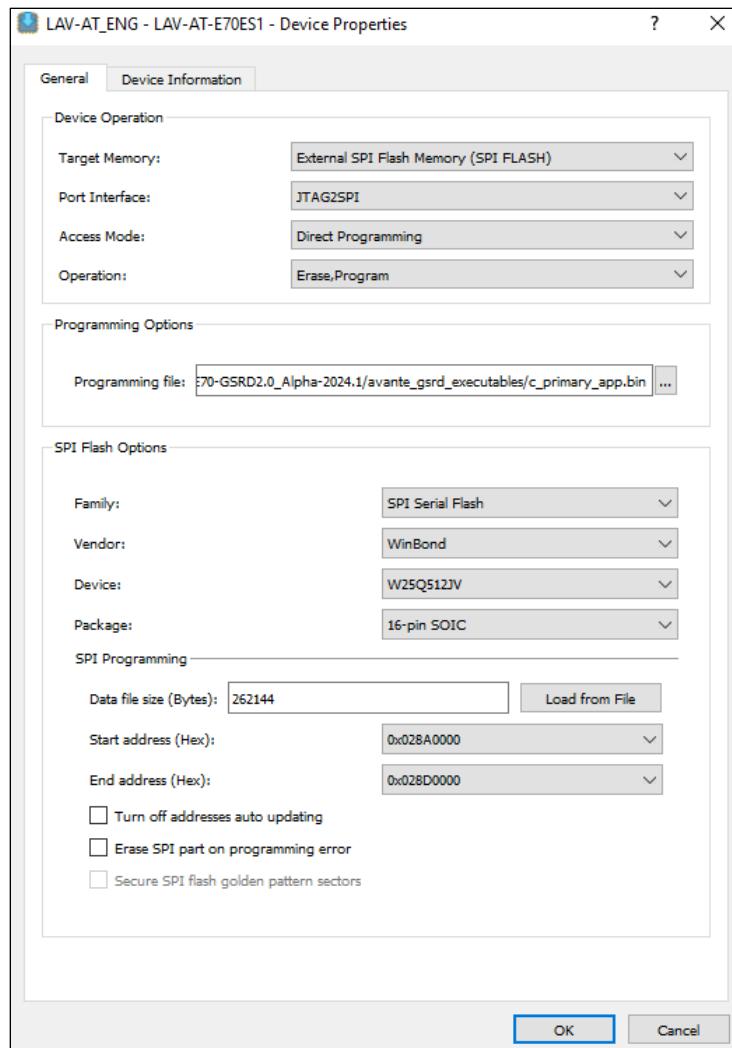

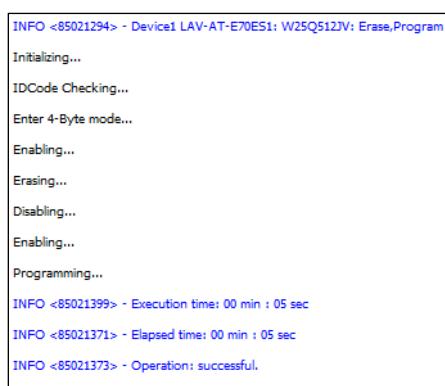

| Figure 7.20. Device Properties to Program the SPI Flash .....                                      | 42 |

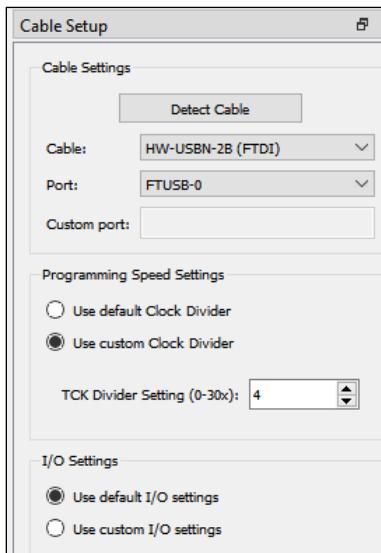

| Figure 7.21. Cable Settings for device programming.....                                            | 43 |

| Figure 7.22. Radiant Programmer Console Output after Programming the SPI Flash.....                | 43 |

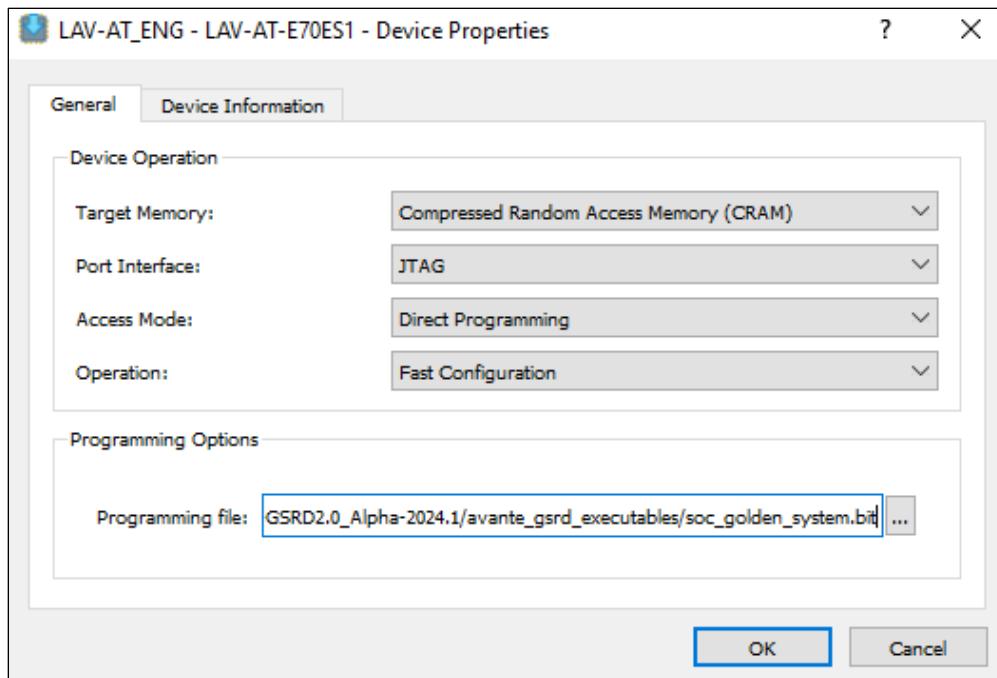

| Figure 7.23. Device Properties to Program the FPGA Bitstream in CRAM .....                         | 44 |

| Figure 7.24. Radiant Programmer Console Output after Bitstream is Programmed.....                  | 44 |

| Figure 7.25. SW1 Reset Button .....                                                                | 45 |

| Figure 7.26. Golden GSRD - Output on UART Terminal for Bootloader and FreeRTOS Start .....         | 46 |

| Figure 7.27. Golden GSRD - Output on UART Terminal for FreeRTOS Running.....                       | 47 |

| Figure 7.28. Primary GSRD Bootloader– Output on UART Terminal .....                                | 48 |

| Figure 7.29. Primary GSRD FreeRTOS– Output on UART Terminal.....                                   | 49 |

| Figure 7.30.Device Properties window to setup MCS programming file.....                            | 50 |

| Figure 7.31. UART Terminal Output after Power-Cycling Board with MCS and Binaries Programmed ..... | 51 |

| Figure 7.32. Switches to Golden GSRD upon SW2 PROGRAMN Button .....                                | 52 |

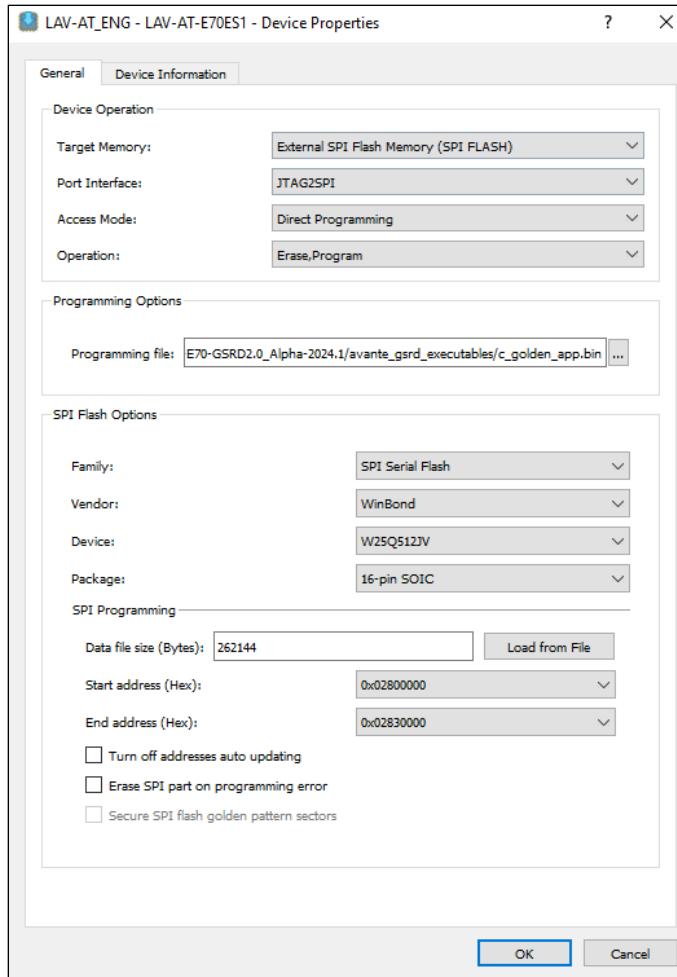

| Figure 7.33. Device Properties settings to program the Golden Application .....                    | 53 |

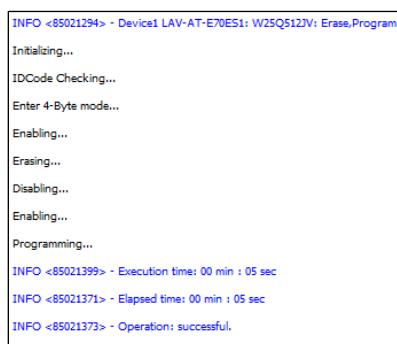

| Figure 7.34. Radiant Programmer Console Output After Programming .....                             | 53 |

| Figure 7.35. Primary GSRD – UART Output after SW1 Reset where CRC Matched .....                    | 54 |

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| Figure 7.36. UART Output Switching to Golden GSRD where CRC Mis-matched Intentionally..... | 55 |

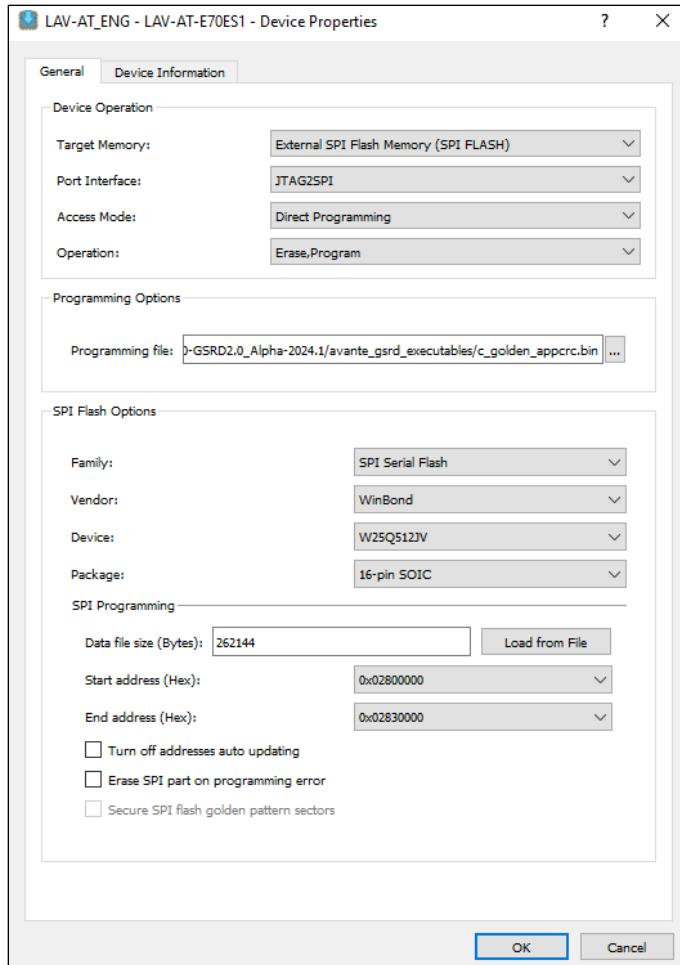

| Figure 7.37. Device Properties for Programming Golden App Binary with CRC.....             | 56 |

| Figure 7.38. Radiant Programmer Console Output After Successful Programming.....           | 56 |

| Figure 7.39. Device Properties Window for Primary App Binary without CRC.....              | 57 |

| Figure 7.40. Radiant Programmer Console Output After Successful Programming.....           | 57 |

| Figure 7.41. Primary GSRD without CRC Fails – UART Terminal .....                          | 58 |

| Figure 7.42. Automatically Jumps to Boot-up Golden GSRD .....                              | 59 |

| Figure 7.43. UART Terminal Output - After Pressing SW2 PROGRAMN Button .....               | 60 |

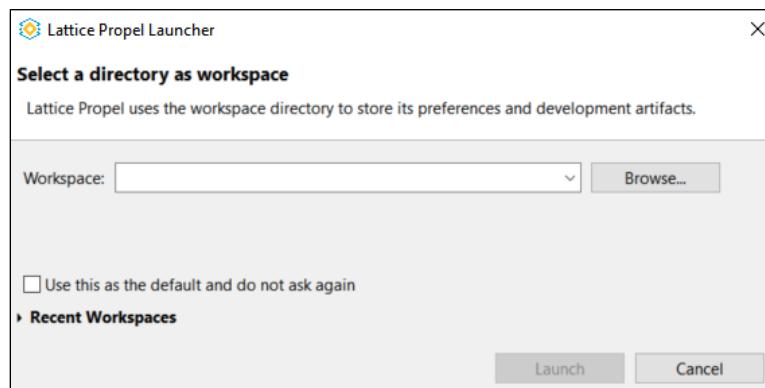

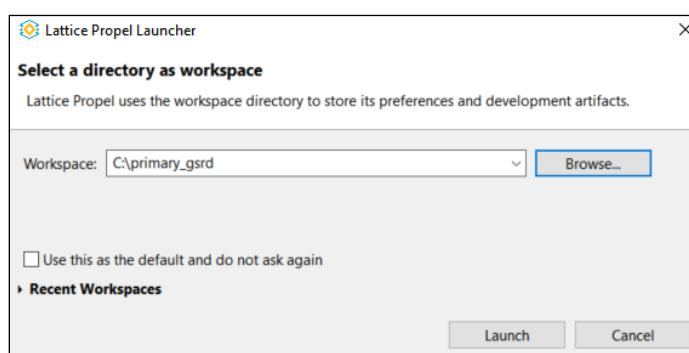

| Figure 8.1. Propel Builder Launcher .....                                                  | 61 |

| Figure 8.2. Provide Name for Workspace Directory .....                                     | 61 |

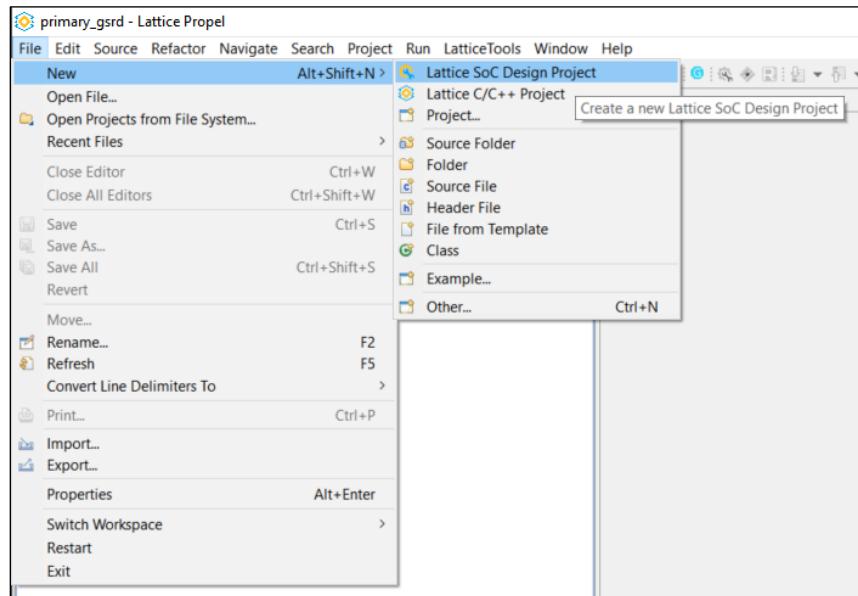

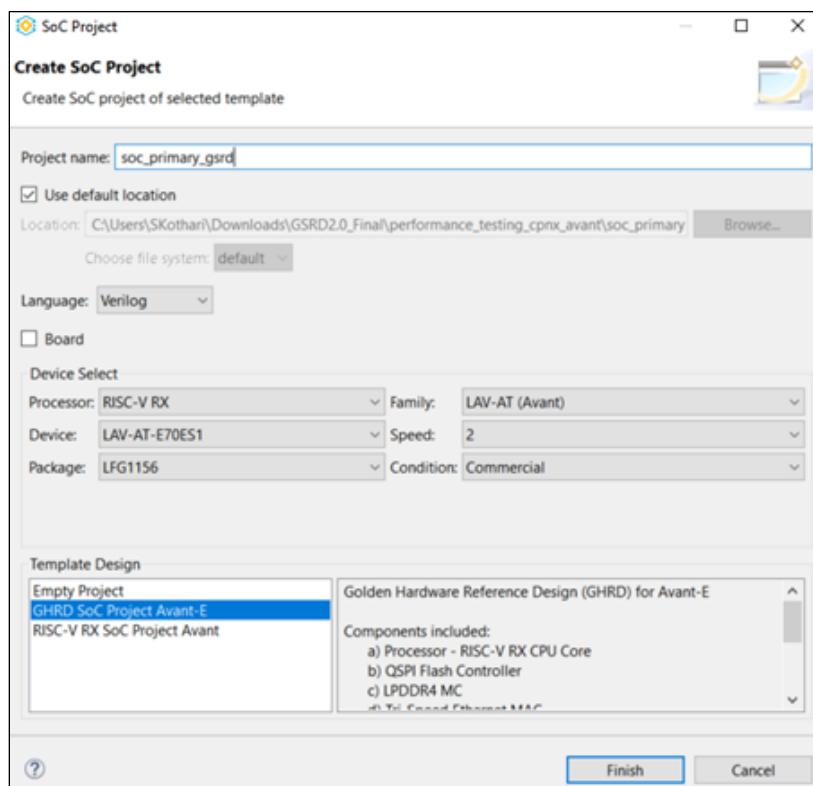

| Figure 8.3. Creating Lattice SoC Design Project .....                                      | 62 |

| Figure 8.4. Soc Project Window .....                                                       | 62 |

| Figure 8.5. Launched SoC in Propel Builder .....                                           | 63 |

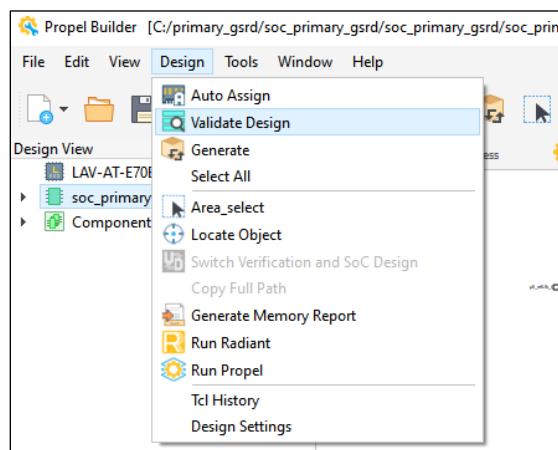

| Figure 8.6. Validate Design in Propel Builder .....                                        | 63 |

| Figure 8.7. TCL Console Output after Validating Design.....                                | 63 |

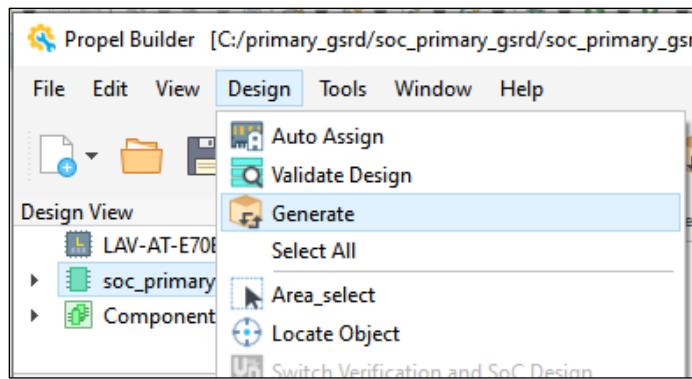

| Figure 8.8. Generate in Propel Builder .....                                               | 64 |

| Figure 8.9. TCL Console Output after Generating Design.....                                | 64 |

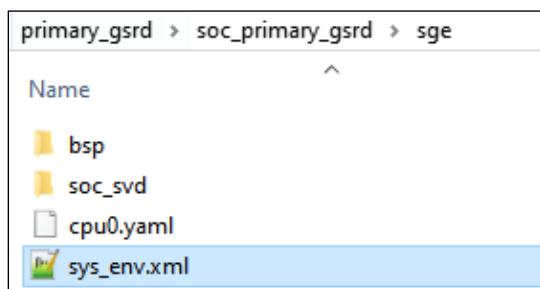

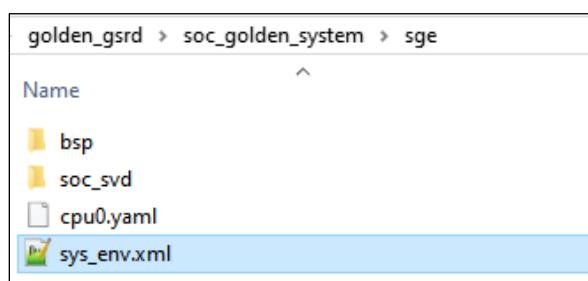

| Figure 8.10. sys_env.xml File Created .....                                                | 64 |

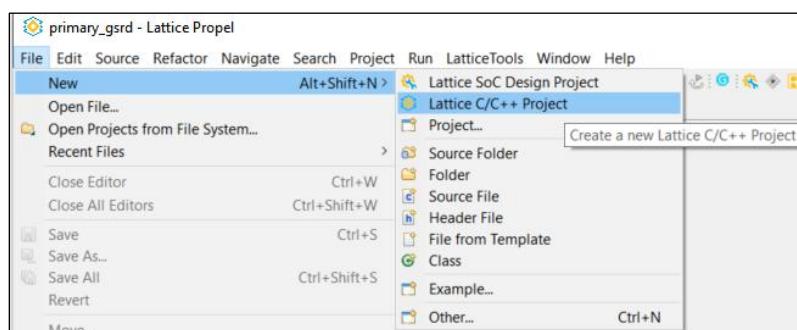

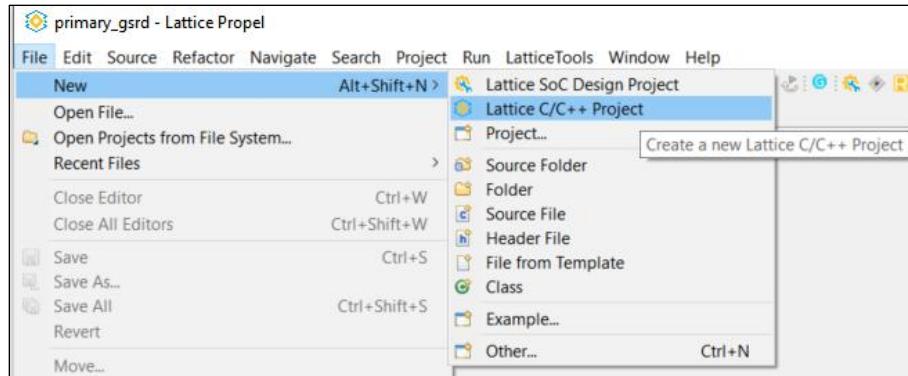

| Figure 8.11. Creating Lattice C/C++ Project for Bootloader .....                           | 64 |

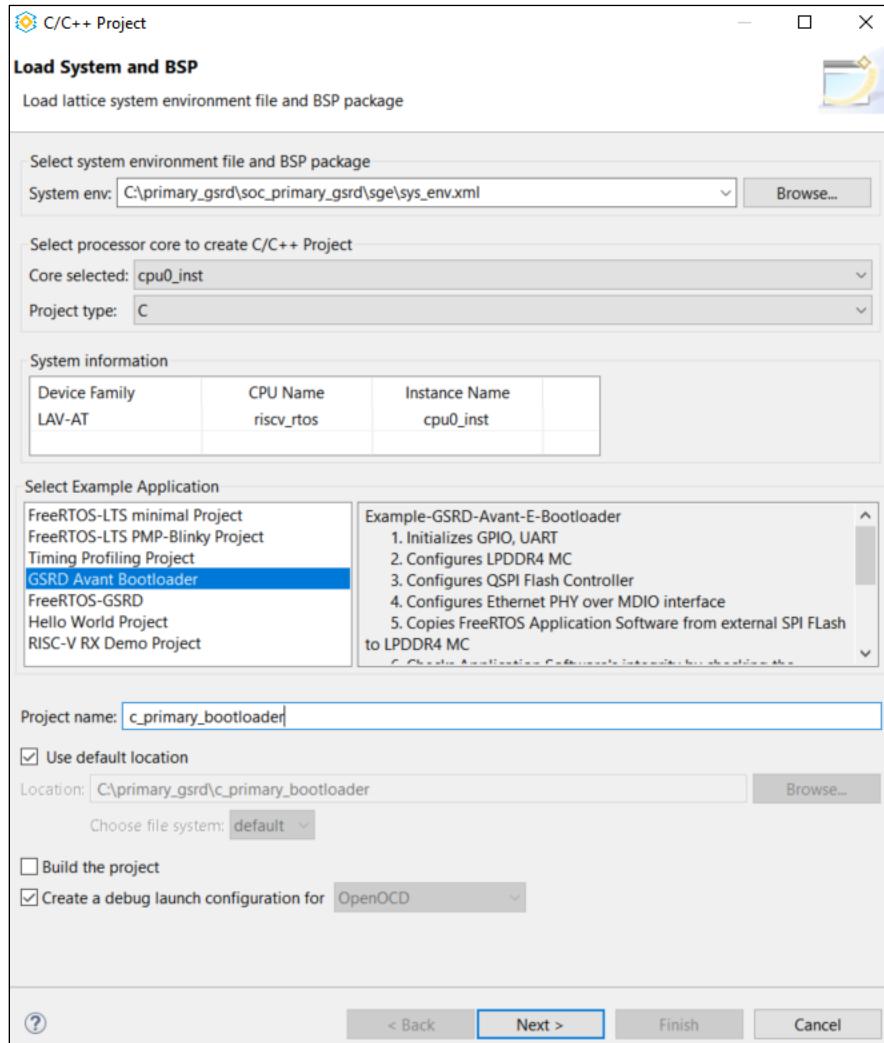

| Figure 8.12. Bootloader C/C++ Selection.....                                               | 65 |

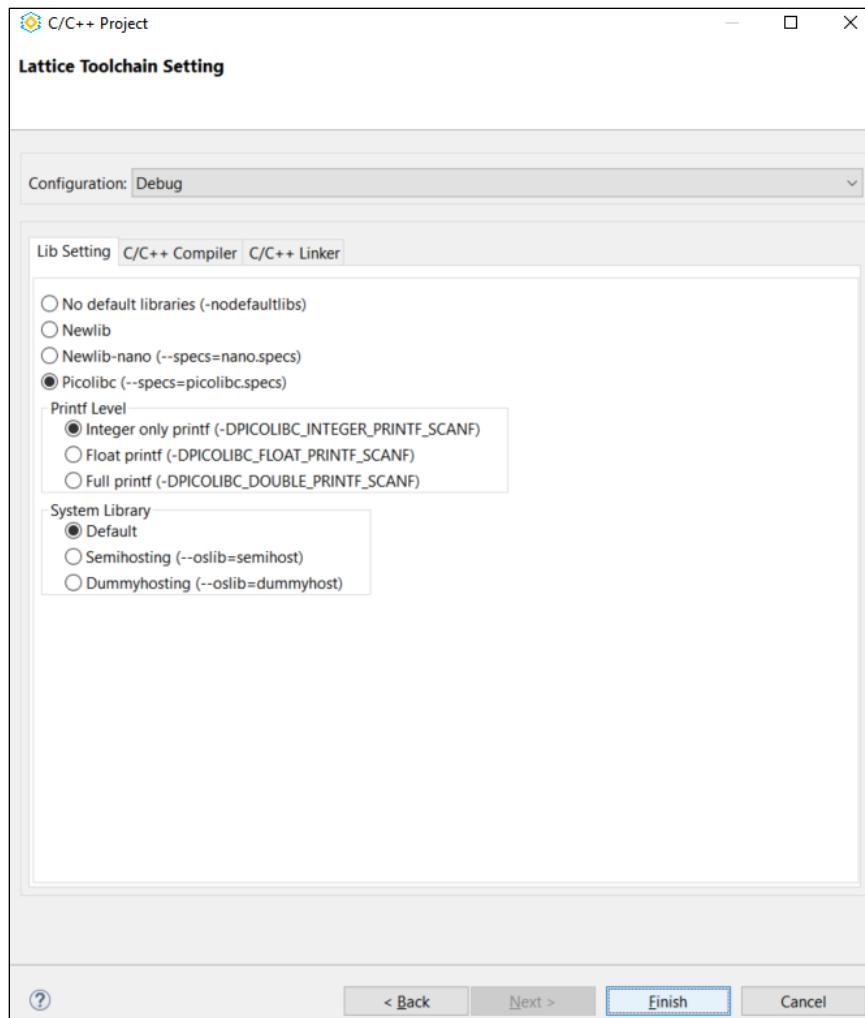

| Figure 8.13. C/C++ Lattice Toolchain Setting.....                                          | 66 |

| Figure 8.14. Bootloader C Project Created .....                                            | 66 |

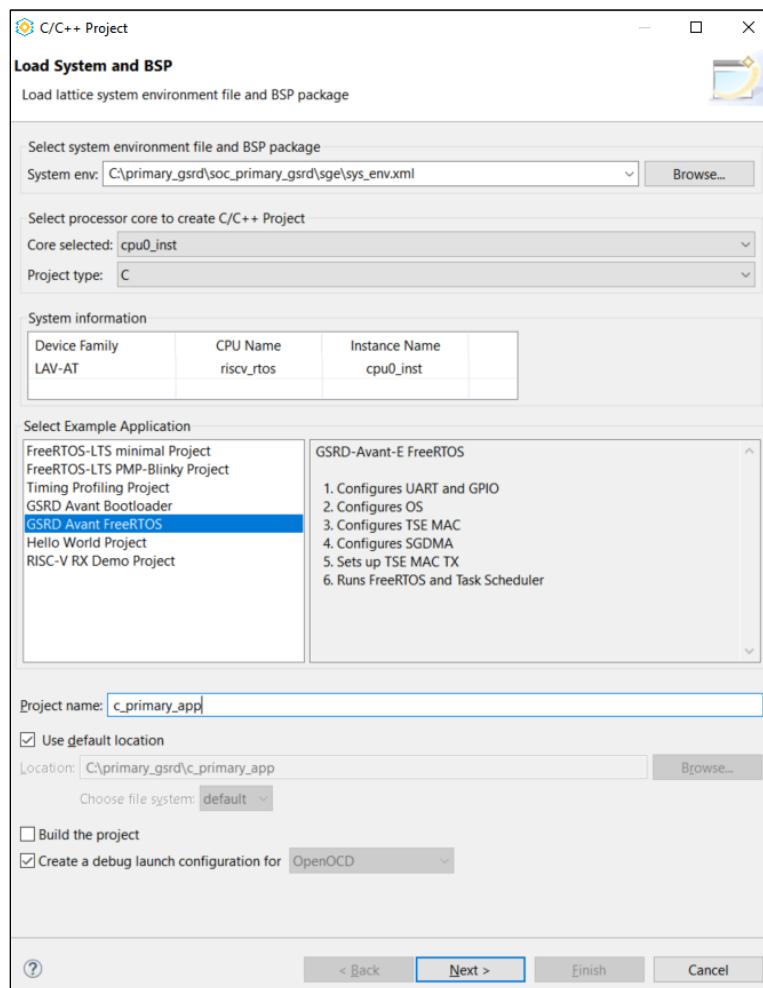

| Figure 8.15. Creating C/C++ Project for FreeRTOS .....                                     | 67 |

| Figure 8.16. FreeRTOS C/C++ Selection .....                                                | 67 |

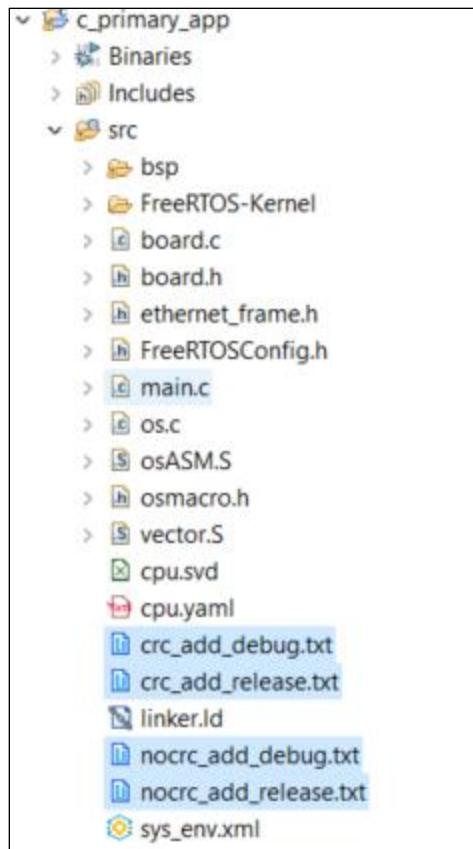

| Figure 8.17. FreeRTOS Project Created .....                                                | 68 |

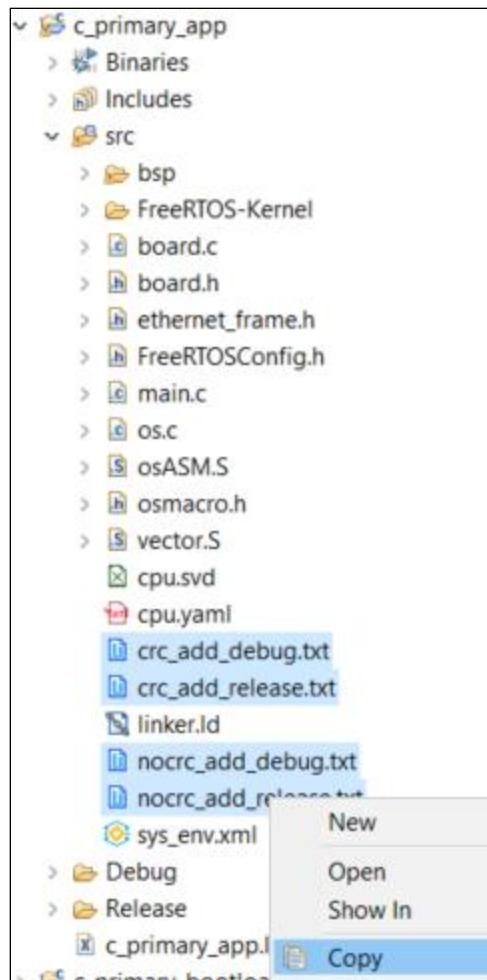

| Figure 8.18. Copy the CRC and NoCRC Add files.....                                         | 69 |

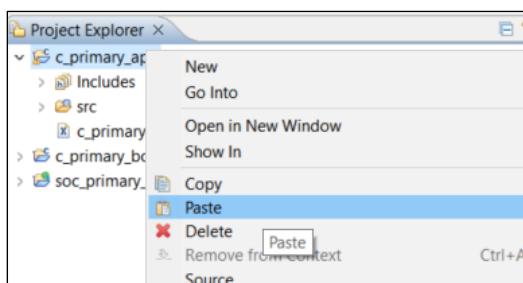

| Figure 8.19. Paste in FreeRTOS C project .....                                             | 69 |

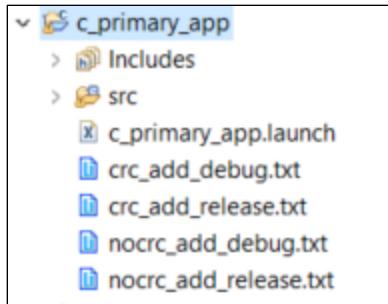

| Figure 8.20. Copied Text Files .....                                                       | 70 |

| Figure 8.21. Updated Primary Address.....                                                  | 70 |

| Figure 8.22. Enable fw_softreset() Function .....                                          | 70 |

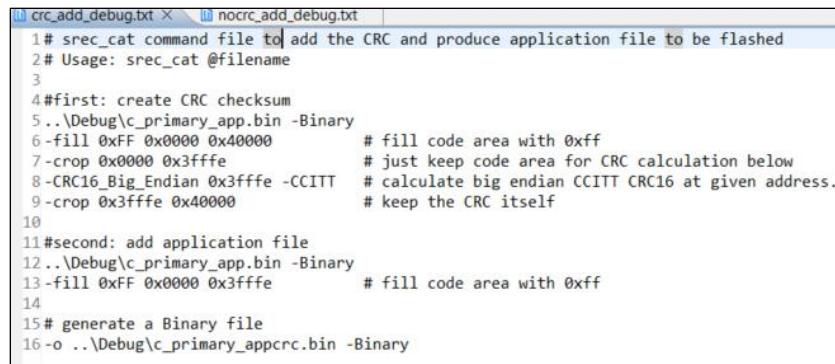

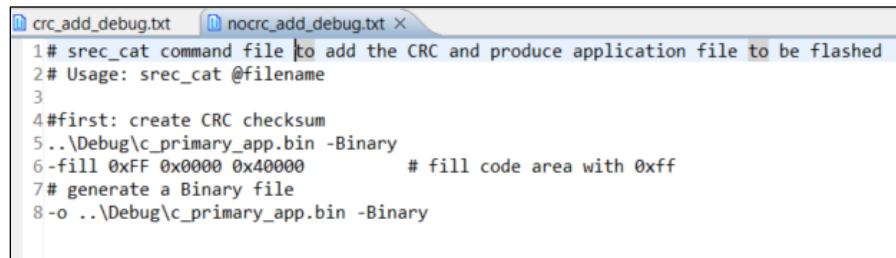

| Figure 8.23. Update crc_add_debug.txt .....                                                | 71 |

| Figure 8.24. Update noncrc_add.txt.....                                                    | 71 |

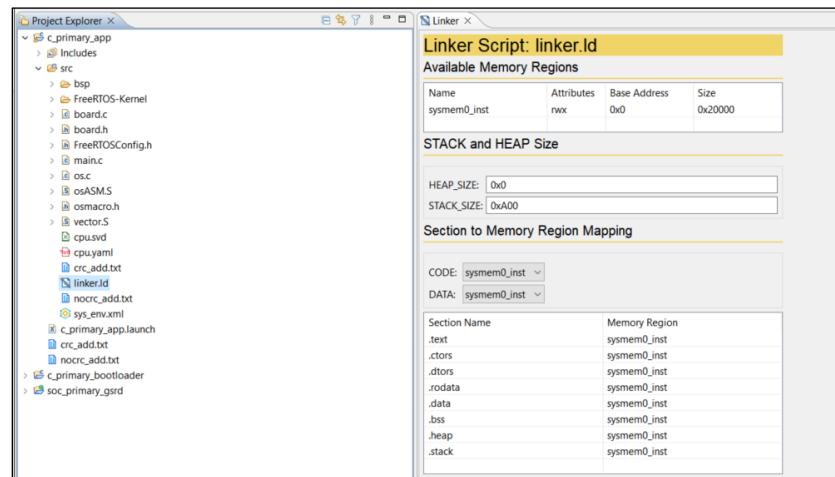

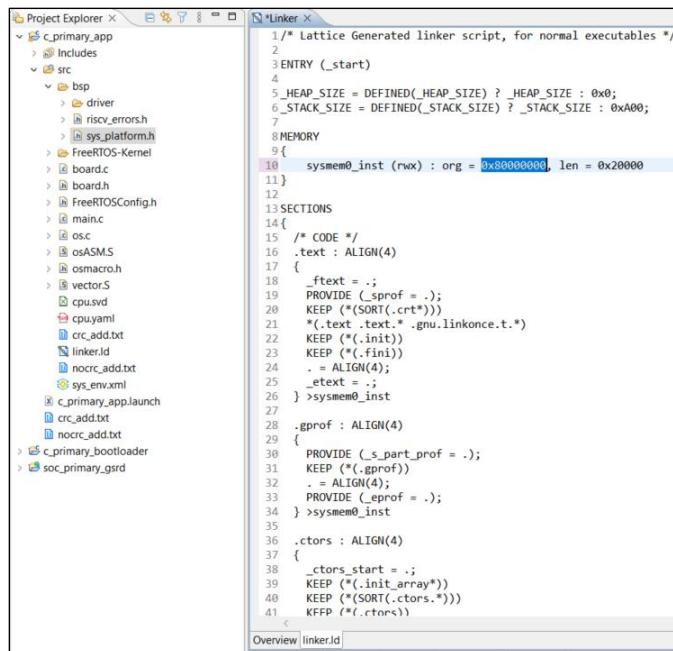

| Figure 8.25. Open Linker.Ld File .....                                                     | 71 |

| Figure 8.26. Update Linker.Id File .....                                                   | 72 |

| Figure 8.27. Workspace .....                                                               | 72 |

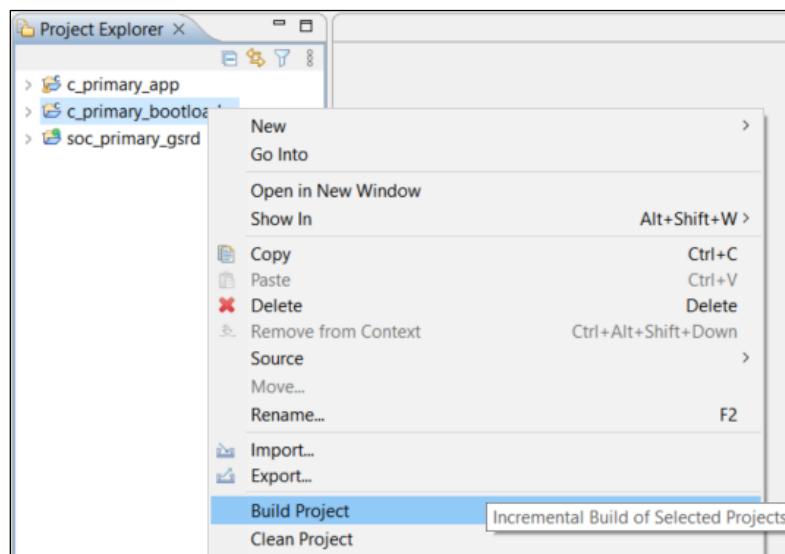

| Figure 8.28. Build Bootloader Project.....                                                 | 72 |

| Figure 8.29. Bootloader Build Project Console Output.....                                  | 73 |

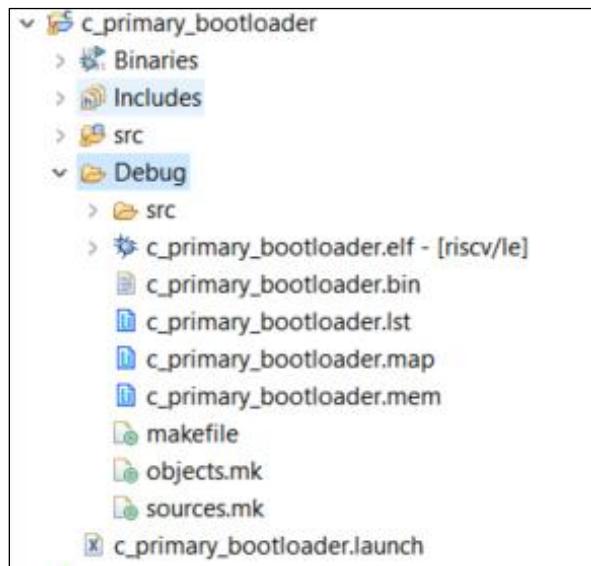

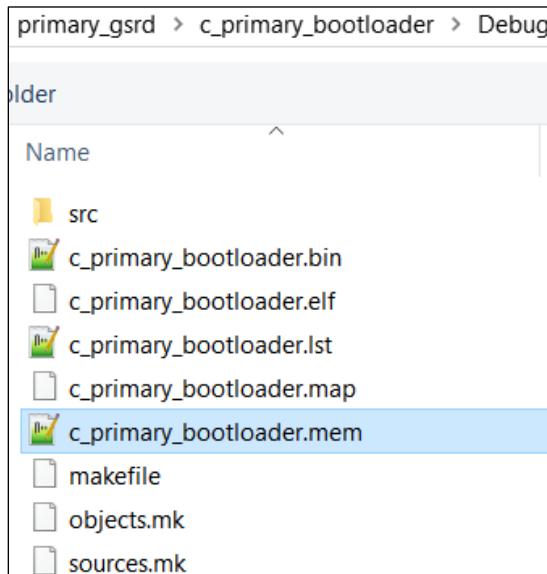

| Figure 8.30. Bootloader Binary Created .....                                               | 73 |

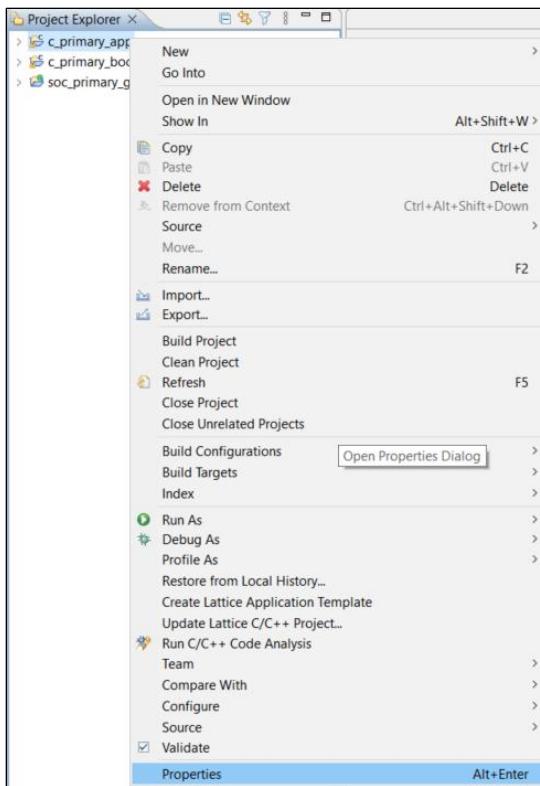

| Figure 8.31. Properties .....                                                              | 74 |

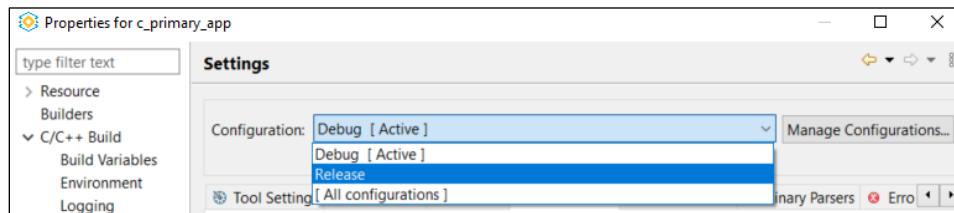

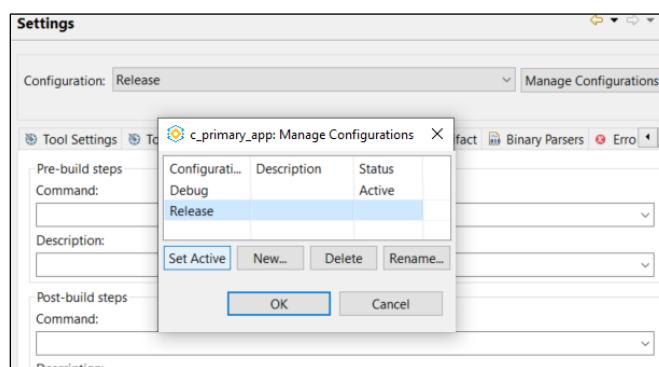

| Figure 8.32. Select Release as Configuration.....                                          | 74 |

| Figure 8.33. Set Release as Active Configuration .....                                     | 74 |

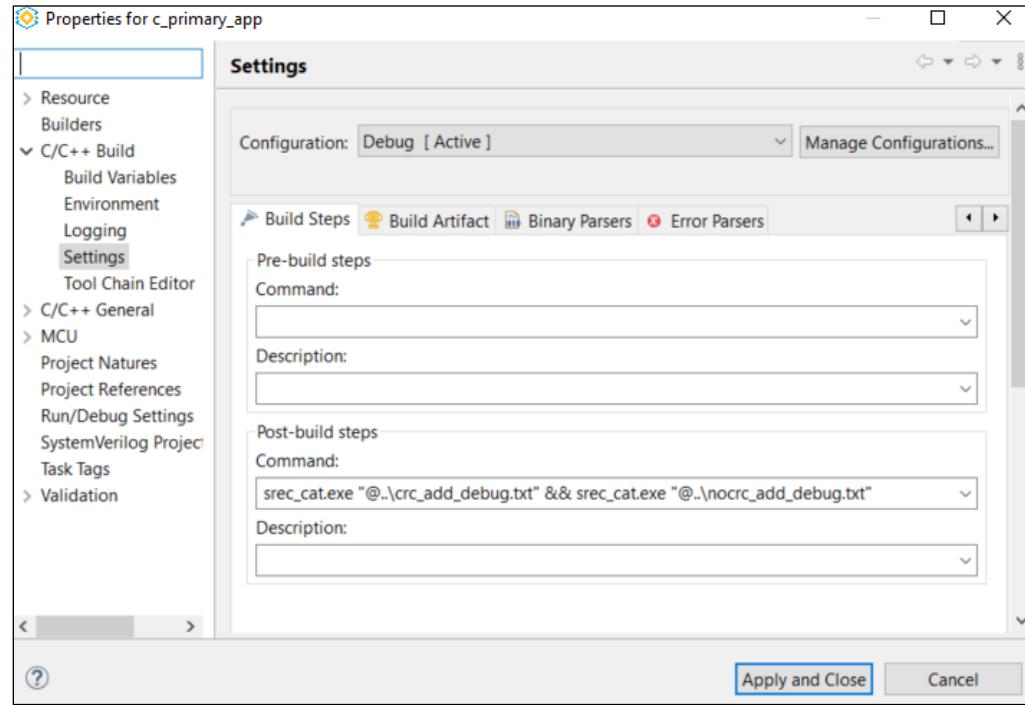

| Figure 8.34. Adding Post Build Step for FreeRTOS Application CRC Binary Append .....       | 75 |

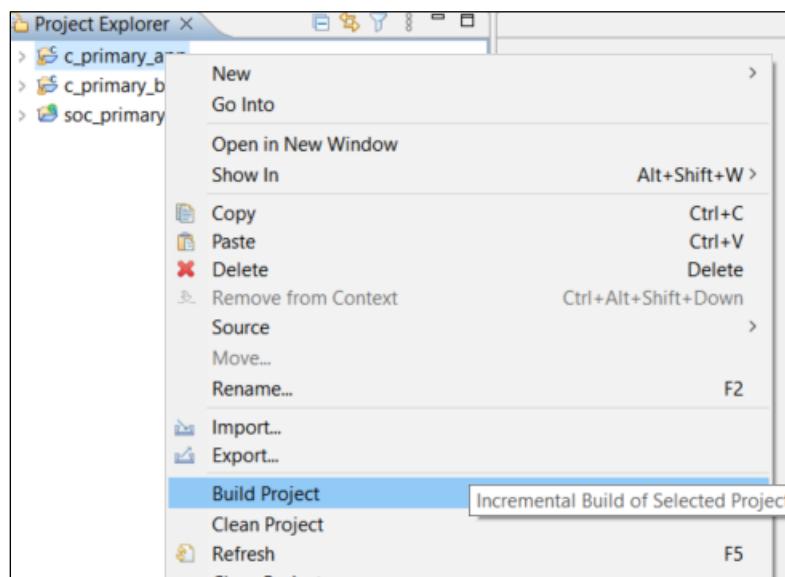

| Figure 8.35. Build c_primary_app C/C++ Project.....                                        | 75 |

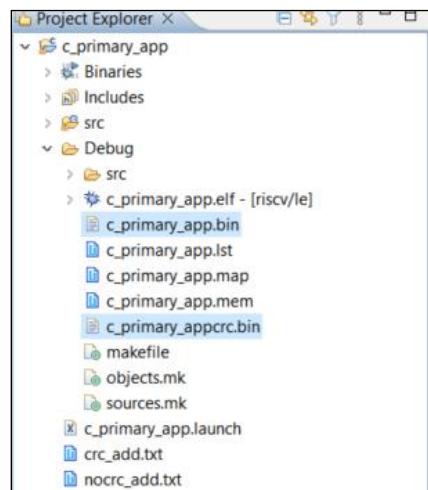

| Figure 8.36. FreeRTOS App Build Project Console Output .....                               | 76 |

| Figure 8.37. FreeRTOS App Binaries Created with CRC and without CRC .....                  | 76 |

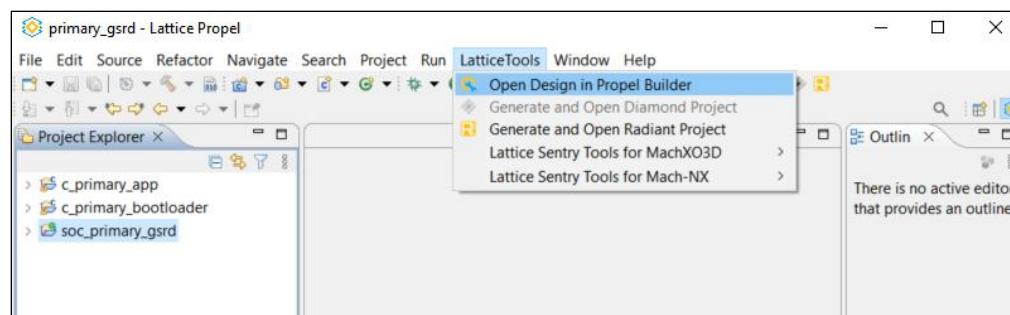

| Figure 8.38. Open Propel Builder .....                                                     | 76 |

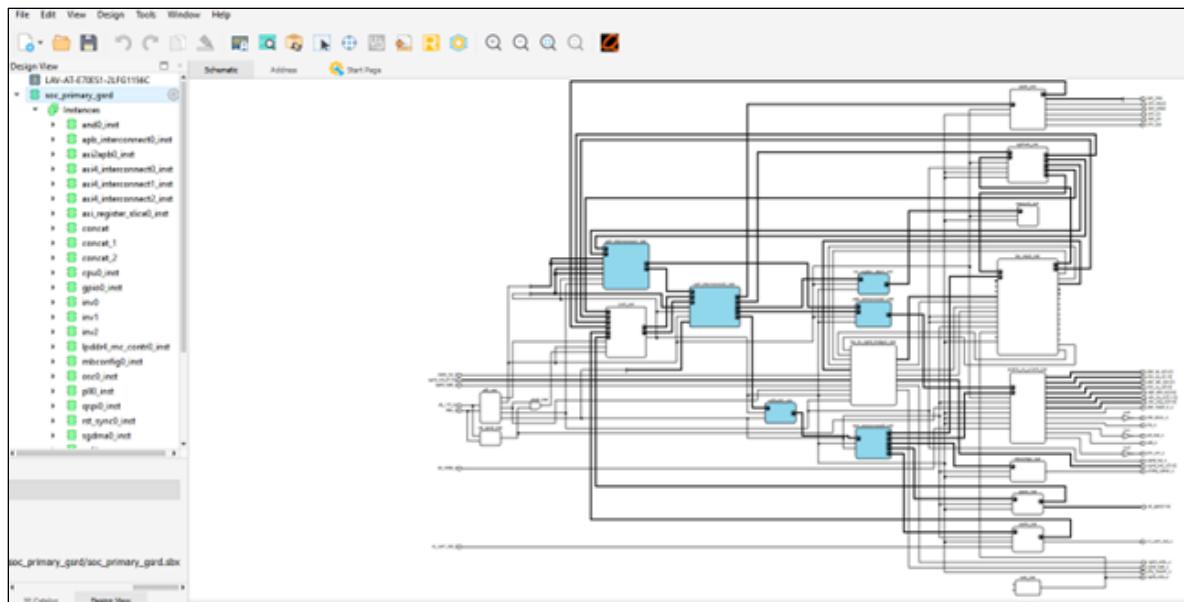

| Figure 8.39. Propel Builder SoC Project.....                                               | 77 |

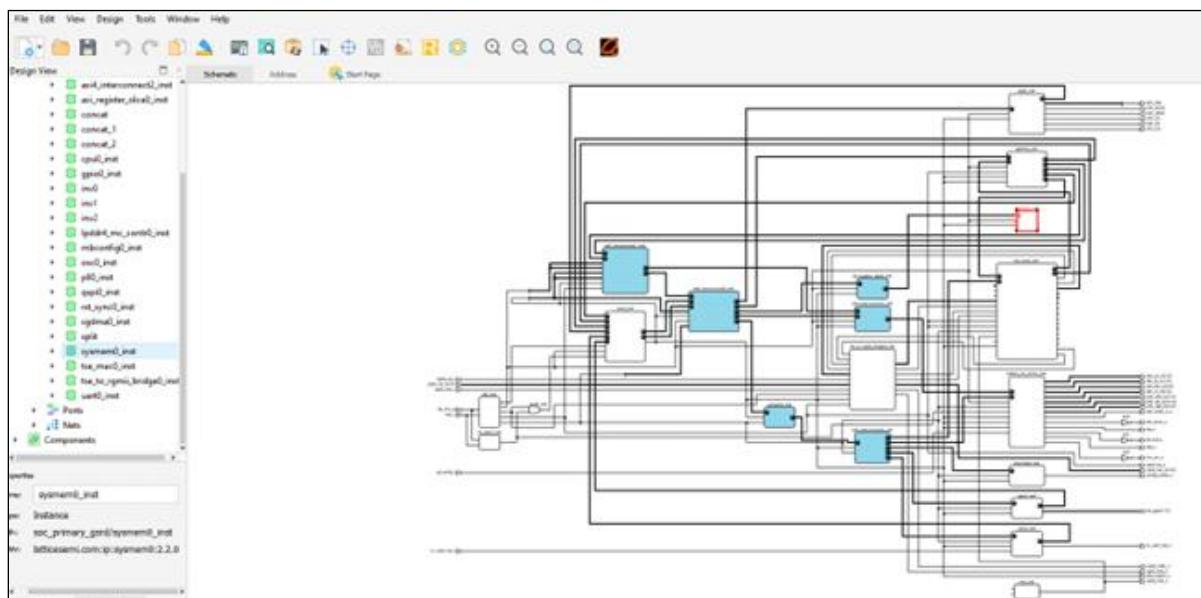

| Figure 8.40. System Memory Highlighted .....                                               | 77 |

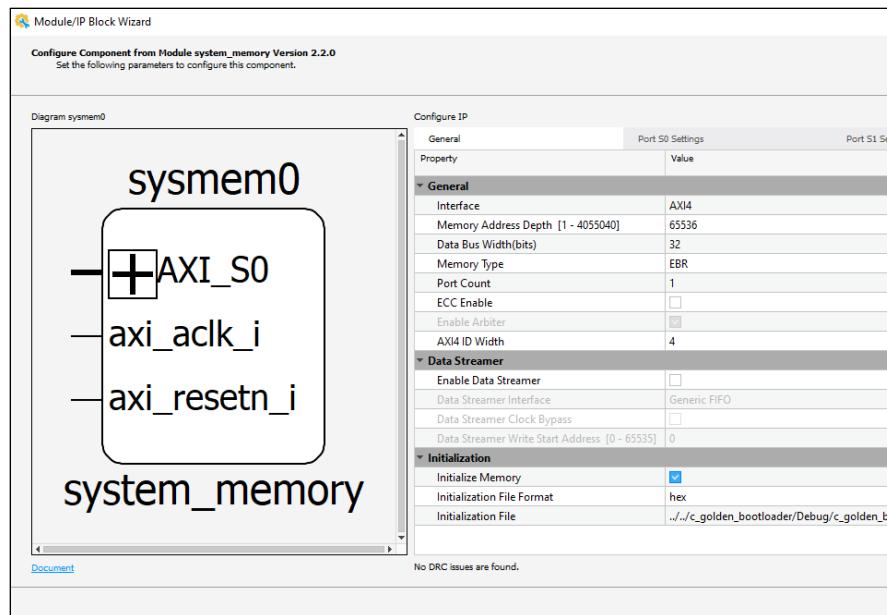

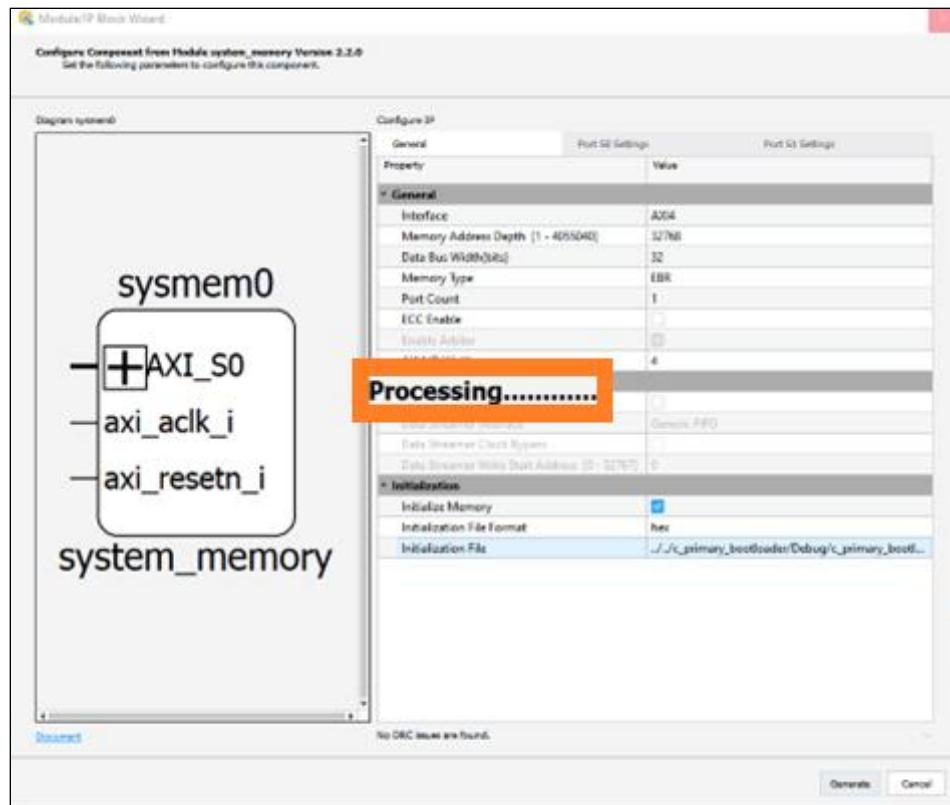

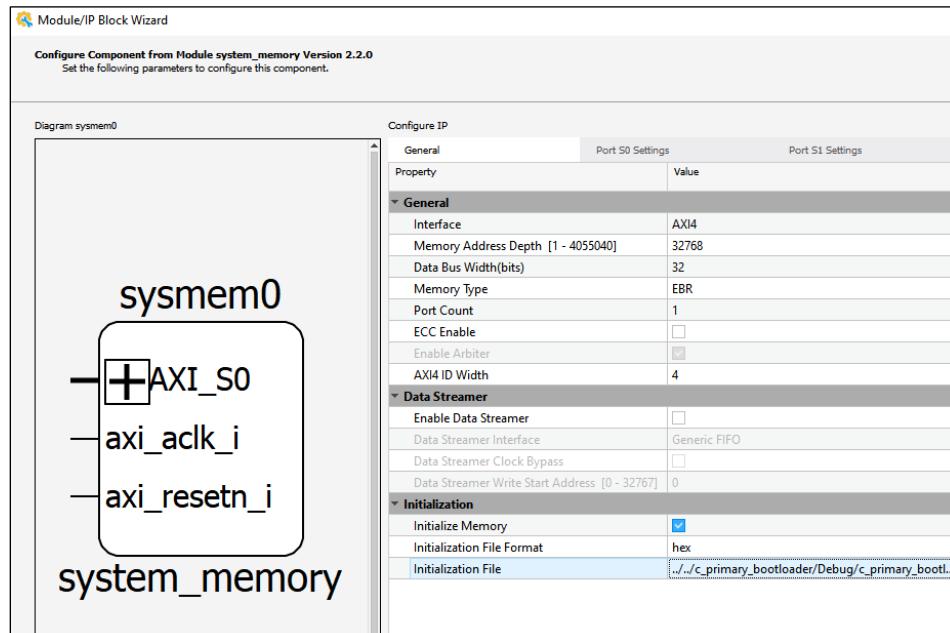

| Figure 8.41. System Memory IP Configuration .....                                          | 78 |

| Figure 8.42. Initialize System Memory with c_primary_bootloader.mem .....                  | 78 |

| Figure 8.43. Click Generate.....                                                           | 79 |

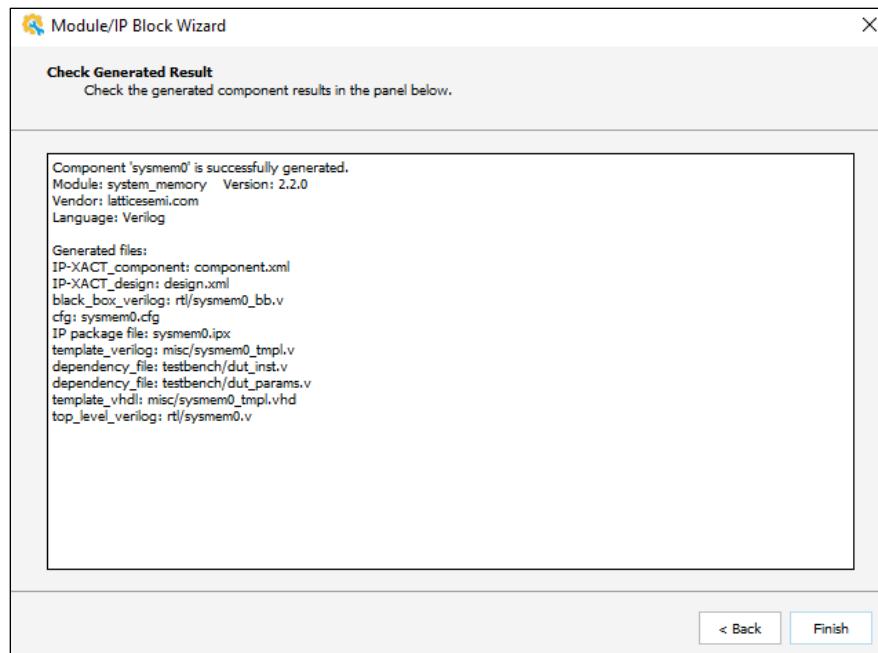

| Figure 8.44.Bootloader file updated in System Memory .....                                 | 79 |

| Figure 8.45. Click Finish .....                                                            | 80 |

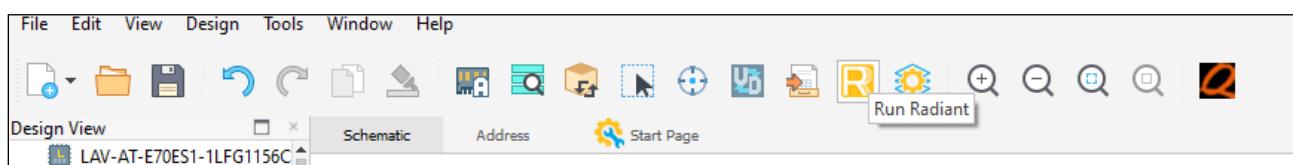

| Figure 8.46. Run Radiant Icon.....                                                         | 80 |

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

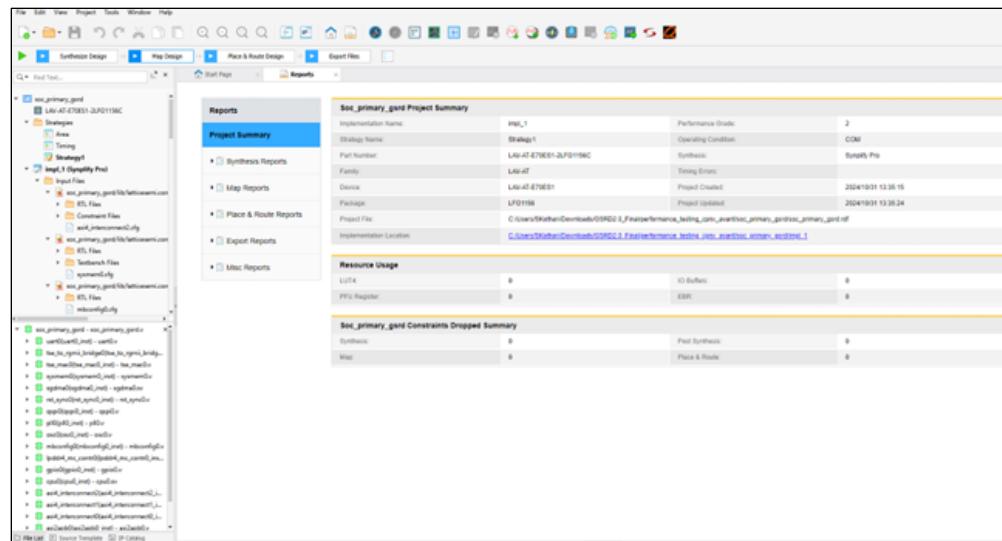

| Figure 8.47. Lattice Radian 2024.1.1 Window.....                                    | 81 |

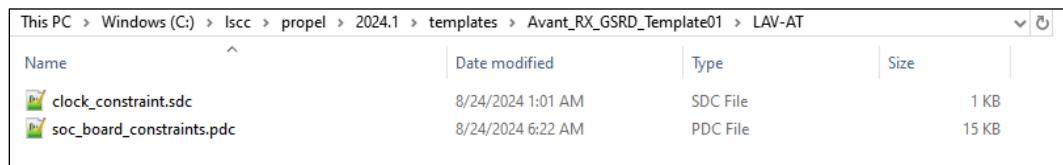

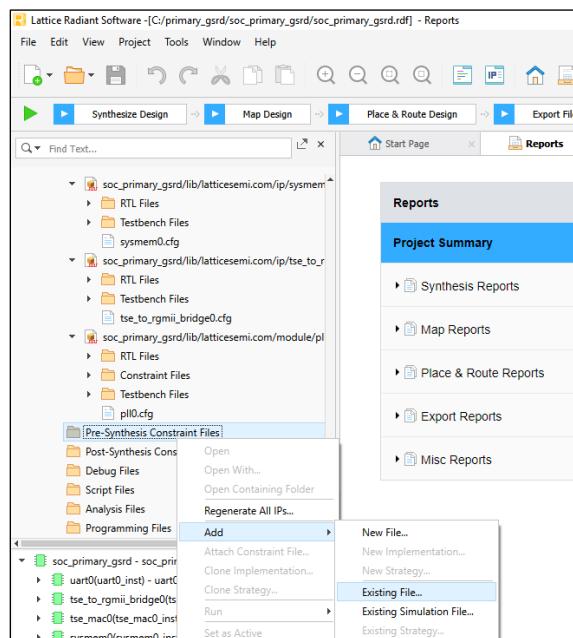

| Figure 8.48. Constraint Files Folder .....                                          | 81 |

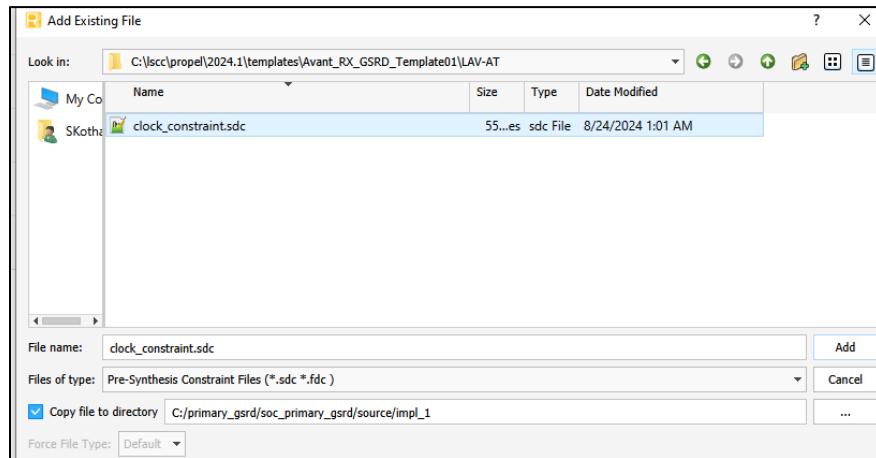

| Figure 8.49. Add Existing Pre-Synthesis Constraint .....                            | 81 |

| Figure 8.50. Select <code>clock_constraint.sdc</code> File .....                    | 82 |

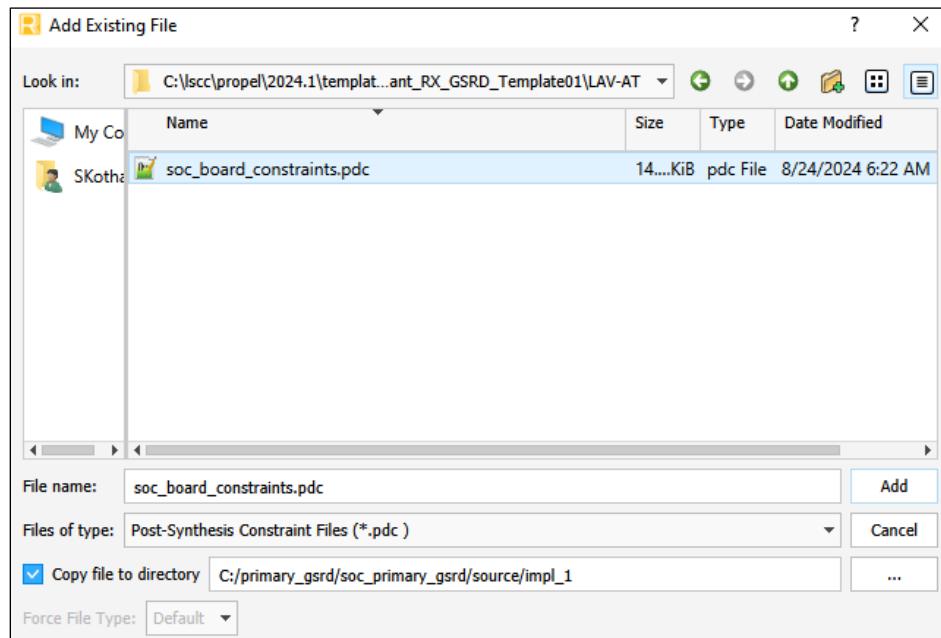

| Figure 8.51. Select <code>soc_board_constraint.pdc</code> File .....                | 82 |

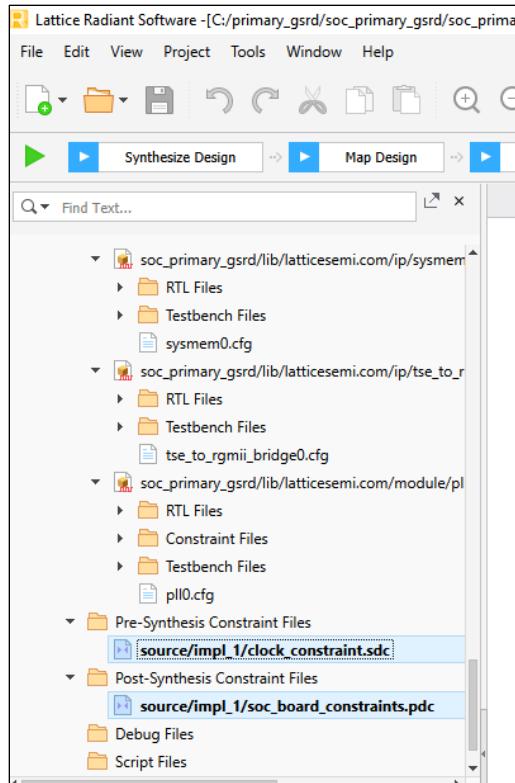

| Figure 8.52. Pre and Post-Synthesis Constraint Files Added .....                    | 83 |

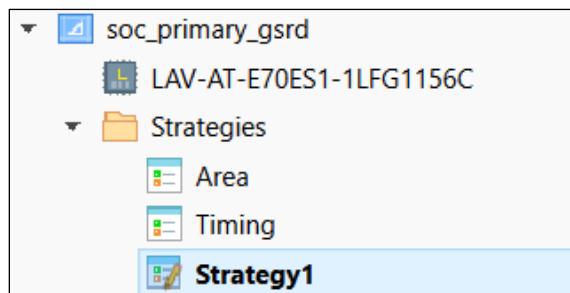

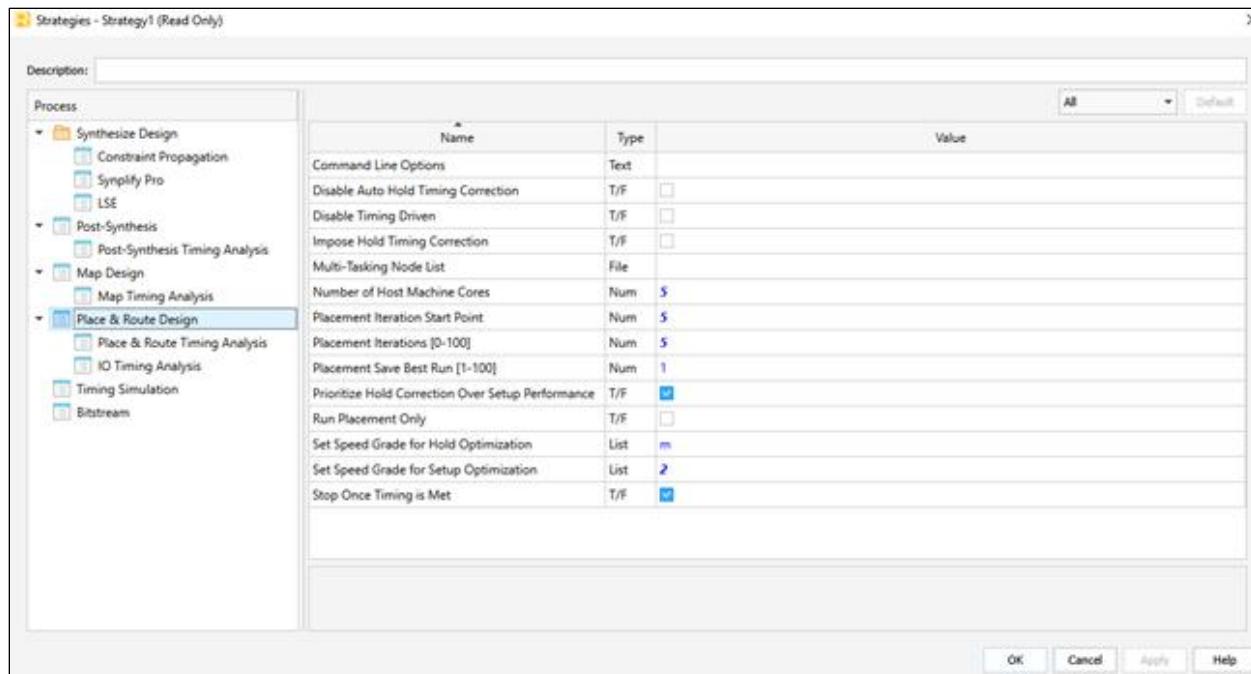

| Figure 8.53. Update the Strategy.....                                               | 83 |

| Figure 8.54. Strategy used for Avant GSRD Testing.....                              | 84 |

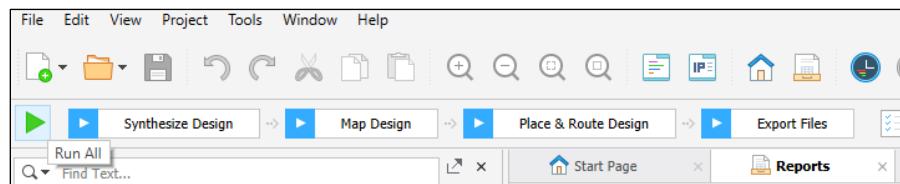

| Figure 8.55. Generating the Bit File .....                                          | 84 |

| Figure 8.56. Successful Radian Flow and Bitstream Generation .....                  | 84 |

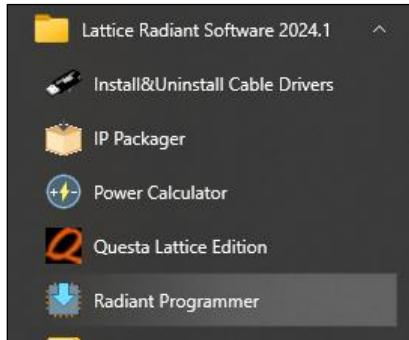

| Figure 8.57. Launch Radian Programmer from Windows Start.....                       | 85 |

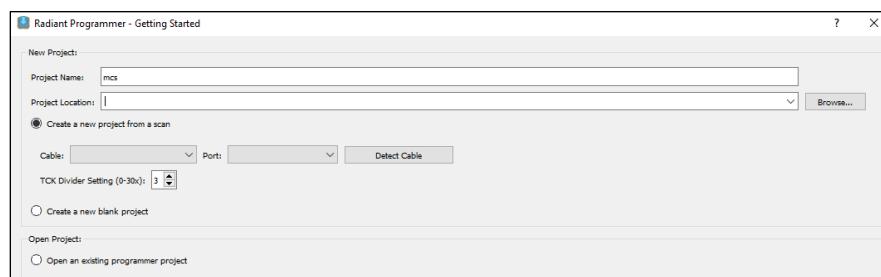

| Figure 8.58. Radian Programmer Getting Started Window .....                         | 85 |

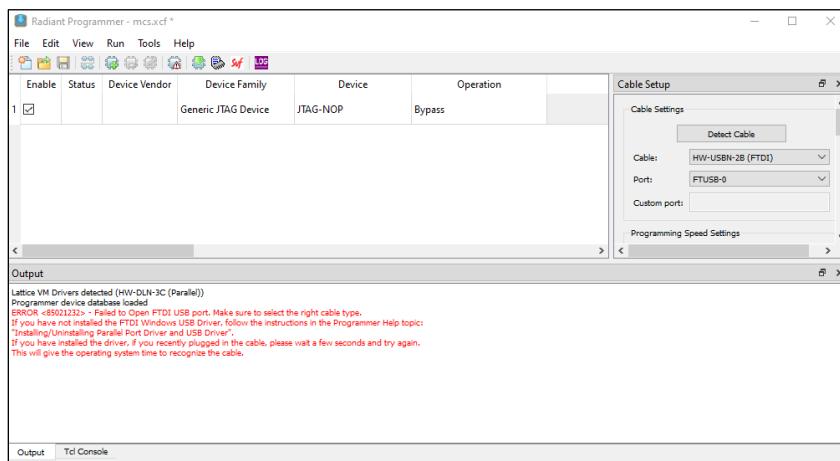

| Figure 8.59. Error if No HW Board is Connected .....                                | 85 |

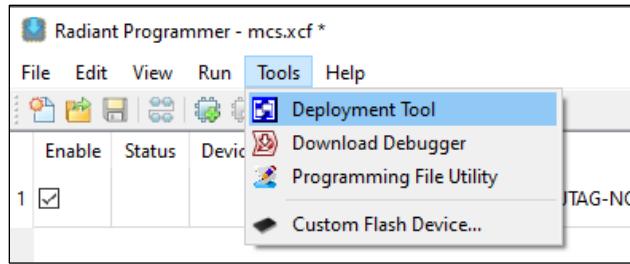

| Figure 8.60. Open Deployment Tool from Radian Programmer .....                      | 86 |

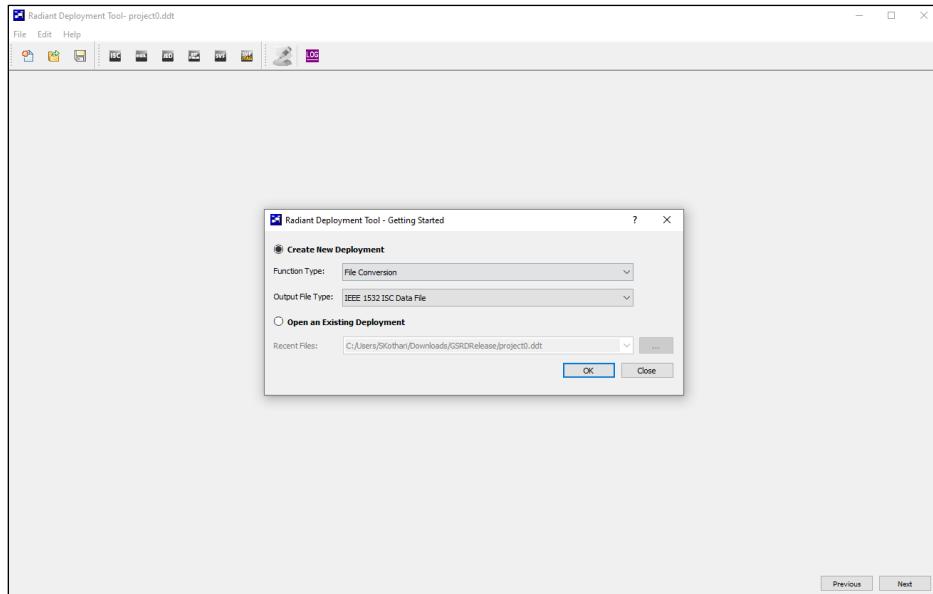

| Figure 8.61. Deployment Tool Start Window .....                                     | 86 |

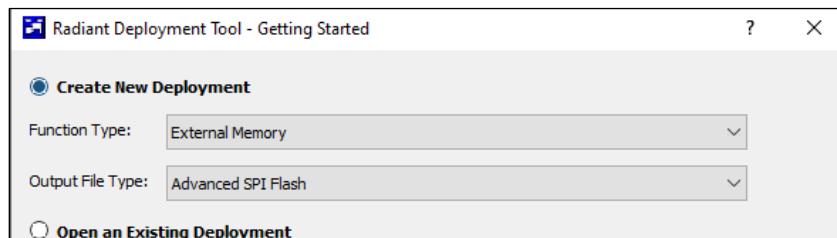

| Figure 8.62. Options for Creating New Deployment .....                              | 86 |

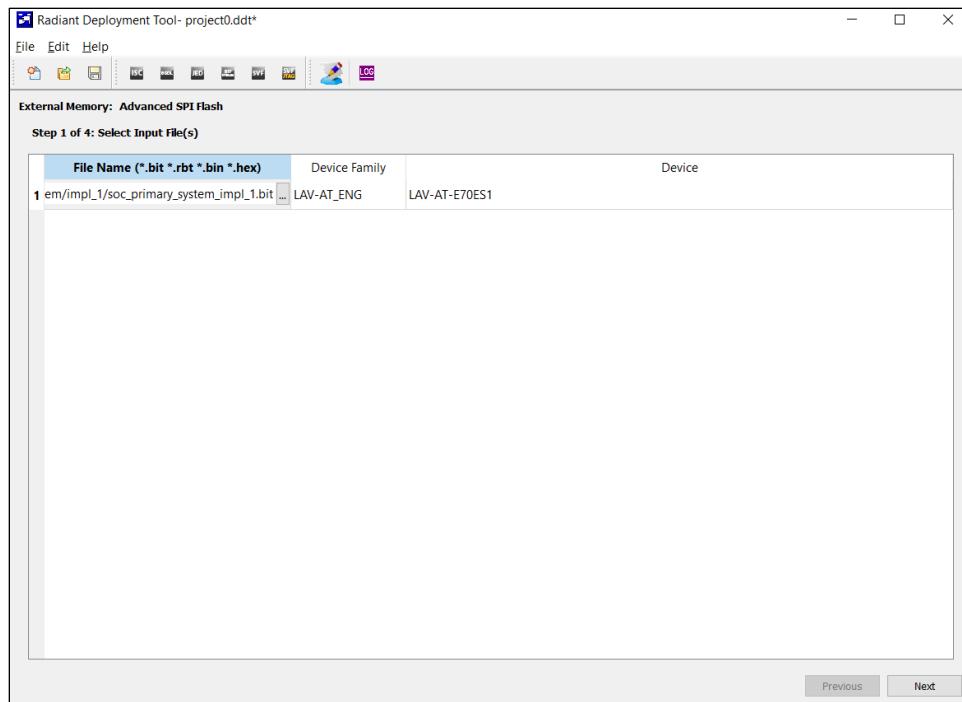

| Figure 8.63. External Memory Step 1 of 4: Select Input Files.....                   | 87 |

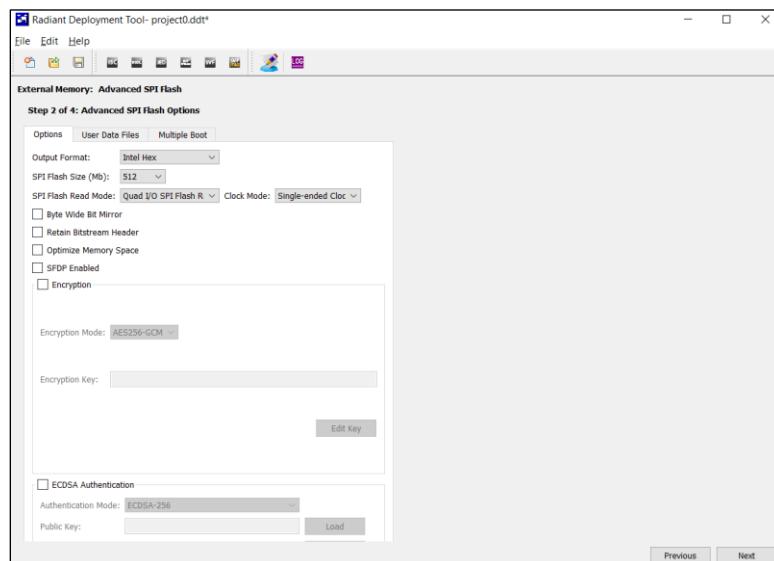

| Figure 8.64. External Memory Step 2 of 4: Select Options.....                       | 87 |

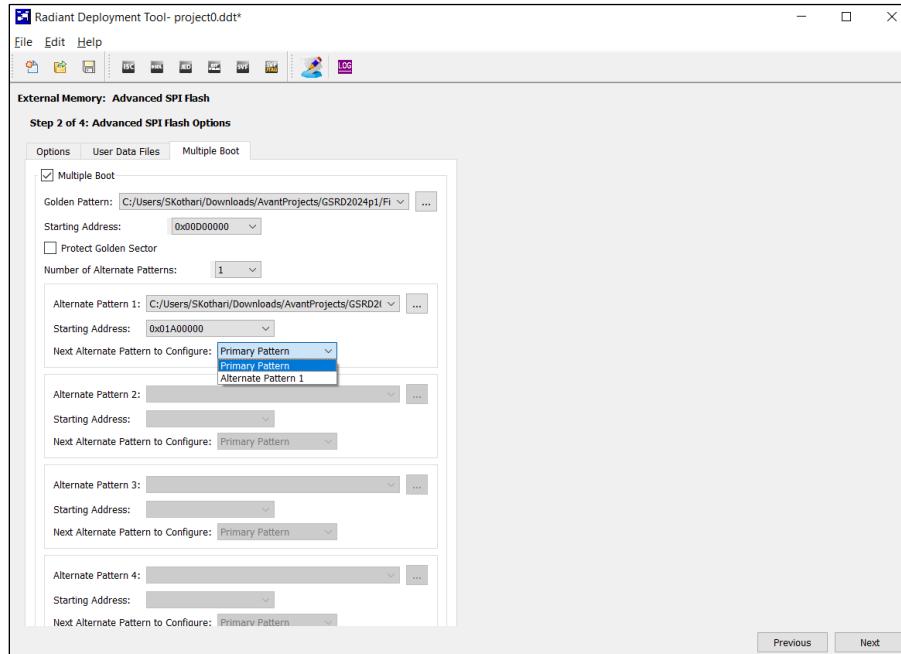

| Figure 8.65. External Memory Step 2 of 4: Multi-Boot.....                           | 88 |

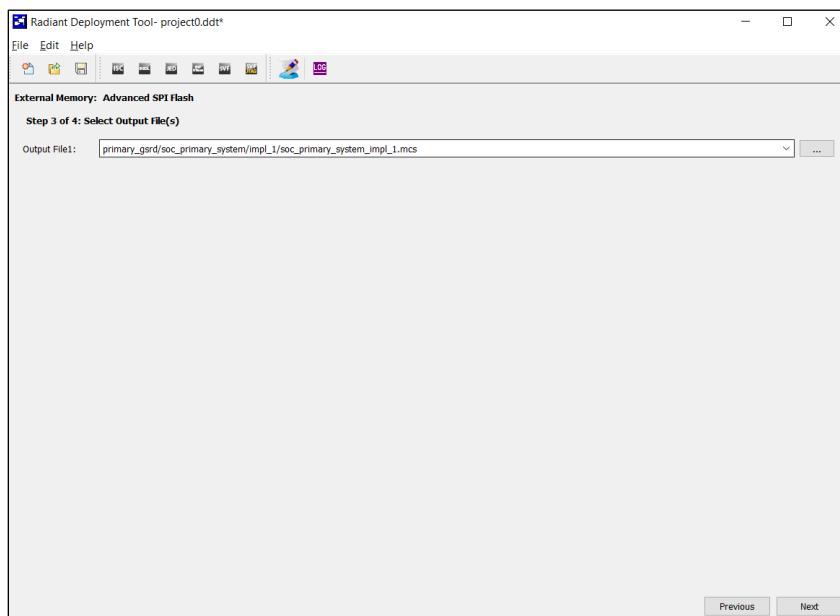

| Figure 8.66. External Memory Step 3 of 4: Select Output File(s) .....               | 88 |

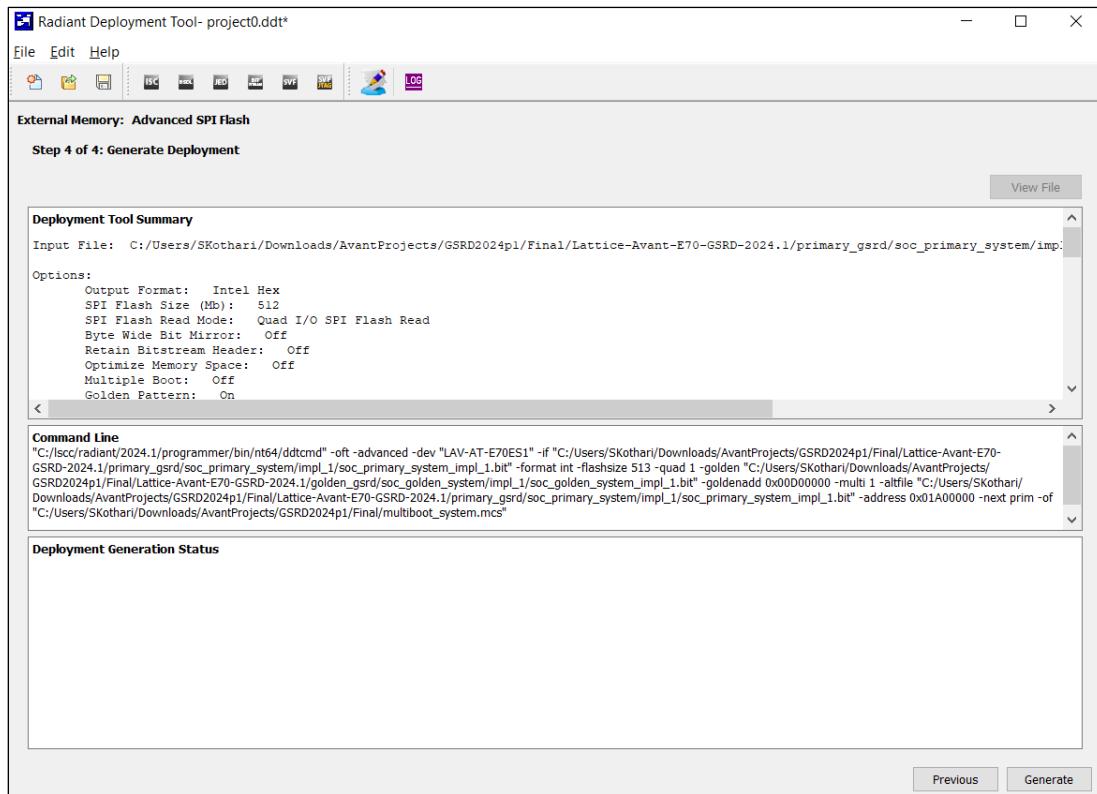

| Figure 8.67. External Memory Step 4 of 4: General Development.....                  | 89 |

| Figure 8.68. MCS File Generated Successfully.....                                   | 89 |

| Figure 9.1. IP Block .....                                                          | 90 |

| Figure 9.2. Customize IP .....                                                      | 90 |

| Figure 9.3. TCL Console Output After Desired Customization .....                    | 91 |

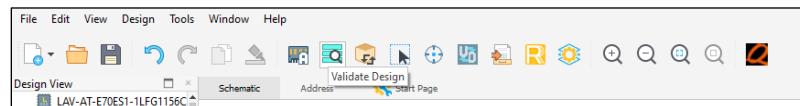

| Figure 9.4. Validate Design again is any IP is updated.....                         | 91 |

| Figure 9.5. Generate again is any IP is updated.....                                | 91 |

| Figure 9.6. New <code>sys_env.xml</code> File Generated.....                        | 91 |

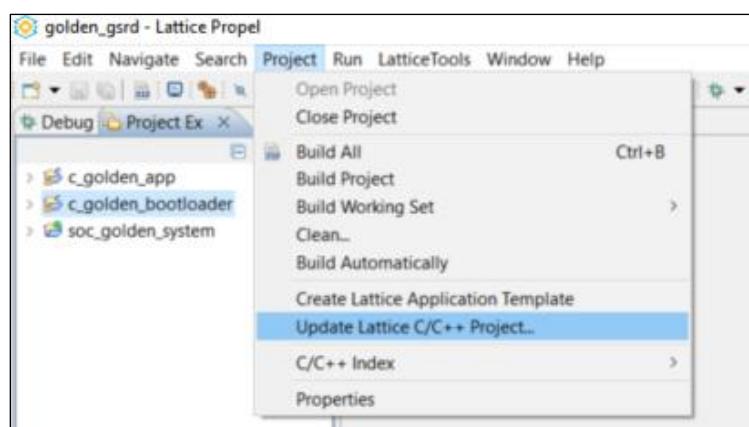

| Figure 9.7. Update Lattice C/C++ Project .....                                      | 91 |

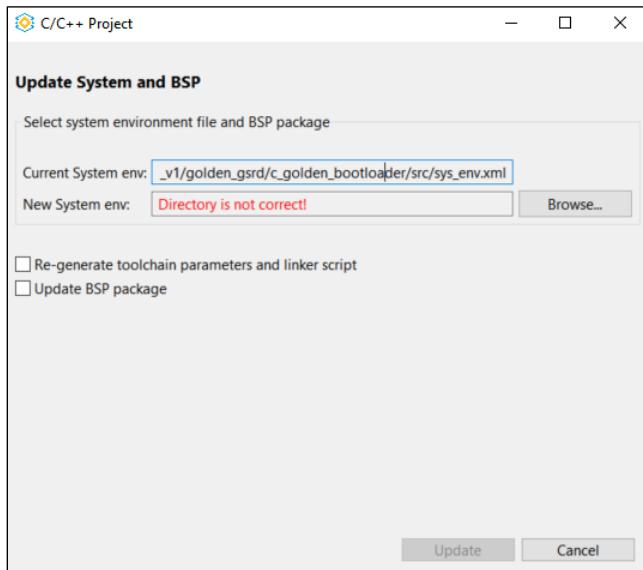

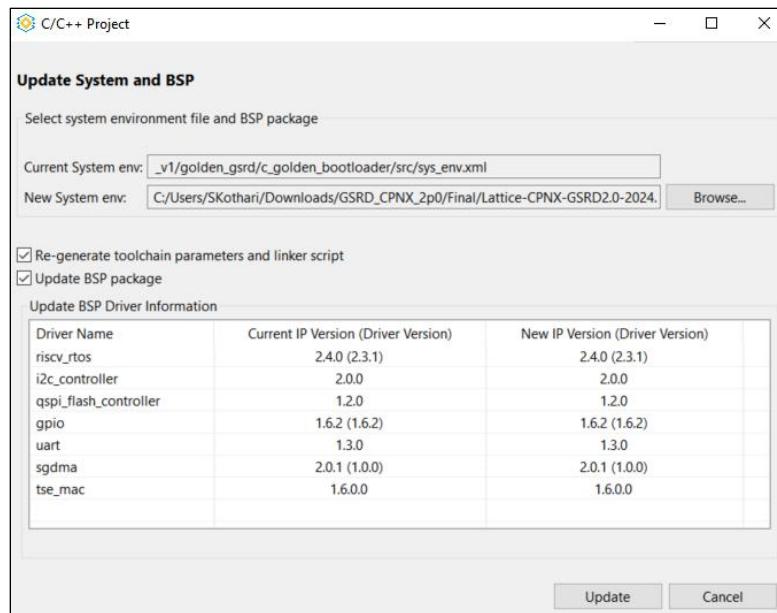

| Figure 9.8. Update System Dialog Window .....                                       | 92 |

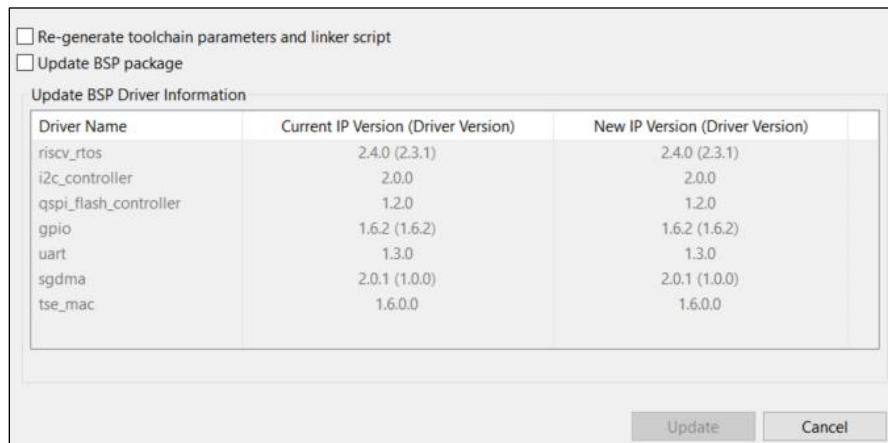

| Figure 9.9. New IP version Details .....                                            | 92 |

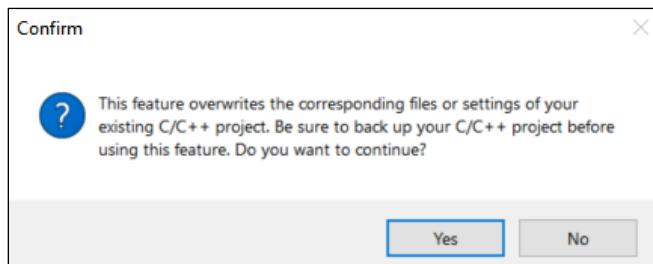

| Figure 9.10. Generate BSP and Toolchain Parameters .....                            | 93 |

| Figure 9.11. Confirm the Changes .....                                              | 93 |

| Figure 9.12. Confirm the Configuration Changes in <code>sys_platform.h</code> ..... | 93 |

## Tables

|                                                     |    |

|-----------------------------------------------------|----|

| Table 1.1. Summary of the System .....              | 10 |

| Table 2.1. IP Versions.....                         | 12 |

| Table 2.2. Reset Scheme.....                        | 14 |

| Table 2.3. System Level Interfaces .....            | 22 |

| Table 2.4. Address Map of GHRD .....                | 22 |

| Table 3.1. Top-level I/O .....                      | 24 |

| Table 6.1. GSRD Total Resource Utilization .....    | 31 |

| Table 7.1. Executable Files for Winbond Flash ..... | 36 |

## Abbreviations in This Document

A list of abbreviations used in this document.

| Abbreviation      | Definition                                   |

|-------------------|----------------------------------------------|

| AHBL              | Advanced High-performance Bus-Lite           |

| APB               | Advanced Peripheral Bus                      |

| API               | Application Programming Interface            |

| AXI               | Advanced eXtensible Interface                |

| AXI4-Lite         | Advanced eXtensible Interface-Lite           |

| CPU               | Central Processing Unit                      |

| DDR               | Double Data Rate                             |

| FIFO              | First-In-First-Out                           |

| FMC               | FPGA Mezzanine Card                          |

| GPIO              | General Purpose Input/Output                 |

| ISR               | Interrupt Service Routines                   |

| LMMI              | Lattice Memory Mapped Interface              |

| LPDDR4            | Low Power Double Data Rate Generation 4      |

| MPMC              | Multi-Port Memory Controller                 |

| QSPI              | Quad Serial Peripheral Interface             |

| RISC-V            | Reduced Instruction Set Computer-V           |

| RTL               | Register Transfer Level                      |

| SFP               | Small Form-Factor Pluggable                  |

| SGDMA             | Scatter-Gather Direct Memory Access          |

| SGMII PCS and GbE | Serial Gigabit Media Independent Interface   |

| SoC               | System on Chip                               |

| TSE MAC           | Tri - Speed Ethernet Media Access Controller |

| UART              | Universal Asynchronous Receiver-Transmitter  |

# 1. Introduction

## 1.1. Overview of the System

The Lattice FPGA-based GSRD SoC design presented herein is aimed at providing a versatile and efficient platform for embedded applications requiring high-performance computing, memory access, data transfer capabilities, and network communication. By integrating various components onto a single FPGA chip, this design offers flexibility, scalability, and cost-effectiveness for a wide range of applications.

The Lattice Golden Hardware Reference Design (GHRD) is a System-on-Chip (SoC) that can be used as a baseline design to create FPGA applications as per the user requirements. It is a RISC-V based design that interacts with various Lattice Soft-IPs and peripherals such as GPIO, UART, I2C, Timer, Tri-Speed Ethernet MAC (TSE MAC), QSPI Flash Controller, Scatter-Gather DMA (SGDMA) and LPDDR4 Memory Controller. All these building blocks are connected via industry standard protocols such as AXI4-Full, AXI-Stream for data transfers and AXI4-Lite, APB for control.

The Lattice Golden Software Reference Design (GSRD) is a comprehensive embedded system which incorporates drivers and relevant firmware needed to operate various design components. FreeRTOS and First Stage Bootloader (FSBL) is built on RISC-V RX CPU Core. The primary function of FSBL is to initialize the hardware blocks in the design using the respective IP drivers and ensure the integrity of the firmware by performing CRC check.

GHRD and GSRD are integrated together to establish a complete system for which relevant binaries and executables are generated by Lattice SW tools such as Propel SDK, Propel Builder and Radiant to program the FPGA Hardware.

As a part of multi-boot demo, the executables folder comprises of compatible binaries and executable images, i.e., FPGA Bitstream (.bit) and Firmware Binary (.bin) for both Primary and Golden GSRD projects. The only difference is that the Primary bitstream contains the code for multi-boot enablement and Golden bitstream does not enable multi-boot.

The GSRD for the Avant-AT-E device is developed and tested with the following Lattice Propel™ and Lattice Radiant™ software versions.

**Note:**

1. The Golden System Reference Design and Demonstration for Avant-E version 2.0 is available in the [GHRD/GSRD Reference Design](#) and [GHRD/GSRD Demonstration](#) web pages.

## 1.2. Quick Facts

**Table 1.1. Summary of the System**

| SoC Requirements    | Supported FPGA Family    | Lattice Avant™-AT-E                                                 |

|---------------------|--------------------------|---------------------------------------------------------------------|

|                     | SoC Version              | 1.0                                                                 |

| FPGA Device(s)      | Targeted Devices         | LAV-AT-E70                                                          |

|                     | Supported User Interface | AXI4-Full, AXI4-Lite, AXI-Stream, APB                               |

| Design Tool Support | Lattice Implementation   | Lattice Propel Software 2024.1<br>Lattice Radiant Software 2024.1.1 |

|                     | Synthesis                | Synopsys® Synplify Pro®                                             |

## 1.3. Features

The key features of the system include:

- FPGA device supported in this document is Lattice Avant-AT-E

- RISC-V RX CPU Core, SGDMA, TSE MAC, LPDDR4, and QSPI Flash Controller over AXI4 Interface

- Low-speed peripherals like GPIO and UART

- Bootloader, Primary and Golden FreeRTOS Application

- Application Firmware's CRC check by function implemented in RISC-V RX bootloader code

- FPGA bitstream CRC check done by FPGA Configuration Engine

- Manual and Automatic Multi-Boot capability

- FreeRTOS Application Software is run on LPDDR4 MC

- 256-bit AXI4 LPDDR4 data width to support 32-bit data to DDR at 800 MHz operating frequency

- AXI4/AXI4-Lite Peripherals at 140 MHz and APB Peripherals at 100 MHz

- 1 Gbps Ethernet throughput through RGMII support at 125 MHz

## 1.4. Naming Conventions

### 1.4.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.4.2. Signal Names

Signal names that end with:

- `_n` are active low (asserted when value is logic 0)

- `_i` are input signals

- `_o` are output signals

- `_io` are bi-directional input/output signals

## 2. Functional Description

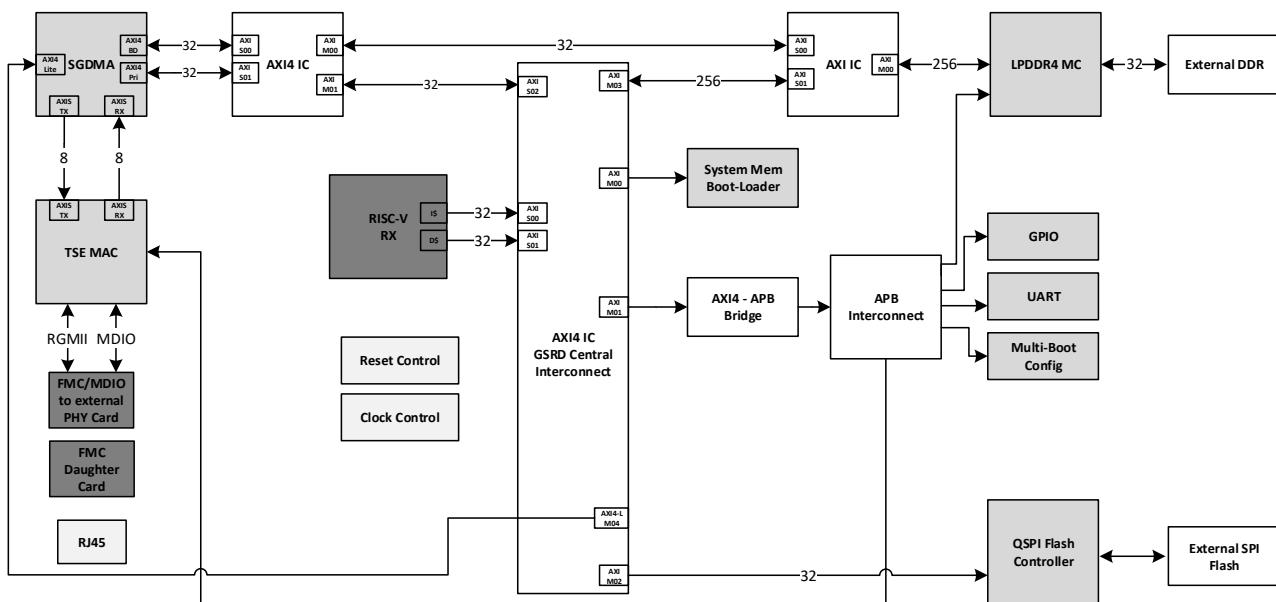

The GSRD/GHRD SoC architecture comprises of a RISC-V CPU core, LPDDR4 Memory Controller, SGDMA controller, QSPI Flash Controller, and a 1 Gbps TSE MAC, interconnected through a combination of high-speed and low-speed bus fabrics such as AXI4 Interconnect and APB Interconnect. This architecture enables seamless communication and data exchange between the components, facilitating efficient operation and system performance.

## 2.1. System Architecture Overview

### 2.1.1. Avant-AT-E

**Figure 2.1. GHRD Architecture on Avant-AT-E**

The design includes the following components:

**Table 2.1. IP Versions**

| Soft-IP                  | IP Version |

|--------------------------|------------|

| RISC-V RX Processor      | v2.4.0     |

| LPDDR4 Memory Controller | v2.2.1     |

| System Memory            | v2.2.0     |

| QSPI Flash Controller    | v1.2.0     |

| General Purpose I/O GPIO | v1.6.2     |

| UART                     | v1.3.0     |

| AXI4 Interconnect        | v2.0.1     |

| APB Interconnect         | v1.2.1     |

| AXI to APB Bridge        | v1.2.0     |

| Tri-Speed Ethernet MAC   | v1.6.0     |

| SGDMA                    | v2.2.0     |

| AXI4 Register Slice      | v1.0.0     |

| Multi-Boot Configuration | V1.0.0     |

| PLL                      | v1.9.0     |

| OSC                      | V2.1.0     |

Each component in the block diagram is instantiated using the IP in Propel Builder. The IP features and parameters are described in the [IP Configurations](#) section.

The signals in each interface are described in the [Signal Description](#) section.

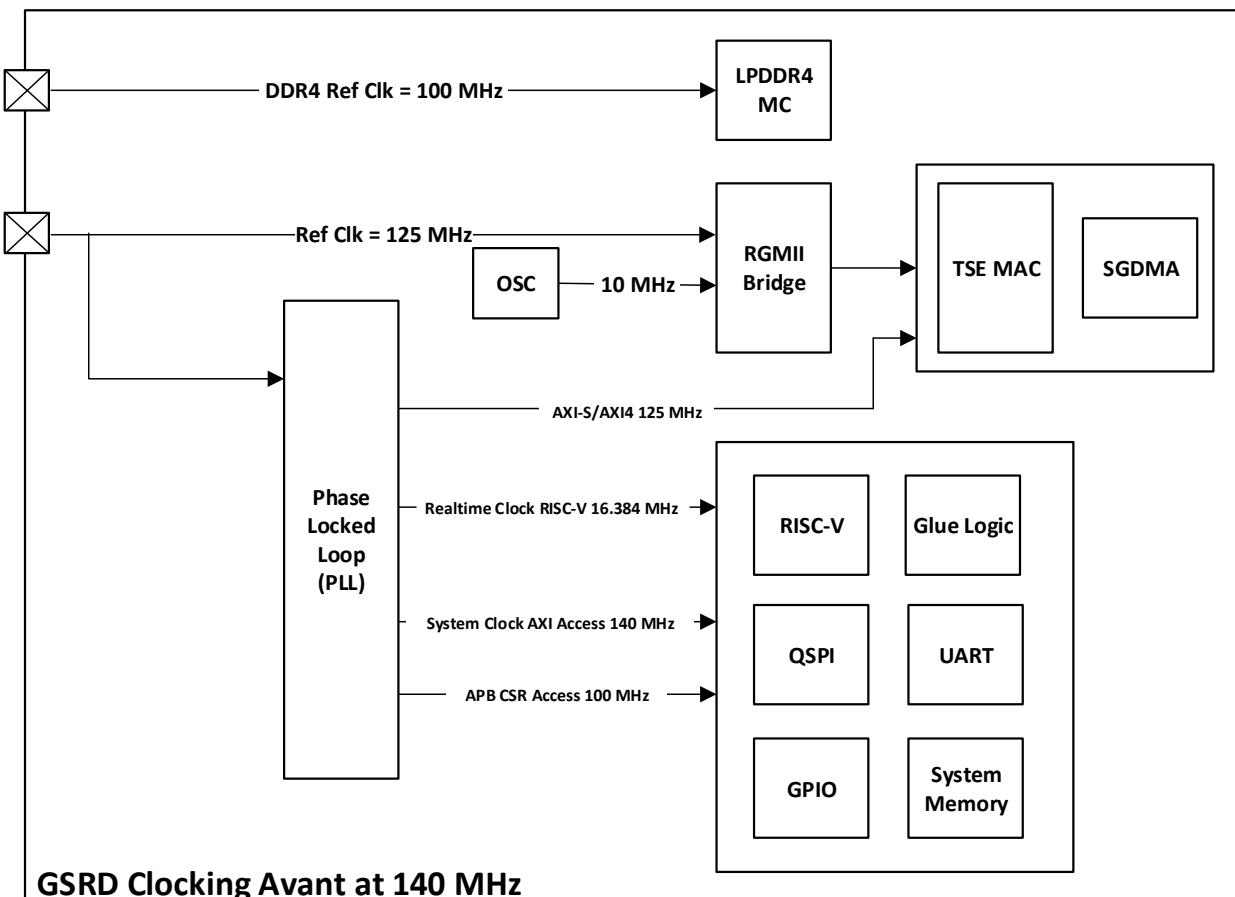

## 2.2. Clocking

This section describes the reference design clocking scheme. There are some minor differences between the clocking scheme and the Lattice Avant-AT-E device. Refer to the [Clocking Overview for Avant-AT-E](#) section.

### 2.2.1. Clocking Overview for Avant-AT-E

There are five clocks in GSRD Avant-AT-E Architecture listed as follows:

- External PLL Reference Clock for LPDDR4 is 100 MHz

- External Reference Clock for TSE MAC is 125 MHz

- On-Chip Oscillator Clock is 10 MHz for TSE MAC MDIO Interface

- External Oscillator Clock is 125 MHz as Input Reference Clock to the PLL

- RISC-V Low Frequency Realtime Clock derived from FPGA PLL is 16.384 MHz

- Internal System Clock derived from FPGA PLL is 125 MHz

- All AXI Peripherals are operating at 140 MHz

- All APB Peripherals are operating at 100 MHz

Figure 2.2. Clocking Structure for Avant-AT-E GSRD

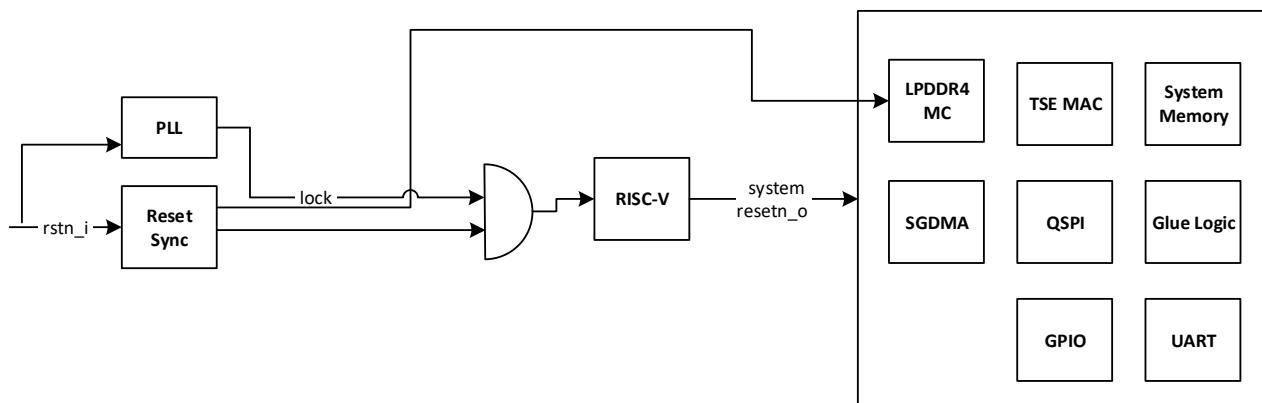

## 2.3. Reset Scheme

There are two resets in the entire design:

- External Asynchronous Reset which is controlled by a push button

- Synchronous Reset for entire system is generated from RISC-V

**Table 2.2. Reset Scheme**

| Reset Signal  | Source                     | Destination                      | Description                                                                                                                        |

|---------------|----------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| rstn_i        | Board Pushbutton           | PLL reset input and Synchronizer | Reset the PLL                                                                                                                      |

| cpu_rstn_i    | PLL Lock and synced rstn_i | RISC-V RX reset input            | Release RISC-V RX from reset pin, synchronizer and PLL lock                                                                        |

| system_rstn_o | RISC-V RX output           | All components in system         | RISC-V RX output reset provides reset to all components in the design. This also triggers the reset during CPU OCD debugging mode. |

**Figure 2.3. Reset Structure for Avant-AT-E GSRD**

## 2.4. IP Configurations

The reference design is created using Lattice Propel Builder. The top-level HDL file is generated by Propel Builder and is used as the top module for the design. The design parameterization is performed by configuring the IP in Propel Builder. This section describes the following IPs and their configuration.

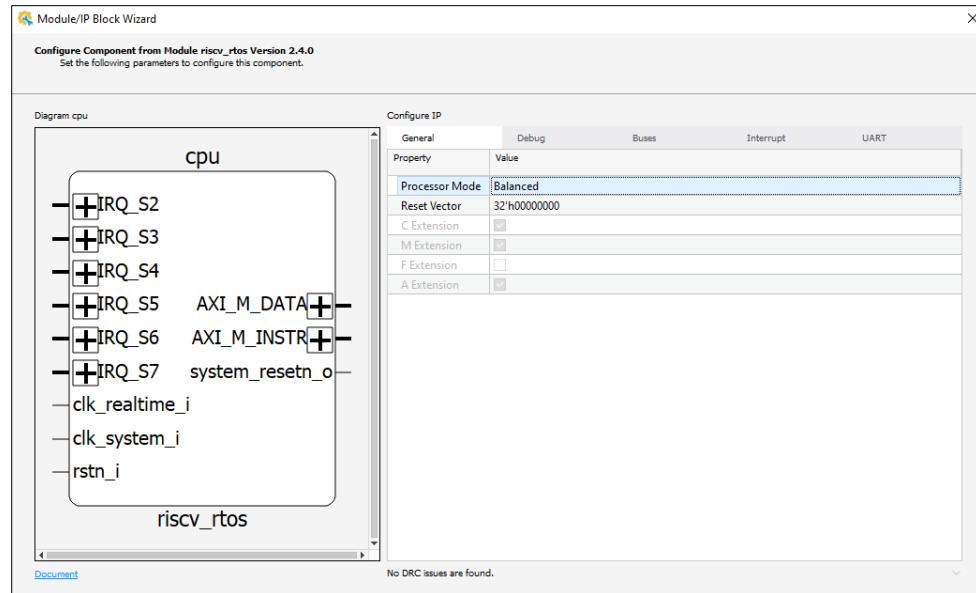

### 2.4.1. RISC-V RX CPU Core

For more information about the IP core including register map information, refer to [RISC-V RX CPU IP Core User Guide \(FPGA-IPUG-02241\)](#). The RISC-V RX CPU IP has AXI-based instruction and data ports. The instruction ports are connected to the memory that contains the bootloader software or the FreeRTOS application software for CPU execution. The data port is connected to the memory and peripherals for control.

Figure 2.4. CPU Configuration – General

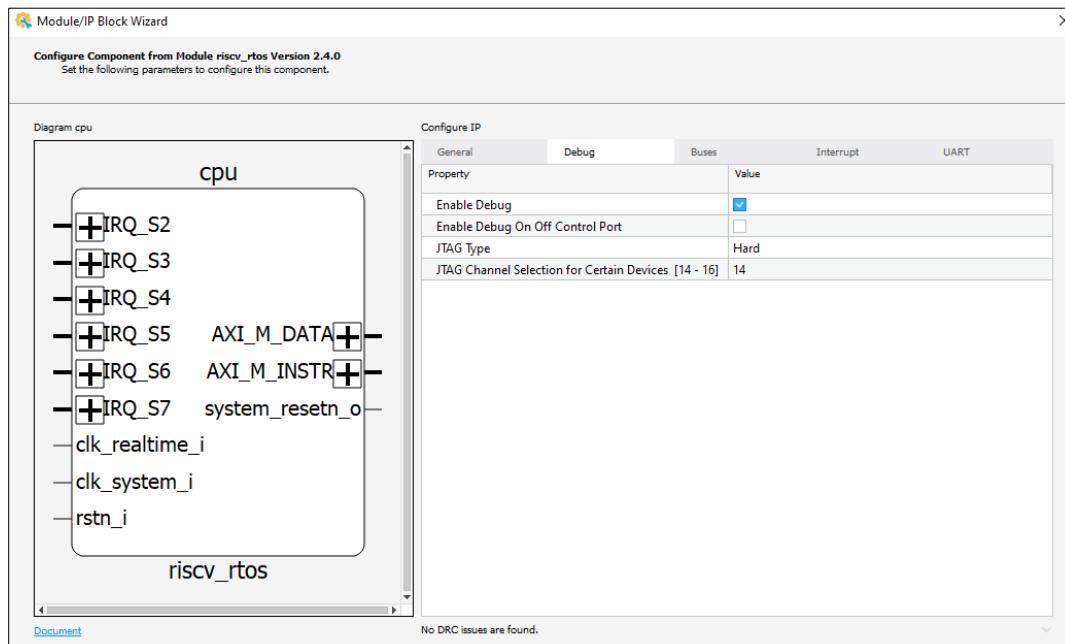

Figure 2.5. CPU Configuration – Debug

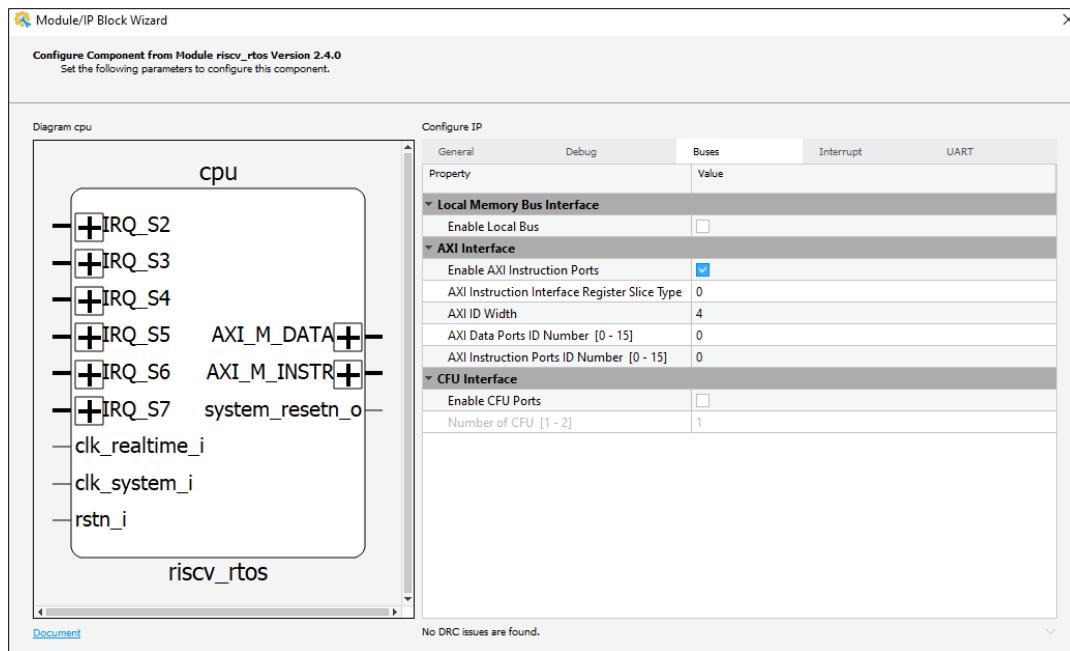

Figure 2.6. CPU Configuration – Buses

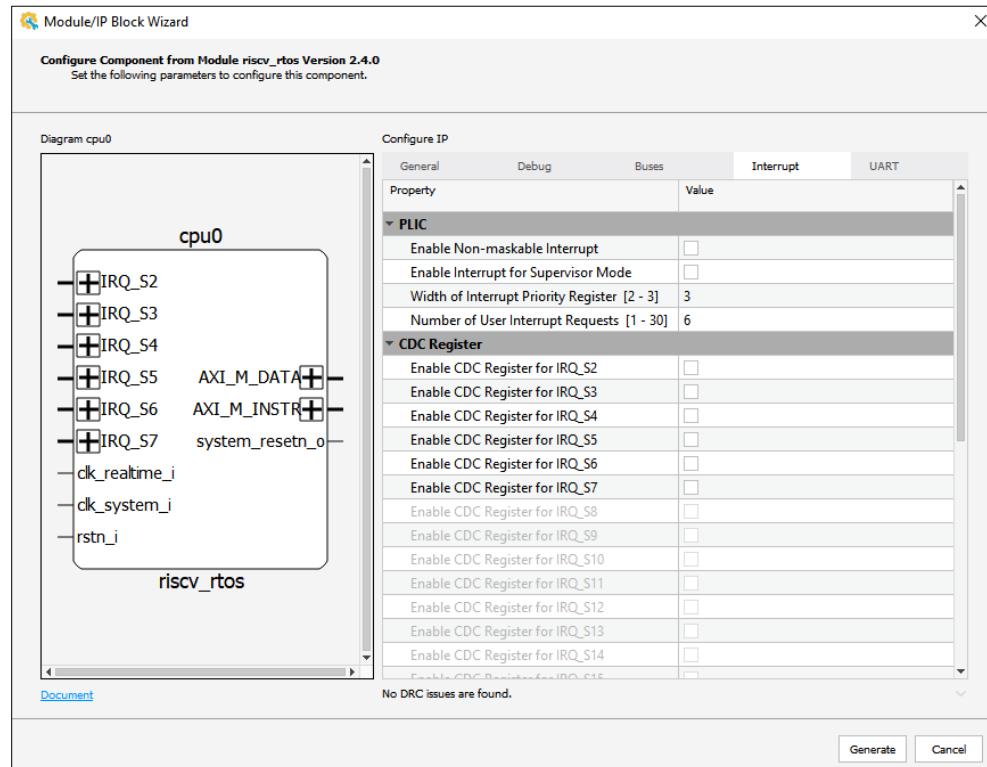

Figure 2.7. CPU Configuration – Interrupt

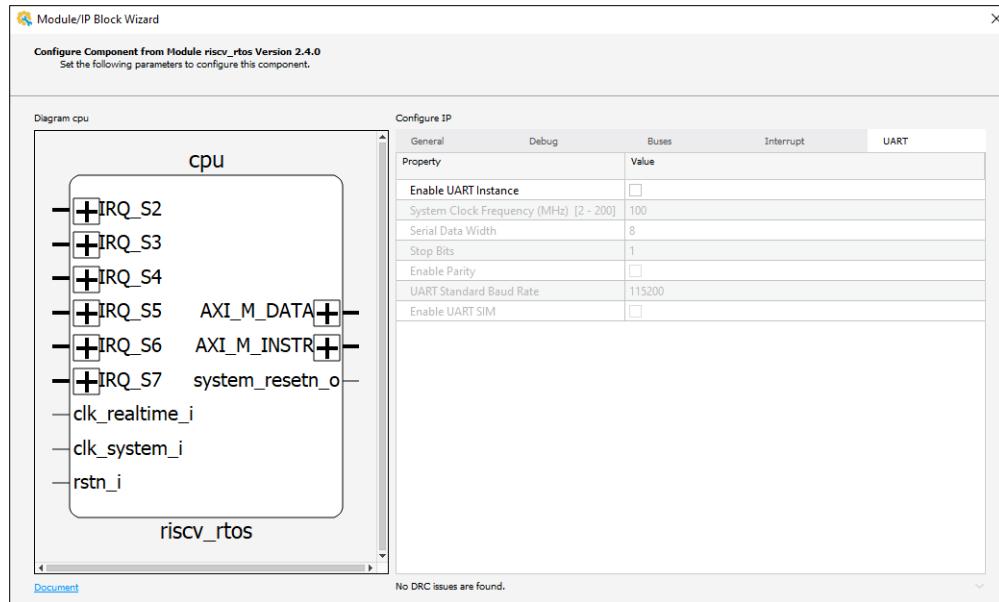

Figure 2.8. CPU Configuration – UART

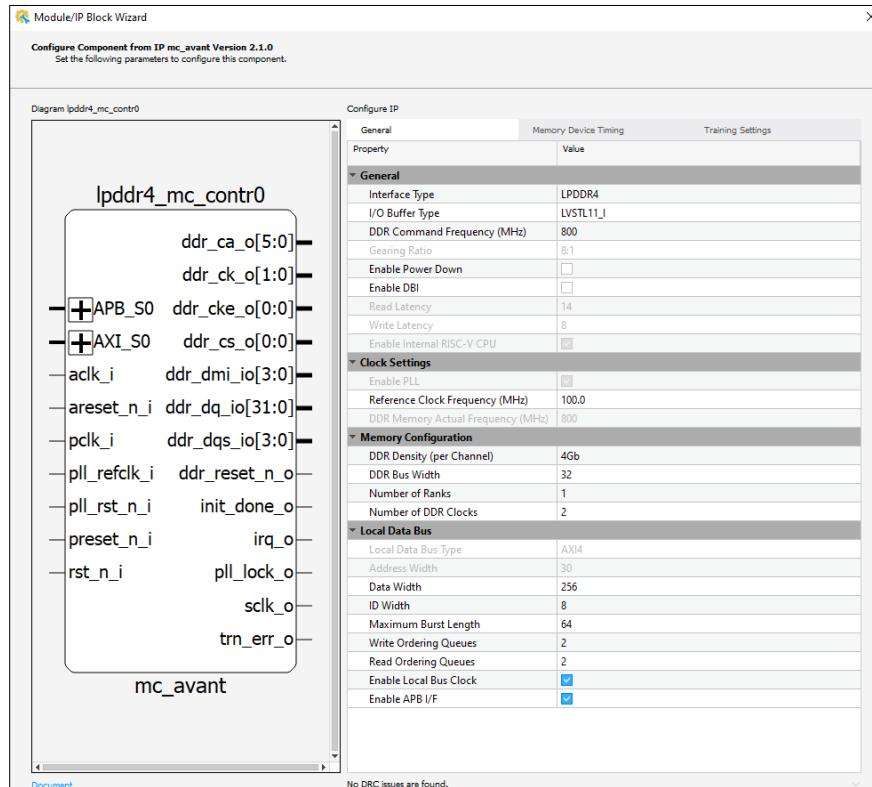

## 2.4.2. LPDDR4 Memory Controller

For more information about the IP core including register map information, refer to [Memory Controller IP Core for Avant Devices \(FPGA-IPUG-02208\)](#).

The LPDDR4 Memory Controller IP enables access to the external LPDDR4 memory modules. The memory can be used to store CPU software code and data.

Figure 2.9. LPDDR4 MC Configuration

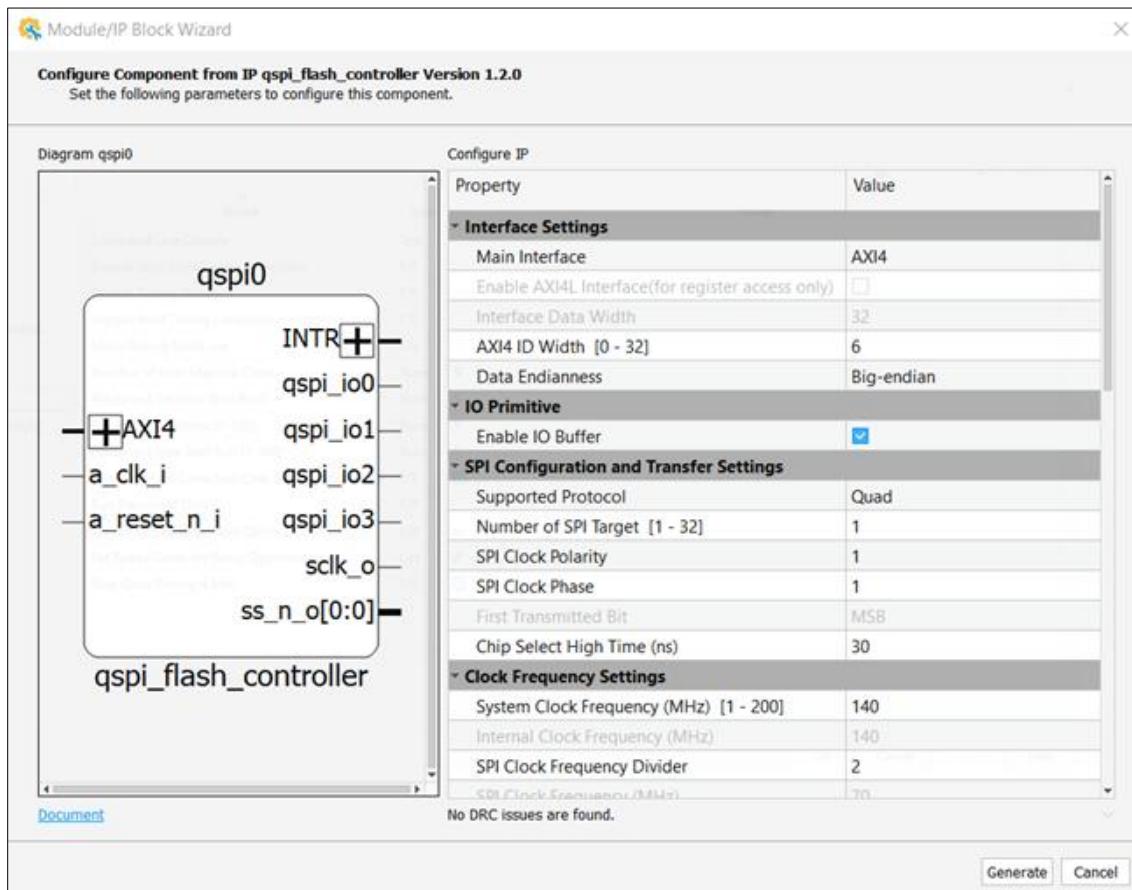

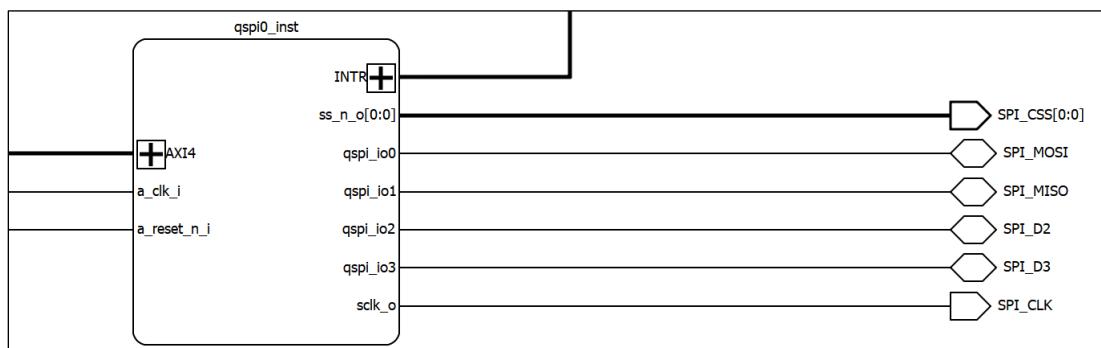

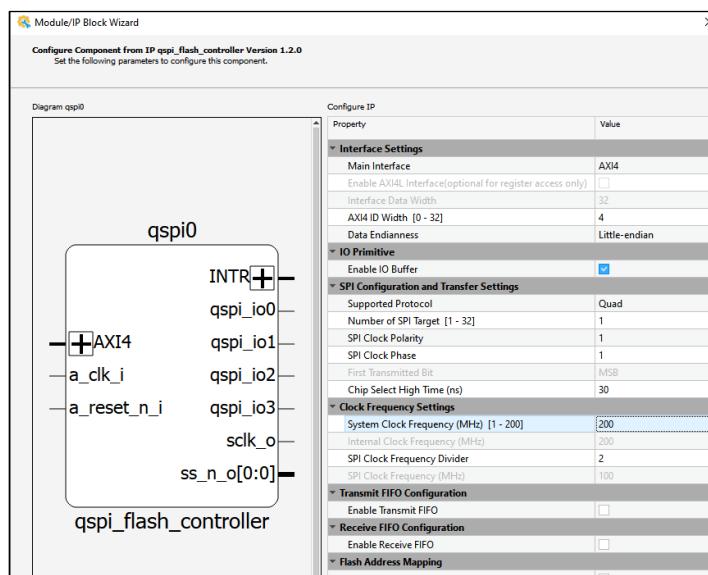

### 2.4.3. QSPI Flash Controller

For more information about the IP core including register map information, refer to [QSPI Flash Controller IP User Guide \(FPGA-IPUG-02248\)](#).

The QSPI Flash Controller is a four tri-state data line serial interface that is commonly used to store, program, erase and read SPI Flash memories. QSPI enhances the throughput of a standard SPI by four times since four bits are transferred every cycle. In GSRD, the QSPI is used to store the application software and bitstreams for both Primary and Golden systems.

Figure 2.10. QSPI Flash Controller Configuration

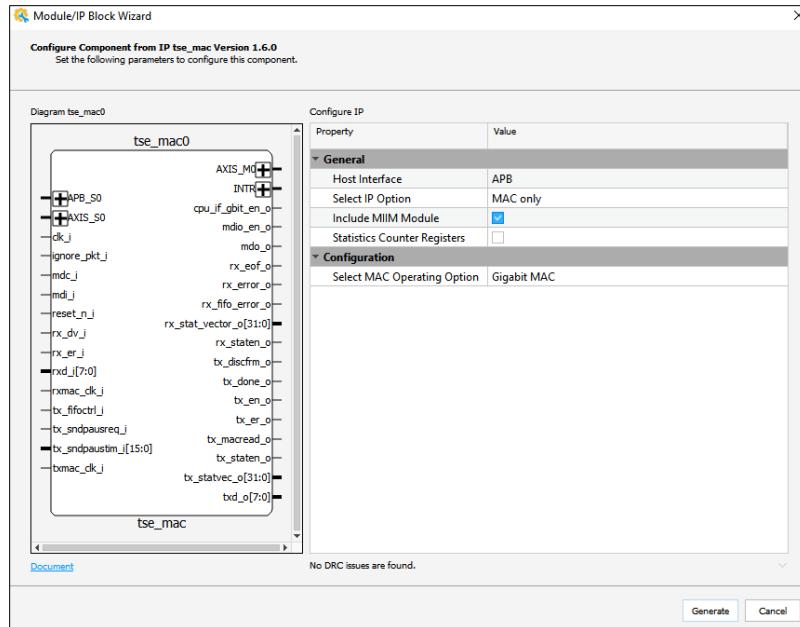

### 2.4.4. Tri-Speed Ethernet MAC

For more information about the IP core including register map information, refer to [Tri-Speed Ethernet MAC IP User Guide \(FPGA-IPUG-02084\)](#).

The TSEMAC IP core is a 10/100/1000 Mbps network interface as per the IEEE 802.3 standard. It is a complex core containing all the necessary logic, interfacing and clocking infrastructure to allow integrating an external industry-standard Ethernet PHY with an internal processor, with minimal overhead. The GSRD requires the Gigabit MAC to support 1 Gbps data-rates. The MIIM interface is used to control the external PHY control and status registers.

Figure 2.11. TSE MAC Configuration

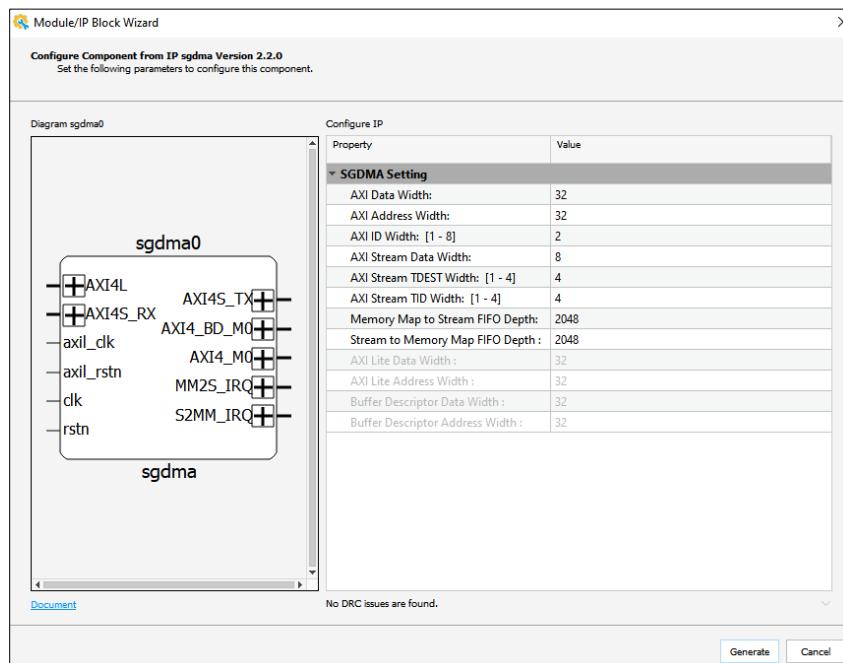

## 2.4.5. Scatter-Gather DMA

For more information about the IP core including register map information, refer to [SGDMA Controller IP Core \(FPGA-IPUG-02131\)](#).

The SGDMA Controller IP core is to access the main memory independent of the CPU processor. It offloads processor intervention. The processor initiates transfer to SGDMA Controller and receives interrupts on completion of the transfer by the DMA engine. The core implements a configurable, AXI4-compliant DMA controller with scatter-gather capability. It also implements the AXI4-Stream interface to support stream data from TSE MAC module. The AXI4-Lite CSR interface is used to configure the control and status registers by the RISC-V CPU.

Figure 2.12. SGDMA Configuration

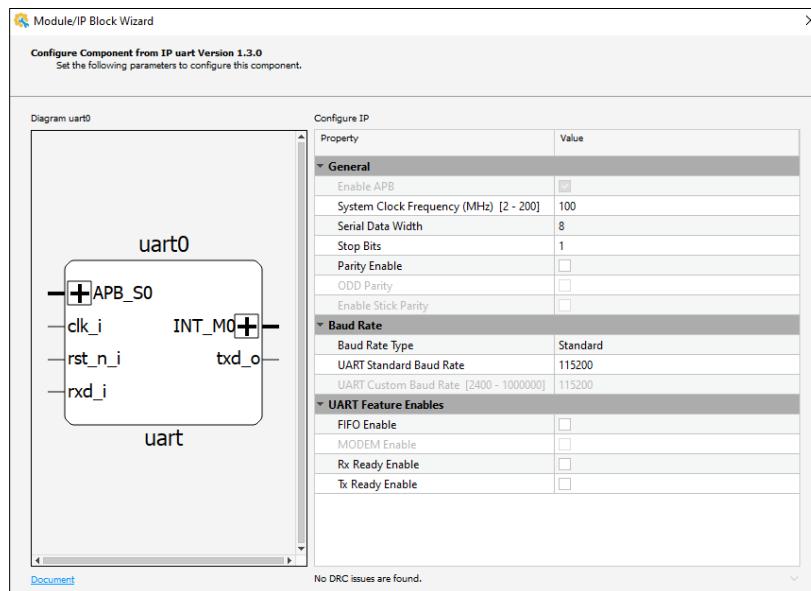

## 2.4.6. UART

For more information about the IP core including register map information, refer to [UART IP User Guide \(FPGA-IPUG-02105\)](#).

The Universal Asynchronous Receiver/Transmitter (UART) Transceiver IP core performs serial-to-parallel conversion of data characters received from a peripheral UART device and parallel-to-serial conversion of data characters received from the host locator inside the FPGA through an APB interface.

Figure 2.13. UART Configuration

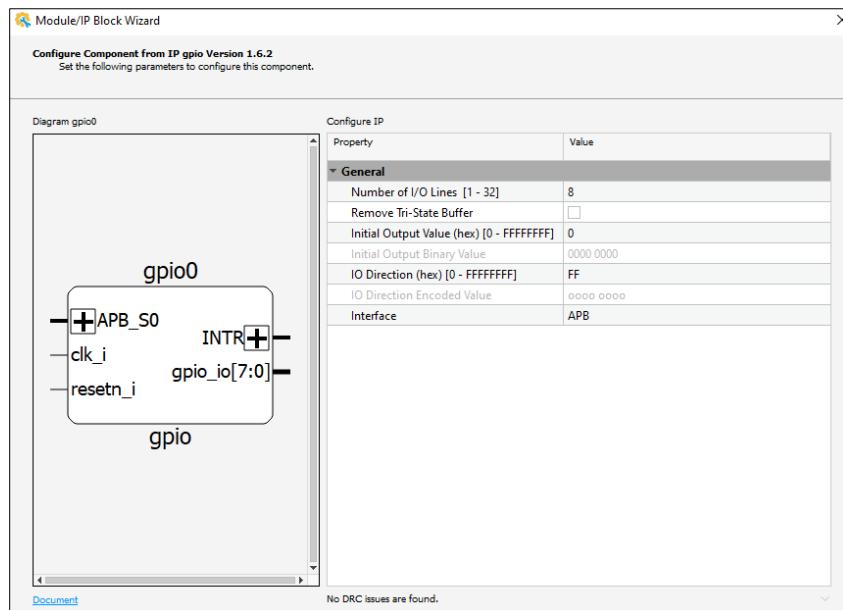

## 2.4.7. GPIO

For more information about the IP core including register map information, refer to [GPIO IP Core \(FPGA-IPUG-02076\)](#). The General Purpose Input/Output (GPIO) peripheral IP provides dedicated memory-mapped interface to configure the GPIO ports as well as the number of input and output ports.

Figure 2.14. GPIO Configuration

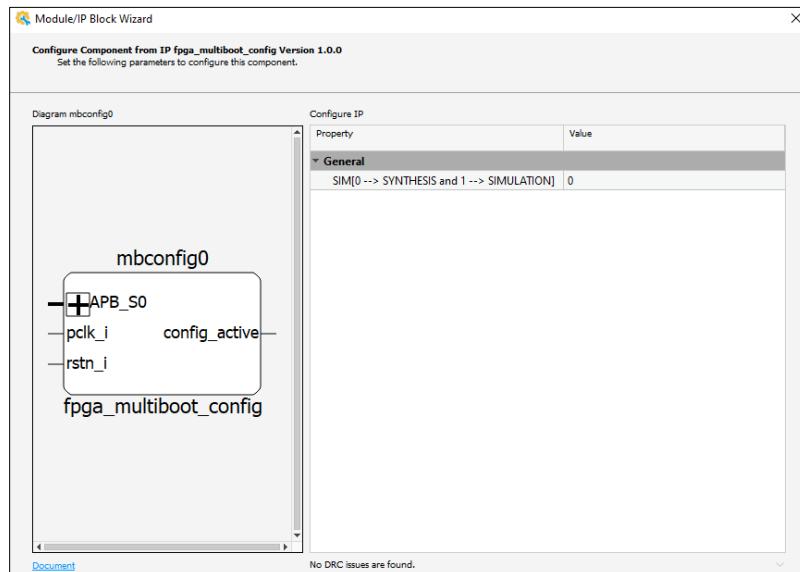

## 2.4.8. Multi-Boot Configuration Module

The Multi-Boot Configuration is used to trigger an internal FPGA REFRESH/PROGRAMM command to LMMI logic. This core IP implements an APB endpoint which decodes the RISC-V CPU command data. The LMMI host FSM inside is used to execute the soft reset to load the next or alternate bitstream and application software data onto the FPGA.

Figure 2.15. Multi-Boot Configuration

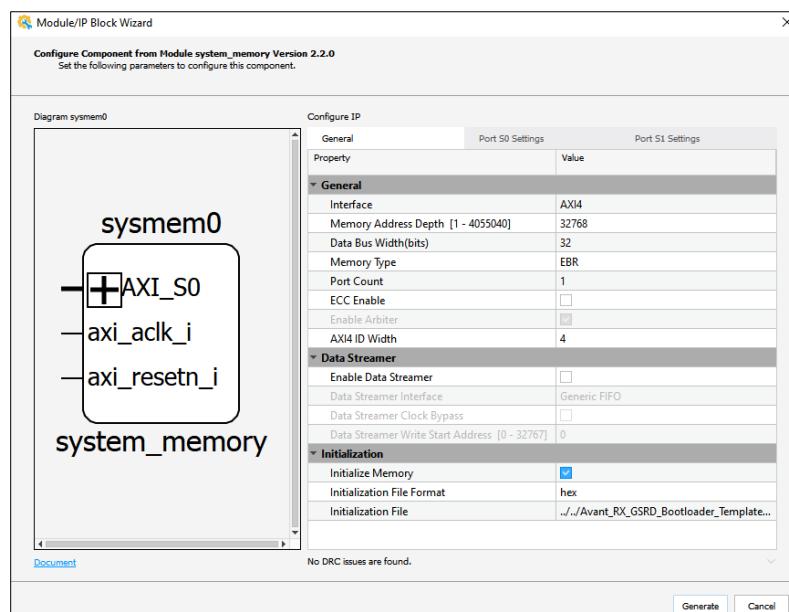

## 2.4.9. System Memory

For more information about the IP core including register map information, refer to [System Memory Module \(FPGA-IPUG-02073\)](#).

The System Memory implements EBR, LRAM, or Distributed Memory in either single port or dual port AHBL or AXI4 subordinate. In GSRD, an EBR and single AXI4 port is used. The system memory in this design is used to store the bootloader.

Figure 2.16. System Memory Configuration

## 2.5. System Level Interfaces

Table 2.3. System Level Interfaces

| Top-Level Interface Name               | Supported Protocol | Description                                           |

|----------------------------------------|--------------------|-------------------------------------------------------|

| Advanced eXtensible Interface 4        | AXI4               | Used for Data/Control Interfaces on all IPs           |

| Advanced eXtensible Interface 4 - Lite | AXI4-Lite          | Used as Control Interface for SGDMA                   |

| Advanced Peripheral Interface          | APB                | Used as Control Interface for low-speed and LPDDR4 MC |

| Serial Peripheral Interface            | SPI/QSPI           | Used for communication with external SPI Flash        |

| Dual Data Rate                         | LPDDR4             | Used for communication with external LPDDR4           |

| 1G Ethernet                            | RGMII              | Used for communication with external FMC              |

## 2.6. SoC Memory/Address Map

Table 2.4. Address Map of GHRD

| Base Address | End Address | Size (kB/MB/1 GB) | Block                    |

|--------------|-------------|-------------------|--------------------------|

| 0x00000000   | 0x0003FFFF  | 256 kB            | CPU Instruction/Data RAM |

| 0xF2000000   | 0xF20FFFFF  | 1 MB              | CLINT (CPU)              |

| 0xFC000000   | 0xFC3FFFFF  | 4 MB              | PLIC (CPU)               |

| 0xF0000000   | 0xF00003FF  | —                 | Reserved_Space1 (CPU)    |

| 0xF0000400   | 0xF1FFFFFF  | —                 | Reserved_Space2 (CPU)    |

| 0xFC400000   | 0xFFFFFFFF  | —                 | Reserved_Space3 (CPU)    |

| 0x40000000   | 0x40000FFF  | 4 kB              | GPIO                     |

| 0x40092000   | 0x40092FFF  | 4 kB              | LPDDR4 APB               |

| 0x80000000   | 0xBFFFFFFF  | 1 GB              | LPDDR4 AXI               |

| 0x40097000   | 0x40097FFF  | 4 kB              | Multi-Boot Config APB    |

| 0x40300000   | 0x4030FFFF  | 64 kB             | QSPI Flash Controller    |

| 0x40098000   | 0x40099FFF  | 4 kB              | SGDMA                    |

| 0x00000000   | 0x0001FFFF  | 128 kB            | System Memory            |

| 0x40001000   | 0x40004FFF  | 16 kB             | TSE MAC                  |

| 0x40090000   | 0x40090FFF  | 4 kB              | UART                     |

| 0x40099000   | 0x40099FFF  | 4 kB              | Watch Dog Timer          |

## 2.7. Functional Operation

The GSRD system comprises of two SoCs (System on Chip) such as Primary and Golden. Each SoC is linked with its respective First-Stage Bootloader (FSBL) and a FreeRTOS Application Software. These SoCs are built using Lattice Propel SDK, Lattice Propel Builder, and Lattice Radiant software tools. The FPGA image comprises of the entire system and is generated by the Radiant tool in the (.bit) bitstream format. The bootloader code is stored inside the system memory and is part of the bitstream. The bitstream and the FreeRTOS application software are stored into the external SPI Flash (Winbond).

During power-on, the Primary FPGA image is loaded into the device CRAM by the Config Engine. Before the device is completely programmed with the bitstream, the config engine checks the CRC (Cyclic Redundancy Check) for the bitstream to be loaded onto the FPGA. Once the FPGA is configured, DONE LED on the board glows green. Immediately, the RISC-V starts executing the bootloader software stored inside system memory and initialize all the soft-IP modules and peripherals to establish a base for communication and data transfers. This process includes configuring the IPs for the desired system operation. After all the IP configuration is complete, RISC-V initiates trigger the QSPI Flash controller to copy the FreeRTOS application software from external SPI Flash into the external LPDDR4 for software execution. Once the application software is copied, the RISC-V checks the CRC on entire copied application software. If the CRC check fails, RISC-V initiates a soft reset/refresh by instructing the multi-boot configuration module to start the PROGRAMN sequence. The PROGRAMN sequence loads the next bitstream into the FPGA which in this case would be the Golden FPGA and FW images, and the same process follows. Once CRC check passes for either Primary or Golden, the RISC-V jumps to the application instruction and starts the FreeRTOS FW execution.

### 3. Signal Description

Table 3.1 shows the input/output interface signals for the top-level module.

**Table 3.1. Top-level I/O**

| Signal Name            | I/O Type     | I/O Width | Description                                                                                     |

|------------------------|--------------|-----------|-------------------------------------------------------------------------------------------------|

| clk_125MHz             | Input        | 1         | Reference clock input for internal PLL and TSE MAC/SGMII                                        |

| pll_refclk_i           | Input        | 1         | Reference clock input for LPDDR4 MC internal PLL                                                |

| rstn_i                 | Input        | 1         | Active low reset input for reference design. Activate by pressing SW1 push button on the board. |

| <b>GPIO</b>            |              |           |                                                                                                 |

| s0_gpio                | Input/Output | 8         | General Purpose I/O signals connect to LED on board                                             |

| <b>UART</b>            |              |           |                                                                                                 |

| s1_uart_txd_o          | Output       | 1         | UART transmit output. Connects to the board TXD signal.                                         |

| s1_uart_rxd_i          | Input        | 1         | UART receive input. Connects to the board RXD signal.                                           |

| <b>QSPI Flash</b>      |              |           |                                                                                                 |

| SPI_CLK                | Output       | 1         | Serial clock to SPI Flash                                                                       |

| SPI_CSS                | Output       | 1         | SPI Flash chip select                                                                           |

| SPI_MOSI               | Input/Output | 1         | Serial data between FPGA and external SPI Flash                                                 |

| SPI_MISO               | Input/Output | 1         | Serial data between FPGA and external SPI Flash                                                 |

| SPI_D2                 | Input/Output | 1         | Serial data between FPGA and external SPI Flash                                                 |

| SPI_D3                 | Input/Output | 1         | Serial data between FPGA and external SPI Flash                                                 |

| <b>LPDDR4 MC</b>       |              |           |                                                                                                 |

| ddr_ca_o               | Output       | 6         | LPDDR4 command/address                                                                          |

| ddr_ck_o               | Output       | 1         | LPDDR4 clock                                                                                    |

| ddr_cke_o              | Output       | 1         | LPDDR4 clock enable                                                                             |

| ddr_cs_o               | Output       | 1         | LPDDR4 chip select                                                                              |

| ddr_dmi_io             | Input/Output | 4         | LPDDR4 data mask                                                                                |

| ddr_dq_io              | Input/Output | 32        | LPDDR4 Data                                                                                     |

| ddr_dqs_io             | Input/Output | 4         | LPDDR4 data strobe                                                                              |

| ddr_reset_n_o          | Output       | 1         | External Memory chip reset signal                                                               |

| init_done_o            | Output       | 1         | Connects to LED for status check                                                                |

| irq_o                  | Output       | 1         | Connects to LED for status check                                                                |

| pll_lock_o             | Output       | 1         | Connects to LED for status check                                                                |

| sclk_o                 | Output       | 1         | Connects to LED for status check                                                                |

| trn_err_o              | Output       | 1         | Connects to LED for status check                                                                |

| <b>RGMII Interface</b> |              |           |                                                                                                 |

| rgmii_rxc_i            | Input        | 1         | RGMII Receive Clock from external PHY                                                           |

| rgmii_rxctl_i          | Input        | 1         | RGMII Receive Control signal from external PHY                                                  |

| rgmii_rxd_i            | Input        | 4         | 4-bit RGMII Receive Data from external PHY                                                      |

| rgmii_txc_o            | Output       | 1         | RGMII Transmit Clock to external PHY                                                            |

| rgmii_txctl_o          | Output       | 1         | RGMII Transmit Control signal to external PHY                                                   |

| rgmii_txd_o            | Output       | 4         | 4-bit RGMII Transmit Data to external PHY                                                       |

| rgmii_mdio_o           | Output       | 1         | RGMII Transmit Control signal to external PHY                                                   |

| rgmii_mdc_o            | Output       | 1         | RGMII Transmit Control signal to external PHY                                                   |

| phy_resetn_o           | Output       | 1         | Hard reset generated from FPGA to reset the external PHY                                        |

| <b>Multi-Boot</b>      |              |           |                                                                                                 |

| config_active_o        | Output       | 1         | Connects to LED to check Multi-Boot Configuration Block                                         |

## 4. Software Components

The GSRD (Golden System Reference Design) is enabled by RISC-V core based FreeRTOS and Lattice FPGA IP modules. Lattice developed BSP (Board Support Package) drivers in C language act as intermediaries, facilitating communication between the hardware elements on the FPGA and FreeRTOS software. During boot up, these drivers initialize and configure FPGA peripherals to establish effective coordination with the RISC-V processor.

### 4.1. Primary and Golden Bootloader

Bootloader is a bare-metal program that does the following IP configurations:

- Configures the GPIO and UART IP

- For LPDDR4 MC configuration, it first reads if the PLL Lock status is set and then initiates Memory Training and waits until training is complete.

- Configures the QSPI flash controller to read the application software stored into external flash while FIFO is disabled using API and copies it into LPDDR4.

- It then calculates the CRC value on the entire FW copied into DDR using `crc16_ccit()` API and compares the value with the original CRC value.

- Failure of the CRC check on the Primary application software triggers reconfiguration of the FPGA with the Golden FPGA bitstream image. This is done by triggering Multi-Boot Configuration module. This step is only used in Primary GSRD system.

### 4.2. Primary and Golden Application

- Executed by RISC-V RX CPU core from LPDDR4 where it initializes the BSP and Operating System

- Configures the TSE MAC handler with 1G Ethernet address, speed mode, MAC upper and lower. Passes TSE Core object to initialize the Ethernet IP and sets the MAC address.

- Creates an Ethernet frame using the API provided in `ethernet_frame.h`.

- Configure the SGDMA IP for MM2S to transfer the Ethernet frame to the TSE MAC and set up S2MM to receive packets from the TSE MAC at 2-second intervals. Runs FreeRTOS scheduler and Task Handler.

For the PHY initialization, it configures the PHY using `mdio_phy_init()` API by performing a PHY reset before starting the TSE packet traffic. The PHY configuration checks if the Marvell 88E151X PHY is attached before performing the configuration.

This also captures the packets sent from the Avant board at two second intervals.

## 5. Design Constraints

The design constraints are divided into two parts, Pre-Synthesis (SDC) and Post-Synthesis Physical (PDC) constraints. They are used to ensure that the design meets the required performance, timing closure, functionality and physical placement requirements as per the FPGA device.

### 5.1. I/O Constraints

```

Ldc_set_sysconfig {MULTI_BOOT_MODE=ENABLE MULTI_BOOT_SEL=STATIC BOOT_SEL=DUAL

MSPI_ADDRESS_32BIT=ENABLE MSPI_COMMAND_32BIT=ENABLE PROGRAMN_RECOVERY=ENABLE}

create_clock -name {pll_refclk_i} -period 10 -waveform {0.000 5.000} [get_ports

pll_refclk_i]

create_clock -name {clk_125_in} -period 8 -waveform {0.000 4.000} [get_ports clk_125_in]

create_clock -name {rgmii_mdc_o} -period 100 [get_nets rgmii_mdc_o_c]

#100MHz LPDDR4 PLL REFERENCE CLOCK

Ldc_set_location -site {AD32} [get_ports pll_refclk_i]

Ldc_set_location -site {AL10} [get_ports clk_125_in]

#RESET

Ldc_set_location -site {AC17} [get_ports rstn_i]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18 PULLMODE=UP} [get_ports rstn_i]

#UART

Ldc_set_location -site {R3} [get_ports s1_uart_txd_o]

Ldc_set_location -site {T3} [get_ports s1_uart_rxd_i]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports s1_uart_rxd_i]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports s1_uart_txd_o]

#GPIO

Ldc_set_location -site {N7} [get_ports {s0_gpio[0]}]

Ldc_set_location -site {L7} [get_ports {s0_gpio[1]}]

#Ldc_set_location -site {L8} [get_ports {s0_gpio[2]}]

#Ldc_set_location -site {P8} [get_ports {s0_gpio[3]}]

#Ldc_set_location -site {M8} [get_ports {s0_gpio[4]}]

#Ldc_set_location -site {M9} [get_ports {s0_gpio[5]}]

#Ldc_set_location -site {P10} [get_ports {s0_gpio[6]}]

#Ldc_set_location -site {N10} [get_ports {s0_gpio[7]}]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports {s0_gpio[*]}]

#SPI FLASH

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33 SLEWRATE=FAST} [get_ports SPI_CLK]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33 SLEWRATE=FAST} [get_ports SPI_CSS]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33 SLEWRATE=FAST} [get_ports SPI_MOSI]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33 SLEWRATE=FAST} [get_ports SPI_MISO]

Ldc_set_port -iobuf {PULLMODE=UP} [get_ports SPI_D2]

Ldc_set_port -iobuf {PULLMODE=UP} [get_ports SPI_D3]

Ldc_set_location -site {L12} [get_ports SPI_MOSI]

Ldc_set_location -site {L10} [get_ports SPI_D2]

Ldc_set_location -site {L11} [get_ports SPI_MISO]

Ldc_set_location -site {L9} [get_ports SPI_D3]

Ldc_set_location -site {P9} [get_ports SPI_CLK]

Ldc_set_location -site {P7} [get_ports SPI_CSS]

```

```

#FPGA CONFIG LED

Ldc_set_location -site {M8} [get_ports config_active_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports config_active_o]

#LPDDR4 MC LEDs

Ldc_set_location -site {N10} [get_ports pll_lock_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports pll_lock_o]

Ldc_set_location -site {P10} [get_ports init_done_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports init_done_o]

Ldc_set_location -site {M9} [get_ports trn_err_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports trn_err_o]

#LPDDR4 MC

Ldc_set_location -site {AC26} [get_ports {ddr_ca_o[0]}]

Ldc_set_location -site {AB27} [get_ports {ddr_ca_o[1]}]

Ldc_set_location -site {AB28} [get_ports {ddr_ca_o[2]}]

Ldc_set_location -site {AC29} [get_ports {ddr_ca_o[3]}]

Ldc_set_location -site {AB29} [get_ports {ddr_ca_o[4]}]

Ldc_set_location -site {AD27} [get_ports {ddr_ca_o[5]}]

Ldc_set_location -site {AB25} [get_ports {ddr_ck_o[0]}]

Ldc_set_location -site {AB26} [get_ports {ddr_cke_o[0]}]

Ldc_set_location -site {AA31} [get_ports {ddr_cs_o[0]}]

Ldc_set_location -site {AF34} [get_ports ddr_reset_n_o]

Ldc_set_location -site {AC23} [get_ports {ddr_dqs_io[0]}]

Ldc_set_location -site {AC34} [get_ports {ddr_dqs_io[1]}]

Ldc_set_location -site {AD22} [get_ports {ddr_dq_io[0]}]

Ldc_set_location -site {AD21} [get_ports {ddr_dq_io[1]}]

Ldc_set_location -site {AE25} [get_ports {ddr_dq_io[2]}]

Ldc_set_location -site {AE24} [get_ports {ddr_dq_io[3]}]

Ldc_set_location -site {AA21} [get_ports {ddr_dq_io[4]}]

Ldc_set_location -site {Y21} [get_ports {ddr_dq_io[5]}]

Ldc_set_location -site {AB24} [get_ports {ddr_dq_io[6]}]

Ldc_set_location -site {AC24} [get_ports {ddr_dq_io[7]}]

Ldc_set_location -site {AD34} [get_ports {ddr_dq_io[8]}]

Ldc_set_location -site {AD33} [get_ports {ddr_dq_io[9]}]

Ldc_set_location -site {AE32} [get_ports {ddr_dq_io[10]}]

Ldc_set_location -site {AE31} [get_ports {ddr_dq_io[11]}]

Ldc_set_location -site {AE33} [get_ports {ddr_dq_io[12]}]

Ldc_set_location -site {AE34} [get_ports {ddr_dq_io[13]}]

Ldc_set_location -site {AB34} [get_ports {ddr_dq_io[14]}]

Ldc_set_location -site {AB33} [get_ports {ddr_dq_io[15]}]

Ldc_set_location -site {AC21} [get_ports {ddr_dmi_io[0]}]

Ldc_set_location -site {AF33} [get_ports {ddr_dmi_io[1]}]

Ldc_set_location -site {AB30} [get_ports {ddr_ck_o[1]}]

Ldc_set_location -site {Y29} [get_ports {ddr_dqs_io[2]}]

Ldc_set_location -site {W23} [get_ports {ddr_dqs_io[3]}]

Ldc_set_location -site {U29} [get_ports {ddr_dq_io[16]}]

Ldc_set_location -site {V29} [get_ports {ddr_dq_io[17]}]

Ldc_set_location -site {U30} [get_ports {ddr_dq_io[18]}]

Ldc_set_location -site {U31} [get_ports {ddr_dq_io[19]}]

Ldc_set_location -site {Y28} [get_ports {ddr_dq_io[20]}]

```

```

Ldc_set_Location -site {AA28} [get_ports {ddr_dq_io[21]}]

Ldc_set_Location -site {V30} [get_ports {ddr_dq_io[22]}]

Ldc_set_Location -site {W30} [get_ports {ddr_dq_io[23]}]

Ldc_set_Location -site {AA24} [get_ports {ddr_dq_io[24]}]

Ldc_set_Location -site {Y24} [get_ports {ddr_dq_io[25]}]

Ldc_set_Location -site {U23} [get_ports {ddr_dq_io[26]}]

Ldc_set_Location -site {U22} [get_ports {ddr_dq_io[27]}]

Ldc_set_Location -site {U25} [get_ports {ddr_dq_io[28]}]

Ldc_set_Location -site {T25} [get_ports {ddr_dq_io[29]}]

Ldc_set_Location -site {U24} [get_ports {ddr_dq_io[30]}]

Ldc_set_Location -site {T24} [get_ports {ddr_dq_io[31]}]

Ldc_set_Location -site {V32} [get_ports {ddr_dmi_io[2]}]

Ldc_set_Location -site {V22} [get_ports {ddr_dmi_io[3]}]

# The ECLKDIV primitive already has constraint but the inferred name is not good.

# The constraint below only aims to assign a name to the generated clock.

create_generated_clock -name {sclk_o} -source [get_pins -hierarchical

{lscc_mc_avant_inst/u_ddrphy/pll_inst/gen_ext_outclkdiv*.u_PLL.PLLC_MODE_inst/CLKOPHY}]

-divide_by 8 [get_pins -hierarchical {lscc_mc_avant_inst/u_ddrphy/u_eclkdiv/ECLKDIVOUT}]

]

set_clock_uncertainty -setup 0.075 [get_clocks sclk_o]

# The PLL lock is false as it toggles only once for a long time

# It is also sampled by double FF

set_false_path -to [get_pins -hierarchical

{lscc_mc_avant_inst/u_ddrphy/i_csr/p_pll_lock_r1*/D}]

# This signal is asserted and then de-asserted while the clocks are stopped, thus, they

# are false path.

set_false_path -to [get_pins -hierarchical {lscc_mc_avant_inst/u_ddrphy/u_eclkdiv/RST}]

# Constraints for the CDC logic on the DDRPHY's CSR

set_max_delay -from [get_pins -hierarchical

{lscc_mc_avant_inst/u_ddrphy/i_csr/wr_data_buff_r*/Q}] -to [get_pins -hierarchical

{lscc_mc_avant_inst/u_ddrphy/i_csr/s_apb_data_r*/D}] -datapath_only 3

set_max_delay -from [get_pins -hierarchical

{lscc_mc_avant_inst/u_ddrphy/i_csr/addr_buff_r*/Q}] -to [get_pins -hierarchical

{lscc_mc_avant_inst/u_ddrphy/i_csr/s_apb_addr_r*/D}] -datapath_only 3

#Constraints for MC's FIFO DC instances

# The distributed RAM data output port to FIFO_DC data output register is already

# guaranteed by the CDC logic and above constraints.

set_max_delay -from [get_pins -hierarchical

{lscc_mc_avant_inst/AXI_BI.u_axi_if/u_rd/ASYNC.u_ctrl_fifo/u_fifo_dc/*.dpram_inst/D0*}]

-datapath_only 3

set_max_delay -from [get_pins -hierarchical

{lscc_mc_avant_inst/AXI_BI.u_axi_if/u_rd/u_rd_rsp/u_data_fifo/u_fifo_dc/*.dpram_inst/D0*}]

-datapath_only 3

set_max_delay -from [get_pins -hierarchical

{lscc_mc_avant_inst/AXI_BI.u_axi_if/u_wr/ASYNC.u_ctrl_fifo/u_fifo_dc/*.dpram_inst/D0*}]

-datapath_only 3

```

```

set_max_delay -from [get_pins -hierarchical

{lscmc_avant_inst/AXI_BI.u_axi_if/u_wr/ASYNC.u_data_fifo/u_fifo_dc/*.dpram_inst/D0*}]

-datapath_only 3

# The reset pin of double FF that synchronizes the reset de-assertion is false path

set_false_path -to [get_pins -hierarchical {lscmc_avant_inst/rst_n*/CD}]

set_false_path -to [get_pins -hierarchical {lscmc_avant_inst/reset_n*/CD}]

set_false_path -to [get_pins -hierarchical {lscmc_avant_inst/phy_srst_n*/CD}]

set_false_path -to [get_pins -hierarchical

{lscmc_avant_inst/u_ddrphy/start_rst_r*/PD}]

set_false_path -to [get_pins -hierarchical {lscmc_avant_inst/u_ddrphy/s_rst_n_r*/CD}]

# TSE MAC RGMII Constraints

Ldc_set_location -site {Y10} [get_ports rgmii_txc_o]

Ldc_set_location -site {AB12} [get_ports rgmii_txctl_o]

Ldc_set_location -site {Y11} [get_ports {rgmii_txd_o[0]}]

Ldc_set_location -site {AA2} [get_ports {rgmii_txd_o[1]}]

Ldc_set_location -site {Y2} [get_ports {rgmii_txd_o[2]}]

Ldc_set_location -site {AB13} [get_ports {rgmii_txd_o[3]}]

Ldc_set_location -site {Y7} [get_ports rgmii_rxc_i]

Ldc_set_location -site {Y6} [get_ports rgmii_rxctl_i]

Ldc_set_location -site {AC7} [get_ports {rgmii_rxd_i[0]}]

Ldc_set_location -site {AC6} [get_ports {rgmii_rxd_i[1]}]

Ldc_set_location -site {AD6} [get_ports {rgmii_rxd_i[2]}]

Ldc_set_location -site {AD5} [get_ports {rgmii_rxd_i[3]}]

Ldc_set_location -site {AA8} [get_ports rgmii_mdc_o]

Ldc_set_location -site {Y9} [get_ports rgmii_mdio_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18} [get_ports rgmii_rxc_i]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18} [get_ports rgmii_rxctl_i]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18} [get_ports {rgmii_rxd_i[*]}]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18 SLEWRATE=FAST} [get_ports rgmii_txc_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18 SLEWRATE=FAST} [get_ports rgmii_txctl_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18 SLEWRATE=FAST} [get_ports {rgmii_txd_o[*]}]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18} [get_ports rgmii_mdc_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18 PULLMODE=UP} [get_ports rgmii_mdio_o]

Ldc_set_location -site {AA9} [get_ports phy_resetn_o]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS18} [get_ports phy_resetn_o]

#create_clock -name {rgmii_rxc_i} -period 8 -waveform {2 6} [get_ports rgmii_rxc_i]

create_clock -name {rgmii_rxc_i} -period 8 [get_ports rgmii_rxc_i]

create_clock -name {rgmii_rxc_i_pad_0} -period 8

#create_clock -name {rgmii_txc_o} -period 8 [get_nets rgmii_txc_o_c]

# - phase-shift 90 Degree

set_input_delay -clock [get_clocks rgmii_rxc_i] -max 0.5 [get_ports {rgmii_rxctl_i

rgmii_rxd_i[*]}]

set_input_delay -clock [get_clocks rgmii_rxc_i] -clock_fall -min -add_delay -0.5

[get_ports {rgmii_rxctl_i rgmii_rxd_i[*]}]

set_output_delay -clock [get_clocks rgmii_txc_o_c] -max 1 [get_ports {rgmii_txctl_o

rgmii_txd_o[*]}]

set_output_delay -clock [get_clocks rgmii_txc_o_c] -clock_fall -min -add_delay -0.8

[get_ports {rgmii_txctl_o rgmii_txd_o[*]}]

```

```

set_clock_groups -group [get_clocks clk_125_in] -group [get_clocks rgmii_txc_o_c] -group

[get_clocks rgmii_rxc_i] -group [get_clocks rgmii_mdc_o] -asynchronous

set_clock_groups -group [get_clocks clk_125_in] -group [get_clocks rgmii_txc_o_c] -group

[get_clocks pll0_inst_clkos2_o_net] -group [get_clocks

{pll0_inst/lssc_pll_inst/clkout_testclk_o}] -group [get_clocks pll0_inst_clkos_o_net] -

group [get_clocks sclk_o] -group [get_clocks {pll0_inst_clkos3_o_net[0]}] -asynchronous

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports TCK]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports TDI]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports TMS]

Ldc_set_port -iobuf {IO_TYPE=LVCMOS33} [get_ports TDO]

set_false_path -from [get_ports rstn_i]

set_false_path -from [get_pins {cpu0_inst/system_resetn_o}]

```

## 6. Resource Utilization

Figure 6.1 shows the GSRD resource utilization and Table 6.1 shows the total LUT4, PFU register, I/O buffer, and EBR resource utilization for Avant-AT-E70.

|                            | LUT4 Logic | LUT4 Distributed RAM | LUT4 Ripple Logic | PFU Registers | I/O Registers | I/O Buffers | DSP MULT | EBR   |

|----------------------------|------------|----------------------|-------------------|---------------|---------------|-------------|----------|-------|

| ▼ soc_primary_gnd          | 41967(12)  | 21906(0)             | 4720(0)           | 47925(6)      | 2(0)          | 91(30)      | 6(0)     | 78(0) |

| ► apb_interconnect0_inst   | 127(0)     | 0(0)                 | 0(0)              | 6(0)          | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► axi2apb0_inst            | 253(0)     | 0(0)                 | 54(0)             | 198(0)        | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► axi4_interconnect0_inst  | 11836(0)   | 6282(0)              | 580(0)            | 17031(0)      | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► axi4_interconnect1_inst  | 2319(0)    | 1746(0)              | 58(0)             | 2891(0)       | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► axi4_interconnect2_inst  | 4659(0)    | 6714(0)              | 220(0)            | 7859(0)       | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► axi_register_slice0_inst | 163(1)     | 0(0)                 | 0(0)              | 301(0)        | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► cpu0_inst                | 4990(0)    | 252(0)               | 1258(0)           | 3311(0)       | 0(0)          | 0(0)        | 6(0)     | 15(0) |

| ► gpio0_inst               | 109(0)     | 0(0)                 | 0(0)              | 97(0)         | 0(0)          | 8(0)        | 0(0)     | 0(0)  |

| ► lpdr4_mc_ctrl0_inst      | 7820(2)    | 1518(0)              | 1056(0)           | 8956(0)       | 0(0)          | 49(0)       | 0(0)     | 25(0) |

| ► mbconfig0_inst           | 15(0)      | 0(0)                 | 0(0)              | 64(0)         | 1(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► osc0_inst                | 0(0)       | 0(0)                 | 0(0)              | 0(0)          | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► pll0_inst                | 22(0)      | 0(0)                 | 0(0)              | 15(0)         | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► qspi0_inst               | 3212(0)    | 0(0)                 | 346(0)            | 2179(0)       | 0(0)          | 4(0)        | 0(0)     | 0(0)  |

| ► rst_sync0_inst           | 43(0)      | 0(0)                 | 32(0)             | 36(0)         | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► sgdma0_inst              | 1575(0)    | 0(0)                 | 538(0)            | 2063(0)       | 0(0)          | 0(0)        | 0(0)     | 4(0)  |

| ► sysmem0_inst             | 478(0)     | 0(0)                 | 82(0)             | 343(0)        | 0(0)          | 0(0)        | 0(0)     | 32(0) |

| ► tse_mac0_inst            | 3021(0)    | 3840(0)              | 412(0)            | 1842(0)       | 0(0)          | 0(0)        | 0(0)     | 2(0)  |

| ► tse_to_rgmi_bridge0_inst | 666(0)     | 1554(0)              | 36(0)             | 119(0)        | 0(0)          | 0(0)        | 0(0)     | 0(0)  |

| ► uart0_inst               | 647(0)     | 0(0)                 | 48(0)             | 608(0)        | 1(0)          | 0(0)        | 0(0)     | 0(0)  |

Figure 6.1. GSRD Resource Utilization on Avant-AT-E70

Table 6.1. GSRD Total Resource Utilization

| Resource                                      | Usage | Percentage Utilization |

|-----------------------------------------------|-------|------------------------|

| LUT4 (Logic + Distributed RAM + Ripple Logic) | 68593 | 17.25%                 |

| PFU Register                                  | 47925 | 12.05%                 |

| I/O Buffers                                   | 91    | —                      |

| EBR                                           | 78    | 7.87%                  |

## 7. Demo User Guide

### 7.1. Boot-Up Sequence

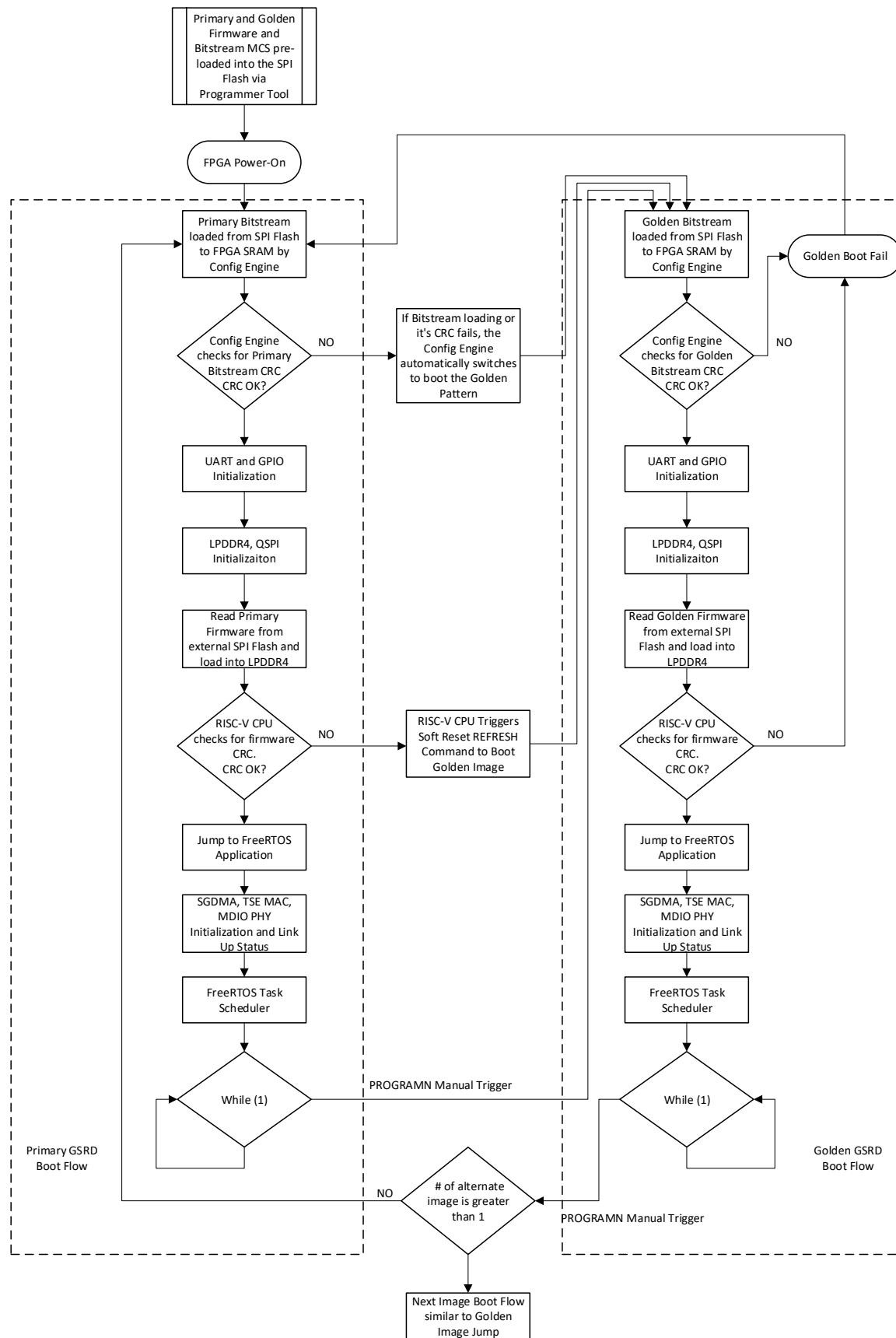

This section describes the RISC-V RX CPU boot up sequence that configures IP drivers, operating modes, bootloader and FreeRTOS application software execution.

Here is the description of the terms used throughout the document:

- Boot Up – Process of starting the RISC-V RX CPU, loading the FreeRTOS application software from external SPI Flash into the LPDDR4 memory and executing the application.

- Bootloader – Code that initializes and configures various peripherals and loads the FreeRTOS application software into LPDDR4 memory. It also checks for the CRC of the copied application and decides whether to execute the application software or load the next best bitstream hardware and corresponding software.

- FreeRTOS – Application software that is loaded into LPDDR4 Memory and executed by RISC-V CPU at the end of boot up process.

- SPI Flash – Non-volatile external memory that stores the FreeRTOS application software and multi-boot MCS bitstream.

The following is the boot up sequence shown in [Figure 7.1](#):

- The system provides similar functionality both in Bare Metal and FreeRTOS mode. For the demo, the Golden and Primary application software binaries and their FPGA bitstream images are stored in external SPI Flash before the boot up sequence is initiated.

- The initial bootloader is a part of the internal system memory ROM embedded into the FPGA bitstream stored inside the external SPI Flash. Upon power-on boot up, the bootloader configures the peripherals and GSRD building blocks such as UART, GPIO, I2C, SGDMA, 1G TSE MAC, SGMII PCS, LPDDR4 and QSPI Controller.

- The bootloader loads the bitstream from the SPI Flash to program the SRAM of the FPGA and fetches the respective application software (Primary) via the QSPI flash controller.

- As the application software needs to be executed from the external memory, the RISC-V module loads it into LPDDR4 Memory controller.

- This application software is stored at the beginning of the LPDDR4 Memory. After the application software is loaded, the RISC-V CPU calculates the CRC of the application code in LPDDR4.

- The calculated LPDDR4 CRC is compared with the original CRC, that is a part of SPI Flash.

- If the condition matches, the RISC-V CPU jumps to FreeRTOS execution from LPDDR4 memory

- If the condition mismatches, the RISC-V CPU issues a FPGA REFRESH command to load the Golden bitstream and application software from SPI Flash.

- Upon the execution of the correct Primary or Golden application software from LPDDR4, the building blocks mentioned earlier are up and running with their associated drivers. For example, if any Ethernet data is expected to arrive, the RISC-V CPU sets up the SGDMA IP accordingly with address, data length and other configuration modes to successfully route the incoming Ethernet packets.

- When the Ethernet frame is received by the TSE MAC IP, it forwards it to SGDMA to transfer the data to its destination based on parameters set. The endpoint in this case is the main memory LPDDR4.

- You can also choose to store the data into another system memory based on SGDMA configuration.

- For outgoing data, the data is fetched from a location inside LPDDR4, and SGDMA transfers the data to TSE MAC for transmission outside the FPGA.

- When no data activity occurs over Ethernet, the RISC-V CPU continues running its tasks in the usual manner based on the loaded software execution.

Figure 7.1. GSRD Boot-Up Sequence

## 7.2. Prerequisites

The following sections show the hardware and software requirements to execute the GSRD demonstration.

### 7.2.1. Software Requirements

- Lattice Propel 2024.1 Package – contains both Lattice Propel SDK and Lattice Propel Builder

- Download here: [Lattice Propel 2024.1](#)

- Lattice Radiant 2024.1.1 Package – contains IP Packager, Radiant Software, QuestaSim, and Programmer

- Download here: [Lattice Radiant 2024.1.1](#)

- Lattice Propel 2024.1 Patch for Avant-AT-E Golden System Reference Design

- Download here: [Downloadable Software tab in the GHRD/GSRD Reference Design](#)

### 7.2.2. Avant-AT-E Requirements

#### 7.2.2.1. Hardware Needed

The section describes the hardware needed to run the GSRD demonstration.

- Lattice Avant-E70 ES1 Evaluation Board

- USB Type-A UART cable for programming the bitstream, application software and proper terminal prints

- Electrical Ethernet FMC daughter card for Ethernet connection over RGMII

- To purchase the daughter card, go to <https://ethernetfmc.com/> and select the part number **OP031-1V8**.

- Ethernet cable to connect one of the Ethernet ports on FMC board to the Host PC

- 12 V power adapter for board power

#### 7.2.2.2. Hardware Setup

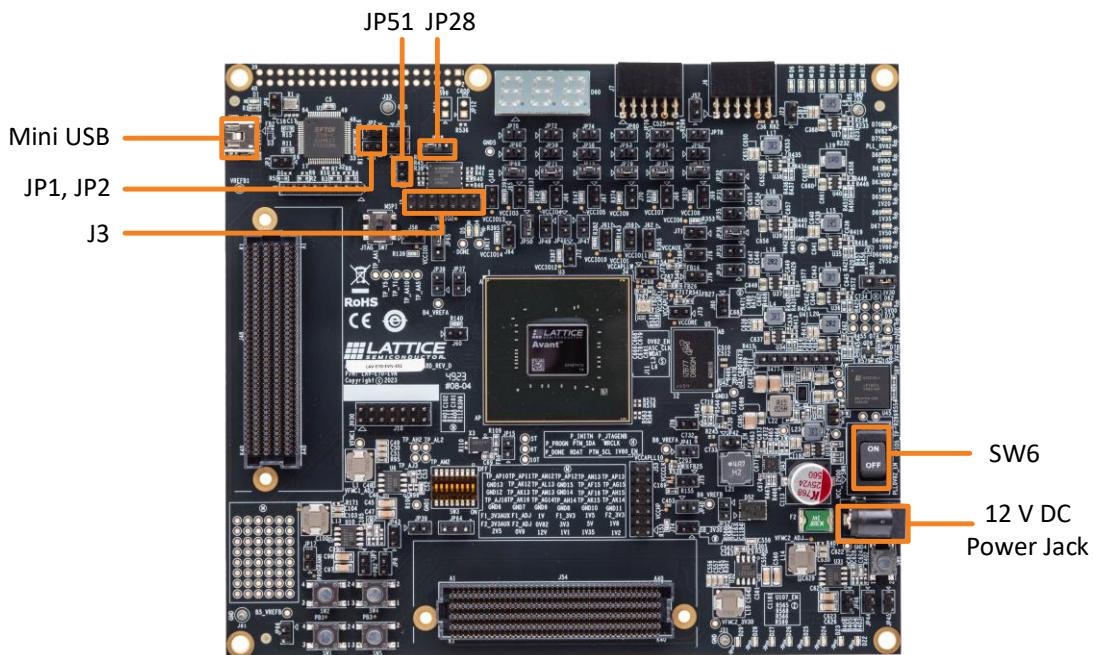

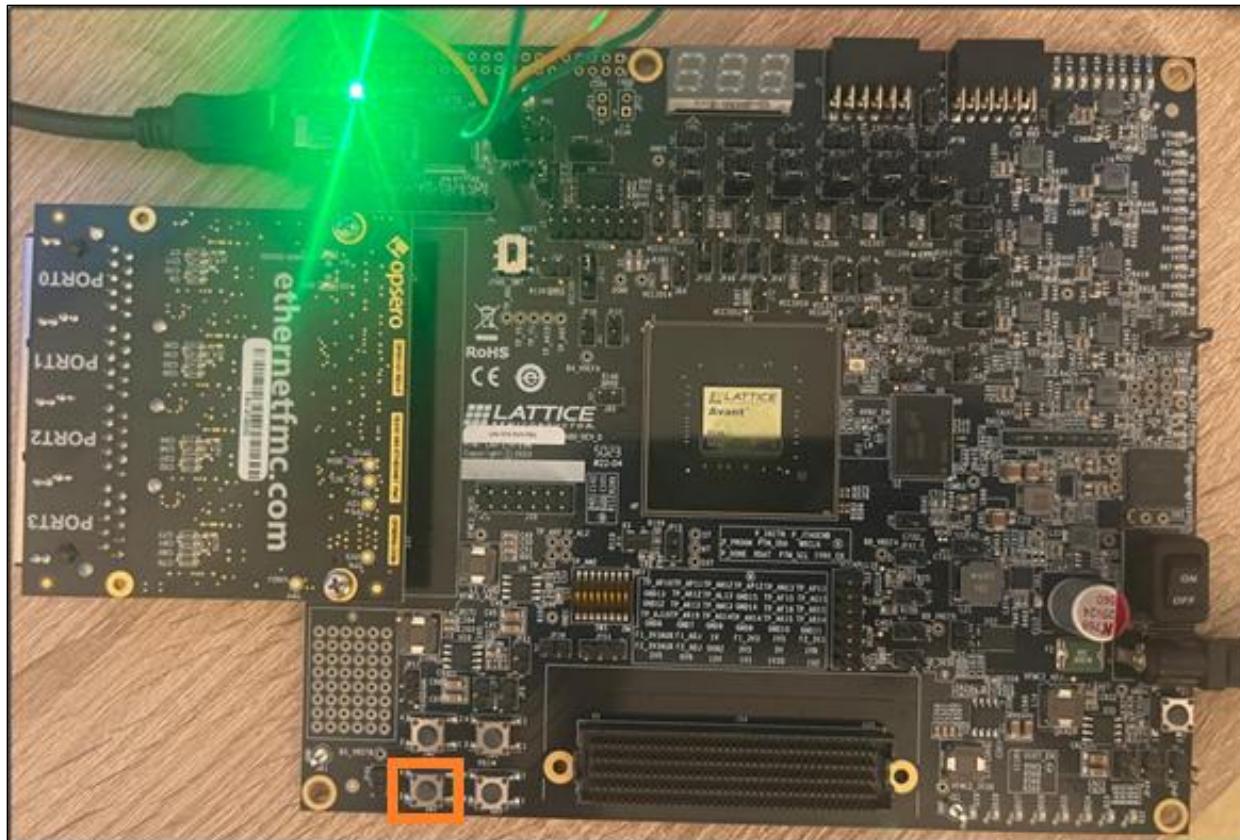

This section provides the procedure for setting up the Avant-E70 ES1 board, shown in [Figure 7.2](#).

Figure 7.2 .Avant-AT-E70 Evaluation Board

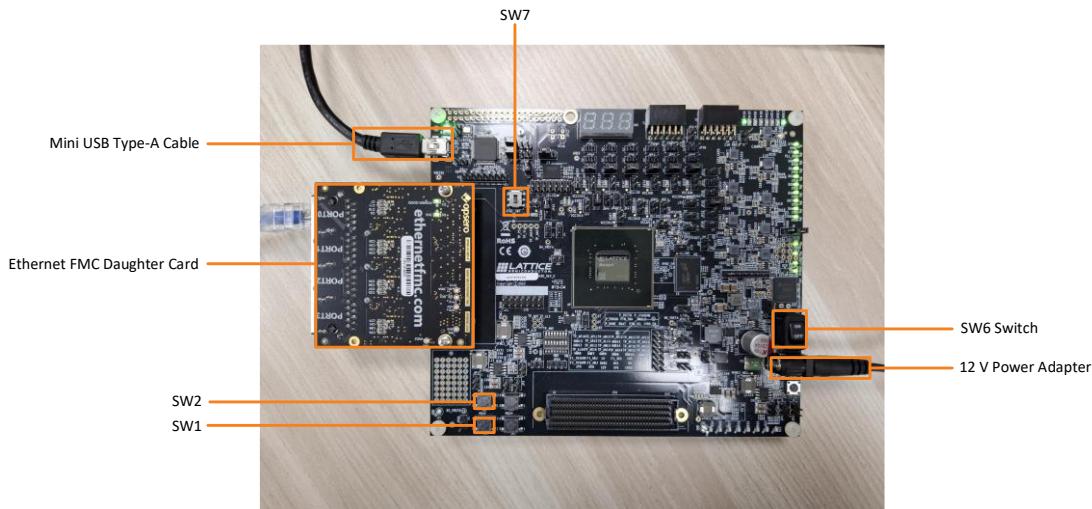

Figure 7.3. Ethernet PHY FMC Card

Figure 7.4. Connections and Buttons needed for Demonstration

To setup the Lattice Avant-AT-E board for GSRD demonstration:

1. Connect the 12 V power adapter to J50.

2. Connect the Mini-USB Type-A cable from PC to J2.

3. Connect jumpers on Pin 1 and Pin 2 on both JP1 and JP2 switches to enable UART.

4. Align and carefully connect the Ethernet FMC daughter card onto J48 connector.

5. Connect the Ethernet RJ45 cable from the host PC cable to the Port0 of FMC card.

6. For FPGA executables programming, use SW7 in JTAG mode. Once programmed, switch to MSPI.

7. Turn on the SW6 switch.

8. SW1 is the FPGA Reset pushbutton to reset the GSRD design.

9. SW2 is the PROGRAMN pushbutton to switch between Primary and Golden GSRD manually.

#### 7.2.2.3. Executables

This section provides the directory structure, file names and locations of the executables (SPI Flash) required for running the GSRD demonstration.

- Download the design package from the Lattice Semiconductor website.

- Go to *Design File* in the [GHRD/GSRD Demonstration](#), download the Avant-AT-E Golden System Reference Design and Demo V1.0 – Bitstream file.

- Unzip the .zip file to your local directory, for example to <C:\user\_workspace>.

- The extracted directory has the following executables listed in [Table 7.1](#).

**Table 7.1. Executable Files for Winbond Flash**

| File Description                                 | File Name              | Starting Address in SPI Flash |

|--------------------------------------------------|------------------------|-------------------------------|

| Primary Software with CRC                        | c_primary_appcrc.bin   | 0x028A 0000                   |

| Primary Software without CRC                     | c_primary_app.bin      | 0x028A 0000                   |

| Primary FPGA Bitstream                           | soc_primary_system.bit | 0x0000 0000                   |

| Golden Software with CRC                         | c_golden_appcrc.bin    | 0x0280 0000                   |

| Golden Software without CRC                      | c_golden_app.bin       | 0x0280 0000                   |

| Golden FPGA Bitstream                            | soc_golden_system.bit  | 0x0000 0000                   |

| Multi-Boot MCS File (Golden + Primary Bitstream) | multiboot_system.mcs   | 0x0000 0000                   |

## 7.3. Implementing the GHRD/GSRD Demo

This section describes the procedure for running the GSRD/GHRD demo using the pre-built executables and binary files in the design package.

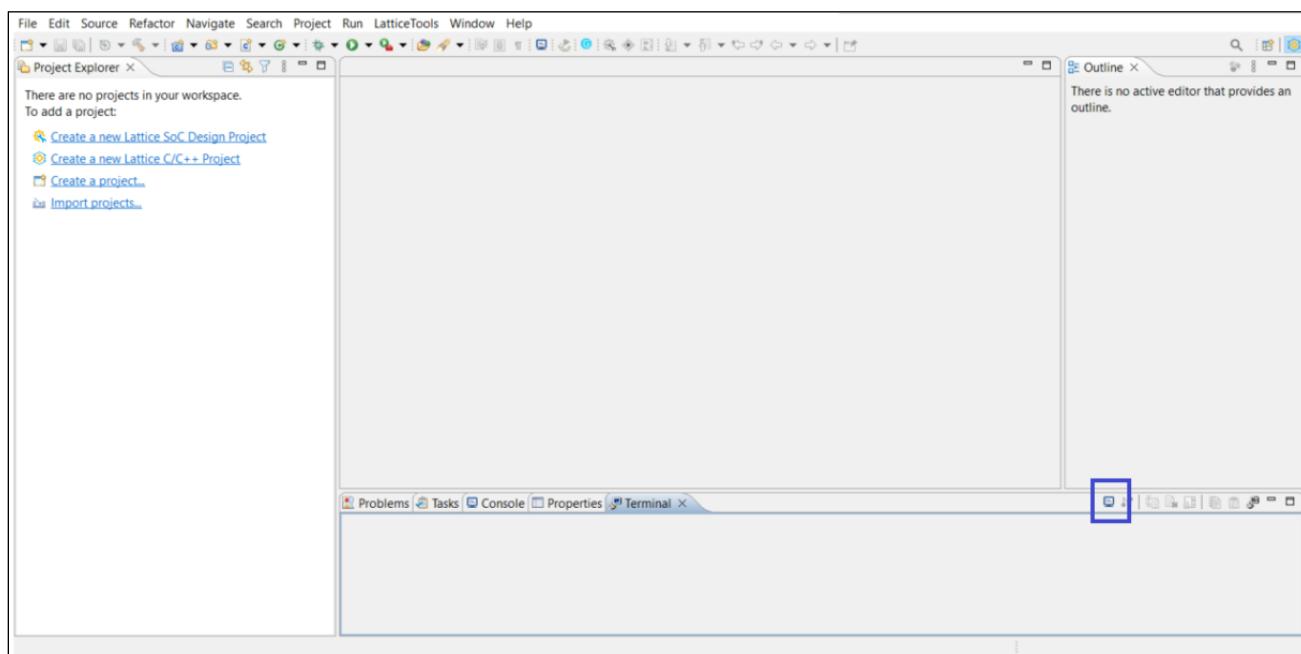

### 7.3.1. Setting up the UART Terminal

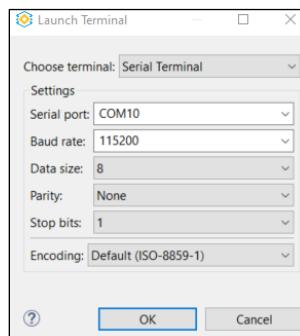

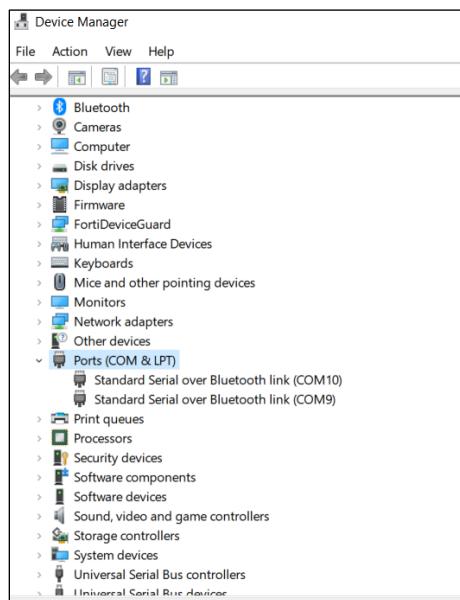

The software code during the GSRD demonstration displays messages on the terminal through the UART interface.

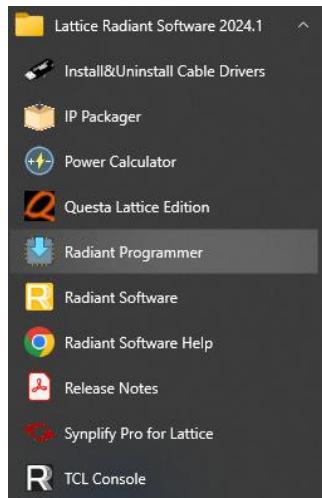

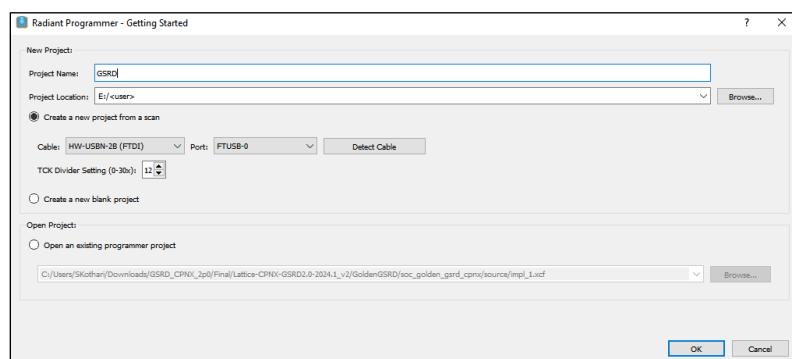

To setup the UART terminal: