# AHB-Lite to AXI4 Bridge IP

IP Version: 1.4.0

## User Guide

FPGA-IPUG-02242-1.4

December 2025

## Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Inclusive Language

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language [FAQ 6878](#) for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## Contents

|                                                |    |

|------------------------------------------------|----|

| Contents.....                                  | 3  |

| Acronyms in This Document .....                | 6  |

| 1. Introduction .....                          | 7  |

| 1.1. Overview of the IP .....                  | 7  |

| 1.2. Quick Facts .....                         | 7  |

| 1.3. IP Support Summary.....                   | 7  |

| 1.4. Features.....                             | 8  |

| 1.5. Licensing and Ordering Information.....   | 8  |

| 1.6. Minimum Device Requirements.....          | 8  |

| 1.7. Naming Conventions .....                  | 8  |

| 1.7.1. Signal Names .....                      | 8  |

| 2. Functional Description.....                 | 9  |

| 2.1. Overview .....                            | 9  |

| 2.2. Interface Description.....                | 9  |

| 2.3. Attributes .....                          | 13 |

| 3. Timing Diagram.....                         | 15 |

| 3.1. Write Operation .....                     | 15 |

| 3.1.1. Write Data Bus Pipeline Disabled .....  | 15 |

| 3.1.2. Write Data Bus Pipeline Enabled.....    | 16 |

| 3.2. Read Operation .....                      | 17 |

| 3.2.1. Read Data Bus Pipeline Disabled .....   | 17 |

| 3.2.2. Read Data Bus Pipeline Enabled.....     | 18 |

| 4. Designing with the IP .....                 | 19 |

| 4.1. Generating and Instantiating the IP ..... | 19 |

| 4.1.1. Generated Files and Structure.....      | 21 |

| Appendix A. Resource Utilization .....         | 22 |

| References .....                               | 24 |

| Technical Support Assistance .....             | 25 |

| Revision History .....                         | 26 |

## Figures

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| Figure 2.1. AHB-Lite to AXI4 Bridge .....                                               | 9  |

| Figure 2.2. IP Core Block Diagram.....                                                  | 10 |

| Figure 3.1. Timing Diagram of Write Transfer with Data Bus Pipeline Disabled.....       | 15 |

| Figure 3.2. Timing Diagram of Write Transfer with Write Data Bus Pipeline Enabled ..... | 16 |

| Figure 3.3. Timing Diagram of Read Transfer with Read Data Bus Pipeline Disabled.....   | 17 |

| Figure 3.4. Timing Diagram of Read Transfer with Read Data Bus Pipeline Enabled .....   | 18 |

| Figure 4.1. Enter Component Name .....                                                  | 19 |

| Figure 4.2. IP Configuration .....                                                      | 20 |

| Figure 4.3. Check Generated Result.....                                                 | 20 |

| Figure 4.4. Schematic Window .....                                                      | 21 |

## Tables

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| Table 1.1. Summary .....                                                        | 7  |

| Table 1.2. AHB-Lite to AXI4 IP Support Readiness .....                          | 7  |

| Table 2.1. Signal Description.....                                              | 11 |

| Table 2.2. IP Parameters.....                                                   | 13 |

| Table 4.1. Generated Files .....                                                | 21 |

| Table A.1. Estimated Device Resource Utilization on Lattice Avant Devices ..... | 22 |

| Table A.2. Estimated Device Resource Utilization on CertusPro-NX Devices .....  | 22 |

## Acronyms in This Document

A list of acronyms used in this document.

| Acronym | Definition                                 |

|---------|--------------------------------------------|

| AMBA    | Advanced Micro-controller Bus Architecture |

| AXI     | Advanced Extensible Interface Bus          |

| AHB     | Advanced High-performance Bus              |

| FPGA    | Field Programmable Gate Array              |

| RTL     | Register Transfer Level                    |

# 1. Introduction

## 1.1. Overview of the IP

The Lattice Semiconductor AHB-Lite to AXI4 Bridge provides an interface between a single high speed AHB-Lite manager (compliant to AMBA 3 AHB-Lite Protocol Specification) and a AXI4 subordinate (compliant to AMBA AXI and ACE Protocol Specification Version H.c).

## 1.2. Quick Facts

The design is implemented in Verilog HDL. The IP can be configured and generated using the Lattice Propel™ Builder and implemented within the Lattice Radiant™ software.

**Table 1.1. Summary**

|                             |                                                     |                                                                                                                                                                                                                                      |

|-----------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>IP Requirements</b>      | Supported Devices                                   | CrossLink™-NX, Certus™-NX, MachXO5™-NX, CertusPro™-NX, Lattice Avant™, Certus-N2, LatticeECP3™, ECP5™                                                                                                                                |

|                             | IP Changes <sup>1</sup>                             | For a list of changes to the IP, refer to the <a href="#">AHB-Lite to AXI4 Bridge IP Release Notes (FPGA-RN-02048)</a> .                                                                                                             |

| <b>Resource Utilization</b> | Supported User Interface                            | AHB-Lite and AXI4                                                                                                                                                                                                                    |

| <b>Design Tool Support</b>  | IP Configuration and Generation <sup>2</sup>        | IP Core v1.1.0 – Lattice Propel Builder software2024.1<br>IP Core v1.2.0 – Lattice Propel Builder software2024.2<br>IP Core v1.3.0 – Lattice Propel Builder software2025.1<br>IP Core v1.4.0 – Lattice Propel Builder software2025.2 |

|                             | IP Implementation (Synthesis, Map, Place and Route) | LatticeECP3 and ECP5 devices: Lattice Diamond software<br>Other devices: Lattice Radiant software                                                                                                                                    |

**Notes:**

1. In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

2. IP Configuration and Generation indicates the IP version release coinciding with the software version release. Check the software for IP version compatibility with earlier or later software versions.

## 1.3. IP Support Summary

**Table 1.2. AHB-Lite to AXI4 IP Support Readiness**

| Device Family | Radiant/Diamond Timing Model | Hardware Validated |

|---------------|------------------------------|--------------------|

| CrossLink-NX  | Final                        | No                 |

| Certus-NX     | Final                        | No                 |

| Certus-N2     | Preliminary                  | No                 |

| MachXO5-NX    | Preliminary                  | No                 |

| CertusPro-NX  | Final                        | No                 |

| Lattice Avant | Preliminary                  | No                 |

| LatticeECP3   | Final                        | No                 |

| ECP5          | Final                        | No                 |

## 1.4. Features

The key features of the AHB-Lite to AXI4 Bridge includes:

- Supports configurable data bus width: 8, 16, 32, 64, 128, 256, 512, and 1024 bits.

- Supports configurable address width: 11 to 32 bits.

- Supports configurable AXI4 ID bus width (1 to 11 bits) so that the width can be matched with subordinate's ID bus width, but the ID value for this bridge will be always tied to 0 since AHB-Lite does not have the concept of ID.

- Supports basic and burst transfer. Single and indefinite length increment transfer on AHB-Lite are converted to INCR burst with length=0 on AXI4.

- Supports narrow transfer where the requested transfer size can be less than data bus width.

- Supports Secure Access at AXI4 interface.

- Supports optional timeout indicator if there is no response from AXI4 subordinate within certain timeframe.

- Supports write/read data bus pipeline for relaxing timing critical path.

Some limitations of AHB-Lite to AXI4 Bridge are listed below:

- Burst transfer only supports 4, 8 and 16 beats as these are bounded by AHB-Lite specification.

- Fixed burst transfer, out of order transaction, and exclusive accesses on AXI4 interface bus are not supported.

- Does not support AXI4 QOS (Quality of Service), Region identifier, and User Defined signals on AXI4 interface bus.

- AXI4 and AHB-Lite interface are expected to have the same address and data bus width, as well as operating at the same clock domain.

- AHB-Lite locked transfer request will be ignored as this feature is not supported on AXI4.

## 1.5. Licensing and Ordering Information

The AHB-Lite to AXI4 Bridge IP is provided at no additional cost with Lattice Propel Builder.

## 1.6. Minimum Device Requirements

There is no minimum device requirements for this IP and can be used on any ECP, Nexus, or Avant device family.

## 1.7. Naming Conventions

### 1.7.1. Signal Names

- $_n$  are active low (asserted when value is logic 0)

- $_i$  are input signals

- $_o$  are output signals

## 2. Functional Description

### 2.1. Overview

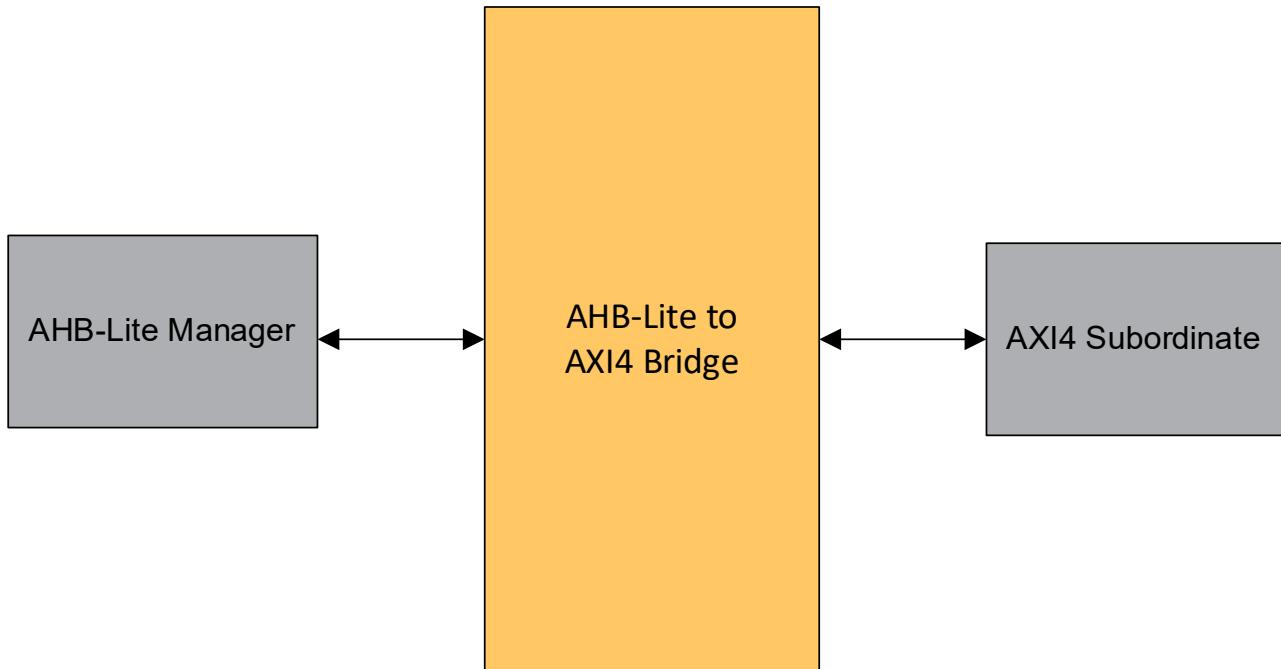

The AHB-Lite to AXI4 Bridge is used for interfacing one AHB-Lite Manager and one AXI4 Subordinate. The read and write transfers on AHB-Lite side are translated into equivalent AXI4 transaction to be compatible with the subordinate. Some additional wait states are expected on the AHB-Lite bus due to the translation operation and pipeline in the bridge.

Figure 2.1. AHB-Lite to AXI4 Bridge

### 2.2. Interface Description

Figure 2.2 below shows the interface diagram of the AHB-Lite to AXI4 Bridge IP. The diagram shows all the available ports on the IP core.

Figure 2.2. IP Core Block Diagram

**Table 2.1. Signal Description**

| Pin Name                           | Direction | Width (Bits) | Description                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Clock and Reset</b>             |           |              |                                                                                                                                                                                                                                                                                                                                                                          |

| clk_i                              | In        | 1            | AHB-Lite to AXI4 bridge clock.                                                                                                                                                                                                                                                                                                                                           |

| resetn_i                           | In        | 1            | Active low reset. It is recommended to share the same reset source as the AHB-Lite manager so that HREADY signals are sync correctly.                                                                                                                                                                                                                                    |

| <b>AHB-Lite Interface (AHBL_S)</b> |           |              |                                                                                                                                                                                                                                                                                                                                                                          |

| ahb_s_hsel_i                       | In        | 1            | AHB-Lite subordinate select.                                                                                                                                                                                                                                                                                                                                             |

| ahb_s_haddr_i                      | In        | M_ADDR_WIDTH | AHB-Lite 32-bit system address bus                                                                                                                                                                                                                                                                                                                                       |

| ahb_s_hwrite_i                     | In        | 1            | Indicates the transfer direction. This signal indicates an AHB-Lite write access when High and an AHB-Lite read access when Low.                                                                                                                                                                                                                                         |

| ahb_s_hwdata_i                     | In        | DATA_WIDTH   | Write data. The write data bus transfers data from the manager to the subordinates during write operations. The width of the port is configurable. Refer to <a href="#">Table 2.2</a> .                                                                                                                                                                                  |

| ahb_s_hsize_i                      | In        | 3            | Indicates AHB-Lite size of transfer.                                                                                                                                                                                                                                                                                                                                     |

| ahb_s_htrans_i                     | In        | 2            | AHB-Lite transfer type, which can be NONSEQ, SEQ, IDLE, or BUSY.                                                                                                                                                                                                                                                                                                         |

| ahb_s_hprot_i                      | In        | 4            | Protection type. Indicates if it is a data access or instruction access transaction. It also indicates if this is a privileged mode or user mode.                                                                                                                                                                                                                        |

| ahb_s_hmastlock_i                  | In        | 1            | Indicates that it is a locked sequence of transfers. This signal is unused internally.                                                                                                                                                                                                                                                                                   |

| ahb_s_hburst_i                     | In        | 3            | AHB-Lite burst type. The burst type indicates if the transfer is a single transfer or forms part of a burst. The burst can be incrementing or wrapping.                                                                                                                                                                                                                  |

| ahb_s_hready_i                     | In        | 1            | Ready signal from AHB-Lite manager to indicate that the previous transfer is completed. This signal can be connected to <i>ahb_s_hreadyout_o</i> if the AHB-Lite manager does not have a HREADY output port.                                                                                                                                                             |

| ahb_s_hreadyout_o                  | Out       | 1            | Ready signal to AHB-Lite manager to indicate that the previous transfer is completed.                                                                                                                                                                                                                                                                                    |

| ahb_s_hrdata_o                     | Out       | DATA_WIDTH   | AHB-Lite read data to the manager. Width of the port is configurable.                                                                                                                                                                                                                                                                                                    |

| ahb_s_hresp_o                      | Out       | 1            | Transfer response. When Low, it indicates that the transfer status is OKAY. When High, it indicates that the transfer status is an ERROR.<br><br>SLVERR and DECERR on AXI4 bus will be translated to error response on AHB-Lite bus. If the returning AXI4 ID does not match with the outgoing AXI4 ID (which is always 0), an error response will be triggered as well. |

| <b>AXI4 Interface (AXI4_M)</b>     |           |              |                                                                                                                                                                                                                                                                                                                                                                          |

| axi_m_awid_o                       | Out       | AXI_ID_WIDTH | AXI4 write ID. This output signal will always be tied to 0.                                                                                                                                                                                                                                                                                                              |

| axi_m_awaddr_o                     | Out       | M_ADDR_WIDTH | Write address. In a write burst transaction, this signal holds the address of the first transfer.                                                                                                                                                                                                                                                                        |

| axi_m_awlen_o                      | Out       | 8            | Burst length. This indicates the number of beats per AXI4 burst.                                                                                                                                                                                                                                                                                                         |

| axi_m_awsize_o                     | Out       | 3            | Burst size. Indicates the size of each transfer in the burst.                                                                                                                                                                                                                                                                                                            |

| axi_m_awburst_o                    | Out       | 2            | Burst type. The burst type and the size information. Determines how the address of each transfer within the burst is calculated.                                                                                                                                                                                                                                         |

| axi_m_awlock_o                     | Out       | 1            | Lock Type. Only normal access type is supported as exclusive access is not supported on AHB-Lite manager.                                                                                                                                                                                                                                                                |

| Pin Name         | Direction | Width (Bits) | Description                                                                                                                                                                                                                                                           |

|------------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| axi_m_awcache_o  | Out       | 4            | Memory type. Only 4 types of encoding are supported which are: device non-bufferable, device bufferable, normal non-cacheable non-bufferable, normal non-cacheable bufferable are supported.<br><br>The rest are not supported as they are not included in AHB-Lite.  |

| axi_m_awprot_o   | Out       | 3            | Access permission signals to protect against illegal transaction. Two protection encoding are supported which are Privileged/Unprivileged access, Data/Instruction access.<br><br>Secure and non-secure access is not supported as this is not supported on AHB-Lite. |

| axi_m_awqos_o    | Out       | 4            | QoS identifier sent for each transaction. Not supported and will always be tied to 0.                                                                                                                                                                                 |

| axi_m_awregion_o | Out       | 4            | Region identifier sent for each transaction. Not supported and will always be tied to 0.                                                                                                                                                                              |

| axi_m_awvalid_o  | Out       | 1            | Write address valid. Indicates that the address and control bits on the channel are valid.                                                                                                                                                                            |

| axi_m_awready_i  | In        | 1            | Write address ready. Indicates the readiness of the subordinate. When asserted, the subordinate is ready for a new address.                                                                                                                                           |

| axi_m_wdata_o    | Out       | DATA_WIDTH   | Write data.                                                                                                                                                                                                                                                           |

| axi_m_wstrb_o    | Out       | DATA_WIDTH   | Write strobes. This signal indicates which eight bits of the write data bus are valid. This signal will be tied to all 1's as the Write Strobe feature is not supported in AHB-Lite.                                                                                  |

| axi_m_wlast_o    | Out       | 1            | Write last. This signal indicates if the current transfer is the last data transfer in a write transaction.                                                                                                                                                           |

| axi_m_wvalid_o   | Out       | 1            | Write valid. This signal indicates data and strobes on the bus are valid.                                                                                                                                                                                             |

| axi_m_wready_i   | In        | 1            | Write data ready. Indicates the readiness of the subordinate. When asserted, the subordinate is ready for new data.                                                                                                                                                   |

| axi_m_bid_i      | In        | AXI_ID_WIDTH | Write response ID from subordinate.                                                                                                                                                                                                                                   |

| axi_m_bresp_i    | In        | 2            | Write response which indicates the status of a write transaction.                                                                                                                                                                                                     |

| axi_m_bvalid_i   | In        | 1            | Write response valid. When asserted, the subordinate is signaling a valid write response.                                                                                                                                                                             |

| axi_m_bready_o   | Out       | 1            | Response ready. Indicates that the manager is now ready to accept a write response.                                                                                                                                                                                   |

| axi_m_arid_o     | Out       | AXI_ID_WIDTH | AXI4 read address ID. This output signal will always be tied to 0.                                                                                                                                                                                                    |

| axi_m_araddr_o   | In        | M_ADDR_WIDTH | Read address. In a read burst transaction, this signal holds the address of the first transfer.                                                                                                                                                                       |

| axi_m_arlen_o    | Out       | 8            | AXI4 read burst length. This indicates the number of beats per AXI4 burst.                                                                                                                                                                                            |

| axi_m_arsize_o   | Out       | 3            | Burst size. This signal indicates the size of each transfer in the burst.                                                                                                                                                                                             |

| axi_m_arburst_o  | Out       | 2            | Burst type. The burst type and the size information. Determines how the address of each transfer within the burst is calculated.                                                                                                                                      |

| axi_m_arlock_o   | Out       | 1            | Lock Type. Only normal access type is supported as exclusive access is not supported on AHB-Lite manager.                                                                                                                                                             |

| axi_m_arcache_o  | Out       | 4            | Memory type. Only 4 types of encoding are supported which are: device non-bufferable, device bufferable, normal non-cacheable non-bufferable, normal non-cacheable bufferable are supported.<br><br>The rest are not supported as they are not included in AHB-Lite.  |

| Pin Name                                                             | Direction | Width (Bits) | Description                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| axi_m_arprot_o                                                       | Out       | 3            | Access permission signals to protect against illegal transaction. Two protection encoding are supported which are Privileged/Unprivileged access, Data/Instruction access.<br><br>Secure and non-secure access is not supported as this is not supported on AHB-Lite.         |

| axi_m_arqos_o                                                        | Out       | 4            | QoS identifier sent for each transaction. Not supported and will always be tied to 0.                                                                                                                                                                                         |

| axi_m_arregion_o                                                     | Out       | 4            | Region identifier sent for each transaction. Not supported and will always be tied to 0.                                                                                                                                                                                      |

| axi_m_arvalid_o                                                      | Out       | 1            | Read address valid. Indicates that the address and control information is valid.                                                                                                                                                                                              |

| axi_m_arready_i                                                      | In        | 1            | Read address ready. Indicates the readiness of the subordinate. When asserted, the subordinate is ready for a new address.                                                                                                                                                    |

| axi_m_rid_i                                                          | In        | AXI_ID_WIDTH | Identification tag for read data and response.                                                                                                                                                                                                                                |

| axi_m_rdata_i                                                        | In        | DATA_WIDTH   | Read data.                                                                                                                                                                                                                                                                    |

| axi_m_rresp_i                                                        | In        | 2            | Read response. Indicates the read transaction status.                                                                                                                                                                                                                         |

| axi_m_rlast_i                                                        | In        | 1            | Read last. This signal indicates if the current transfer is the last data transfer in a read transaction.                                                                                                                                                                     |

| axi_m_rvalid_i                                                       | In        | 1            | Read valid. Indicates that the read data channel signals are valid.                                                                                                                                                                                                           |

| axi_m_ready_o                                                        | Out       | 1            | Read ready. Indicates the readiness of the manager. When asserted, the manager is ready to receive data.                                                                                                                                                                      |

| <b>Optional interface (enabled when AXI4 Timeout counter &gt; 0)</b> |           |              |                                                                                                                                                                                                                                                                               |

| axi_timeout_o                                                        | Out       | 1            | AXI4 timeout signal. Asserted when AXI4 subordinate does not response within the threshold set for that option.<br><br>When this signal is asserted, it is recommended to reset the entire AXI4 and AHB-Lite bus to recover the bus as the AXI4 subordinate is probably hung. |

## 2.3. Attributes

Table 2.2 below provides the list of user-configurable attributes for AHB-Lite to AXI4 Bridge. The attribute values are configured using the IP Core Block Wizard in the Propel Builder software.

**Table 2.2. IP Parameters**

| Attribute Name              | Attribute ID      | Selectable Values                  | Default | Dependency on Other Attributes | Description                                                                                                                        |

|-----------------------------|-------------------|------------------------------------|---------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| <b>General Settings tab</b> |                   |                                    |         |                                |                                                                                                                                    |

| Address Width               | M_ADDR_WIDTH      | 11-32                              | 32      | —                              | Specifies the bit width of AHB-Lite and AXI4 address bus signals.                                                                  |

| Data Bus width              | DATA_WIDTH        | 8, 16, 32, 64, 128, 256, 512, 1024 | 32      | —                              | Specifies the bit width of AHB-Lite and AXI4 data bus signals.                                                                     |

| AXI Transaction ID width    | AXI_ID_WIDTH      | 1-11                               | 4       | —                              | Specifies the bit width of AXI4 Transaction ID signals. The ID value will always be set to 0.                                      |

| AXI Secure access           | AXI_SECURE_ACCESS | 0,1                                | 0       | —                              | Specifies the support for secure access at AXI4 side. Enabling this parameter will enable secure access for all AXI4 transactions. |

| Attribute Name                   | Attribute ID    | Selectable Values | Default | Dependency on Other Attributes | Description                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|-----------------|-------------------|---------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>General Settings tab</b>      |                 |                   |         |                                |                                                                                                                                                                                                                                                                                                                                         |

| AXI Timeout counter <sup>1</sup> | AXI_TIMEOUT     | 0,16,32, 64,128   | 0       | —                              | <p>Specifies the number of clock cycles to wait for AXI4 subordinate to response and assert timeout signal if it is not responding.</p> <p>e.g:</p> <ul style="list-style-type: none"> <li>• 0 – no timeout counter will be implemented.</li> <li>• 16 – Timeout if there is no response from bridge within 16 clock cycles.</li> </ul> |

| Read Data bus Pipeline Enable    | RDDATA_PIPELINE | 0,1               | 0       | —                              | Enable this parameter to add a pipeline stage to Read Data bus. Useful for relaxing the timing critical path if there is any violated path detected on this bus.                                                                                                                                                                        |

| Write Data bus Pipeline Enable   | WRDATA_PIPELINE | 0,1               | 0       | —                              | Enable this parameter to add a pipeline stage to Write Data bus. Useful for relaxing the timing critical path if there is any violated path detected on this bus.                                                                                                                                                                       |

| Narrow transfers support         | NARROW_TRANSFER | 0,1               | 0       | DATA_WIDTH > 8                 | Enable this parameter to support narrow transfer feature where the requested transfer size can be less than the DATA_WIDTH selected.                                                                                                                                                                                                    |

**Note:**

1. In cases where the AW (Address Write) and W (Write Data) channels operate concurrently, the timeout counter is reset upon receipt of any valid AW or W response from AXI subordinate.

## 3. Timing Diagram

### 3.1. Write Operation

#### 3.1.1. Write Data Bus Pipeline Disabled

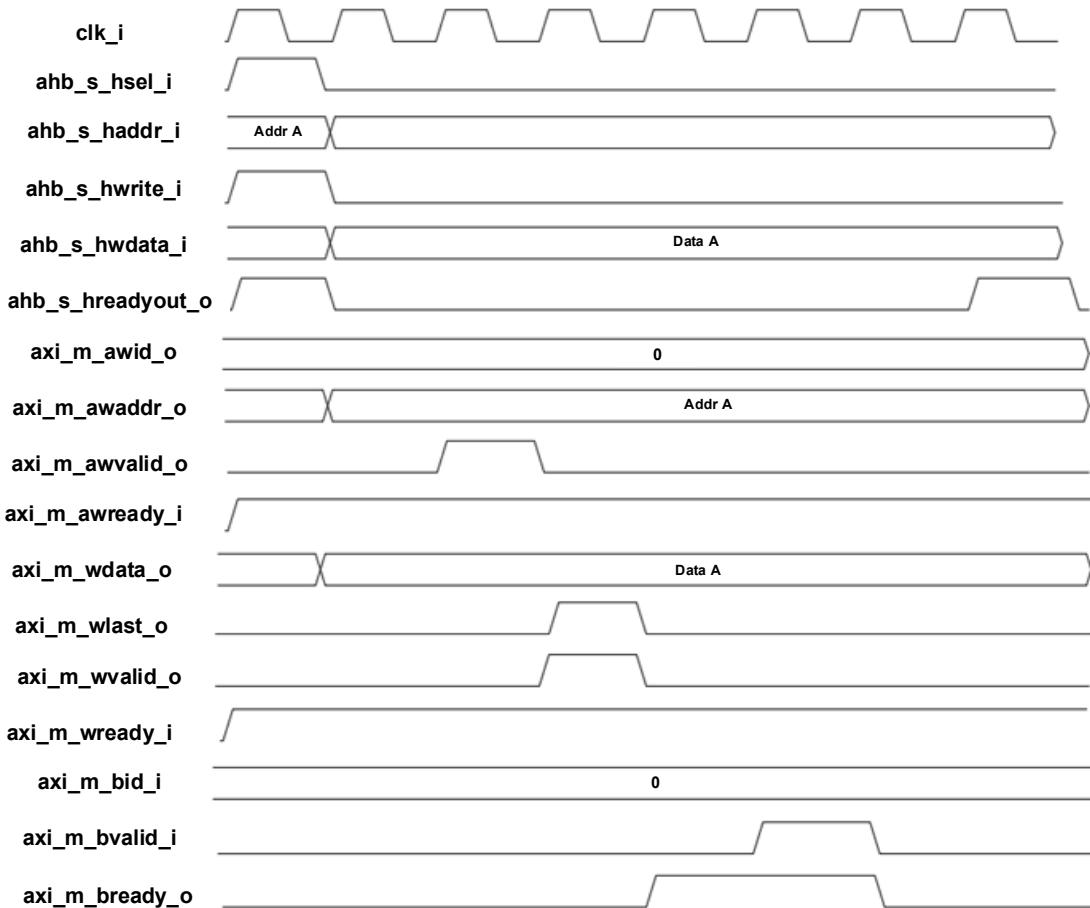

**Figure 3.1. Timing Diagram of Write Transfer with Data Bus Pipeline Disabled**

Figure 3.1 shows a basic write transfer with write data bus pipeline disabled.

1. At the first clock cycle, the AHB-Lite manager initiates a write transfer by driving the address and control signals. This is the address phase of the AHB-Lite write transfer.

2. At the 2nd clock cycle, the data phase of AHB-Lite starts and the AHB-Lite manager drives the HWDATA bus with a valid data.

3. At the 3rd clock cycle, the bridge is driving the AXI4 write address channels to start the write transfer at the AXI4 bus. The transaction is acknowledged immediately since AWREADY signal is asserted from the beginning. If it is not asserted, the AWVALID signal will be held high until the bridge sees the ready signal turns high.

4. At the 4th clock cycle, the write data channel on AXI4 are being asserted to transfer the data. The transaction is immediately being acknowledged, since WREADY signal is asserted from the beginning.

5. At the 5th clock cycle, the Bready signal at AXI4 Write response channel is asserted and waiting for the Bvalid signal to be asserted.

6. At the 6th clock cycle, the bridge sees a Bvalid signal asserted, indicating that the write transfer is complete. The Bready signal is de-asserted at this point.

7. At the 8th clock cycle, the bridge asserts the HREADYOUT signal on the AHB-Lite bus, indicating to the AHB-Lite manager that the write transfer is complete and ready for the next transfer.

### 3.1.2. Write Data Bus Pipeline Enabled

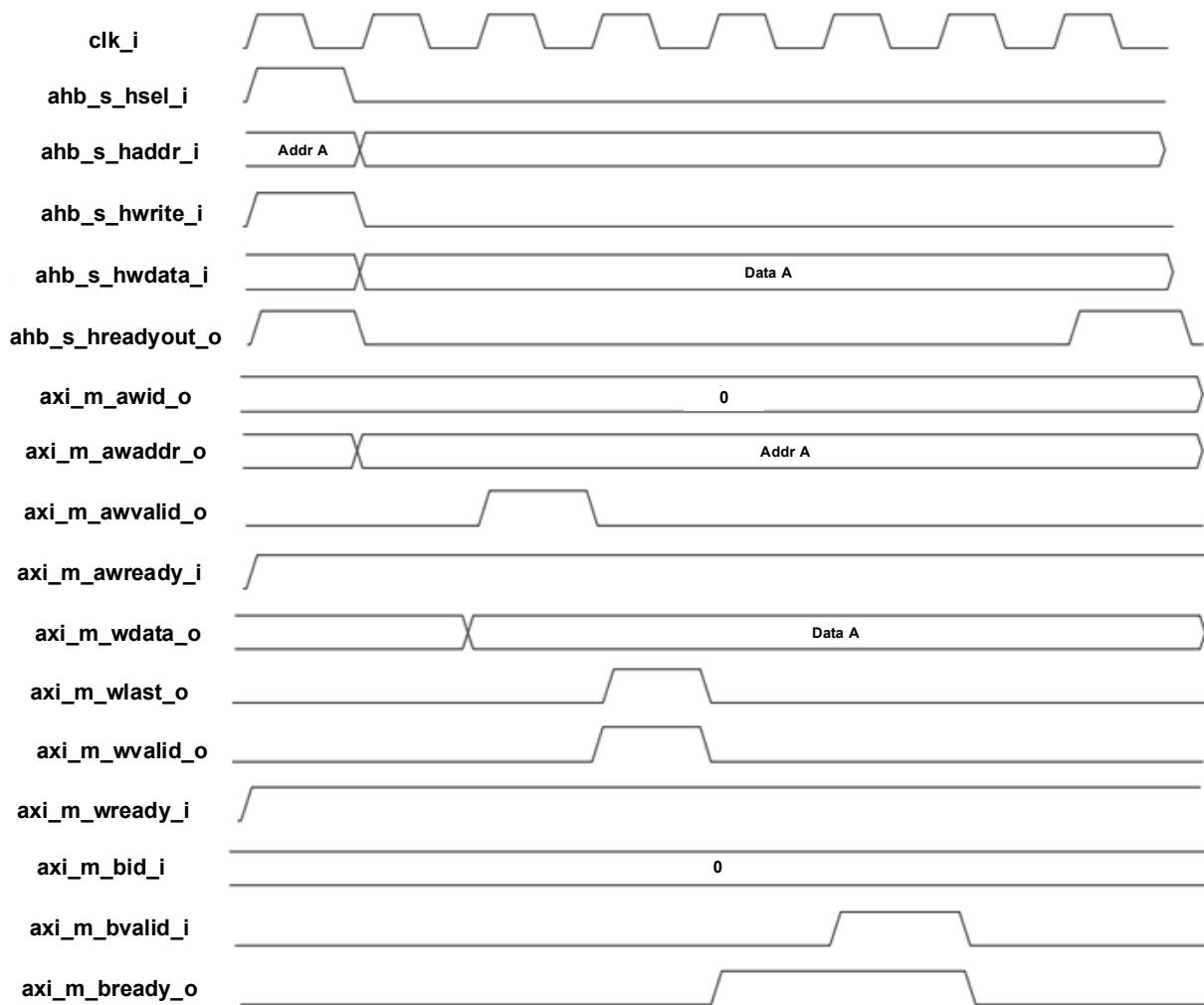

**Figure 3.2. Timing Diagram of Write Transfer with Write Data Bus Pipeline Enabled**

Figure 3.2 shows a basic write transfer with a write data bus pipeline enabled. Generally, the write operation works similar as the write transfer with a write data bus pipeline disabled. The only exception is at the 2nd clock cycle, the AXI4 WDATA signal is still not driven by valid data. The data reaches the output at 1 clock cycle later, which is at the 3rd clock cycle.

## 3.2. Read Operation

### 3.2.1. Read Data Bus Pipeline Disabled

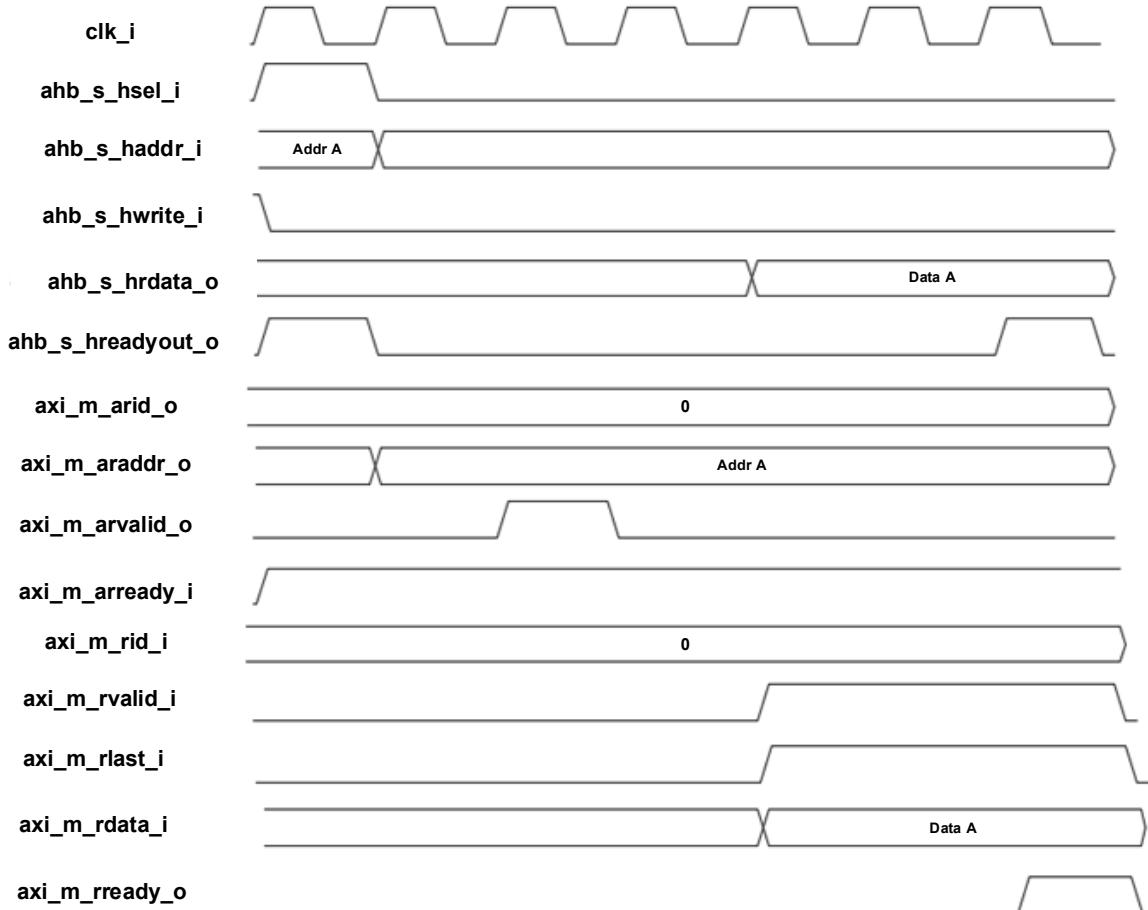

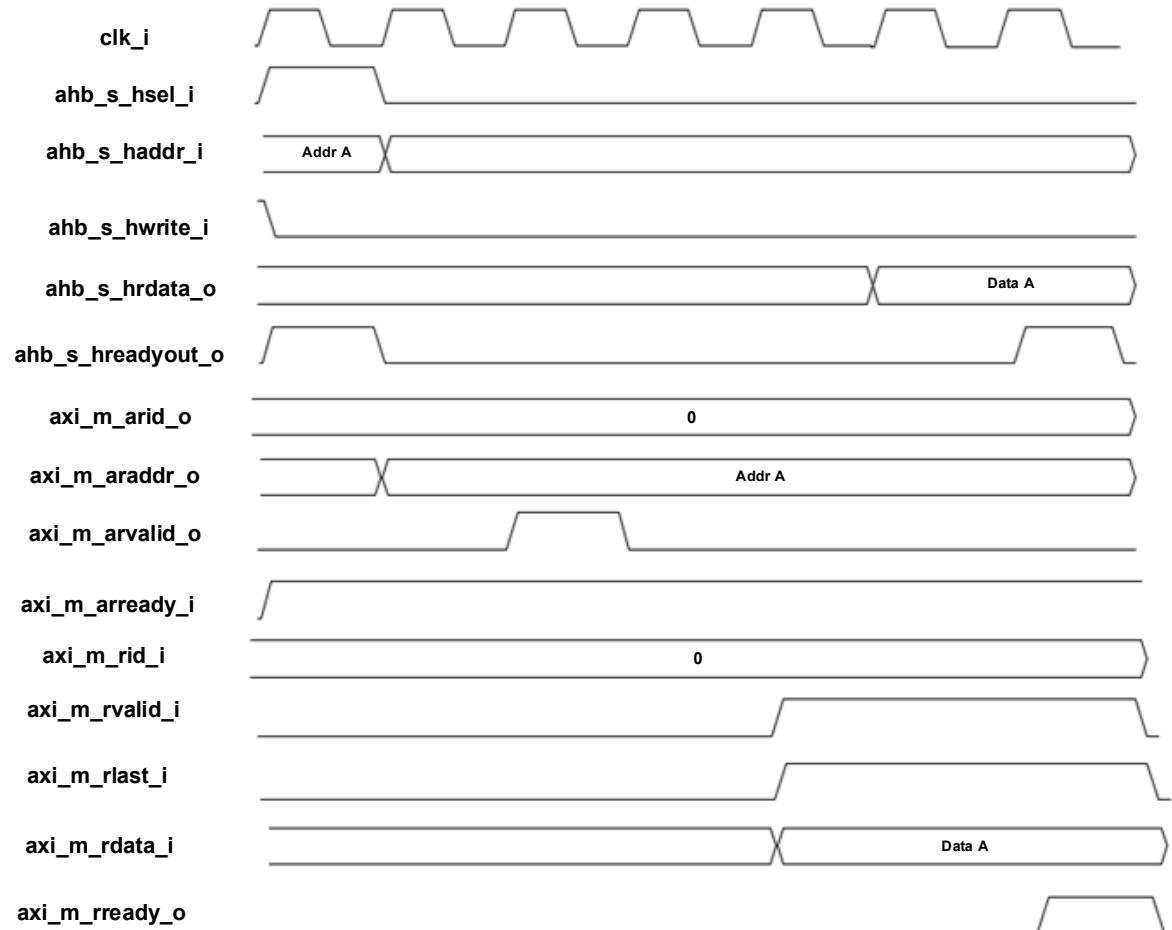

**Figure 3.3. Timing Diagram of Read Transfer with Read Data Bus Pipeline Disabled**

Figure 3.3 shows a basic read transfer with read data bus pipeline disabled.

1. At the first clock cycle, the AHB-Lite manager initiates a read transfer by driving the address and control signals. This is the address phase of the AHB-Lite read transfer.

2. At the 2nd clock cycle, the data phase of the AHB-Lite transfer starts, and the AHB-Lite manager is waiting for the valid read data.

3. At the 3rd clock cycle, the bridge starts to initiate a read transfer to the AXI4 subordinate by driving the read address channels.

4. The bridge waits for the valid read data after initiating the transfer. The read data channel returns the read data at the 5th clock cycle.

5. The Read data channel holds the valid data until the bridge indicates that the transfer is complete by asserting the RReady at the 7th clock cycle. At the same clock cycle, the HREADYOUT to the AHB-Lite manager is also asserted.

### 3.2.2. Read Data Bus Pipeline Enabled

**Figure 3.4. Timing Diagram of Read Transfer with Read Data Bus Pipeline Enabled**

Figure 3.4 shows the basic read transfer with the read data bus pipeline enabled. Generally, the read operation works similar as the read transfer with the pipeline disabled. The only exception is the HRDATA on the AHB-Lite interface is outputting the read data at the 6th clock cycle instead of the 5th clock cycle.

## 4. Designing with the IP

This section provides information on how to generate the IP Core using the Lattice Propel Builder software. For more details on the Lattice Propel software, refer to the [Lattice Propel User Guide](#).

**Note:** The screenshots provided are for reference only. Details may vary depending on the version of the IP or software being used. If there have been no significant changes to the GUI, a screenshot may reflect an earlier version of the IP.

### 4.1. Generating and Instantiating the IP

You can use the Lattice Propel software to generate this IP module along with other components required in your System-on-Chip (SoC) design. The steps below describe the procedure for generating the AHB-Lite to AXI4 Bridge IP in the Lattice Propel software.

1. Create a new Lattice Propel software project or open an existing project.

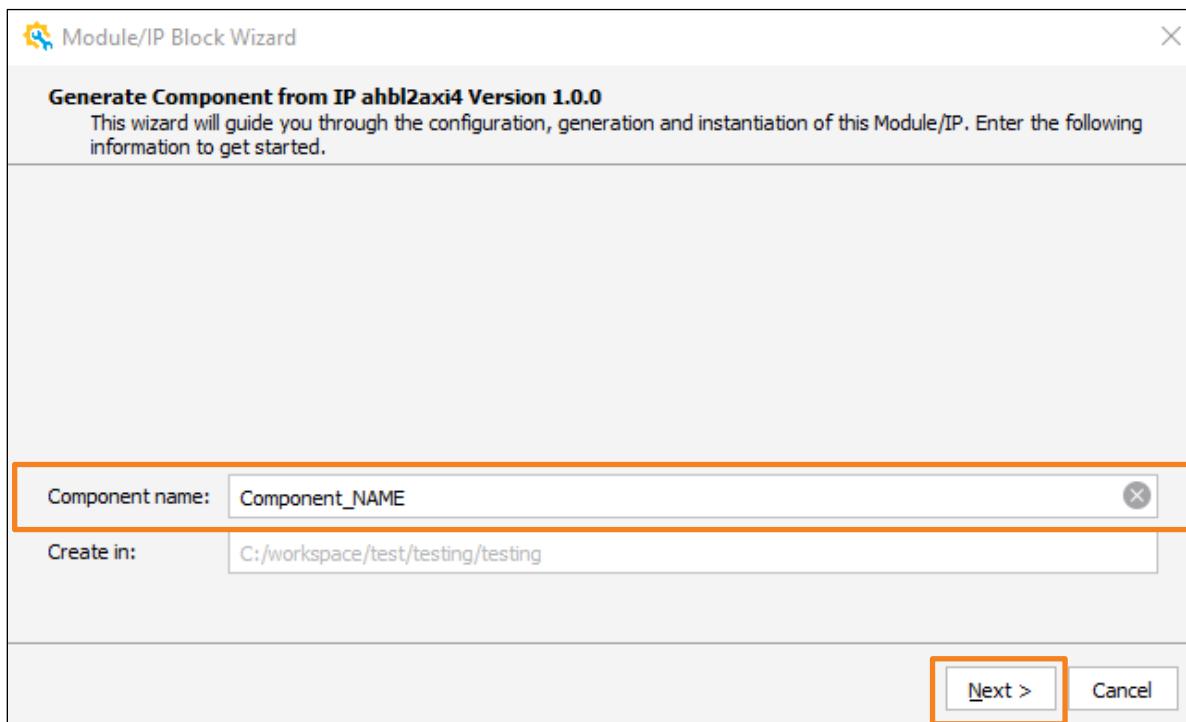

2. In the **IP Catalog** tab, double click **AHB-Lite to AXI4 Bridge** under **IP > Processors\_Controllers\_and\_Peripherals** category. The Module/IP Block Wizard window opens as shown in [Figure 4.1](#). Enter your desired component name in the **Component Name** field then click **Next**.

**Figure 4.1. Enter Component Name**

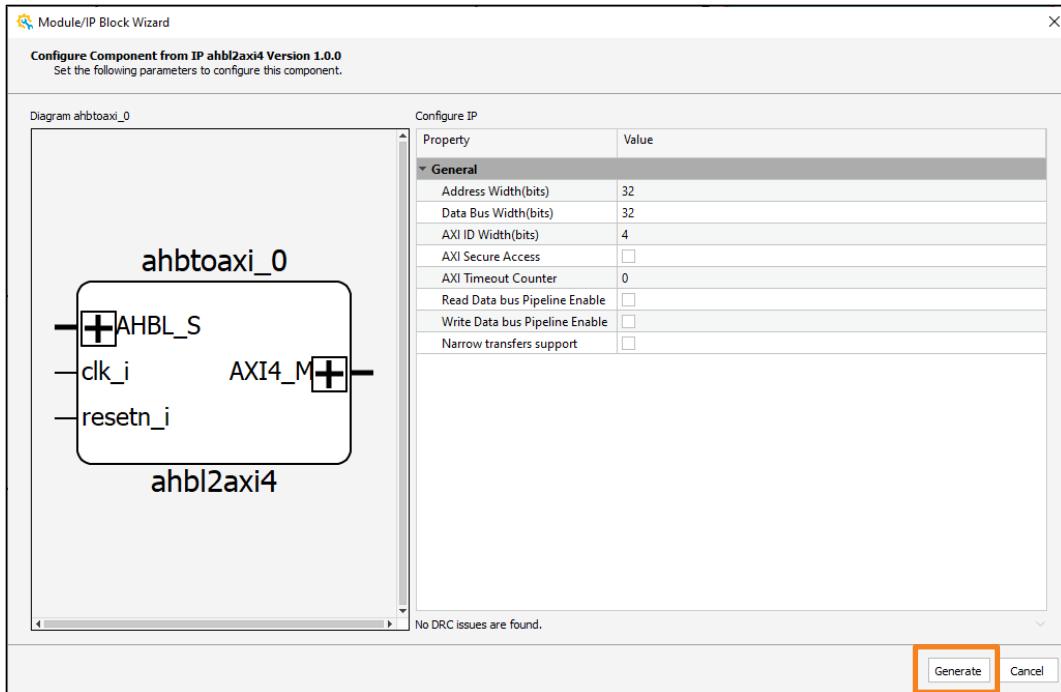

3. In the next Module/IP Block Wizard window, customize the IP according to your required configuration. [Figure 4.2](#) shows an example configuration. For more details on the configuration options, please refer to [Section 2.3](#).

Figure 4.2. IP Configuration

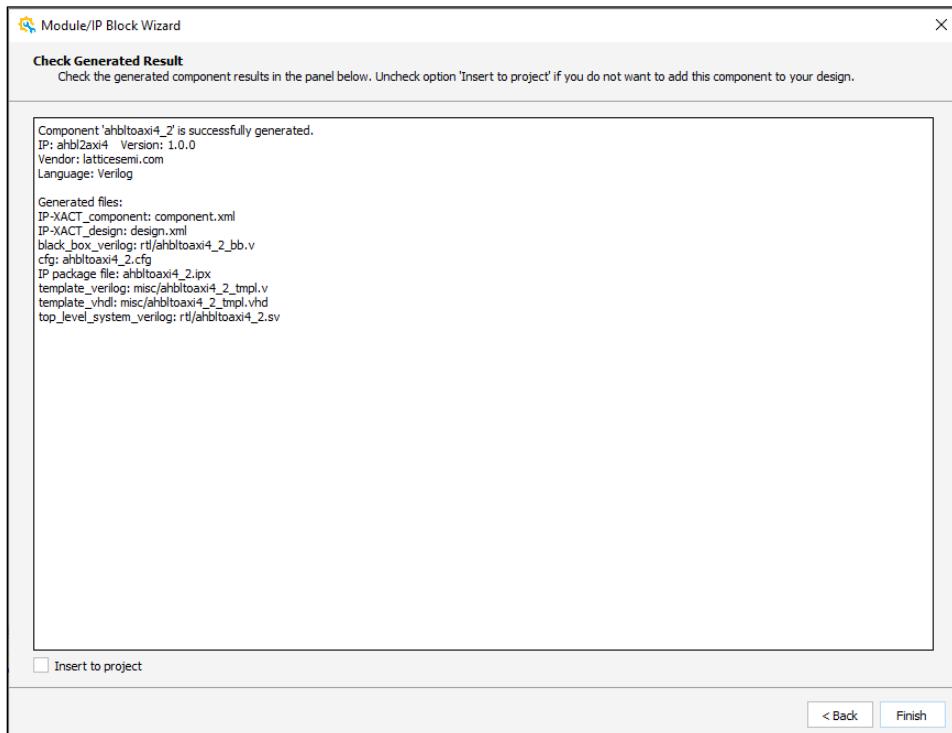

4. Click the **Generate** button. The **Check Generated Result** dialog box opens as shown in [Figure 4.3](#). This dialog box shows the design block messages and results.

Figure 4.3. Check Generated Result

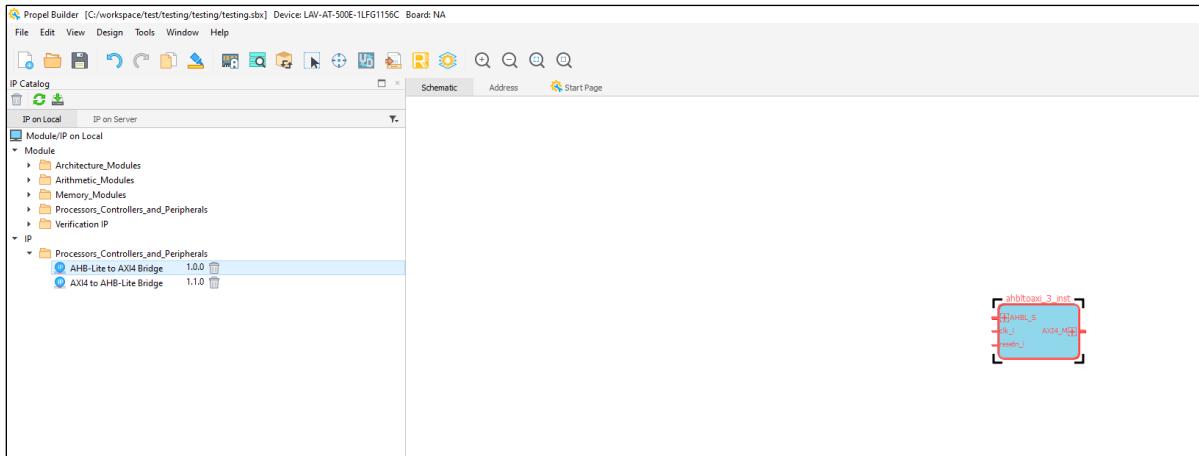

5. The generated IP will appear as a block diagram in the Schematic window. Connect it to the rest of the components in your system as shown in **Figure 4.4**.

**Figure 4.4. Schematic Window**

6. Once all the components are connected, click **Design -> Validate Design** to validate your design. If everything is okay, click **Design -> Generate** to generate the RTL files for your created system. All the generated files are placed under <directory paths in the **Create in** field as shown in **Step 2** > / lib/ latticesemi.com/ folder.

#### 4.1.1. Generated Files and Structure

The generated AHB-Lite to AXI4 Bridge IP package includes the closed-box (<Component name>\_bb.v) and the instance templates (<Component name>\_tmpl.v/vhd) that's use to instantiate the core in a top-level design. An example RTL top-level reference source file (Component name>.v) is given that can be used as an instantiation template for the module. The generated files are listed in **Table 4.1**.

**Table 4.1. Generated Files**

| Attribute                                                       | Description                                                                     |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------|

| <Component name>.ipx                                            | This file contains the information on the files associated to the generated IP. |

| <Component name>.cfg                                            | This file contains the parameter values used in the IP configuration.           |

| component.xml                                                   | Contains the ipxact:component information of the IP.                            |

| design.xml                                                      | Documents the configuration parameters of the IP in IP-XACT 2014 format.        |

| rtl/<Component name>.v                                          | This file provides an example RTL top file that instantiates the module.        |

| rtl/<Component name>_bb.v                                       | This file provides the synthesis closed-box.                                    |

| misc/<Component name>_tmpl.v<br>misc /<Component name>_tmpl.vhd | These files provide instance templates for the module.                          |

## Appendix A. Resource Utilization

Table A.1 shows a sample of the resource utilization of the AHB-Lite to AXI4 Bridge IP on Lattice Avant devices.

Table A.1. Estimated Device Resource Utilization on Lattice Avant Devices

| Data Width | AXI4 Timeout Counter | Attribute Values              |                                |                         | Clock Fmax (MHz) | LUTs | Register | EBRs |

|------------|----------------------|-------------------------------|--------------------------------|-------------------------|------------------|------|----------|------|

|            |                      | Read Data Bus Pipeline Enable | Write Data Bus Pipeline Enable | Narrow Transfer Support |                  |      |          |      |

| 32         | 0                    | 0                             | 0                              | 0                       | 350              | 95   | 82       | 0    |

| 32         | 0                    | 1                             | 1                              | 0                       | 350              | 89   | 144      | 0    |

| 32         | 128                  | 0                             | 0                              | 0                       | 350              | 118  | 108      | 0    |

| 32         | 128                  | 1                             | 1                              | 0                       | 350              | 115  | 170      | 0    |

| 256        | 0                    | 0                             | 0                              | 0                       | 350              | 95   | 82       | 0    |

| 256        | 0                    | 1                             | 1                              | 0                       | 350              | 97   | 604      | 0    |

| 256        | 128                  | 0                             | 0                              | 0                       | 350              | 118  | 108      | 0    |

| 256        | 128                  | 1                             | 1                              | 0                       | 350              | 122  | 620      | 0    |

| 32         | 0                    | 0                             | 0                              | 1                       | 350              | 105  | 96       | 0    |

| 32         | 0                    | 1                             | 1                              | 1                       | 350              | 106  | 161      | 0    |

| 32         | 128                  | 0                             | 0                              | 1                       | 350              | 128  | 115      | 0    |

| 32         | 128                  | 1                             | 1                              | 1                       | 350              | 125  | 170      | 0    |

| 256        | 0                    | 0                             | 0                              | 1                       | 350              | 125  | 116      | 1    |

| 256        | 0                    | 1                             | 1                              | 1                       | 350              | 128  | 634      | 1    |

| 256        | 128                  | 0                             | 0                              | 1                       | 350              | 150  | 139      | 1    |

| 256        | 128                  | 1                             | 1                              | 1                       | 350              | 156  | 652      | 1    |

**Notes:**

1. Address width is always set to 32 bits in all configurations listed.

2. The resource values are populated using LAV-AT-E70-1LFG676C device compiled in the Lattice Radiant 2023.1 design software with Synplify Pro. When the IP is combined with other blocks in the FPGA, the value can be expected to vary from the value in the table.

Table A.2 shows a sample of the resource utilization of AHB-Lite to AXI4 Bridge IP on CertusPro-NX devices.

Table A.2. Estimated Device Resource Utilization on CertusPro-NX Devices

| Data Width | AXI4 Timeout Counter | Attributes Values             |                                |                         | Clock Fmax (MHz)                    |                                                                | LUTs | Register | EBRs |

|------------|----------------------|-------------------------------|--------------------------------|-------------------------|-------------------------------------|----------------------------------------------------------------|------|----------|------|

|            |                      | Read Data Bus Pipeline Enable | Write Data Bus Pipeline Enable | Narrow Transfer Support | Performance Grade = 7 & 8_Low-Power | Performance Grade = 9_Low-Power and All High-Performance Grade |      |          |      |

| 32         | 0                    | 0                             | 0                              | 0                       | 160                                 | 200                                                            | 83   | 87       | 0    |

| 32         | 0                    | 1                             | 1                              | 0                       | 160                                 | 200                                                            | 83   | 151      | 0    |

| 32         | 128                  | 0                             | 0                              | 0                       | 160                                 | 200                                                            | 109  | 105      | 0    |

| 32         | 128                  | 1                             | 1                              | 0                       | 160                                 | 200                                                            | 104  | 169      | 0    |

| 256        | 0                    | 0                             | 0                              | 0                       | 160                                 | 200                                                            | 83   | 87       | 0    |

| 256        | 0                    | 1                             | 1                              | 0                       | 160                                 | 200                                                            | 86   | 599      | 0    |

| 256        | 128                  | 0                             | 0                              | 0                       | 160                                 | 200                                                            | 109  | 105      | 0    |

| 256        | 128                  | 1                             | 1                              | 0                       | 160                                 | 200                                                            | 104  | 617      | 0    |

| 32         | 0                    | 0                             | 0                              | 1                       | 160                                 | 200                                                            | 94   | 94       | 0    |

| 32         | 0                    | 1                             | 1                              | 1                       | 160                                 | 200                                                            | 94   | 158      | 0    |

| 32         | 128                  | 0                             | 0                              | 1                       | 160                                 | 200                                                            | 115  | 112      | 0    |

| Attributes Values |                      |                               |                                |                         | Clock Fmax (MHz)                    |                                                                | LUTs | Register | EBRs |

|-------------------|----------------------|-------------------------------|--------------------------------|-------------------------|-------------------------------------|----------------------------------------------------------------|------|----------|------|

| Data Width        | AXI4 Timeout Counter | Read Data Bus Pipeline Enable | Write Data Bus Pipeline Enable | Narrow Transfer Support | Performance Grade = 7 & 8_Low-Power | Performance Grade = 9_Low-Power and All High-Performance Grade |      |          |      |

| 32                | 128                  | 1                             | 1                              | 1                       | 160                                 | 200                                                            | 115  | 176      | 0    |

| 256               | 0                    | 0                             | 0                              | 1                       | 160                                 | 200                                                            | 116  | 118      | 2    |

| 256               | 0                    | 1                             | 1                              | 1                       | 160                                 | 200                                                            | 116  | 630      | 2    |

| 256               | 128                  | 0                             | 0                              | 1                       | 160                                 | 200                                                            | 137  | 136      | 2    |

| 256               | 128                  | 1                             | 1                              | 1                       | 160                                 | 200                                                            | 137  | 648      | 2    |

**Notes:**

1. Address width is always set to 32 bits in all configurations listed.

2. The resource values are populated using LFCPNX-50-7ASG256C and LFCPNX-50-9ASG256C device compiled in Lattice Radiant 2023.1 design software with Synplify Pro. When the IP is combined with other blocks in FPGA, the value can be expected to vary from the value in the table.

## References

- [AHB-Lite to AXI4 Bridge IP Release Notes \(FPGA-RN-02048\)](#)

- [Lattice Propel 1.0 User Guide \(FPGA-UG-02110\)](#)

- [Lattice Radiant Timing Constraints Methodology \(FPGA-AN-02059\)](#)

- [AMBA AXI and ACE Protocol Specification](#) web page for AMBA AXI and ACE Protocol Specification version H.c

- [AMBA 3 AHB-Lite Protocol Specification](#) web page

- [LatticeECP3](#) web page

- [ECP5](#) web page

- [CrossLink-NX](#) web page

- [CertusPro-NX](#) web page

- [Certus-NX](#) web page

- [Certus-N2](#) web page

- [MachXO5-NX](#) web page

- [Avant-E](#) web page

- [Avant-G](#) web page

- [Avant-X](#) web page

- [Lattice Radiant Software](#) web page

- [Lattice Propel Design Environment](#) web page

- [Lattice Diamond Software](#) web page

- [Lattice Insights](#) for Lattice Semiconductor training courses and learning plans

## Technical Support Assistance

Submit a technical support case through [www.latticesemi.com/techsupport](http://www.latticesemi.com/techsupport).

For frequently asked questions, refer to the Lattice Answer Database at [www.latticesemi.com/Support/AnswerDatabase](http://www.latticesemi.com/Support/AnswerDatabase).

## Revision History

**Note:** In some instances, the IP may be updated without changes to the user guide. The user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

### Revision 1.4, IP v1.4.0, December 2025

| Section                | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction           | <p>Updated <a href="#">Quick Facts</a> section:</p> <ul style="list-style-type: none"> <li>Added note, <i>In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.</i></li> <li>Added note, <i>IP Configuration and Generation indicates the IP version release coinciding with the software version release. Check the software for IP version compatibility with earlier or later software versions.</i></li> </ul> |

| Functional Description | <p>Updated <a href="#">Table 2.2. IP Parameters</a>:</p> <ul style="list-style-type: none"> <li>Added note, <i>In cases where the AW (Address Write) and W (Write Data) channels operate concurrently, the timeout counter is reset upon receipt of any valid AW or W response from AXI subordinate.</i></li> </ul>                                                                                                                                                                                                                                                                                      |

| Designing with the IP  | <p>Added note, <i>The screenshots provided are for reference only. Details may vary depending on the version of the IP or software being used. If there have been no significant changes to the GUI, a screenshot may reflect an earlier version of the IP.</i></p>                                                                                                                                                                                                                                                                                                                                      |

| Revision History       | <p>Added note, <i>In some instances, the IP may be updated without changes to the user guide. The user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.</i></p>                                                                                                                                                                                                                                                                                                                                     |

### Revision 1.3, IP v1.3.0, June 2025

| Section      | Change Summary                                                                                                                                                                                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction | <p>Updated Table 1.1. Summary as follows:</p> <ul style="list-style-type: none"> <li>Renamed <i>Supported FPGA Family</i> to <i>Supported Devices</i>.</li> <li>Removed the <i>Targeted Devices</i> row.</li> <li>Added IP version.</li> </ul> |

| References   | Updated references.                                                                                                                                                                                                                            |

### Revision 1.2, IP v1.2.0, December 2024

| Section      | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction | <ul style="list-style-type: none"> <li>Updated Table 1.1 Summary. <ul style="list-style-type: none"> <li>Added Certus-N2, LatticeECP3, and ECP5 devices.</li> <li>Added IP Changes.</li> <li>Updated Design Tool Support.</li> </ul> </li> <li>Added the IP Support Summary section.</li> <li>Removed the <i>IP Validation Summary</i> section.</li> <li>Added ECP as one of the minimum device requirements for this IP in the Minimum Device Requirements section.</li> </ul> |

| References   | Updated references.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Revision 1.1, June 2024

| Section | Change Summary                                                                                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All     | <ul style="list-style-type: none"> <li>This release is for version 1.1.0 of the AHB-Lite to AXI4 Bridge IP.</li> <li>Renamed document from <i>AHB-Lite to AXI4 Bridge IP Core</i> to <i>AHB-Lite to AXI4 Bridge IP</i>.</li> <li>Changed <i>AXI</i> to <i>AXI4</i>.</li> </ul> |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | <ul style="list-style-type: none"><li>Changed <i>AHB</i> to <i>AHB-Lite</i>.</li><li>Performed minor formatting and typo edits.</li></ul>                                                                                                                                                                                                                                                                                            |

| Introduction          | <ul style="list-style-type: none"><li>Added CrossLink-NX, Certus-NX, and MachXO5-NX devices in Table 1.1 Summary.</li><li>Updated the simulation tool in the IP Validation Summary section.</li><li>Added validation status for IP version 1.1.0 in Table 1.2 IP Validation Level.</li><li>Updated the minimum device requirements for this IP to Nexus or Avant device family in the Minimum Device Requirements section.</li></ul> |

| Designing with the IP | Changed <i>black-box</i> to <i>closed-box</i> in the Generated Files and Structure section.                                                                                                                                                                                                                                                                                                                                          |

| References            | Updated references.                                                                                                                                                                                                                                                                                                                                                                                                                  |

**Revision 1.0, December 2023**

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

[www.latticesemi.com](http://www.latticesemi.com)