# QSPI Flash Controller IP

IP Version: v1.5.0

## User Guide

FPGA-IPUG-02248-1.3

June 2025

## Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Inclusive Language

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language [FAQ 6878](#) for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# Contents

|                                                             |    |

|-------------------------------------------------------------|----|

| Contents .....                                              | 3  |

| Abbreviations in This Document.....                         | 8  |

| 1. Introduction .....                                       | 9  |

| 1.1. Overview of the IP .....                               | 9  |

| 1.2. Quick Facts .....                                      | 9  |

| 1.3. IP Support Summary .....                               | 10 |

| 1.4. Features .....                                         | 13 |

| 1.5. Licensing and Ordering Information .....               | 14 |

| 1.5.1. Ordering Part Number.....                            | 14 |

| 1.6. Hardware Support.....                                  | 14 |

| 1.7. Minimum Device Requirements .....                      | 14 |

| 1.8. Naming Conventions .....                               | 14 |

| 1.8.1. Nomenclature.....                                    | 14 |

| 1.8.2. Signal Names .....                                   | 14 |

| 1.8.3. Attribute Names.....                                 | 14 |

| 2. Functional Description.....                              | 15 |

| 2.1. IP Architecture Overview .....                         | 15 |

| 2.2. Clocking .....                                         | 15 |

| 2.2.1. Clocking Overview .....                              | 15 |

| 2.3. Reset .....                                            | 16 |

| 2.3.1. Reset Overview .....                                 | 16 |

| 2.4. User Interfaces .....                                  | 16 |

| 2.5. Other IP Specific Blocks/Layers/Interfaces .....       | 16 |

| 2.5.1. IP Core Operation .....                              | 16 |

| 2.5.2. User Packet Frame Structure .....                    | 19 |

| 3. IP Parameter Description.....                            | 23 |

| 3.1. General.....                                           | 23 |

| 3.2. IP Parameter Settings for Example Use Cases.....       | 26 |

| 3.2.1. SPI Protocols.....                                   | 26 |

| 3.2.2. SPI Clock Phase and Polarity.....                    | 27 |

| 3.2.3. Big and Little Endian.....                           | 28 |

| 3.2.4. MSB or LSB First Transmitted Bit Transaction .....   | 28 |

| 3.2.5. Multiple SPI Targets .....                           | 28 |

| 3.2.6. Transmit and Receive FIFO .....                      | 28 |

| 4. Signal Description .....                                 | 29 |

| 5. Register Description .....                               | 34 |

| 5.1. Overview .....                                         | 34 |

| 5.2. Configuration Registers.....                           | 35 |

| 5.2.1. QSPI Configuration Register 0 .....                  | 35 |

| 5.2.2. QSPI Configuration Register 1 .....                  | 37 |

| 5.2.3. Flash Command Code 0 Register.....                   | 37 |

| 5.2.4. Flash Command Code 1 Register.....                   | 37 |

| 5.2.5. Flash Command Code 2 Register.....                   | 38 |

| 5.2.6. Flash Command Code 3 Register.....                   | 38 |

| 5.2.7. Flash Command Code 4 Register.....                   | 38 |

| 5.2.8. Flash Command Code 5 Register.....                   | 39 |

| 5.2.9. Flash Command Code 6 Register.....                   | 39 |

| 5.2.10. Flash Command Code 7 Register.....                  | 39 |

| 5.2.11. Minimum Flash Address Alignment Register .....      | 40 |

| 5.2.12. Starting Flash Address Space Mapping Register ..... | 40 |

| 5.2.13. Flash Memory Map Size Register .....                | 41 |

| 5.2.14. AXI/AHB-L Address Map Register .....                | 41 |

|                                                                                      |    |

|--------------------------------------------------------------------------------------|----|

| 5.3. Status and Interrupt Registers .....                                            | 42 |

| 5.3.1. Transaction Status Register .....                                             | 42 |

| 5.3.2. Interrupt Status Register .....                                               | 42 |

| 5.3.3. Interrupt Enable Register .....                                               | 45 |

| 5.3.4. Interrupt Set Register .....                                                  | 46 |

| 5.3.5. Supported Flash Command Packet Header and Data Transfer Status Register ..... | 47 |

| 5.3.6. Generic SPI Transaction Packet Header and Data Transfer Status Register ..... | 47 |

| 5.4. Control Registers .....                                                         | 47 |

| 5.4.1. TX FIFO Mapping .....                                                         | 47 |

| 5.4.2. RX FIFO Mapping .....                                                         | 48 |

| 5.4.3. Packet Header 0 Register .....                                                | 48 |

| 5.4.4. Packet Header 1 Register .....                                                | 51 |

| 5.4.5. Packet Header 2 Register .....                                                | 52 |

| 5.4.6. Packet Header 3 Register .....                                                | 52 |

| 5.4.7. Packet Data 0 Register .....                                                  | 52 |

| 5.4.8. Packet Data 1 Register .....                                                  | 53 |

| 5.4.9. Start Transaction Register .....                                              | 53 |

| 5.5. Operation Details/Programming Flow .....                                        | 54 |

| 5.5.1. Flash Write/Erase Supported Commands with FIFO Enabled .....                  | 54 |

| 5.5.2. Flash Read Supported Commands with FIFO Enabled .....                         | 59 |

| 5.5.3. Flash Supported Commands using Packet Header and Data Registers .....         | 61 |

| 5.5.4. Generic Flash Write Operation .....                                           | 63 |

| 5.5.5. Generic Flash Read Operation .....                                            | 65 |

| 5.5.6. Non-XiP Access (Direct Write/Read Access) through Flash Memory Map .....      | 66 |

| 5.5.7. XiP Access (Direct Read Access) through Flash Memory Map .....                | 69 |

| 5.5.8. Polling Mode .....                                                            | 72 |

| 6. Example Design .....                                                              | 73 |

| 6.1. Example Design Supported Configuration .....                                    | 73 |

| 6.2. Overview of the Example Design and Features .....                               | 74 |

| 6.3. Example Design Components .....                                                 | 75 |

| 6.4. Generating the Example Design .....                                             | 75 |

| 6.5. Simulating the Example Design .....                                             | 79 |

| 6.6. Hardware Testing .....                                                          | 81 |

| 7. Designing with the IP .....                                                       | 82 |

| 7.1. Generating and Instantiating the IP .....                                       | 82 |

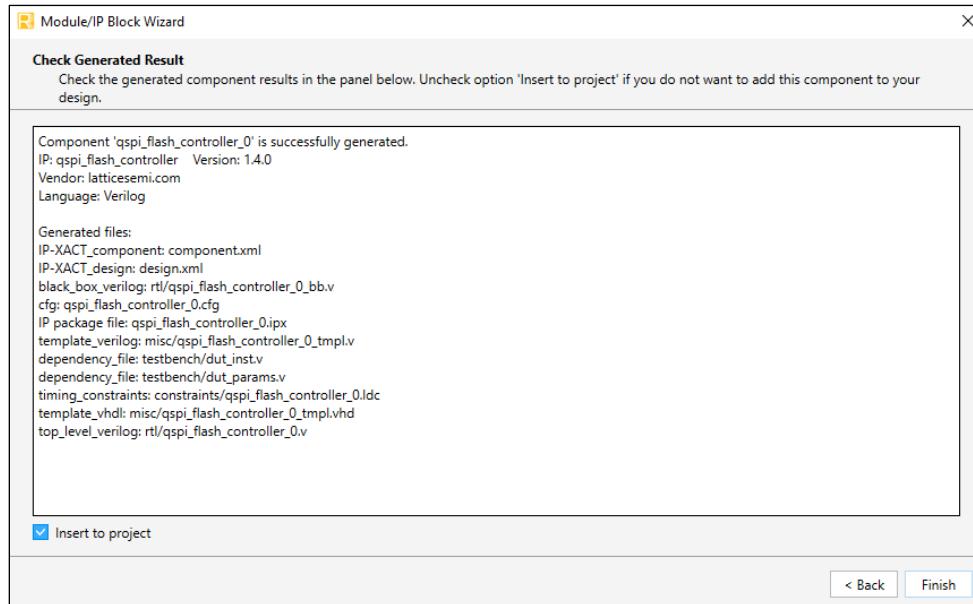

| 7.1.1. Generated Files and File Structure .....                                      | 84 |

| 7.2. Running Functional Simulation .....                                             | 85 |

| 7.3. Constraining the IP .....                                                       | 86 |

| Appendix A. Resource Utilization .....                                               | 87 |

| References .....                                                                     | 91 |

| Technical Support Assistance .....                                                   | 92 |

| Revision History .....                                                               | 93 |

## Figures

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| Figure 2.1. QSPI Flash Controller IP Block Diagram .....                                | 15 |

| Figure 2.2. Write Enable Command 06h Supported Command Sequence on SPI Mode .....       | 17 |

| Figure 2.3. Read Data Command 03h Supported Command Sequence on SPI Mode .....          | 17 |

| Figure 2.4. Block Erase Type 1 Command 20h Supported Command Sequence on SPI Mode ..... | 17 |

| Figure 2.5. Page Program Command 02h Supported Command Sequence on SPI Mode .....       | 18 |

| Figure 2.6. Supported Flash Command Packet with 2DW Header .....                        | 19 |

| Figure 2.7. Supported Flash Command Packet with 3DW Header .....                        | 20 |

| Figure 2.8. Supported Flash Command Packet with 4DW Header .....                        | 21 |

| Figure 2.9. Generic Command Packet with 1DW Header .....                                | 22 |

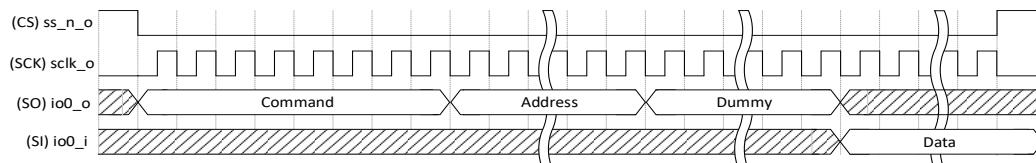

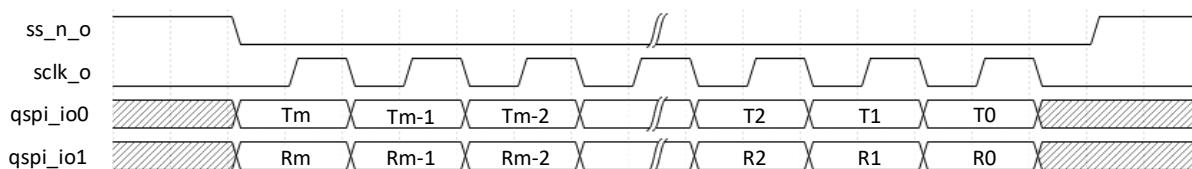

| Figure 3.1. Standard SPI Timing Diagram .....                                           | 26 |

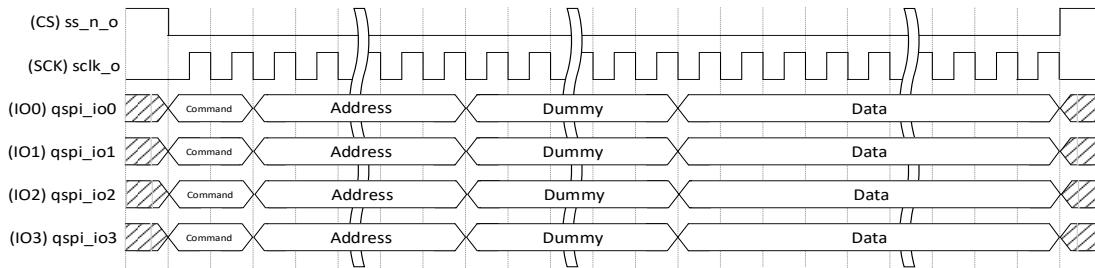

| Figure 3.2. Extended SPI Timing Diagram .....                                           | 26 |

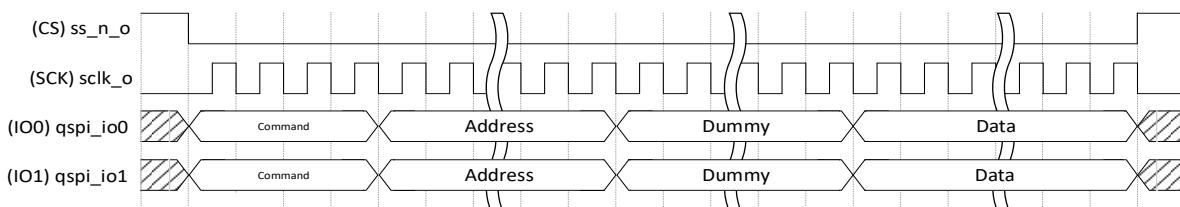

| Figure 3.3. Dual SPI Timing Diagram .....                                               | 26 |

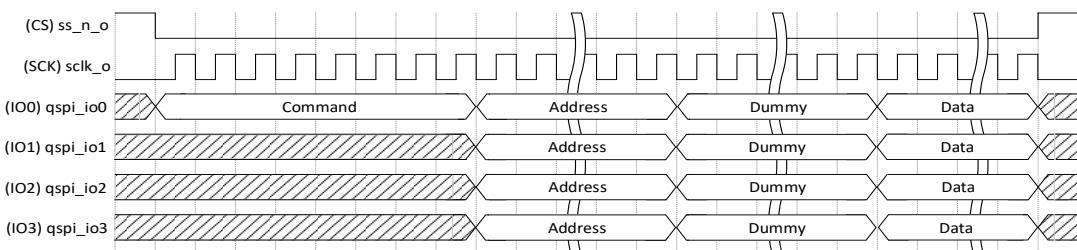

| Figure 3.4. Quad SPI Timing Diagram .....                                               | 27 |

| Figure 3.5. Clocking Mode 0 (SPI Clock Polarity=0, SPI Clock Phase=0) Waveforms .....   | 27 |

| Figure 3.6. Clocking Mode 3 (SPI Clock Polarity=1, SPI Clock Phase=1) Waveforms .....   | 27 |

| Figure 6.1. QSPI Flash Controller IP Example Design in SoC Project .....                | 74 |

| Figure 6.2. QSPI Flash Controller Example Design Block Diagram .....                    | 75 |

| Figure 6.3. Lattice Propel Launcher .....                                               | 76 |

| Figure 6.4. Create SoC Project .....                                                    | 76 |

| Figure 6.5. Define Instance .....                                                       | 77 |

| Figure 6.6. Address Tab .....                                                           | 77 |

| Figure 6.7. Build SoC Project Result .....                                              | 78 |

| Figure 6.8. C/C++ Project Load System and BSP .....                                     | 78 |

| Figure 6.9. Build C/C++ Project Result .....                                            | 79 |

| Figure 6.10. Reload sbx .....                                                           | 79 |

| Figure 6.11. Verification Project Schematic .....                                       | 79 |

| Figure 6.12. Edited Testbench File .....                                                | 80 |

| Figure 6.13. Simulation Waveform .....                                                  | 80 |

| Figure 7.1. Module/IP Block Wizard .....                                                | 82 |

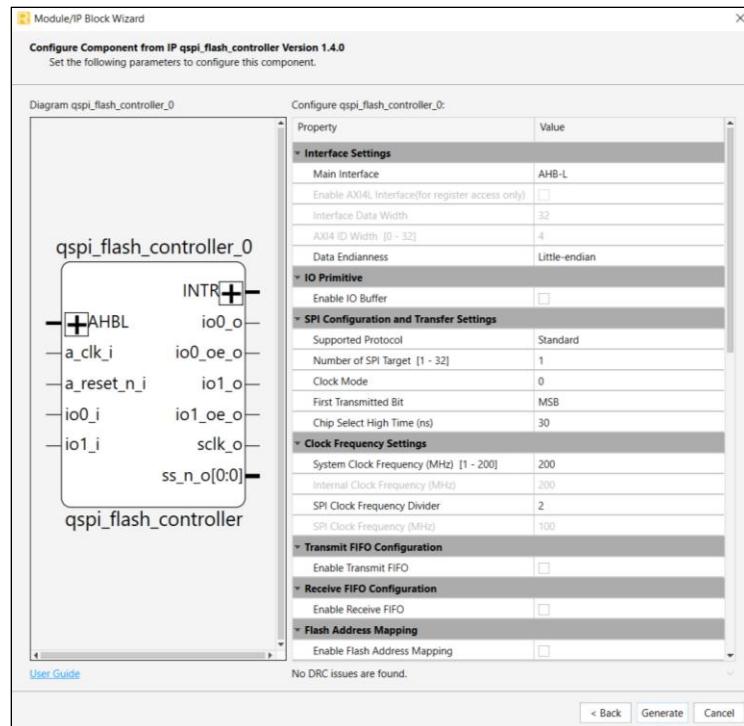

| Figure 7.2. IP Configuration – View 1 .....                                             | 83 |

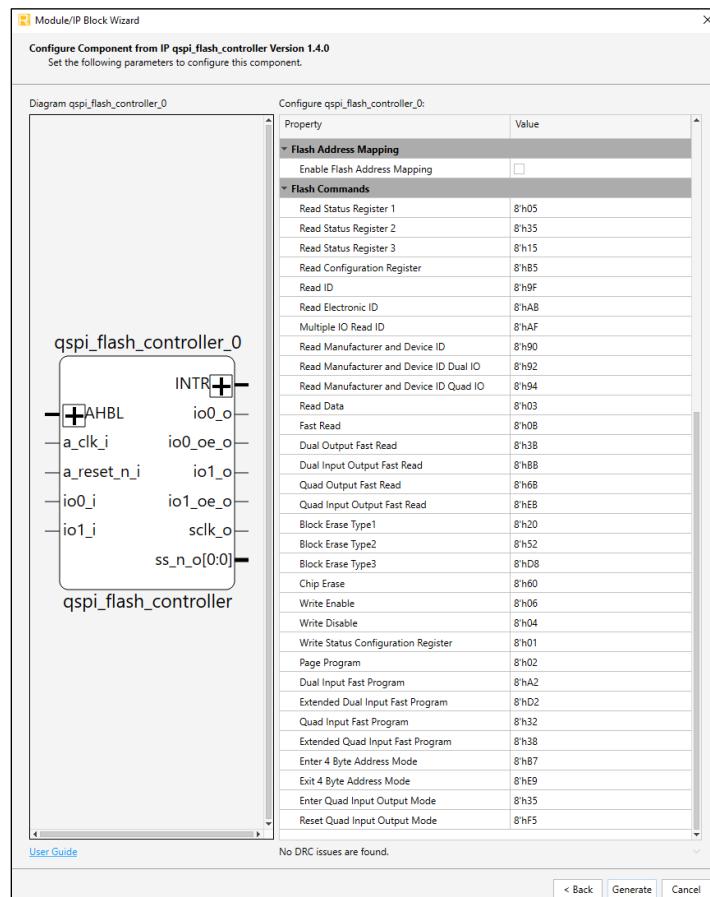

| Figure 7.3. IP Configuration – View 2 .....                                             | 83 |

| Figure 7.4. Check Generating Results .....                                              | 84 |

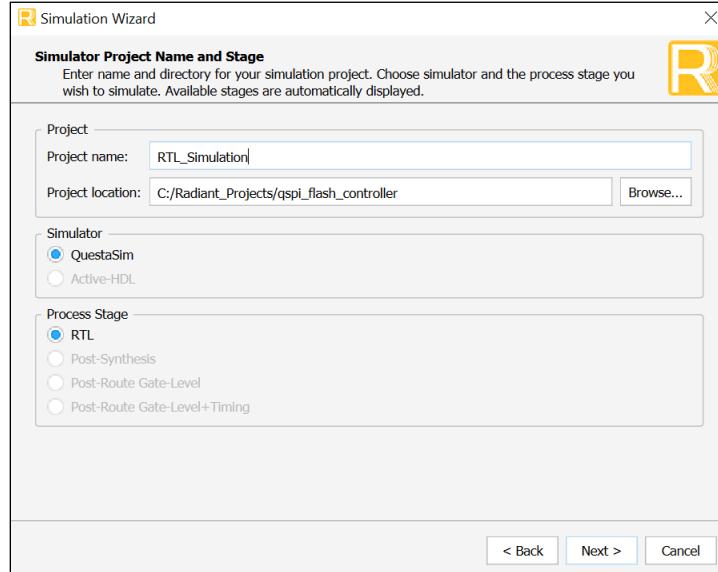

| Figure 7.5. Simulation Wizard .....                                                     | 85 |

| Figure 7.6: Adding Re-Ordering Source .....                                             | 85 |

| Figure 7.7. Simulation Waveform .....                                                   | 86 |

## Tables

|                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------|----|

| Table 1.1. Summary of the QSPI Flash Controller IP .....                                                         | 9  |

| Table 1.2. QSPI Flash Controller IP Support Readiness.....                                                       | 10 |

| Table 1.3. Minimum Device Requirements for QSPI Flash Controller IP .....                                        | 14 |

| Table 2.1. User Interfaces and Supported Protocols .....                                                         | 16 |

| Table 3.1. General Attributes .....                                                                              | 23 |

| Table 3.2. Clocking Modes .....                                                                                  | 27 |

| Table 3.3. Bus Interface Data Endianness.....                                                                    | 28 |

| Table 4.1. Top-Level Ports .....                                                                                 | 29 |

| Table 5.1. Register Access Types .....                                                                           | 34 |

| Table 5.2. Summary of QSPI Flash Controller IP Core Registers .....                                              | 34 |

| Table 5.3. QSPI Configuration Register 0.....                                                                    | 35 |

| Table 5.4. QSPI Configuration Register 1.....                                                                    | 37 |

| Table 5.5. Flash Command Code 0 Register .....                                                                   | 37 |

| Table 5.6. Flash Command Code 1 Register .....                                                                   | 37 |

| Table 5.7. Flash Command Code 2 Register .....                                                                   | 38 |

| Table 5.8. Flash Command Code 3 Register .....                                                                   | 38 |

| Table 5.9. Flash Command Code 4 Register .....                                                                   | 38 |

| Table 5.10. Flash Command Code 5 Register .....                                                                  | 39 |

| Table 5.11. Flash Command Code 6 Register .....                                                                  | 39 |

| Table 5.12. Flash Command Code 7 Register .....                                                                  | 39 |

| Table 5.13. Minimum Flash Address Alignment Register .....                                                       | 40 |

| Table 5.14. Starting Flash Address Space Mapping Register .....                                                  | 40 |

| Table 5.15. Flash Memory Map Size Register .....                                                                 | 41 |

| Table 5.16. AXI/AHB-L Address Map Register .....                                                                 | 41 |

| Table 5.17. Transaction Status Register .....                                                                    | 42 |

| Table 5.18. Interrupt Status Register when FIFO is Enabled .....                                                 | 42 |

| Table 5.19. Interrupt Status Register when FIFO is Disabled.....                                                 | 44 |

| Table 5.20. Interrupt Enable Register when FIFO is Enabled.....                                                  | 45 |

| Table 5.21. Interrupt Enable Register when FIFO is Disabled.....                                                 | 45 |

| Table 5.22. Interrupt Set Register when FIFO is Enabled .....                                                    | 46 |

| Table 5.23. Interrupt Set Register when FIFO is Disabled .....                                                   | 46 |

| Table 5.24. Supported Flash Command Transaction Status Register .....                                            | 47 |

| Table 5.25. Generic SPI Transaction Status Register .....                                                        | 47 |

| Table 5.26. TX FIFO Mapping Register .....                                                                       | 47 |

| Table 5.27. RX FIFO Mapping Register.....                                                                        | 48 |

| Table 5.28. Packet Header 0 Register – Supported Flash Commands.....                                             | 48 |

| Table 5.29. Supported Flash Commands .....                                                                       | 49 |

| Table 5.30. Packet Header 0 Register – Generic SPI Transactions.....                                             | 50 |

| Table 5.31. Packet Header 1 Register .....                                                                       | 51 |

| Table 5.32. Packet Header 2 Register .....                                                                       | 52 |

| Table 5.33. Packet Header 3 Register .....                                                                       | 52 |

| Table 5.34. Packet Data 0 Register .....                                                                         | 52 |

| Table 5.35. Packet Data 1 Register .....                                                                         | 53 |

| Table 5.36. Start Transaction Register .....                                                                     | 53 |

| Table 5.37. Programming Flow: Enter Quad Input/Output Mode, Without Payload, Standard SPI .....                  | 54 |

| Table 5.38. Programming Flow: Block Erase Type 1, Without Payload, Big Endian, Standard SPI .....                | 55 |

| Table 5.39. Programming Flow: Write Status/Configuration Register, With Payload, Big Endian, Standard SPI .....  | 56 |

| Table 5.40. Programming Flow: 256-bytes Page Program, FIFO Enabled, Big Endian, Standard SPI .....               | 57 |

| Table 5.41. Programming Flow: 256-bytes Extended Quad Input Fast Program, FIFO Enabled, Little Endian .....      | 57 |

| Table 5.42. Programming Flow: Read Status Register, FIFO Enabled, Standard SPI.....                              | 59 |

| Table 5.43. Programming Flow: 256-bytes Quad Input/Output Fast Read, FIFO Enabled, Big Endian, Extended SPI..... | 59 |

| Table 5.44. Programming Flow: 256-bytes Page Program, FIFO Disabled, Big Endian, Standard SPI.....               | 61 |

|                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------|----|

| Table 5.45. Programming Flow: 256-bytes Quad Input/Output Fast Read, FIFO Disabled, Big Endian, Extended SPI..... | 62 |

| Table 5.46. Programming Flow: Sending a Command, FIFO Disabled, Big Endian .....                                  | 63 |

| Table 5.47. Programming Flow: Sending Command and Data, FIFO Disabled, Big Endian.....                            | 63 |

| Table 5.48. Programming Flow: Sending Command then Read Data, FIFO Disabled, Big Endian .....                     | 65 |

| Table 5.49. Programming Flow: Enter 4-byte Address Mode, FIFO Disabled, Big Endian .....                          | 66 |

| Table 5.50. Programming Flow: Write Status Register, FIFO Disabled, Big Endian .....                              | 67 |

| Table 5.51. Programming Flow: Direct Write Access, Big Endian.....                                                | 68 |

| Table 5.52. Programming Flow: 1-Byte Quad Input/Output Fast Read, FIFO Disabled, Big Endian .....                 | 69 |

| Table 5.53. Programming Flow: 4-Byte Address, FIFO Disabled, Big Endian .....                                     | 70 |

| Table 5.54. Programming Flow: XiP Pattern and Dummy, FIFO Disabled, Big Endian .....                              | 70 |

| Table 5.55. Programming Flow: Read 4-bytes Data, FIFO Disabled, Big Endian.....                                   | 71 |

| Table 6.1. QSPI Flash Controller IP Configuration Used on Example Design .....                                    | 73 |

| Table 7.1. Generated File List .....                                                                              | 84 |

| Table A.1. Resource Utilization using LAV-AT-E70-3LFG1156I .....                                                  | 87 |

| Table A.2. Resource Utilization using LAV-AT-E70-1LFG1156I .....                                                  | 87 |

| Table A.3. Resource Utilization using LFCPNX-100-9LFG672I.....                                                    | 88 |

| Table A.4. Resource Utilization using LFCPNX-100-7LFG672I.....                                                    | 89 |

| Table A.5. Resource Utilization using LFD2NX-40-9BG256I.....                                                      | 89 |

| Table A.6. Resource Utilization using LFD2NX-40-7BG256I.....                                                      | 90 |

## Abbreviations in This Document

A list of abbreviations used in this document.

| Abbreviation      | Definition                                |

|-------------------|-------------------------------------------|

| AHB               | Advanced High-performance Bus             |

| AHB-L, AHB-Lite   | Advanced High-performance Bus Lite        |

| AMBA              | Advanced Microcontroller Bus Architecture |

| AXI4              | Advanced eXtensible Interface 4           |

| AXI4-L, AXI4-Lite | Advanced eXtensible Interface 4 Lite      |

| CLINT             | Core Local Interrupter                    |

| CPHA              | SPI Clock Phase                           |

| CPOL              | SPI Clock Polarity                        |

| CPU               | Central Processing Unit                   |

| CSR               | Configuration Status Register             |

| DRC               | Design Rule Checking                      |

| DSPI              | Dual Serial Peripheral Interface          |

| FIFO              | First In, First Out                       |

| FPGA              | Field-Programmable Gate Array             |

| HDL               | Hardware Description Language             |

| INCR              | Incrementing                              |

| LSB               | Least Significant Bit                     |

| MSB               | Most Significant Bit                      |

| PFR               | Platform Firmware Resiliency              |

| PLIC              | Platform Level Interrupt Controller       |

| QSPI              | Quad Serial Peripheral Interface          |

| SPI               | Serial Peripheral Interface               |

| TCM               | Tightly-Coupled Memory                    |

| XiP               | eXecute-in-Place                          |

# 1. Introduction

## 1.1. Overview of the IP

The Lattice QSPI Flash Controller IP core supports the SPI, DSPI, and QSPI protocols to perform operations on the target flash device.

A Quad Serial Peripheral Interface (QSPI) uses four tri-state data lines and is commonly used to program, erase, and read SPI flash memories. QSPI enhances the throughput of a standard SPI by four times since four bits are transferred with every clock cycle.

A Dual Serial Peripheral Interface (DSPI) uses two tri-state data lines and is used to program, erase, and read SPI flash memories. DSPI transfers two bits with every clock cycle.

A Standard Serial Peripheral Interface (SPI) uses separate data lines for input and output to perform flash operations.

## 1.2. Quick Facts

Table 1.1. Summary of the QSPI Flash Controller IP

|                             |                                     |                                                                                                                                                                                               |

|-----------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>IP Requirements</b>      | Supported Devices                   | Lattice CrossLink™-NX, Certus™-NX (LFD2NX-17, LFD2NX-40), CertusPro™-NX, MachXO5™-NX (LFMXO5-25, LFMXO5-55T, LFMXO5-100T), Avant™ (LAV-AT-E70, LAV-AT-G70, LAV-AT-X70), Certus-N2 (LN2-CT-20) |

|                             | IP Changes                          | Refer to the <a href="#">QSPI Flash Controller IP Release Notes (FPGA-RN-02016)</a> .                                                                                                         |

| <b>Resource Utilization</b> | Supported User Interface            | Advanced High-performance Bus Lite (AHB-Lite), Advanced eXtensible Interface 4 Lite (AXI4-Lite), Advanced eXtensible Interface 4 (AXI4)                                                       |

|                             | Resources                           | Refer to <a href="#">Appendix A. Resource Utilization</a> .                                                                                                                                   |

| <b>Design Tool Support</b>  | Lattice Implementation <sup>1</sup> | IP Core v1.4.0 – Lattice Radiant™ Software 2024.2<br>IP Core v1.5.0 – Lattice Radiant Software 2025.1                                                                                         |

|                             | Synthesis                           | Synopsys® Synplify Pro®, Lattice Synthesis Engine                                                                                                                                             |

|                             | Simulation                          | Refer to the Lattice Radiant Software User Guide for the list of supported simulators.                                                                                                        |

**Note:**

1. Lattice Implementation indicates the IP version release coinciding with the software version release. Check the software for IP version compatibility with earlier or later software versions.

## 1.3. IP Support Summary

Table 1.2. QSPI Flash Controller IP Support Readiness

| Device Family | IP Configuration and Settings                                                                                                                             | On-board Flash                           | Clock Frequency                                                                                           | Flash Settings                                                                    | Flash Commands                                                                                                                                                                                                                                                        | Radiant Timing Model | Hardware Validated |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|

| CertusPro-NX  | AHB-L and AXI4L interface, Disabled Transmit and Receive FIFO, Supported Commands                                                                         | Micron 128 Mbit SPI Flash (MT25QU128ABA) | System Clock Frequency: 125 MHz SPI Clock Frequency (max): 31.25 MHz (System Clock Frequency divide by 4) | Quad SPI, Clock mode 3, 3-byte address mode                                       | Read Configuration Register, Read ID, Multiple I/O Read ID, Fast Read, Dual Input/Output Fast Read, Quad Input/Output Fast Read, Block Erase Type 1, Block Erase Type 3, Write Configuration Register, Page Program, Dual Input Fast Program, Quad Input Fast Program | Final                | Yes                |

|               | AHB-L and AXI4L interface, Disabled Transmit and Receive FIFO, Direct Write and Read Access, Generic Command Packet (To enable/disable XiP Mode of Flash) |                                          | System Clock Frequency: 125 MHz SPI Clock Frequency (max): 31.25 MHz (System Clock Frequency divide by 4) | Extended SPI Mode, XiP and non-XiP modes, Clock mode 0 and 3, 3-byte address mode | Page Program, Dual Input Fast Program, Extended Dual Input Fast Program, Quad Input Fast Program, Extended Quad Input Fast Program, Read Data, Fast Read, Dual Output Fast Read, Dual Input/Output Fast Read, Quad Output Fast Read, Quad Input/Output Fast Read      | Final                | Yes                |

| Device Family | IP Configuration and Settings                                                                                                                             | On-board Flash                            | Clock Frequency                                                                                           | Flash Settings                                                                       | Flash Commands                                                                                                                                                                                                         | Radiant Timing Model | Hardware Validated |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|

| CertusPro-NX  | AXI4 and AXI4L interface, Disabled Transmit and Receive FIFO, Direct Write and Read Access, Generic Command Packet (To enable/disable XiP Mode of Flash)  | Winbond 512 Mbit SPI Flash (W25Q512JV)    | System Clock Frequency: 125 MHz SPI Clock Frequency (max): 31.25 MHz (System Clock Frequency divide by 4) | Quad SPI, XiP and non-XiP modes, Clock mode 0 and 3, 3-byte and 4-byte address modes | Page Program, Quad Input Page Program, Read Data, Fast Read, Dual Output Fast Read, Dual Input/Output Fast Read, Quad Output Fast Read, Quad Input/Output Fast Read                                                    | Final                | Yes                |

|               | AXI4 and AXI4L interface, Disabled Transmit and Receive FIFO, Supported Commands                                                                          |                                           |                                                                                                           | Quad SPI, Clock mode 0 and 3, 3-byte and 4-byte address modes                        | Read ID (Read JEDEC ID), Read Manufacturer and Device ID (Read Device ID), Read Manufacturer and Device ID - Dual SPI, Read Manufacturer and Device ID - Quad SPI, Enter 4-byte address mode, Exit 4-byte address mode | Final                | Yes                |

|               | AHB-L and AXI4L interface, Disabled Transmit and Receive FIFO, Supported Commands                                                                         | Macronix 512 Mbit SPI Flash (MX25L51245G) | System Clock Frequency: 125 MHz SPI Clock Frequency (max): 31.25 MHz (System Clock Frequency divide by 4) | Standard SPI, Clock mode 0 and 3,                                                    | Read ID, Read Electronic ID, Read Manufacturer and Device ID, Write Status Register, Read Status Register, Enter Quad Mode, Exit Quad Mode                                                                             | Final                | Yes                |

|               | AHB-L and AXI4L interface, Disabled Transmit and Receive FIFO, Direct Write and Read Access, Generic Command Packet (To enable/disable XiP Mode of Flash) |                                           | System Clock Frequency: 125 MHz SPI Clock Frequency (max): 31.25 MHz (System Clock Frequency divide by 4) | Quad SPI, XiP and non-XiP modes, Clock mode 0 and 3, 3-byte and 4-byte address modes | Page Program (QPI Mode), Quad Input/Output Fast Read (QPI Mode)                                                                                                                                                        | Final                | Yes                |

| Device Family | IP Configuration and Settings                                                    | On-board Flash                        | Clock Frequency                                                                                           | Flash Settings                                         | Flash Commands                                                                                                                                                                                                                                                             | Radiant Timing Model | Hardware Validated |

|---------------|----------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|

| Avant         | AXI4 interface, Disabled Transmit and Receive FIFO, Supported Commands           | Winbond 512Mbit SPI Flash (W25Q512JV) | System Clock Frequency: 125 MHz SPI Clock Frequency (max): 31.25 MHz (System Clock Frequency divide by 4) | Quad SPI, Clock mode 3, 3-byte address mode            | Read ID, Quad Input/Output Fast Read, Block Erase Type 1, Block Erase Type 3, Write Status Register, Quad Input Fast Program                                                                                                                                               | Advance              | Yes                |

|               | AXI4 and AXI4L interface, Disabled Transmit and Receive FIFO, Supported Commands |                                       | System Clock Frequency: 100 MHz SPI Clock Frequency (max): 25 MHz (System Clock Frequency divide by 4)    | Quad SPI, Clock mode 3, 3-byte and 4-byte address mode | Read Manufacturer and Device ID Dual I/O, Read Manufacturer and Device ID Quad I/O, Read Status Register-1, Dual Input/Output Fast Read, Quad Input/Output Fast Read, Block Erase Type 1, Block Erase Type 3, Write Status Register, Page Program, Quad Input Fast Program | Advance              | Yes                |

## 1.4. Features

Key features of the QSPI Flash Controller IP include:

- Different bus interfaces:

- AMBA 3 AHB-Lite Protocol v1.0

- 32-bit data and 32-bit address

- Single and burst transfers. Burst transfer is only supported on direct access – non-XiP and XiP.

- For non-XiP and XiP accesses, only a 32-bit data size is supported.

- AMBA AXI4-Lite Protocol (for CSR access only)

- 32-bit data and 32-bit address

- Single transfer only

- AMBA AXI4 Protocol

- 32-bit data and 32-bit address

- Single and multiple burst transfers. Burst transfer is only supported on direct access – non-XiP and XiP.

- For non-XiP and XiP accesses, only a 32-bit data size is supported.

- Scalable performance: 1X, 2X, 4X I/O widths

- Programmable SPI clock mode of 0 or 3

- Programmable serial clock frequency

- Optional use of transmit and receive FIFOs with configurable FIFO depth for register-based access only

- RISC V QSPI code little endian and code execution

- Big- and little-endian support

- Supports flash commands that allow access and control to configuration, function, and other write registers

- Internal decoding of SPI flash instructions for supported flash commands

- Generic command packet to perform user-defined SPI transactions

- eXecute In Place (XiP) for read access

- Configurable SPI mode/protocols with the following interfaces:

- Standard SPI – SCK, CS, SI, SO

- Dual SPI – SCK, CS, IO0, IO1

- Quad SPI – SCK, CS, IO0, IO1, IO2, IO3

- Standard SPI mode:

- Controller mode only

- MSB or LSB first transaction

- Multiple-target environment

- Dual and Quad SPI modes:

- Controller mode only

- MSB first transaction

- SPI transfer length of 8-bits only

- Multiple-target environment

- Interrupt capability

- Supported system clock frequency up to 200 MHz. The maximum frequencies for supported Avant and Nexus devices are 200 MHz and 125 MHz, respectively. Refer to [Appendix A](#) for sample  $f_{MAX}$  values.

## 1.5. Licensing and Ordering Information

The QSPI Flash Controller IP is provided at no additional cost with the Lattice Radiant software.

### 1.5.1. Ordering Part Number

The QSPI Flash Controller IP does not require an ordering part number.

## 1.6. Hardware Support

Refer to the [Example Design](#) section for more information on the boards used.

## 1.7. Minimum Device Requirements

The minimum device requirements for the QSPI Flash Controller IP are as follows:

**Table 1.3. Minimum Device Requirements for QSPI Flash Controller IP**

| Device                             | Speed Grades |

|------------------------------------|--------------|

| LAV-AT-E70, LAV-AT-G70, LAV-AT-X70 | 1, 2, 3      |

| LFD2NX-17, LFD2NX-40               | 7, 8, 9      |

| LFCPNX-50, LFCPNX-100              | 7, 8, 9      |

| LIFCL-17, LIFCL-33, LIFCL-40       | 7, 8, 9      |

| LFMXO5-25, LFMXO5-55T, LFMXO5-100T | 7, 8, 9      |

| LN2-CT-20                          | 1, 2, 3      |

## 1.8. Naming Conventions

### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.8.2. Signal Names

Signal names that end with:

- `_n` are active low (asserted when value is logic 0)

- `_i` are input signals

- `_o` are output signals

- `_io` are bi-directional input/output signals

### 1.8.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (*Attribute Name*).

## 2. Functional Description

### 2.1. IP Architecture Overview

The QSPI Flash Controller IP core allows the host inside the FPGA to communicate with multiple external SPI flash devices using either standard, extended dual/quad, dual, or quad SPI protocols.

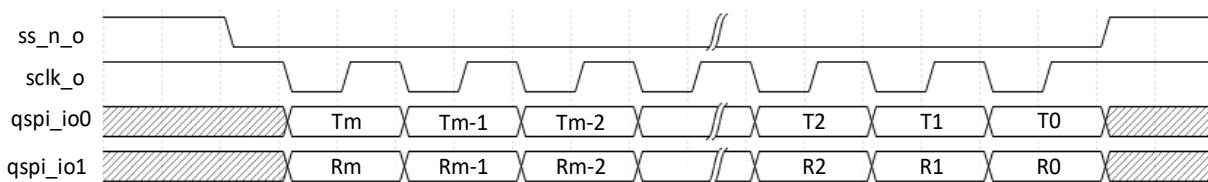

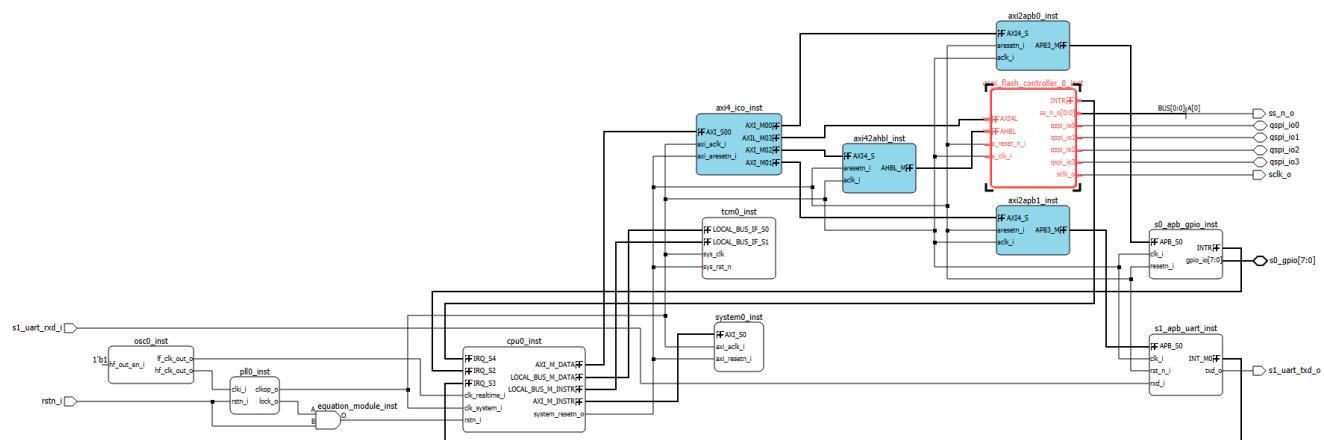

Figure 2.1 shows the block diagram of the QSPI Flash Controller IP.

Figure 2.1. QSPI Flash Controller IP Block Diagram

### 2.2. Clocking

There are two clocks for this IP.

#### 2.2.1. Clocking Overview

`a_clk_i` is the system clock that is also used as the AHB-Lite, AXI4-Lite, or AXI4 input clock. `sclk_o` is the serial clock to SPI flash.

## 2.3. Reset

There is only one reset for this IP.

### 2.3.1. Reset Overview

`a_reset_n_i` is an asynchronous active low reset. When low, output ports and registers are forced to their reset values.

## 2.4. User Interfaces

**Table 2.1. User Interfaces and Supported Protocols**

| User Interface                          | Supported Protocols          | Description                                                                                                                                                                                                              |

|-----------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced eXtensible Interface 4         | AXI4                         | The AXI4 bus interface can be used as the main interface for all IP operations. When flash address mapping is enabled, this interface can only be used for non-XiP direct write/read access and XiP direct read access.  |

| Advanced eXtensible Interface 4         | AXI4-Lite                    | This interface is used when flash address mapping is enabled. Configuration, control and status register, and supported command transactions can use this interface.                                                     |

| Advanced High-performance Bus Interface | AHB-Lite                     | The AHB-L bus interface can be used as the main interface for all IP operations. When flash address mapping is enabled, this interface can only be used for non-XiP direct write/read access and XiP direct read access. |

| Serial Peripheral Interface             | Standard, dual, and quad SPI | The Serial Peripheral Interface enables communication between the QSPI Flash Controller IP and target SPI flash device.                                                                                                  |

## 2.5. Other IP Specific Blocks/Layers/Interfaces

### 2.5.1. IP Core Operation

This IP supports standard, dual, and quad SPI transactions. During quad SPI-enabled protocol communication, standard and dual SPI transactions can still be processed by the controller. Likewise, during dual SPI-enabled protocol communication, standard SPI transactions can still be processed by the controller.

Controller sequences are mainly categorized for supported commands and generic SPI transactions.

This IP also provides an option to map the target flash device to an address space to mimic local memory access. When this is enabled, XiP access and non-XiP access can be performed by the controller using the selected IP's main interface.

#### 2.5.1.1. Supported Commands Flash Operation

IP supported flash commands are listed in [Table 5.29](#) including commonly used flash commands such as erase, page program, and read. For a flash operation, the `flash_command_code` bits of the packet header 0 register value are used by the controller to generate the complete sequence needed to execute the operation. The opcode used is based on the flash command opcode setting on the IP GUI or through the Flash Command Code 0 to 7 Registers with addresses 0x0000\_000C to 0x0000\_0028.

Below are the sample sequences automatically created by the controller based on flash\_command\_code register bits:

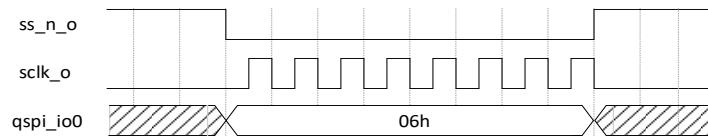

- flash\_command\_code == 5'h14, Write Enable flash command: The controller sends the equivalent opcode to the SPI interface.

**Figure 2.2. Write Enable Command 06h Supported Command Sequence on SPI Mode**

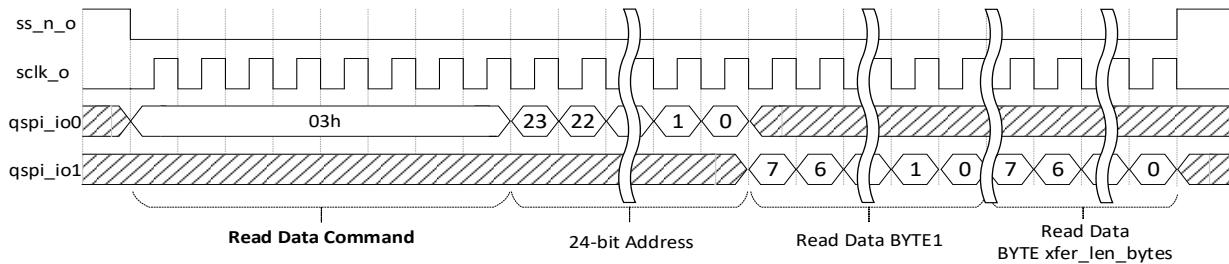

- flash\_command\_code == 5'h0A, Read Data flash command: The controller sends the equivalent opcode and specified flash address to the SPI interface. The SPI transaction remains active until xfer\_len\_bytes of data are read from the flash.

**Figure 2.3. Read Data Command 03h Supported Command Sequence on SPI Mode**

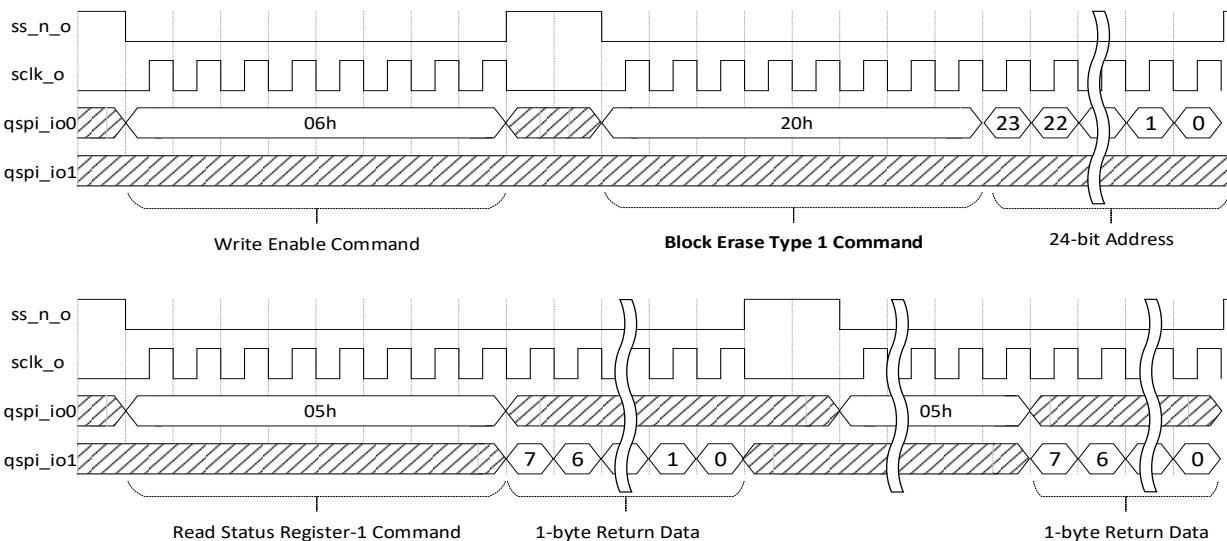

- flash\_command\_code == 5'h10, Block Erase Type 1 flash command: The controller sends the write enable opcode, equivalent erase opcode, specified flash address, and read status register opcode to the SPI interface. For erase flash transaction, the controller automatically sends the write enable and read status register flash command opcodes before and after sending the main flash command and address to the interface, respectively. The controller continues to send the read status register command until it reads that the flash is no longer busy.

**Figure 2.4. Block Erase Type 1 Command 20h Supported Command Sequence on SPI Mode**

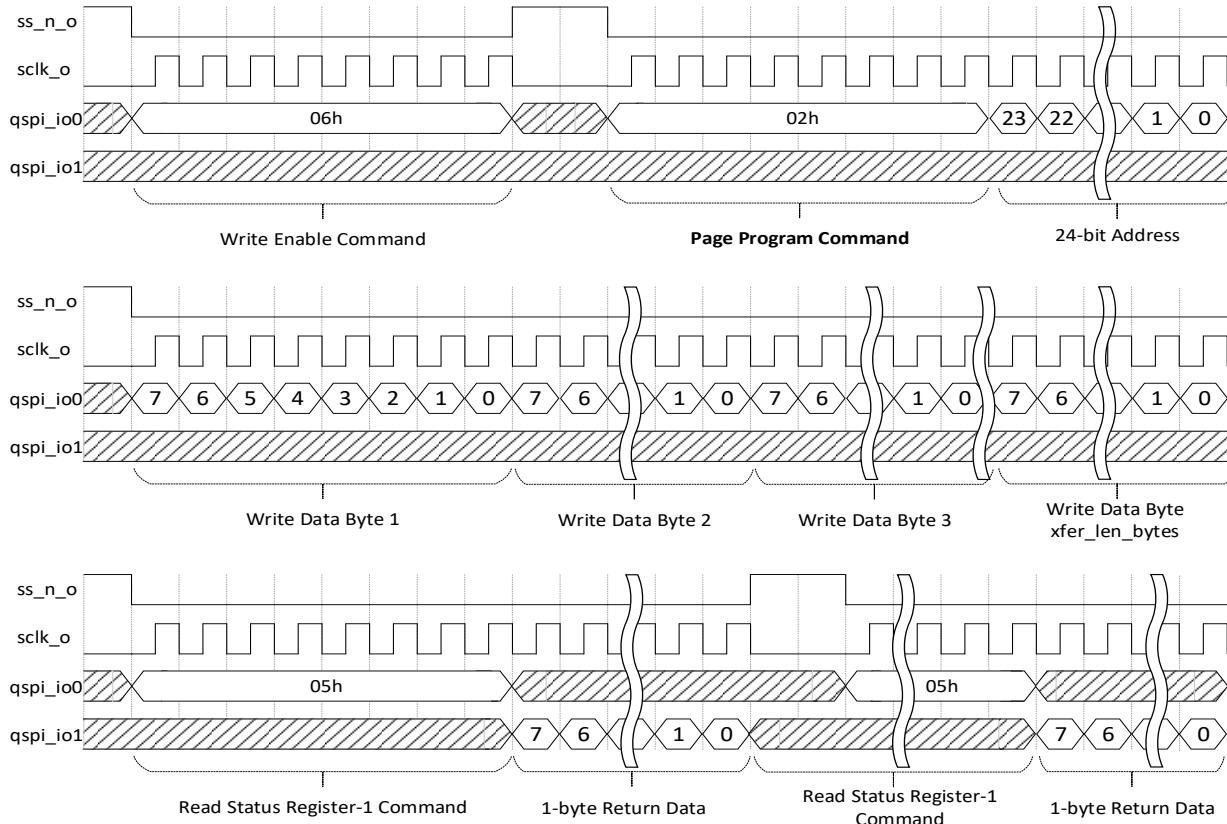

- `flash_command_code == 5'h17`, Page Program flash command: The controller sends the write enable opcode, equivalent page program opcode, and specified flash address. The SPI transaction remains active until all `xfer_len_bytes` of data from the packet data register or FIFO are sent to the flash after which the read status register opcode is sent to the SPI interface to end the flash operation. For write transaction, the controller automatically sends the write enable and read status register flash command opcodes before and after sending the main flash command, address, and data to the interface, respectively. The controller continues to send the read status register command until it reads that the flash is no longer busy.

**Figure 2.5. Page Program Command 02h Supported Command Sequence on SPI Mode**

### 2.5.1.2. Generic Commands Operation

The IP can also process generic SPI transactions. The controller just sends and reads data to and from the SPI interface using packet data registers or FIFO based on the transaction described through the packet header 0 register for generic SPI transaction as listed in [Table 5.30](#). Refer to the [Generic Flash Write Operation](#) and [Generic Flash Read Operation](#) sections for sample sequences on how use these features of the IP.

### 2.5.1.3. Non-XIP Access

This is a direct write or read access using AXI4 or AHB-L interface with INCR type burst operation to program to or read from flash. Single and burst transfers are supported for AHB-L and AXI4. When using this feature, both interfaces support a 32-bit data size only.

The program command can be set through the *Write Access Command* IP attribute or through the configuration register 0 `flash_map_en_wr_access_cmd` bits. The read command can be set through the *Read Access Command* IP attribute or through the configuration register 0 `flash_map_en_rd_access_cmd` bits. There are other IP attributes which should also be set to define the access to the flash such as *Flash Address Width*, *Command Lane Width*, *Address Lane Width*, *Data Lane Width*, and *Dummy clock cycles* equivalent to QSPI configuration register 0 bits [31:16] as described in the [QSPI Configuration Register 0](#) section.

The write or read access address on the interface and the *Flash Address Mapping* attributes are used to determine the flash address targeted for the access. All *Flash Address Mapping* attributes are listed in [Table 3.1](#). An example of non-XiP access is described in the [Non-XiP Access \(Direct Write/Read Access\) through Flash Memory Map](#) section.

#### 2.5.1.4. eXecute-in-Place (XiP) Access

This is a direct read access using the AXI4 or AHB-L interface with INCR type burst operation read from flash using its XiP mode. Single and burst transfers are supported for AHB-L and AXI4. When using this feature, both interfaces support a 32-bit data size only.

Accessing flash devices via XiP mode allows for faster read execution because only an address is required during operation.

To use this IP feature, the flash device XiP mode must first be activated using generic command packet. Refer to the flash device data sheet on how to activate and deactivate its XiP mode.

Once the flash device XiP mode is activated, set the xip\_enable bit on the start transaction register to perform XiP access. Through direct read access using the AXI4 or AHB-L interface, the controller performs direct read using the read command specified on the IP GUI during generation or through QSPI Configuration Register 0 bits with XiP-enabled flash. An example of XiP access is described in the [XiP Access](#) section.

### 2.5.2. User Packet Frame Structure

This section describes the packet structures used by the IP to generate SPI transactions. The packet header and data structure can also be written to the TX FIFO whenever the TX FIFO is enabled. Read data from the flash device can be stored in the RX FIFO when enabled or in the packet data register before the data is read through the interface.

For flash operations of supported commands, the number of dwords on the header depends on the flash address width.

[Figure 2.6](#) shows the packet structure for supported commands, such as write and read status register, that do not require a flash address but has write or read data.

|                       | 7                      | 6 | 5                    | 4                                                        | 3                    | 2            | 1                    | 0 |

|-----------------------|------------------------|---|----------------------|----------------------------------------------------------|----------------------|--------------|----------------------|---|

| Byte 0                | multiple_flash_target  |   |                      | flash_cmd_code [4:0]                                     |                      | with_payload | sup_flash_cmd = 1    |   |

| Byte 1                |                        |   |                      | num_wait_state [7:0]                                     |                      |              |                      |   |

| Byte 2                |                        |   |                      | xfer_len_bytes [7:0]                                     |                      |              |                      |   |

| Byte 3                |                        |   |                      | xfer_len_bytes [15:8]                                    |                      |              |                      |   |

| Byte 4                | reserved [1:0]         |   | dat_lane_width [1:0] |                                                          | adr_lane_width [1:0] |              | cmd_lane_width [1:0] |   |

| Byte 5                | flash_addr_width [2:0] |   |                      |                                                          | tgt_cs [4:0]         |              |                      |   |

| Byte 6                |                        |   |                      | reserved [7:0]                                           |                      |              |                      |   |

| Byte 7                |                        |   |                      | reserved [7:0]                                           |                      |              |                      |   |

| Byte 8                |                        |   |                      | payload [7:0]                                            |                      |              |                      |   |

| Byte 9                |                        |   |                      | payload [15:8]                                           |                      |              |                      |   |

| ...                   |                        |   |                      | ...                                                      |                      |              |                      |   |

| Byte 7+xfer_len_bytes |                        |   |                      | payload [(xfer_len_bytes*8) - 1 : (xfer_len_bytes-1)*8)] |                      |              |                      |   |

**Figure 2.6. Supported Flash Command Packet with 2DW Header**

Figure 2.7 shows the packet structure for supported commands, such as page program and read data, with 32-bit flash address and write or read data.

|                        | 7                      | 6 | 5                    | 4                                                       | 3                    | 2            | 1                    | 0 |

|------------------------|------------------------|---|----------------------|---------------------------------------------------------|----------------------|--------------|----------------------|---|

| Byte 0                 | multiple_flash_target  |   |                      | flash_cmd_code [4:0]                                    |                      | with_payload | sup_flash_cmd = 1    |   |

| Byte 1                 |                        |   |                      | num_wait_state [7:0]                                    |                      |              |                      |   |

| Byte 2                 |                        |   |                      | xfer_len_bytes [7:0]                                    |                      |              |                      |   |

| Byte 3                 |                        |   |                      | xfer_len_bytes [15:8]                                   |                      |              |                      |   |

| Byte 4                 | reserved [1:0]         |   | dat_lane_width [1:0] |                                                         | adr_lane_width [1:0] |              | cmd_lane_width [1:0] |   |

| Byte 5                 | flash_addr_width [2:0] |   |                      |                                                         | tgt_cs [4:0]         |              |                      |   |

| Byte 6                 |                        |   |                      | reserved [7:0]                                          |                      |              |                      |   |

| Byte 7                 |                        |   |                      | reserved [7:0]                                          |                      |              |                      |   |

| Byte 8                 |                        |   |                      | flash_address [31:24]                                   |                      |              |                      |   |

| Byte 9                 |                        |   |                      | flash_address [23:16]                                   |                      |              |                      |   |

| Byte 10                |                        |   |                      | flash_address [15:8]                                    |                      |              |                      |   |

| Byte 11                |                        |   |                      | flash_address [7:0]                                     |                      |              |                      |   |

| Byte 12                |                        |   |                      | payload [7:0]                                           |                      |              |                      |   |

| Byte 13                |                        |   |                      | payload [15:8]                                          |                      |              |                      |   |

| ...                    |                        |   |                      | ...                                                     |                      |              |                      |   |

| Byte 11+xfer_len_bytes |                        |   |                      | payload [(xfer_len_bytes*8) -1 : (xfer_len_bytes-1)*8)] |                      |              |                      |   |

Figure 2.7. Supported Flash Command Packet with 3DW Header

Figure 2.8 shows the packet structure for supported commands, such as page program and read data, with more than 32-bit flash address and with write or read data.

|                        | 7                      | 6 | 5                    | 4                                                       | 3                    | 2            | 1                    | 0 |

|------------------------|------------------------|---|----------------------|---------------------------------------------------------|----------------------|--------------|----------------------|---|

| Byte 0                 | multiple_flash_target  |   |                      | flash_cmd_code [4:0]                                    |                      | with_payload | sup_flash_cmd = 1    |   |

| Byte 1                 |                        |   |                      | num_wait_state [7:0]                                    |                      |              |                      |   |

| Byte 2                 |                        |   |                      | xfer_len_bytes [7:0]                                    |                      |              |                      |   |

| Byte 3                 |                        |   |                      | xfer_len_bytes [15:8]                                   |                      |              |                      |   |

| Byte 4                 | reserved [1:0]         |   | dat_lane_width [1:0] |                                                         | adr_lane_width [1:0] |              | cmd_lane_width [1:0] |   |

| Byte 5                 | flash_addr_width [2:0] |   |                      |                                                         | tgt_cs [4:0]         |              |                      |   |

| Byte 6                 |                        |   |                      | reserved [7:0]                                          |                      |              |                      |   |

| Byte 7                 |                        |   |                      | reserved [7:0]                                          |                      |              |                      |   |

| Byte 8                 |                        |   |                      | flash_address [63:56]                                   |                      |              |                      |   |

| Byte 9                 |                        |   |                      | flash_address [55:48]                                   |                      |              |                      |   |

| Byte 10                |                        |   |                      | flash_address [47:40]                                   |                      |              |                      |   |

| Byte 11                |                        |   |                      | flash_address [39:32]                                   |                      |              |                      |   |

| Byte 12                |                        |   |                      | flash_address [31:24]                                   |                      |              |                      |   |

| Byte 13                |                        |   |                      | flash_address [23:16]                                   |                      |              |                      |   |

| Byte 14                |                        |   |                      | flash_address [15:8]                                    |                      |              |                      |   |

| Byte 15                |                        |   |                      | flash_address [7:0]                                     |                      |              |                      |   |

| Byte 16                |                        |   |                      | payload [7:0]                                           |                      |              |                      |   |

| Byte 17                |                        |   |                      | payload [15:8]                                          |                      |              |                      |   |

| ...                    |                        |   |                      | ...                                                     |                      |              |                      |   |

| Byte 15+xfer_len_bytes |                        |   |                      | payload [(xfer_len_bytes*8) -1 : (xfer_len_bytes-1)*8)] |                      |              |                      |   |

Figure 2.8. Supported Flash Command Packet with 4DW Header

Figure 2.9 shows the packet structure for generic SPI transaction where the controller only serializes the payload to the SPI interface or reads the data from the SPI interface.

|                       | 7                     | 6                  | 5         | 4                    | 3                     | 2              | 1                                                       | 0 |

|-----------------------|-----------------------|--------------------|-----------|----------------------|-----------------------|----------------|---------------------------------------------------------|---|

| Byte 0                | multiple_flash_target | frm_end            | frm_start | data_rate            | lane_width[1:0]       | cmd_type       | sup_flash_cmd = 0                                       |   |

| Byte 1                |                       | num_wait_sck [2:0] |           |                      | tgt_cs [4:0]          |                |                                                         |   |

| Byte 2                |                       |                    |           | xfer_len_bytes [7:0] |                       |                |                                                         |   |

| Byte 3                |                       |                    |           |                      | xfer_len_bytes [15:8] |                |                                                         |   |

| Byte 4                |                       |                    |           |                      |                       | payload [7:0]  |                                                         |   |

| Byte 5                |                       |                    |           |                      |                       | payload [15:8] |                                                         |   |

| ...                   |                       |                    |           |                      |                       | ...            |                                                         |   |

| Byte 5+xfer_len_bytes |                       |                    |           |                      |                       |                | payload [(xfer_len_bytes*8) -1 : (xfer_len_bytes-1)*8)] |   |

Figure 2.9. Generic Command Packet with 1DW Header

Table 5.28, Table 5.31, Table 5.32, Table 5.33, Table 5.34, and Table 5.35 show the packet header and data field definitions for flash operations of supported commands. Table 5.30, Table 5.34, and Table 5.35 show the packet header and data field definitions for generic SPI operations.

### 3. IP Parameter Description

The configurable attributes of the QSPI Flash Controller IP are shown in the following table. You can configure the IP by setting the attributes accordingly in the IP Catalog's Module/IP wizard of the Lattice Radiant software.

Wherever applicable, default values are in bold.

#### 3.1. General

**Table 3.1. General Attributes**

| Attribute                                          | Selectable Values                                         | Description                                                                                                                                                                                                                     |

|----------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Interface Settings</b>                          |                                                           |                                                                                                                                                                                                                                 |

| Main Interface                                     | <b>AHB-L</b> , AXI4                                       | Selects memory-mapped interface to be used by the host. The unselected interfaces are not available in the generated IP.                                                                                                        |

| Enable AXI4-L Interface (For register access only) | <b>Checked</b>                                            | Use the AXI4-L for register access when flash address mapping is enabled. Informational only.                                                                                                                                   |

| Interface Data Width                               | <b>32</b>                                                 | All interfaces use a 32-bit data width. Informational only.                                                                                                                                                                     |

| AXI4 ID Width                                      | <b>0–32, 4</b>                                            | Editable when <i>Main Interface == AXI4</i> .                                                                                                                                                                                   |

| Data Endianness                                    | <b>Little-endian</b> , Big-endian                         | Endianness of the interface data port.                                                                                                                                                                                          |

| <b>IO Primitive</b>                                |                                                           |                                                                                                                                                                                                                                 |

| Enable IO Buffer                                   | <b>Checked</b> , <b>Unchecked</b>                         | Enables bidirectional ports.                                                                                                                                                                                                    |

| <b>SPI Configuration and Transfer Setting</b>      |                                                           |                                                                                                                                                                                                                                 |

| Supported Protocol                                 | <b>Standard</b> , Dual, Quad                              | Standard, dual, and quad SPI are the supported protocols. Extended dual and quad SPI are also supported. When quad SPI is selected, the IP can also operate on 1X and 2X I/O widths. Dual SPI can also operate on 1X I/O width. |

| Number of SPI Target                               | <b>1–32</b>                                               | Specifies the number of target-select signal bits. Each bit is used for selecting an SPI target device.                                                                                                                         |

| Clock Mode                                         | <b>0, 3</b>                                               | SPI polarity and phase combination<br>Specifies the polarity of the SPI serial clock during idle state. Also specifies whether the rising or falling edge of the SPI serial clock will be used to shift in and out data.        |

| First Transmitted Bit                              | <b>MSB</b> , LSB                                          | Specifies the direction of shifting the data bits into and out of the SPI interface.<br>Editable if <i>Supported Protocol = Standard SPI</i> . Otherwise, value is fixed to MSB first transaction.                              |

| Chip Select High Time (ns)                         | <b>30, ..., 100</b>                                       | Specifies the minimum chip select high time.                                                                                                                                                                                    |

| <b>Clock Frequency Settings</b>                    |                                                           |                                                                                                                                                                                                                                 |

| System Clock Frequency (MHz)                       | <b>1–200</b>                                              | Specifies the clock frequency of the interface.                                                                                                                                                                                 |

| Internal Clock Frequency (MHz)                     | <b>1–200</b>                                              | Clock frequency to be used for core operation. Informational only. Value follows the <i>System Clock Frequency</i> attribute.                                                                                                   |

| SPI Clock Frequency Divider                        | <b>2, 4, 6, 8 ... 62</b>                                  | Specifies the divider value to generate the SPI clock from the system clock.                                                                                                                                                    |

| SPI Clock Frequency (MHz)                          | <b>System Clock Frequency/62–System Clock Frequency/2</b> | Indicates the resulting SPI clock frequency based on system clock frequency and divider values. Informational only.<br><i>SPI Clock Frequency (MHz) = System Clock Frequency (MHz) / SPI Clock Frequency Divider</i>            |

| <b>Transmit FIFO Configuration</b>                 |                                                           |                                                                                                                                                                                                                                 |

| Enable Transmit FIFO                               | <b>Checked</b> , <b>Unchecked</b>                         | Enables transmit FIFO.                                                                                                                                                                                                          |

| Address Depth                                      | <b>16, 32, 64, 128</b>                                    | Specifies the number of FIFO levels.<br>Visible and editable only when <i>Enable Transmit FIFO == Checked</i> .                                                                                                                 |

| Attribute                            | Selectable Values                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Receive FIFO Configuration</b>    |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Enable Receive FIFO                  | <input checked="" type="checkbox"/> <input type="checkbox"/> <b>Unchecked</b>                                                             | Enables receive FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

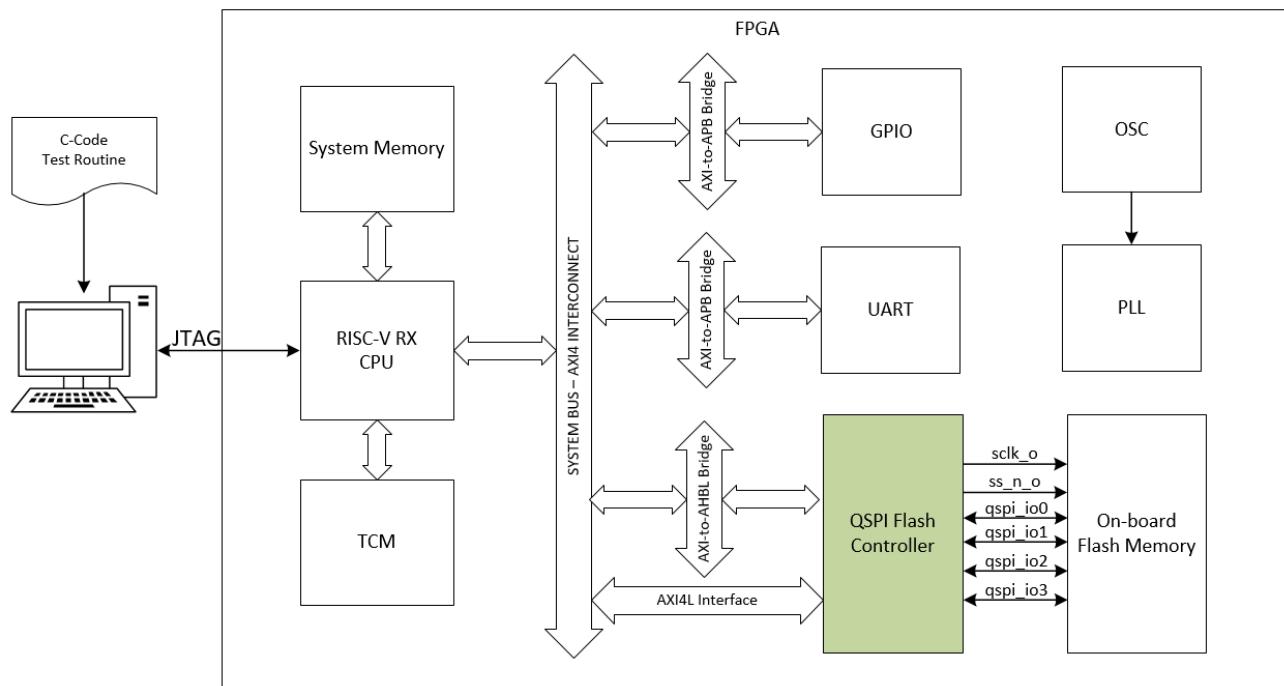

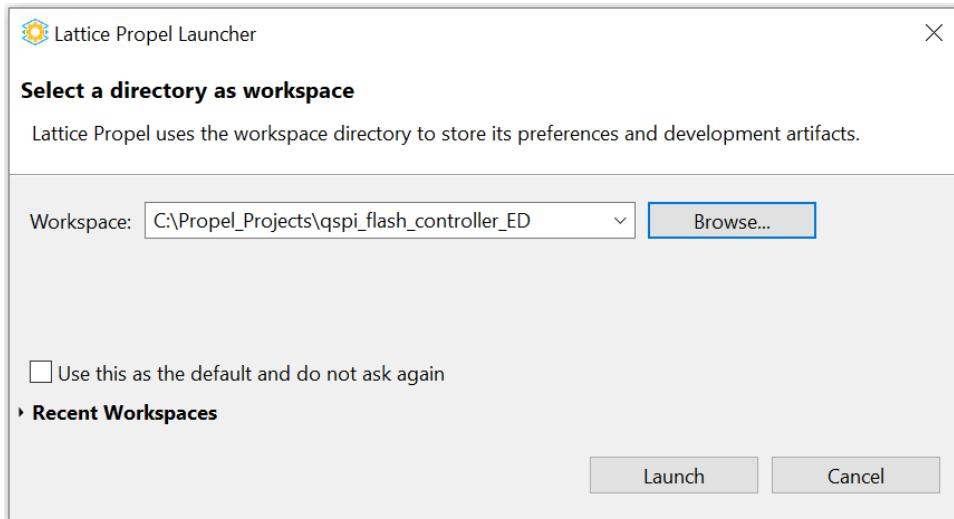

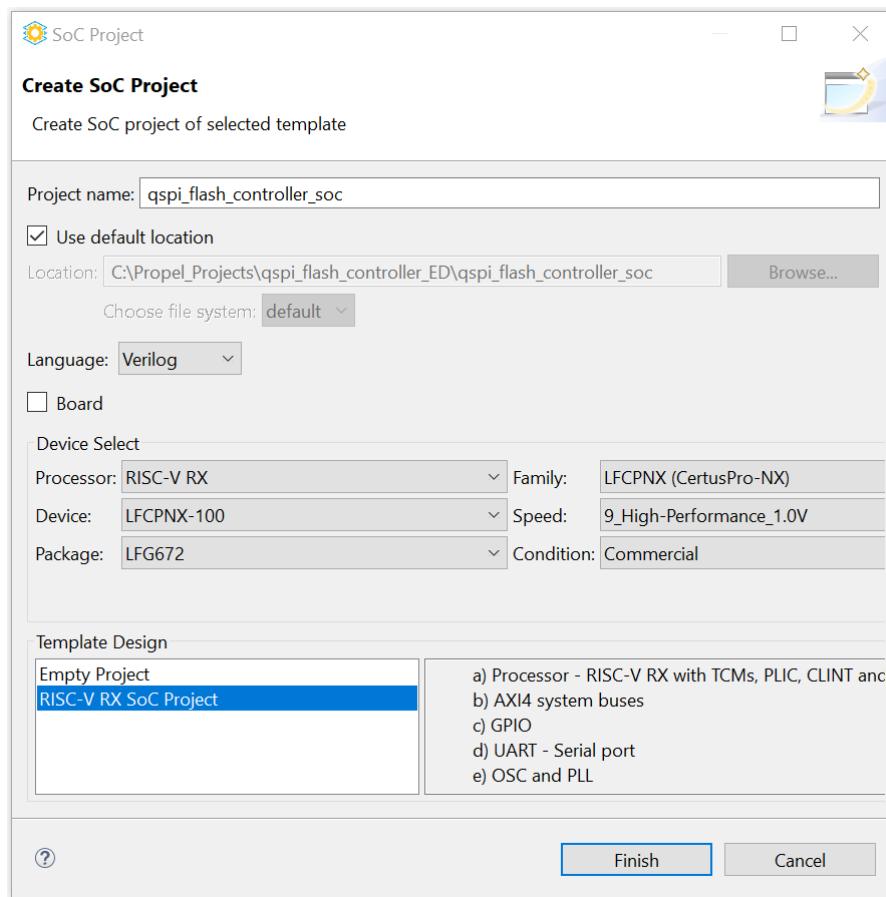

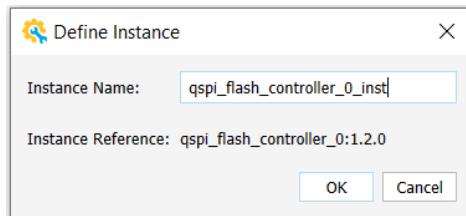

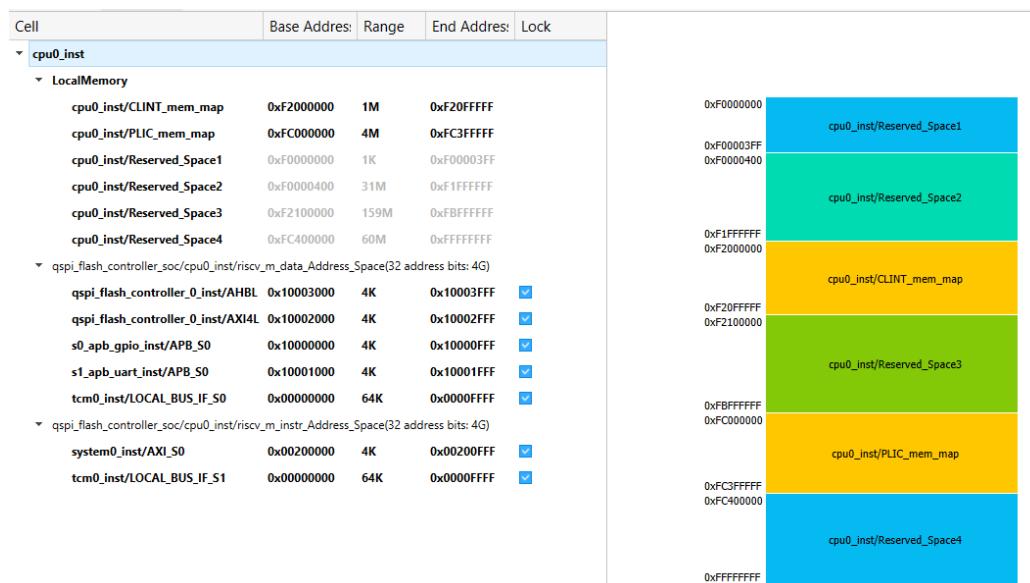

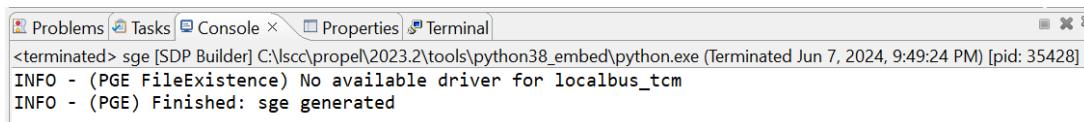

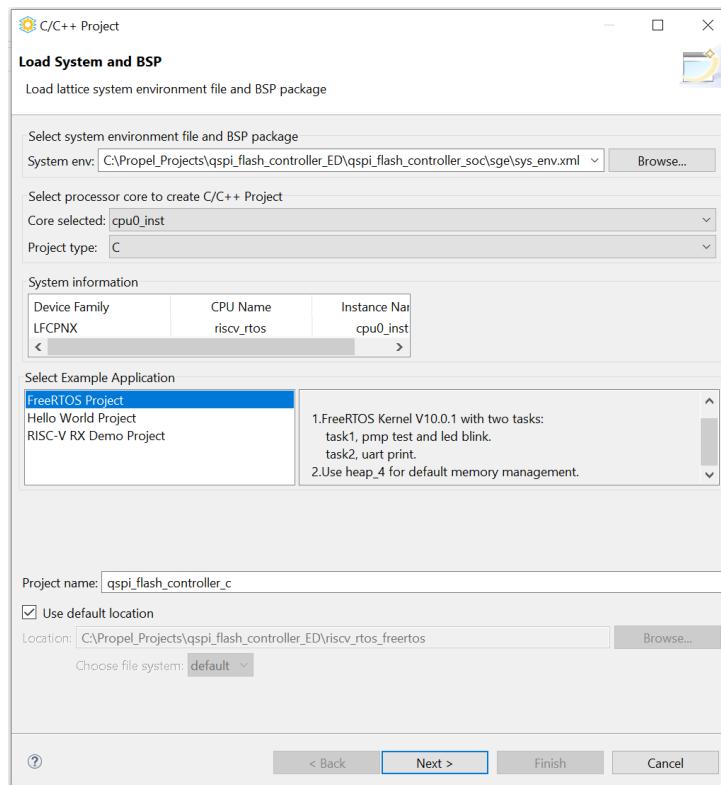

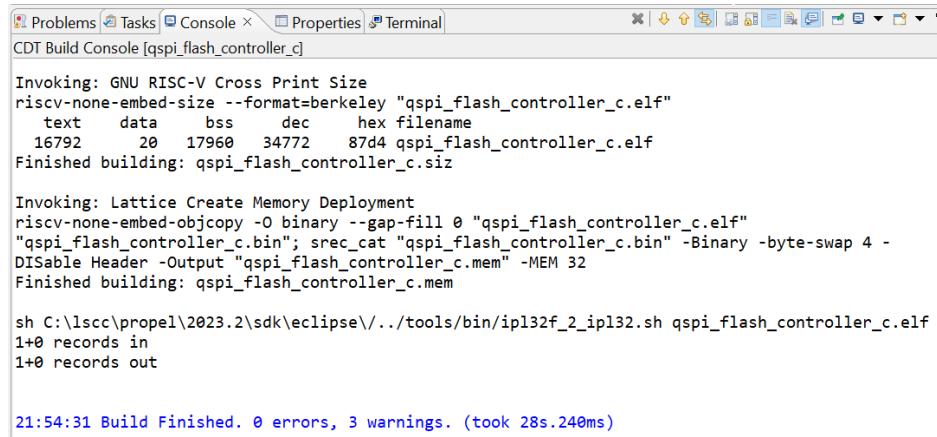

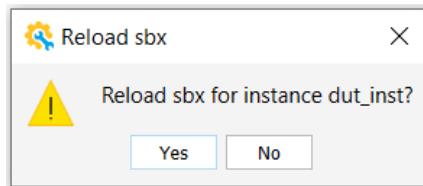

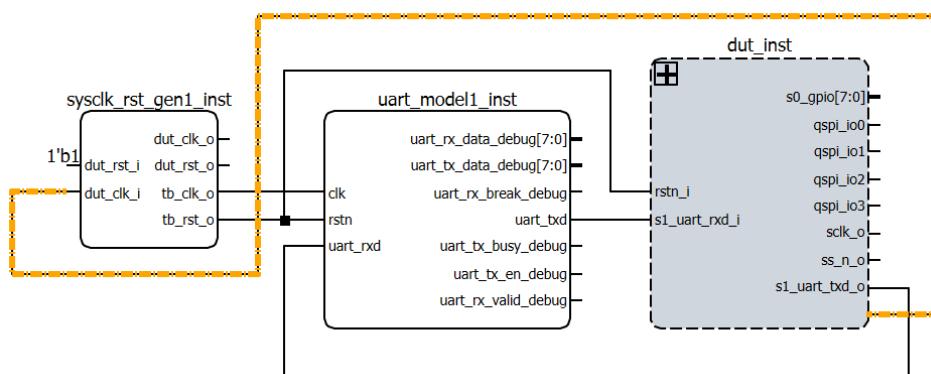

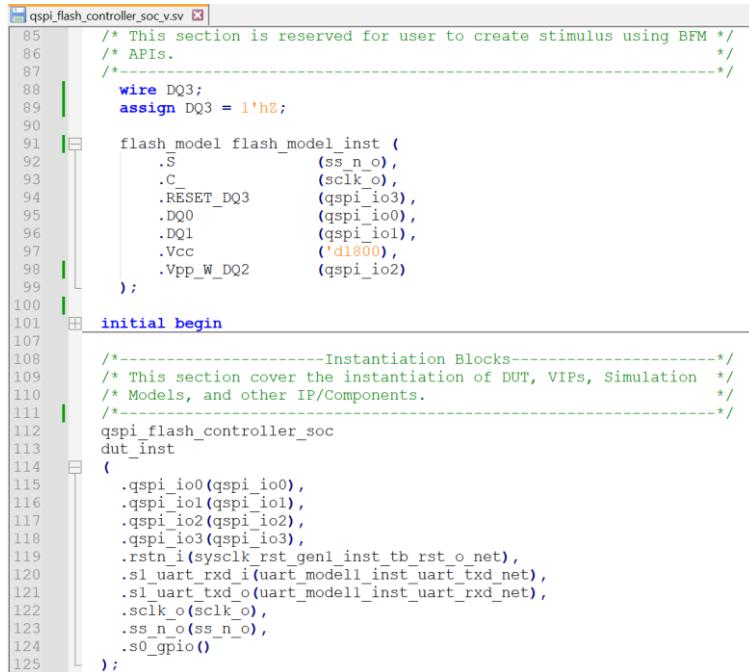

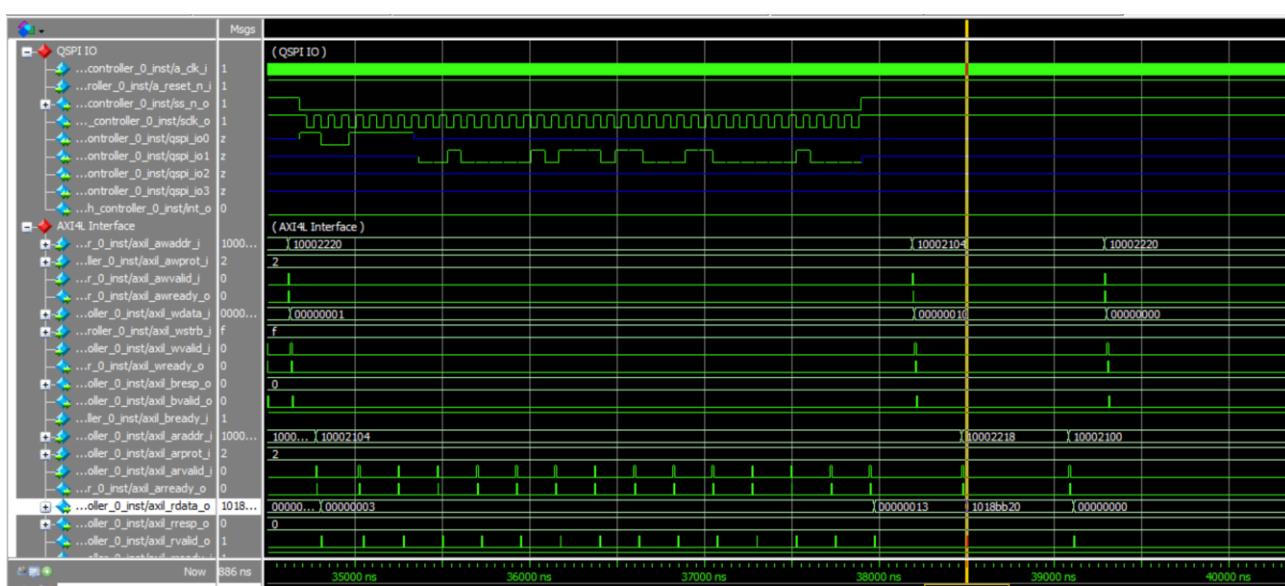

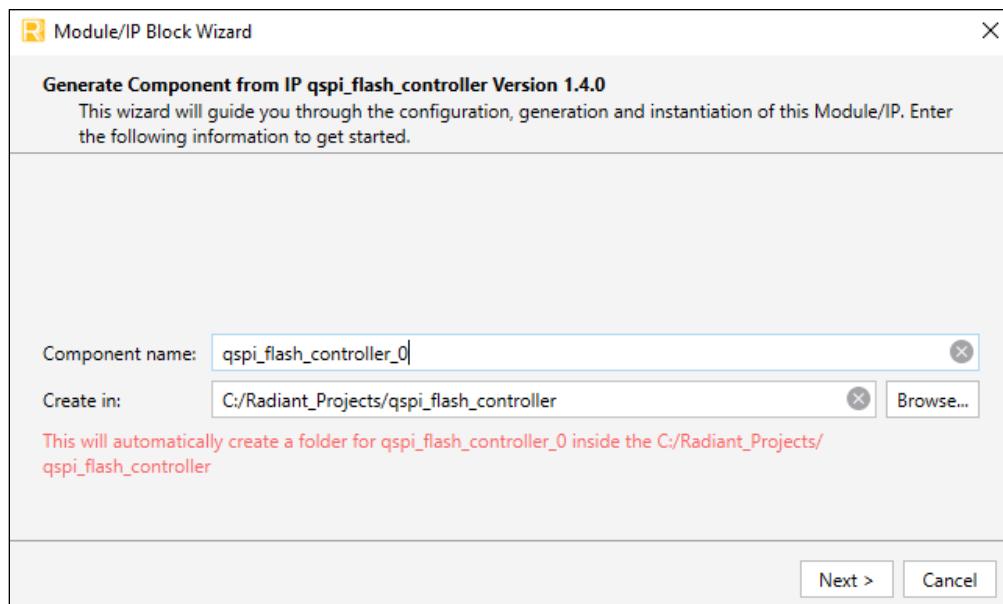

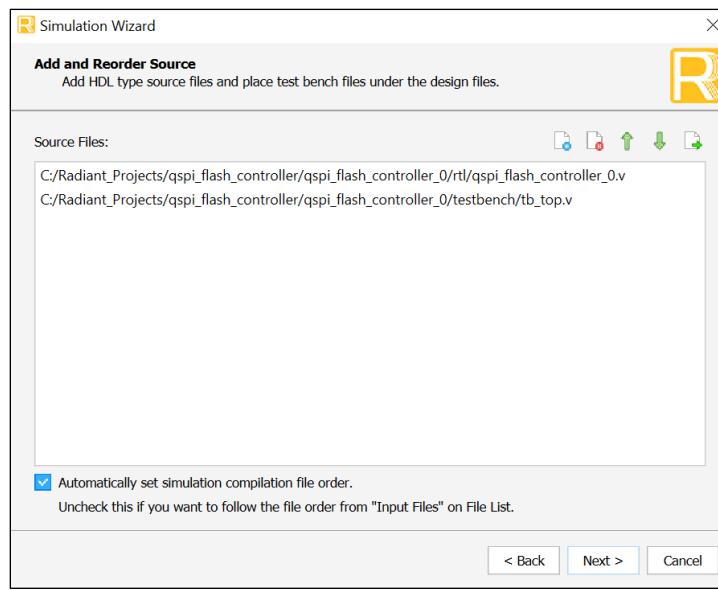

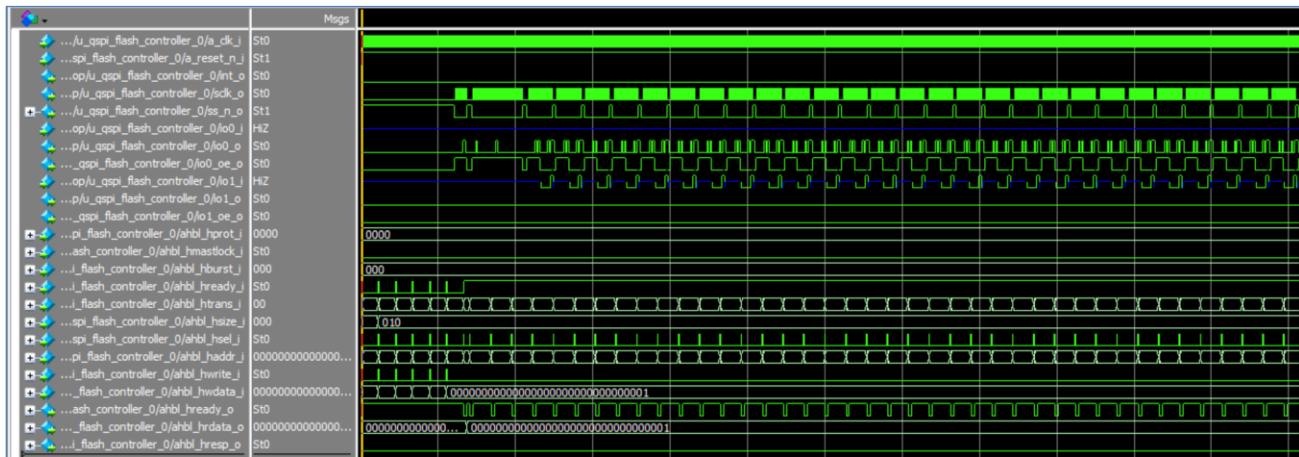

| Address Depth                        | <b>16, 32, 64, 128, 256, 512</b>                                                                                                          | Specifies the number of FIFO levels.<br>Visible and editable only when <i>Enable Receive FIFO == Checked</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                 |