# **Internal Flash Controller IP for MachXO5-NX**

IP Version: v2.3.0

## **User Guide**

FPGA-IPUG-02174-1.7

December 2025

## Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Inclusive Language

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language [FAQ 6878](#) for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## Contents

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| Contents .....                                                          | 3  |

| Abbreviations in This Document.....                                     | 7  |

| 1. Introduction .....                                                   | 8  |

| 1.1. Overview of the IP .....                                           | 8  |

| 1.2. Quick Facts .....                                                  | 8  |

| 1.3. IP Support Summary .....                                           | 8  |

| 1.4. Features .....                                                     | 9  |

| 1.5. Licensing and Ordering Information .....                           | 9  |

| 1.6. Hardware Support.....                                              | 9  |

| 1.7. Naming Conventions .....                                           | 9  |

| 1.7.1. Nomenclature.....                                                | 9  |

| 1.7.2. Signal Names .....                                               | 9  |

| 1.7.3. Attribute Names .....                                            | 9  |

| 2. Functional Description.....                                          | 10 |

| 2.1. IP Architecture Overview .....                                     | 10 |

| 2.2. Clocking and Reset .....                                           | 11 |

| 2.2.1. Clocking and Reset Overview .....                                | 11 |

| 2.3. Block Partitioning .....                                           | 13 |

| 2.4. Setting Initial Data in Flash Memory .....                         | 18 |

| 2.4.1. Binary File .....                                                | 18 |

| 2.4.2. Hexadecimal File .....                                           | 18 |

| 2.5. Transaction Offset Computation.....                                | 18 |

| 2.6. Programming Flow .....                                             | 20 |

| 2.6.1. Write Access Operation 1.....                                    | 20 |

| 2.6.2. Write Access Operation 2.....                                    | 22 |

| 2.6.3. Read Access Operation 1.....                                     | 23 |

| 2.6.4. Read Access Operation 2.....                                     | 24 |

| 2.6.5. Erase Operation.....                                             | 25 |

| 2.6.6. Normal Operation (Erase Write Read) .....                        | 26 |

| 2.6.7. Normal Operation (Erase Write Read) with TRANSACTION_STATUS..... | 27 |

| 3. IP Parameter Description.....                                        | 30 |

| 3.1. General.....                                                       | 30 |

| 3.2. CFG0/1/2 and UFM0/1/2 Settings .....                               | 31 |

| 3.3. USERDATA0 to USERDATA8 Settings.....                               | 32 |

| 3.4. Oscillator Setting .....                                           | 35 |

| 3.5. Access Mode .....                                                  | 35 |

| 4. Signal Description .....                                             | 36 |

| 5. Register Description .....                                           | 38 |

| 5.1. Overview .....                                                     | 38 |

| 5.2. UFM_CTRL_REG Register .....                                        | 38 |

| 5.3. TRANSACTION_ADDR Register .....                                    | 39 |

| 5.4. WR_FIFO_DATA Register.....                                         | 39 |

| 5.5. RD_FIFO_DATA Register.....                                         | 39 |

| 5.6. TRANSACTION_CTRL Register .....                                    | 40 |

| 5.7. FIFO_STATUS Register .....                                         | 41 |

| 5.8. FIFO_CTRL Register .....                                           | 41 |

| 5.9. INT_STATUS Register.....                                           | 42 |

| 5.10. INT_ENABLE Register .....                                         | 42 |

| 5.11. INT_SET Register .....                                            | 43 |

| 5.12. TRANSACTION_STATUS Register .....                                 | 43 |

| 6. Example Design.....                                                  | 44 |

| 6.1. Example Design Supported Configuration .....                       | 44 |

---

|                                                        |    |

|--------------------------------------------------------|----|

| 6.2. Overview of the Example Design and Features ..... | 46 |

| 6.3. Example Design Components.....                    | 47 |

| 6.4. Generating the Example Design.....                | 47 |

| 6.5. Hardware Testing .....                            | 50 |

| 6.5.1. Hardware Testing Setup .....                    | 50 |

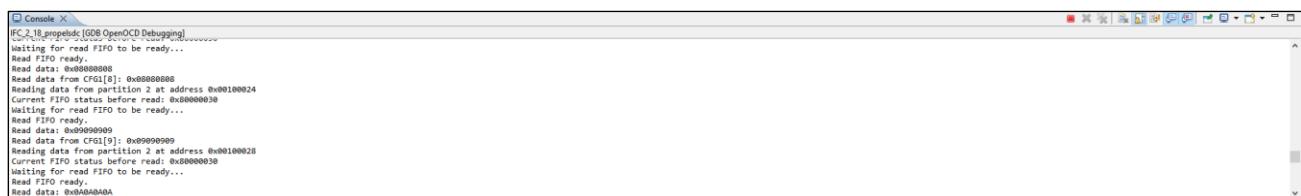

| 6.5.2. Expected Output .....                           | 50 |

| 7. Designing with the IP .....                         | 51 |

| 7.1. Generating and Instantiating the IP .....         | 51 |

| Appendix A. Resource Utilization .....                 | 55 |

| References .....                                       | 57 |

| Technical Support Assistance .....                     | 58 |

| Revision History .....                                 | 59 |

## Figures

|                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. Internal Flash Controller Block Diagram (Default) .....                                       | 10 |

| Figure 2.2. Clocking and Reset with Internal Oscillator .....                                             | 11 |

| Figure 2.3. Clocking and Reset with Internal Oscillator ( <i>Use HFCLK for LMMI CLK = Checked</i> ) ..... | 12 |

| Figure 2.4. Clocking and Reset with Oscillator Soft IP .....                                              | 12 |

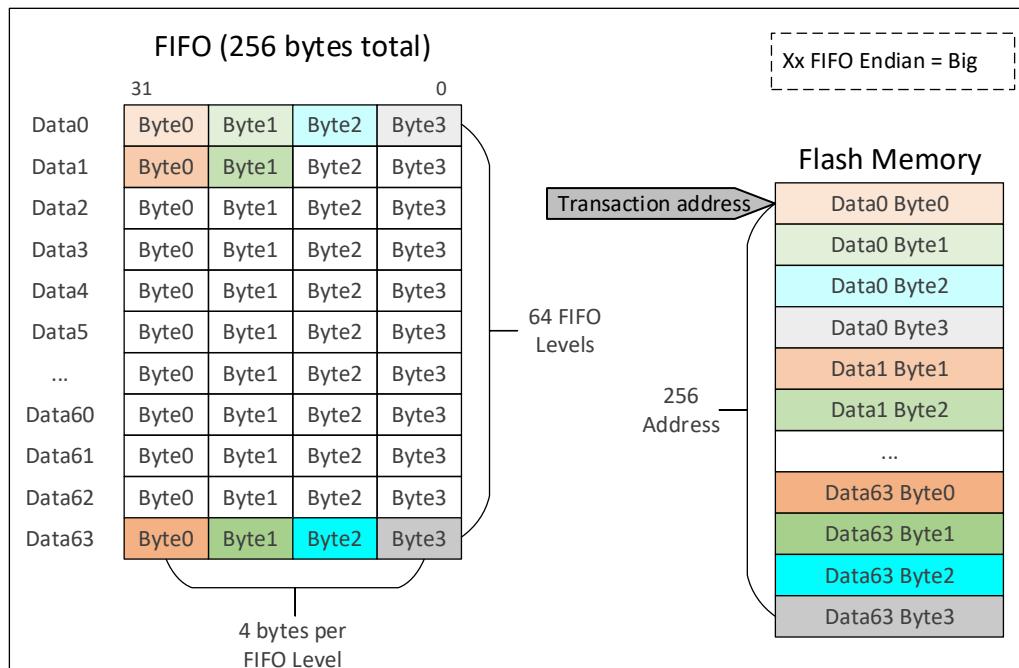

| Figure 2.5. FIFO and Flash Memory Relationship (Big Endian) .....                                         | 21 |

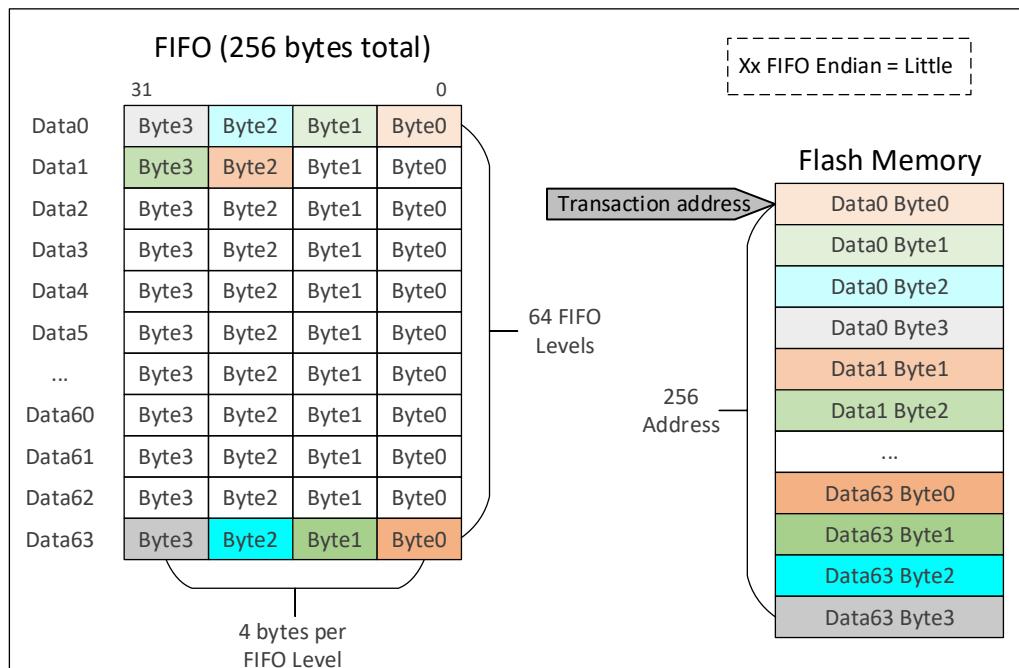

| Figure 2.6. FIFO and Flash Memory Relationship (Little Endian) .....                                      | 21 |

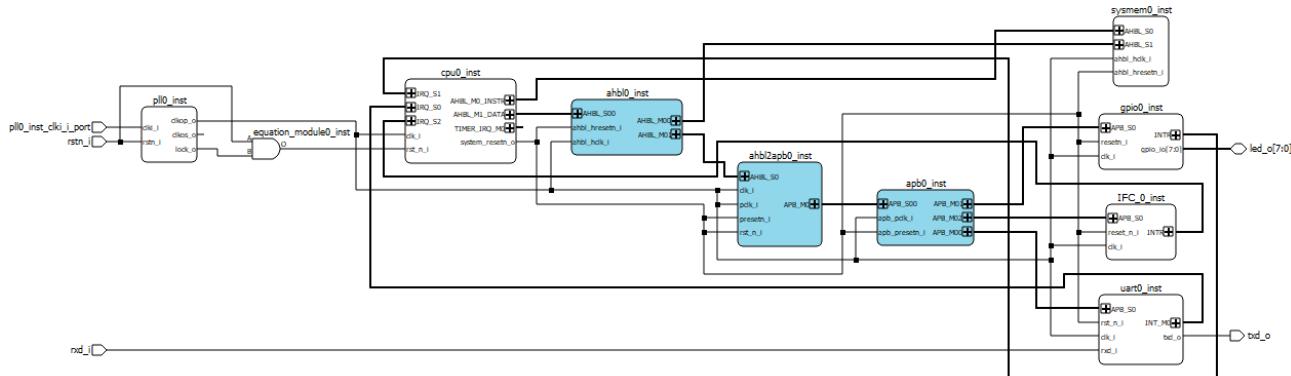

| Figure 6.1. Internal Flash Controller IP for MachXO5-NX in Propel SoC Project .....                       | 46 |

| Figure 6.2. Sample C Code Test Routine .....                                                              | 46 |

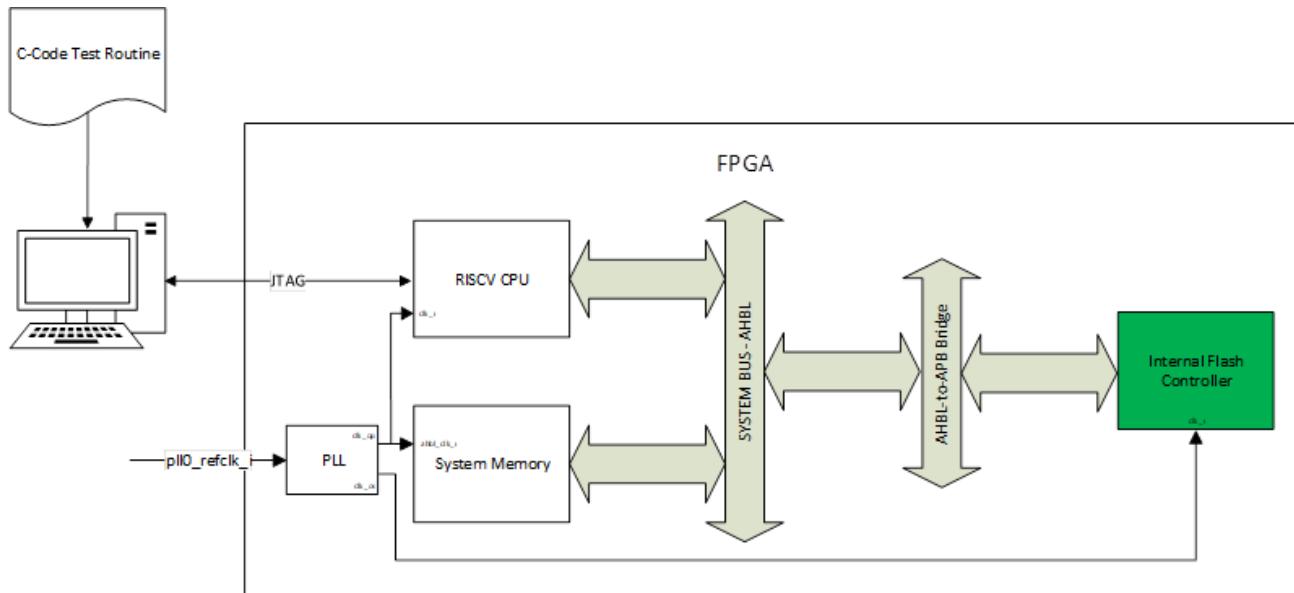

| Figure 6.3. Internal Flash Controller Example Design Block Diagram .....                                  | 47 |

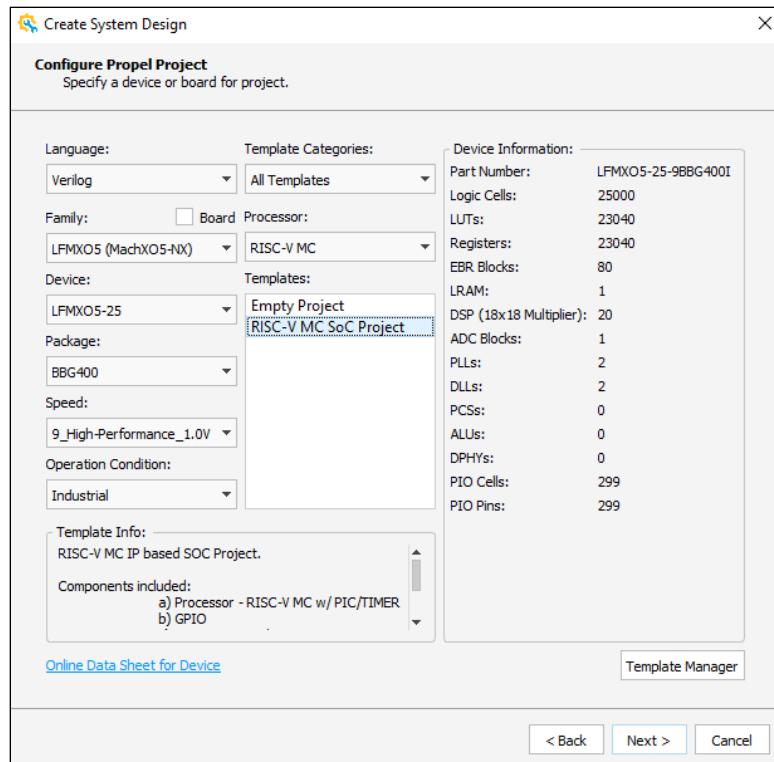

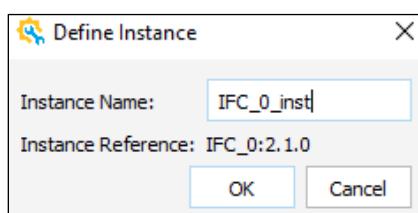

| Figure 6.4. Create System Design .....                                                                    | 48 |

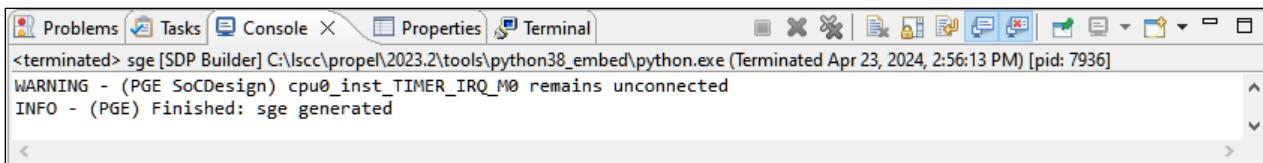

| Figure 6.5. Build SoC Project Result .....                                                                | 49 |

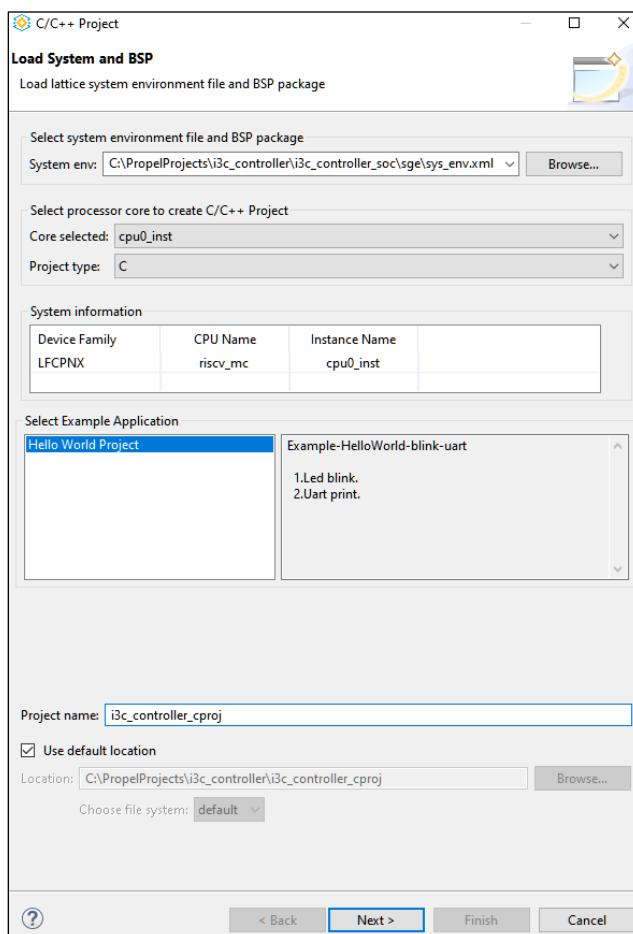

| Figure 6.6. C/C++ Project .....                                                                           | 49 |

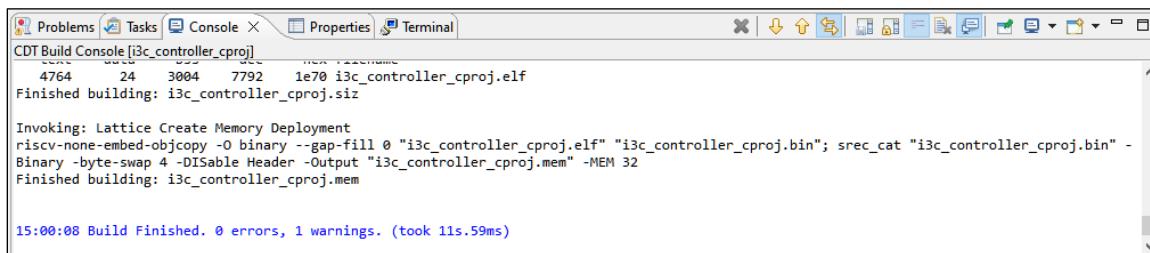

| Figure 6.7. Build C/C++ Project Result .....                                                              | 50 |

| Figure 6.8. C/C++ Project Log .....                                                                       | 50 |

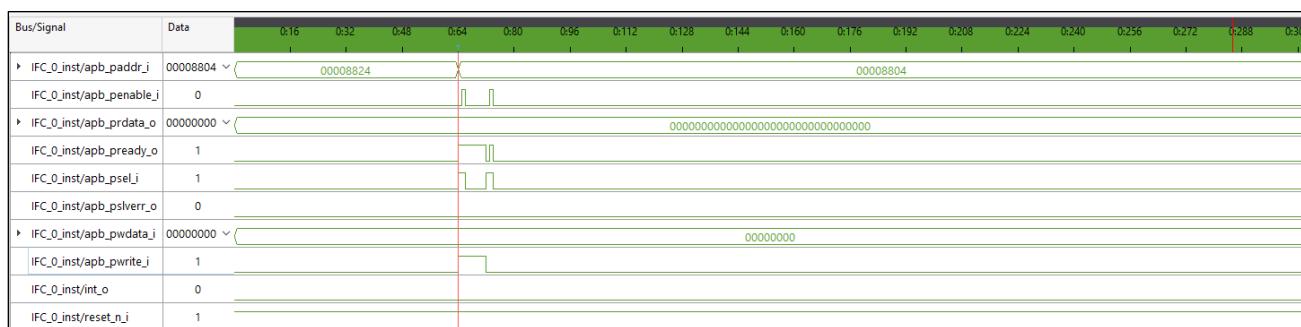

| Figure 6.9. APB Interface Reveal Waveform .....                                                           | 50 |

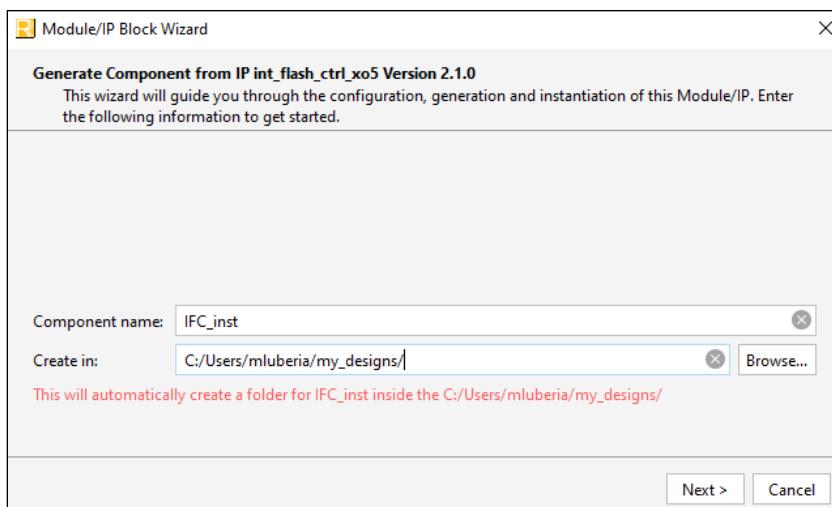

| Figure 7.1. Generating Internal Flash Controller Using Module/IP Block Wizard .....                       | 51 |

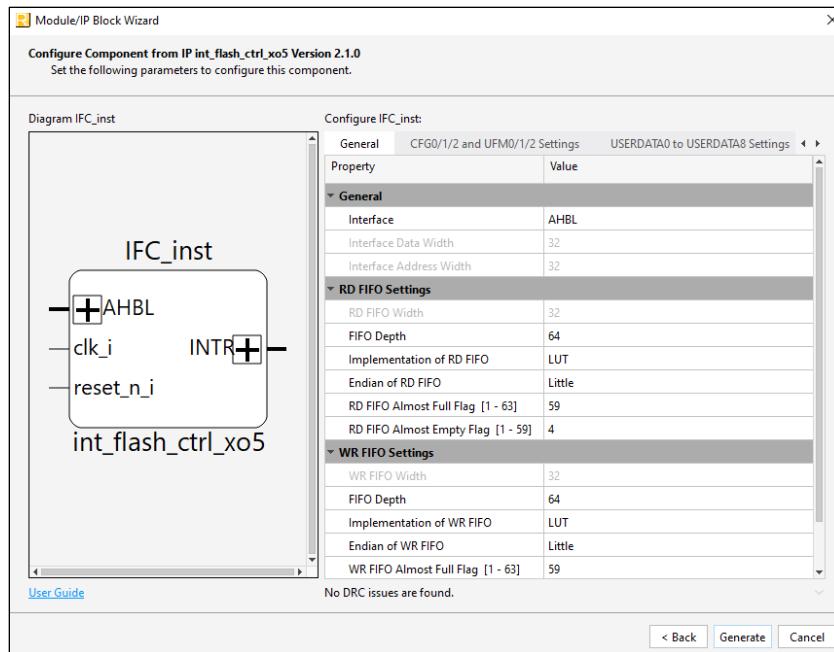

| Figure 7.2. Module/IP Block Wizard – General Tab .....                                                    | 52 |

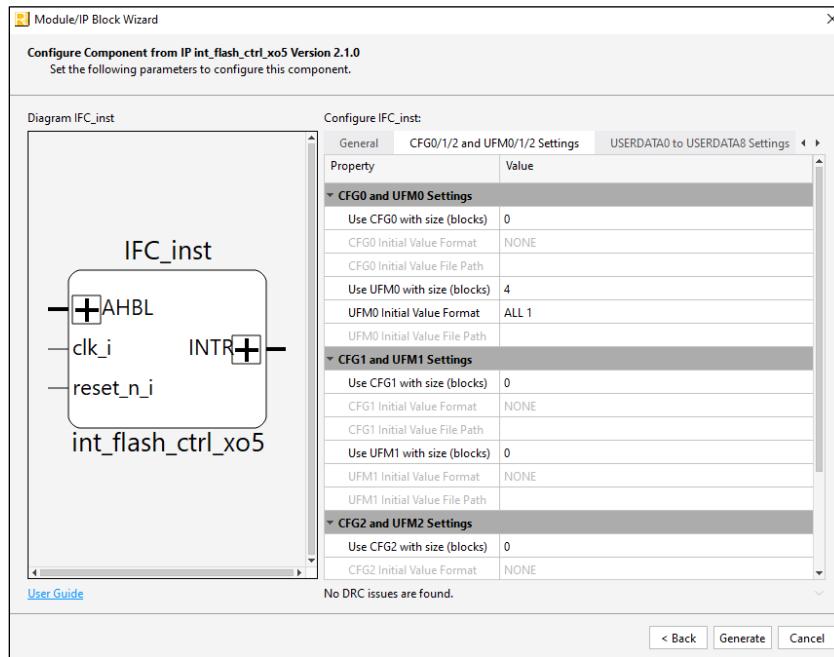

| Figure 7.3. Module/IP Block Wizard – CFG0/1/2 and UFM0/1/2 Settings Tab .....                             | 52 |

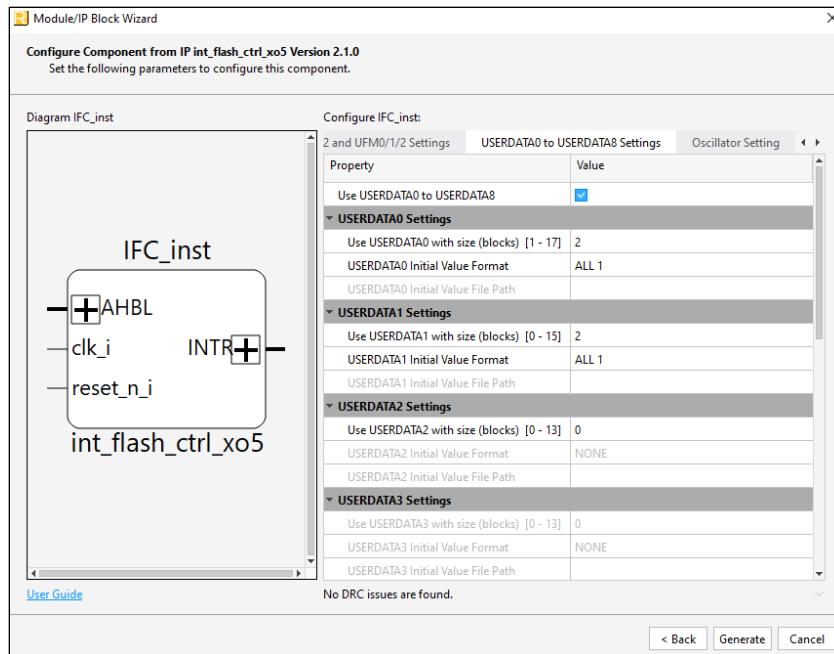

| Figure 7.4. Module/IP Block Wizard – USERDATA0 to USERDATA8 Settings Tab .....                            | 53 |

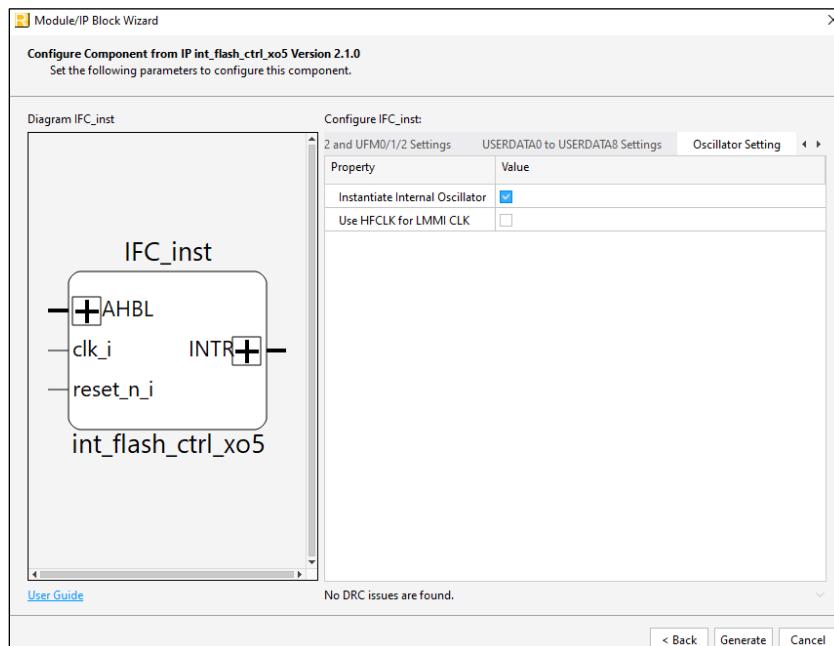

| Figure 7.5. Module/IP Block Wizard – Oscillator Setting Tab .....                                         | 53 |

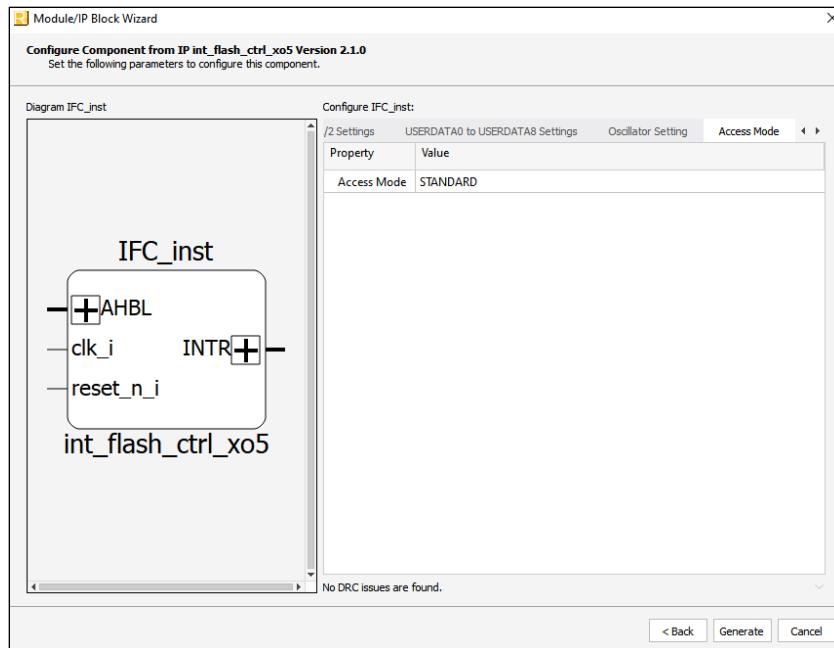

| Figure 7.6. Module/IP Block Wizard – Access Mode Tab .....                                                | 54 |

## Tables

|                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------|----|

| Table 1.1. Summary of the Internal Flash Controller IP for MachXO5-NX.....                                 | 8  |

| Table 1.2. Internal Flash Controller IP for MachXO5-NX Support Readiness .....                             | 8  |

| Table 2.1. Flash Memory Map for LFMXO5-25 Device .....                                                     | 13 |

| Table 2.2. Flash Memory Map for LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T Devices.....              | 13 |

| Table 2.3. Flash Memory Map for LFMXO5-55T and LFMXO5-100T Devices .....                                   | 14 |

| Table 2.4. Different Combinations of CFGx/UFMx Block Size.....                                             | 15 |

| Table 2.5. Sample Settings 1.....                                                                          | 15 |

| Table 2.6. Sample Settings 2.....                                                                          | 16 |

| Table 2.7. Flash Memory Partition Initialization Options .....                                             | 18 |

| Table 2.8. Flash Memory Map (Partition) for LFMXO5-25 Device .....                                         | 18 |

| Table 2.9. Flash Memory Map (Partition) for LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T Devices ..... | 19 |

| Table 2.10. Flash Memory Map (Partition) for LFMXO5-55T and LFMXO5-100T Devices.....                       | 19 |

| Table 3.1. General Attributes .....                                                                        | 30 |

| Table 3.2. CFG0/1/2 and UFM0/1/2 Attributes .....                                                          | 31 |

| Table 3.3. USERDATA0 to USERDATA8 Attributes .....                                                         | 32 |

| Table 3.4. Oscillator Attributes .....                                                                     | 35 |

| Table 3.5. Access Mode Attribute.....                                                                      | 35 |

| Table 4.1. Internal Flash Controller Ports .....                                                           | 36 |

| Table 5.1. Register Access Types .....                                                                     | 38 |

| Table 5.2. Summary of Internal Flash Controller IP for MachXO5-NX Registers .....                          | 38 |

| Table 5.3. UFM_CTRL_REG Register .....                                                                     | 38 |

| Table 5.4. TRANSACTION_ADDR Register.....                                                                  | 39 |

| Table 5.5. WR_FIFO_DATA Register .....                                                                     | 39 |

| Table 5.6. RD_FIFO_DATA Register .....                                                                     | 39 |

| Table 5.7. TRANSACTION_CTRL Register .....                                                                 | 40 |

| Table 5.8. FIFO_STATUS Register.....                                                                       | 41 |

| Table 5.9. FIFO_CTRL Register .....                                                                        | 41 |

| Table 5.10. INT_STATUS Register .....                                                                      | 42 |

| Table 5.11. INT_ENABLE Register .....                                                                      | 42 |

| Table 5.12. INT_SET Register .....                                                                         | 43 |

| Table 5.13. TRANSACTION_STATUS Register .....                                                              | 43 |

| Table 6.1. Internal Flash Controller IP for MachXO5-NX Configuration Supported by the Example Design ..... | 44 |

| Table A.1. Resource Utilization Using LFMXO5-25-7BBG256C .....                                             | 55 |

| Table A.2. Resource Utilization Using LFMXO5-25-9BBG256C .....                                             | 56 |

## Abbreviations in This Document

A list of abbreviations used in this document.

| Abbreviation | Definition                                  |

|--------------|---------------------------------------------|

| AHB-L        | Advanced High-Performance Bus – Lite        |

| AMBA         | Advanced Microcontroller Bus Architecture   |

| APB          | Advanced Peripheral Bus                     |

| CPU          | Central Processing Unit                     |

| EBR          | Embedded Block RAM                          |

| FIFO         | First In, First Out                         |

| FPGA         | Field Programmable Gate Array               |

| GPIO         | General Purpose Input/Output                |

| GUI          | Graphical User Interface                    |

| HDL          | Hardware Description Language               |

| IP           | Intellectual Property                       |

| ISR          | Interrupt Service Routine                   |

| JTAG         | Joint Test Action Group                     |

| LMMI         | Lattice Memory Mapped Interface             |

| LUT          | Look-Up Table                               |

| PLL          | Phase-Locked Loop                           |

| RISC-V       | Reduced Instruction Set Computer V          |

| SDK          | Software Development Kit                    |

| SoC          | System-on-Chip                              |

| SPI          | Serial Peripheral Interface                 |

| SSPI         | Target Serial Peripheral Interface          |

| UART         | Universal Asynchronous Receiver/Transmitter |

| UFM          | User Flash Memory                           |

# 1. Introduction

The Lattice MachXO5™-NX device contains an internal flash memory, which can be accessed for various purposes including configuration data storage. This document describes the Internal Flash Controller IP for MachXO5-NX.

## 1.1. Overview of the IP

The Internal Flash Controller IP for MachXO5-NX enables you to access the internal flash memory of the MachXO5-NX device using the Advanced High-Performance Bus – Lite (AHB-Lite) or Advanced Peripheral Bus (APB) interface.

## 1.2. Quick Facts

**Table 1.1. Summary of the Internal Flash Controller IP for MachXO5-NX**

|                             |                          |                                                                                                          |

|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|

| <b>IP Requirements</b>      | Supported Devices        | MachXO5-NX (except LFMXO5-15D, LFMXO5-55TD)                                                              |

|                             | IP Changes <sup>1</sup>  | Refer to the <a href="#">Internal Flash Controller IP for MachXO5-NX Release Notes (FPGA-RN-02085)</a> . |

| <b>Resource Utilization</b> | Supported User Interface | AHB-Lite, APB                                                                                            |

|                             | Resources                | Refer to <a href="#">Appendix A. Resource Utilization</a> .                                              |

| <b>Design Tool Support</b>  | Lattice Implementation   | IP Core v2.3.0 – Lattice Propel™ 2025.2 Design Environment                                               |

|                             | Synthesis                | Synopsis® Synplify Pro® for Lattice, Lattice Synthesis Engine                                            |

|                             | Simulation               | Not supported                                                                                            |

| <b>Driver Support</b>       | API Reference            | Refer to the <a href="#">Internal Flash Controller Driver API Reference (FPGA-TN-02421)</a> .            |

**Note:**

1. In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

## 1.3. IP Support Summary

**Table 1.2. Internal Flash Controller IP for MachXO5-NX Support Readiness**

| Device Family | IP                                       | Interface | FIFO Depth | FIFO Endian (Write/Read) | Instantiate Internal Oscillator | Hardware Validated |

|---------------|------------------------------------------|-----------|------------|--------------------------|---------------------------------|--------------------|

| LFMXO5-25     | Internal Flash Controller for MachXO5-NX | APB       | 64         | Little/Little            | Yes                             | Yes                |

|               |                                          | AHB-Lite  | 64         | Little/Little            | Yes                             | Yes                |

| LFMXO5-25     | Internal Flash Controller for MachXO5-NX | APB       | 64         | Little/Little            | No                              | Yes                |

|               |                                          | AHB-Lite  | 64         | Little/Little            | No                              | Yes                |

| LFMXO5-25     | Internal Flash Controller for MachXO5-NX | APB       | 32         | Big/Little               | No                              | No                 |

|               |                                          | AHB-Lite  | 32         | Little/Big               | No                              | No                 |

## 1.4. Features

Key features of the Internal Flash Controller IP for MachXO5-NX include:

- AHB-Lite interface

- APB interface

- Initial user data to be programmed into the flash memory

- Up to 50 MHz input clock frequency

## 1.5. Licensing and Ordering Information

The Internal Flash Controller IP for MachXO5-NX is provided at no additional cost with the Lattice Propel design environment.

## 1.6. Hardware Support

Refer to the [Example Design](#) section for more information on the board used

## 1.7. Naming Conventions

### 1.7.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.7.2. Signal Names

Signal names that end with:

- `_n` are active low signals (asserted when value is logic 0)

- `_i` are input signals

- `_o` are output signals

### 1.7.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (*Attribute Name*).

## 2. Functional Description

### 2.1. IP Architecture Overview

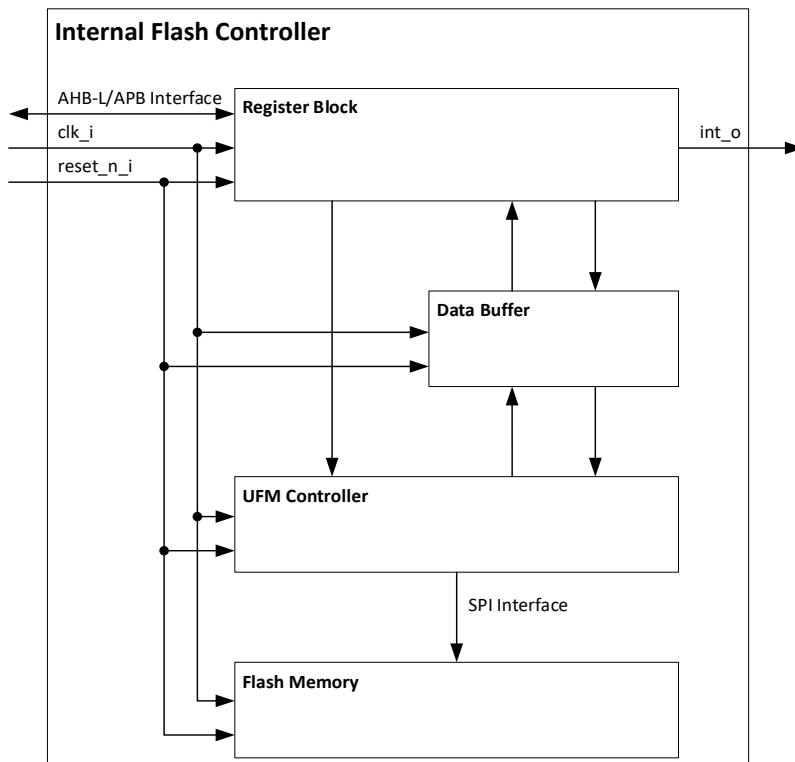

The Internal Flash Controller IP for MachXO5-NX has a system bus interface to access the registers. The input bus can be configured through IP attributes as either an AHB-Lite or APB interface. This IP also has four sub-blocks: register block, data buffer, controller, and flash memory. [Figure 2.1](#) shows the connections of the sub-blocks.

**Note:** With SSPI persistence enabled in user mode, there is a limitation on operation of the SSPI/JTAG bus when using the Internal Flash Controller IP for MachXO5-NX. Do not access the SSPI/JTAG port when accessing flash memory using the Internal Flash Controller IP for MachXO5-NX or vice versa.

The register block handles all incoming bus transactions. It stores the register values and provides them to the controller. It also performs write or read access to the data buffer depending on the register access. The data buffer implements two FIFO buffers to temporarily store read data from and write data to the flash memory. The controller performs the transactions to the flash memory based on the register values. It also performs write or read access to the data buffer depending on the type of transaction with the flash memory. The flash memory receives the transactions from the controller.

**Figure 2.1. Internal Flash Controller Block Diagram (Default)**

## 2.2. Clocking and Reset

The Internal Flash Controller IP for MachXO5-NX contains two internal clock domains: clk\_i and Immi\_clk\_i. These two clocks must always operate at the same frequency to ensure proper synchronization and reliable operation of the IP. The Internal Flash Controller IP for MachXO5-NX also contains three internal resets: asynchronous resets reset\_n\_i and Immi\_resetn\_i, and soft reset (accessible through the register).

### 2.2.1. Clocking and Reset Overview

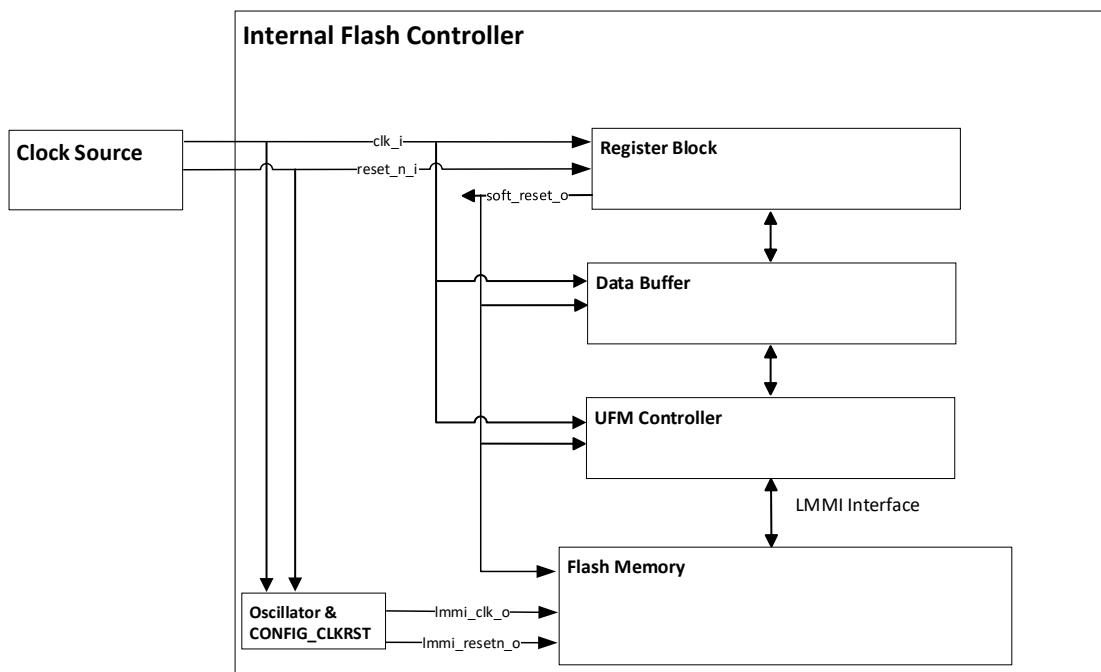

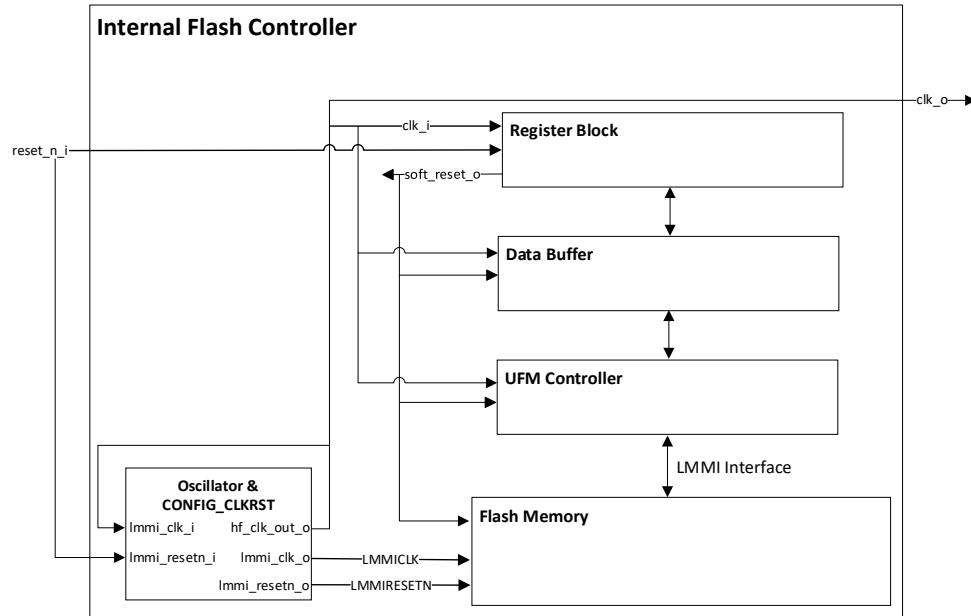

When *Instantiate Internal Oscillator* is enabled, Immi\_clk\_i and Immi\_resetn\_i for the flash memory are internally generated using an internal oscillator as shown in [Figure 2.2](#). The CONFIG\_CLKRST module generates the required clock and signals to ensure proper IP operation. When *Use HFCLK for LMMI CLK* is enabled, the register block, data buffer, and UFM controller use the high-frequency output of the internal oscillator as the clock signal as shown in [Figure 2.3](#). If you are using only clk\_i for all blocks including the flash memory, the frequency of the clock source must be set to less than or equal to 50 MHz.

**Figure 2.2. Clocking and Reset with Internal Oscillator**

Figure 2.3. Clocking and Reset with Internal Oscillator (Use HFCLK for LMMI CLK = Checked)

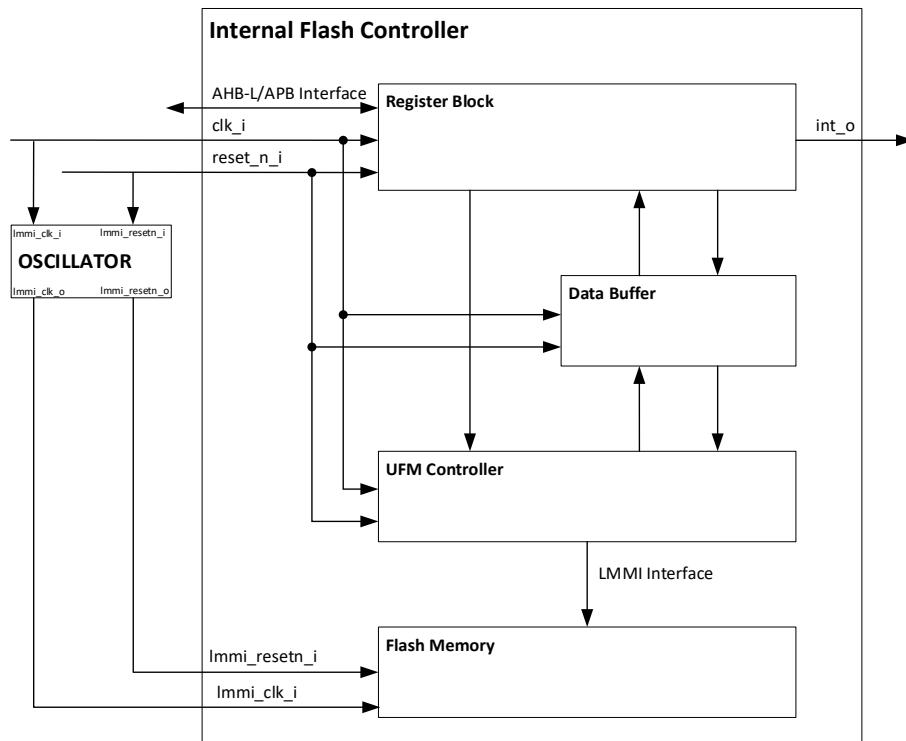

If you do not want to instantiate the oscillator internally in the IP and intend to share the clock source with other IPs, you must disable *Instantiate Internal Oscillator* and instantiate an oscillator soft IP instead due to physical routing restrictions and for proper handling of clocking and reset. Figure 2.4 shows the connection of the oscillator soft IP to the ports of the Internal Flash Controller IP for MachXO5-NX. Immi\_clk\_o and Immi\_resetn\_o of the oscillator must drive Immi\_clk\_i and Immi\_resetn\_i, respectively. The inputs to clk\_i and reset\_n\_i can be used for other modules.

Figure 2.4. Clocking and Reset with Oscillator Soft IP

## 2.3. Block Partitioning

**Table 2.1** shows the whole memory map of the LFMXO5-25 device's flash memory. **Table 2.2** shows the whole memory map of the LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T devices' flash memory. **Table 2.3** shows the whole memory map of the LFMXO5-55T and LFMXO5-100T devices' flash memory. You can modify the partition sizes by changing the attributes prior to IP generation. There are five options for configuring each of the three CFGx/UFMx partition sizes as shown in **Table 2.4**. The rules for configuring the partition sizes of USERDATAx are described in **Table 3.3**. **Table 2.5** and **Table 2.6** show sample settings for different flash partition block sizes.

**Table 2.1. Flash Memory Map for LFMXO5-25 Device**

| Block Start Address<br>(24-Bit Byte Address) | Block End Address<br>(24-Bit Byte Address) | Block Count     | Sector Count     | Contents                                                                                                          |

|----------------------------------------------|--------------------------------------------|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------|

| 00<br>(0x00_0000)                            | 00<br>(0x00_FFFF)                          | 1               | 16               | —                                                                                                                 |

| 01<br>(0x01_0000)                            | 11<br>(0x0B_FFFF)                          | 11              | 176              | CFG0                                                                                                              |

| 12<br>(0x0C_0000)                            | 15<br>(0x0F_FFFF)                          | 4               | 64               | UFM0                                                                                                              |

| 16<br>(0x10_0000)                            | 26<br>(0x1A_FFFF)                          | 11              | 176              | CFG1                                                                                                              |

| 27<br>(0x1B_0000)                            | 30<br>(0x1E_FFFF)                          | 4               | 64               | UFM1                                                                                                              |

| 31<br>(0x1F_0000)                            | 41<br>(0x29_FFFF)                          | 11              | 176              | CFG2                                                                                                              |

| 42<br>(0x2A_0000)                            | 45<br>(0x2D_FFFF)                          | 4               | 64               | UFM2                                                                                                              |

| 46<br>(0x2E_0000)                            | 63<br>(0x3E_FFFF)                          | Total $\leq$ 17 | Total $\leq$ 272 | USERDATA0<br>USERDATA1<br>USERDATA2<br>USERDATA3<br>USERDATA4<br>USERDATA5<br>USERDATA6<br>USERDATA7<br>USERDATA8 |

**Note:** A single page has 256 bytes of data.

**Table 2.2. Flash Memory Map for LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T Devices**

| Block Start Address<br>(24-Bit Byte Address) | Block End Address<br>(24-Bit Byte Address) | Block Count | Sector Count | Contents  |

|----------------------------------------------|--------------------------------------------|-------------|--------------|-----------|

| 00<br>(0x00_0000)                            | 00<br>(0x00_FFFF)                          | 1           | 16           | —         |

| 01<br>(0x01_0000)                            | 21<br>(0x15_FFFF)                          | 21          | 336          | CFG0      |

| 22<br>(0x16_0000)                            | 28<br>(0x1C_FFFF)                          | 7           | 112          | UFM0      |

| 29<br>(0x1D_0000)                            | 49<br>(0x31_FFFF)                          | 21          | 336          | CFG1      |

| 50<br>(0x32_0000)                            | 56<br>(0x38_FFFF)                          | 7           | 112          | UFM1      |

| 57                                           | 62                                         | 6           | 96           | USERDATA0 |

| Block Start Address<br>(24-Bit Byte Address) | Block End Address<br>(24-Bit Byte Address) | Block Count | Sector Count | Contents                                                                                             |

|----------------------------------------------|--------------------------------------------|-------------|--------------|------------------------------------------------------------------------------------------------------|

| 0x39_0000                                    | (0x3E_FFFF)                                |             |              |                                                                                                      |

| 64<br>(0x40_0000)                            | 84<br>(0x54_FFFF)                          | 21          | 336          | CFG2                                                                                                 |

| 85<br>(0x55_0000)                            | 91<br>(0x5B_FFFF)                          | 7           | 112          | UFM2                                                                                                 |

| 92<br>(0x5C_0000)                            | 127<br>(0x7F_FFFF)                         | Total ≤ 36  | Total ≤ 576  | USERDATA1<br>USERDATA2<br>USERDATA3<br>USERDATA4<br>USERDATA5<br>USERDATA6<br>USERDATA7<br>USERDATA8 |

**Note:** A single page has 256 bytes of data.

**Table 2.3. Flash Memory Map for LFMXO5-55T and LFMXO5-100T Devices**

| Block Start Address<br>(24-Bit Byte Address) | Block End Address<br>(24-Bit Byte Address) | Block Count | Sector Count | Contents                                                                                                          |

|----------------------------------------------|--------------------------------------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| 00<br>(0x00_0000)                            | 00<br>(0x00_FFFF)                          | 1           | 16           | —                                                                                                                 |

| 01<br>(0x01_0000)                            | 33<br>(0x21_FFFF)                          | 33          | 528          | CFG0                                                                                                              |

| 34<br>(0x22_0000)                            | 48<br>(0x30_FFFF)                          | 15          | 240          | UFM0                                                                                                              |

| 49<br>(0x31_0000)                            | 81<br>(0x51_FFFF)                          | 33          | 528          | CFG1                                                                                                              |

| 82<br>(0x52_0000)                            | 96<br>(0x60_FFFF)                          | 15          | 240          | UFM1                                                                                                              |

| 97<br>(0x61_0000)                            | 129<br>(0x81_FFFF)                         | 33          | 528          | CFG2                                                                                                              |

| 130<br>(0x82_0000)                           | 144<br>(0x90_FFFF)                         | 15          | 240          | UFM2                                                                                                              |

| 145<br>(0x91_0000)                           | 255<br>(0xFE_FFFF)                         | Total ≤ 110 | Total ≤ 1760 | USERDATA0<br>USERDATA1<br>USERDATA2<br>USERDATA3<br>USERDATA4<br>USERDATA5<br>USERDATA6<br>USERDATA7<br>USERDATA8 |

**Note:** One page is composed of 256 bytes of data. One 4 KB sector is equivalent to 16 pages while one 64 KB block is equivalent to 256 pages.

For the LFMXO5-55T and LFMXO5-100T devices, CFGx and UFMx partitions have 33 and 15 64 KB blocks, respectively. CFGx and UFMx pairs can be combined to form 48 64 KB blocks. There are CFG0, CFG1, CFG2, UFM0, UFM1, and UFM2. USERDATA0 to USERDATA8 have a total of 110 64 KB blocks. [Table 2.3](#) shows the boundary address for each memory partition of LFMXO5-55T and LFMXO5-100T devices.

**Table 2.4. Different Combinations of CFGx/UFMx Block Size**

| Item No.                                                | CFGx Block Count | UFMx Block Count | Use Partition Setting   | Description                                                                                 |

|---------------------------------------------------------|------------------|------------------|-------------------------|---------------------------------------------------------------------------------------------|

| <b>LFMXO5-25</b>                                        |                  |                  |                         |                                                                                             |

| 1                                                       | 15               | 0                | Use CFGx with size = 15 | Only one partition CFGx having 15 block size                                                |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| 2                                                       | 11               | 0                | Use CFGx with size = 11 | Only one partition CFGx having 11 block size; do not access the partition for UFMx          |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| 3                                                       | 0                | 4                | Use CFGx with size = 0  | Only one partition UFMx having 4 block size; do not access the partition for CFGx           |

|                                                         |                  |                  | Use UFMx with size = 4  |                                                                                             |

| 4                                                       | 11               | 4                | Use CFGx with size = 11 | Two partitions CFGx having 11 block size and UFMx having 4 block size                       |

|                                                         |                  |                  | Use UFMx with size = 4  |                                                                                             |

| 5                                                       | 0                | 0                | Use CFGx with size = 0  | No partition is selected. Do not access both.                                               |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| <b>LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T</b> |                  |                  |                         |                                                                                             |

| 1                                                       | 28               | 0                | Use CFGx with size = 28 | Only one partition CFGx having 28 block size                                                |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| 2                                                       | 21               | 0                | Use CFGx with size = 21 | Only one partition CFGx having 21 block size; do not access the partition for UFMx          |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| 3                                                       | 0                | 7                | Use CFGx with size = 0  | Only one partition UFMx having 7 block size; do not access the partition for CFGx           |

|                                                         |                  |                  | Use UFMx with size = 7  |                                                                                             |

| 4                                                       | 21               | 7                | Use CFGx with size = 21 | Two partitions CFGx having 21 block size and UFMx having 7 block size                       |

|                                                         |                  |                  | Use UFMx with size = 7  |                                                                                             |

| 5                                                       | 0                | 0                | Use CFGx with size = 0  | No partition is selected. Do not access both.                                               |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| <b>LFMXO5-55T and LFMXO5-100T</b>                       |                  |                  |                         |                                                                                             |

| 1                                                       | 48               | 0                | Use CFGx with size = 48 | Only one partition CFGx having 48 block size.                                               |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| 2                                                       | 33               | 0                | Use CFGx with size = 33 | Only one partition CFGx having 33 block size; you should not access the partition for UFMx. |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

| 3                                                       | 0                | 15               | Use CFGx with size = 0  | Only one partition UFMx having 15 block size; you should not access the partition for CFGx. |

|                                                         |                  |                  | Use UFMx with size = 15 |                                                                                             |

| 4                                                       | 33               | 15               | Use CFGx with size = 33 | Two partitions CFGx having 33 block size and UFMx having 15 block size.                     |

|                                                         |                  |                  | Use UFMx with size = 15 |                                                                                             |

| 5                                                       | 0                | 0                | Use CFGx with size = 0  | Neither CFG nor UFMx should be accessed.                                                    |

|                                                         |                  |                  | Use UFMx with size = 0  |                                                                                             |

**Table 2.5. Sample Settings 1**

| Block Start Address | Block End Address | Block Count | Use Partition Setting   | Contents      |

|---------------------|-------------------|-------------|-------------------------|---------------|

| <b>LFMXO5-25</b>    |                   |             |                         |               |

| 1                   | 15                | 15          | Use CFG0 with size = 15 | CFG0          |

|                     |                   |             | Use UFM0 with size = 0  | Do not access |

| 16                  | 26                | 11          | Use CFG1 with size = 11 | CFG1          |

| NA                  | NA                | 0           | Use UFM1 with size = 0  | Do not access |

| NA                  | NA                | 0           | Use CFG2 with size = 0  | Do not access |

| 42                  | 45                | 4           | Use UFM2 with size = 4  | UFM2          |

| 46                  | 55                | 10          | USERDATA0 Size = 10     | USERDATA0     |

| 56                  | 63                | 8           | USERDATA1 Size = 8      | USERDATA1     |

| Block Start Address                                     | Block End Address | Block Count | Use Partition Setting    | Contents      |

|---------------------------------------------------------|-------------------|-------------|--------------------------|---------------|

| NA                                                      | NA                | 0           | USERDATA2 Size = 0       | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| <b>LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T</b> |                   |             |                          |               |

| 1                                                       | 28                | 28          | Use CFG0 with size = 28  | CFG0          |

| NA                                                      | NA                | 0           | Use UFM0 with size = 0   | Do not access |

| 29                                                      | 49                | 21          | Use CFG1 with size = 21  | CFG1          |

| NA                                                      | NA                | 0           | Use UFM1 with size = 0   | Do not access |

| 57                                                      | 62                | 6           | USERDATA0 Size = 6       | USERDATA0     |

| NA                                                      | NA                | 0           | Use CFG2 with size = 0   | Do not access |

| 85                                                      | 91                | 7           | Use UFM2 with size = 7   | UFM2          |

| 92                                                      | 95                | 4           | USERDATA1 Size = 4       | USERDATA1     |

| 96                                                      | 99                | 4           | USERDATA2 Size = 4       | USERDATA2     |

| 100                                                     | 103               | 4           | USERDATA3 Size = 4       | USERDATA3     |

| 104                                                     | 107               | 4           | USERDATA4 Size = 4       | USERDATA4     |

| 108                                                     | 111               | 4           | USERDATA5 Size = 4       | USERDATA5     |

| 112                                                     | 115               | 4           | USERDATA6 Size = 4       | USERDATA6     |

| 116                                                     | 119               | 4           | USERDATA7 Size = 4       | USERDATA7     |

| 120                                                     | 127               | 8           | USERDATA8 Size = 8       | USERDATA8     |

| <b>LFMXO5-55T and LFMXO5-100T</b>                       |                   |             |                          |               |

| 1                                                       | 48                | 48          | Use CFG0 with size = 48  | CFG0          |

|                                                         |                   |             | Use UFM0 with size = 0   | Do not Access |

| NA                                                      | NA                | 0           | Use CFG1 with size = 0   | Do not Access |

| 82                                                      | 96                | 15          | Use UFM1 with size = 15  | UFM1          |

| 97                                                      | 129               | 33          | Use CFG2 with size = 33  | CFG2          |

| 130                                                     | 144               | 15          | Use UFM2 with size = 15  | UFM2          |

| 145                                                     | 157               | 13          | USERDATA0 Size =13       | USERDATA0     |

| 158                                                     | 170               | 13          | USERDATA1 Size =13       | USERDATA1     |

| 171                                                     | 183               | 13          | USERDATA2 Size = 13      | USERDATA2     |

| 184                                                     | 196               | 13          | USERDATA3 Size = 13      | USERDATA3     |

| 197                                                     | 209               | 13          | USERDATA4 Size = 13      | USERDATA4     |

| 210                                                     | 222               | 13          | USERDATA5 Size = 13      | USERDATA5     |

| 223                                                     | 235               | 13          | USERDATA6 Size = 13      | USERDATA6     |

| 236                                                     | 248               | 13          | USERDATA7 Size = 13      | USERDATA7     |

| 249                                                     | 254               | 6           | USERDATA8 Size = 6       | USERDATA8     |

**Table 2.6. Sample Settings 2**

| Block Start Address | Block End Address | Block Count | Use Partition Setting   | Contents      |

|---------------------|-------------------|-------------|-------------------------|---------------|

| <b>LFMXO5-25</b>    |                   |             |                         |               |

| 1                   | 11                | 11          | Use CFG0 with size = 11 | CFG0          |

| 12                  | 15                | 4           | Use UFM0 with size = 4  | UFM0          |

| NA                  | NA                | 0           | Use CFG1 with size = 0  | Do not access |

| Block Start Address                                     | Block End Address | Block Count | Use Partition Setting    | Contents      |

|---------------------------------------------------------|-------------------|-------------|--------------------------|---------------|

| NA                                                      | NA                | 0           | Use UFM1 with size = 0   | Do not access |

| NA                                                      | NA                | 0           | Use CFG2 with size = 0   | Do not access |

| NA                                                      | NA                | 0           | Use UFM2 with size = 0   | Do not access |

| 46                                                      | 53                | 8           | USERDATA0 Size = 8       | USERDATA0     |

| 54                                                      | 57                | 4           | USERDATA1 Size = 4       | USERDATA1     |

| 58                                                      | 59                | 2           | USERDATA2 Size = 2       | USERDATA2     |

| 60                                                      | 60                | 1           | USERDATA3 Size = 1       | USERDATA3     |

| 61                                                      | 62                | 2           | USERDATA4 Size = 2       | USERDATA4     |

| NA                                                      | NA                | NA          | USERDATA5 Size = 0       | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| <b>LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T</b> |                   |             |                          |               |

| 1                                                       | 21                | 21          | Use CFG0 with size = 21  | CFG0          |

| 22                                                      | 28                | 7           | Use UFM0 with size = 7   | UFM0          |

| 29                                                      | 56                | 28          | Use CFG1 with size = 28  | CFG1          |

| NA                                                      | NA                | 0           | Use UFM1 with size = 0   | Do not access |

| 57                                                      | 61                | 5           | USERDATA0 Size = 5       | USERDATA0     |

| NA                                                      | NA                | 0           | Use CFG2 with size = 0   | Do not access |

| 85                                                      | 91                | 7           | Use UFM2 with size = 7   | UFM2          |

| 92                                                      | 127               | 36          | USERDATA1 Size = 36      | USERDATA1     |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| NA                                                      | NA                | 0           | Automatically set to '0' | Do not access |

| <b>LFMXO5-55T and LFMXO5-100T</b>                       |                   |             |                          |               |

| NA                                                      | NA                | 0           | Use CFG0 with size = 0   | Do not access |

| NA                                                      | NA                | 0           | Use UFM0 with size = 0   | Do not access |

| 49                                                      | 81                | 33          | Use CFG1 with size = 33  | CFG1          |

| 82                                                      | 96                | 15          | Use UFM1 with size = 15  | UFM1          |

| 97                                                      | 129               | 33          | Use CFG2 with size = 33  | CFG2          |

| 130                                                     | 144               | 15          | Use UFM2 with size = 15  | UFM2          |

| 145                                                     | 208               | 64          | USERDATA0 Size = 64      | USERDATA0     |

| 209                                                     | 240               | 32          | USERDATA1 Size = 32      | USERDATA1     |

| 241                                                     | 254               | 14          | USERDATA2 Size = 14      | USERDATA2     |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

| NA                                                      | NA                | NA          | Automatically set to '0' | Do not access |

## 2.4. Setting Initial Data in Flash Memory

This section provides information on how to set the initial data for the flash device using attributes. [Table 2.7](#) describes the five options available for initializing the flash memory partition. Note that initial data is for simulation purpose only. Initial value options create memory initialization files for convenience. These options are intended for optional customer-driven simulation and do not indicate official simulation support.

**Table 2.7. Flash Memory Partition Initialization Options**

| Partition Initial Value Format | Description                                                                                                                                                  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALL 1                          | An initialization data file is generated automatically containing each bit of the whole memory partition set to 1.                                           |

| ALL 0                          | An initialization data file is generated automatically containing each bit of the whole memory partition set to 0.                                           |

| NONE                           | No initialization data file is generated. Initialization of the MachXO5-NX device flash memory uses the factory default value, which is equivalent to ALL 1. |

| BINFILE                        | Initialization data file of the memory partition that you provide. The initialization data file is in the binary memory file format.                         |

| HEXFILE                        | Initialization data file of the memory partition that you provide. The initialization data file is in the hexadecimal memory file format.                    |

### 2.4.1. Binary File

The binary file is a text file of 0s and 1s. The number of rows is equal to the block size of the partition multiplied by 128. Each row has 4096 bits.

### 2.4.2. Hexadecimal File

The hexadecimal file is a text file of hexadecimal characters. The number of rows is equal to the block size of the partition multiplied by 128. Each row has 1024 hexadecimal characters.

## 2.5. Transaction Offset Computation

The Internal Flash Controller IP for MachXO5-NX computes the address of the flash transaction based on TRANSACTION\_ADDR.transaction\_partition and TRANSACTION\_ADDR.transaction\_offset. transaction\_partition determines the Partition Start Address as shown in the following tables. For a flash transaction address to be valid, Partition Start Address + transaction\_offset must not exceed the next Partition Start Address.

**Table 2.8. Flash Memory Map (Partition) for LFMXO5-25 Device**

| Partition Start Address                                | transaction_partition | Partition |

|--------------------------------------------------------|-----------------------|-----------|

| 0x01_0000                                              | 0x00                  | CFG0      |

| 0x0C_0000                                              | 0x01                  | UFM0      |

| 0x10_0000                                              | 0x02                  | CFG1      |

| 0x1B_0000                                              | 0x03                  | UFM1      |

| 0x1F_0000                                              | 0x04                  | CFG2      |

| 0x2A_0000                                              | 0x05                  | UFM2      |

| 0x2E_0000                                              | 0x06                  | USERDATA0 |

| 0x2E_0000 + (Size of USERDATA0 × 0x01_0000)            | 0x07                  | USERDATA1 |

| Address of USERDATA1 + (Size of USERDATA1 × 0x01_0000) | 0x08                  | USERDATA2 |

| Address of USERDATA2 + (Size of USERDATA2 × 0x01_0000) | 0x09                  | USERDATA3 |

| Address of USERDATA3 + (Size of USERDATA3 × 0x01_0000) | 0x0A                  | USERDATA4 |

| Address of USERDATA4 + (Size of USERDATA4 × 0x01_0000) | 0x0B                  | USERDATA5 |

| Address of USERDATA5 + (Size of USERDATA5 × 0x01_0000) | 0x0C                  | USERDATA6 |

| Address of USERDATA6 + (Size of USERDATA6 × 0x01_0000) | 0x0D                  | USERDATA7 |

| Partition Start Address                                | transaction_partition | Partition |

|--------------------------------------------------------|-----------------------|-----------|

| Address of USERDATA7 + (Size of USERDATA7 × 0x01_0000) | 0x0E                  | USERDATA8 |

**Table 2.9. Flash Memory Map (Partition) for LFMXO5-35, LFMXO5-35T, LFMXO5-65, and LFMXO5-65T Devices**

| Partition Start Address                                | transaction_partition | Partition |

|--------------------------------------------------------|-----------------------|-----------|

| 0x01_0000                                              | 0x00                  | CFG0      |

| 0x16_0000                                              | 0x01                  | UFM0      |

| 0x1D_0000                                              | 0x02                  | CFG1      |

| 0x32_0000                                              | 0x03                  | UFM1      |

| 0x39_0000                                              | 0x06                  | USERDATA0 |

| 0x40_0000                                              | 0x04                  | CFG2      |

| 0x55_0000                                              | 0x05                  | UFM2      |

| 0x5C_0000 + (Size of USERDATA1 × 0x01_0000)            | 0x07                  | USERDATA1 |

| Address of USERDATA1 + (Size of USERDATA2 × 0x01_0000) | 0x08                  | USERDATA2 |

| Address of USERDATA2 + (Size of USERDATA3 × 0x01_0000) | 0x09                  | USERDATA3 |

| Address of USERDATA3 + (Size of USERDATA4 × 0x01_0000) | 0x0A                  | USERDATA4 |

| Address of USERDATA4 + (Size of USERDATA5 × 0x01_0000) | 0x0B                  | USERDATA5 |

| Address of USERDATA5 + (Size of USERDATA6 × 0x01_0000) | 0x0C                  | USERDATA6 |

| Address of USERDATA6 + (Size of USERDATA7 × 0x01_0000) | 0x0D                  | USERDATA7 |

| Address of USERDATA7 + (Size of USERDATA7 × 0x01_0000) | 0x0E                  | USERDATA8 |

**Table 2.10. Flash Memory Map (Partition) for LFMXO5-55T and LFMXO5-100T Devices**

| Partition Start Address                                | transaction_partition | Partition |

|--------------------------------------------------------|-----------------------|-----------|

| 0x01_0000                                              | 0x00                  | CFG0      |

| 0x22_0000                                              | 0x01                  | UFM0      |

| 0x31_0000                                              | 0x02                  | CFG1      |

| 0x1B_0000                                              | 0x03                  | UFM1      |

| 0x52_0000                                              | 0x04                  | CFG2      |

| 0x61_0000                                              | 0x05                  | UFM2      |

| 0x82_0000                                              | 0x06                  | USERDATA0 |

| 0x91_0000 + (Size of USERDATA0 × 0x01_0000)            | 0x07                  | USERDATA1 |

| Address of USERDATA1 + (Size of USERDATA1 × 0x01_0000) | 0x08                  | USERDATA2 |

| Address of USERDATA2 + (Size of USERDATA2 × 0x01_0000) | 0x09                  | USERDATA3 |

| Address of USERDATA3 + (Size of USERDATA3 × 0x01_0000) | 0x0A                  | USERDATA4 |

| Address of USERDATA4 + (Size of USERDATA4 × 0x01_0000) | 0x0B                  | USERDATA5 |

| Address of USERDATA5 + (Size of USERDATA5 × 0x01_0000) | 0x0C                  | USERDATA6 |

| Address of USERDATA6 + (Size of USERDATA6 × 0x01_0000) | 0x0D                  | USERDATA7 |

| Address of USERDATA7 + (Size of USERDATA7 × 0x01_0000) | 0x0E                  | USERDATA8 |

## 2.6. Programming Flow

### 2.6.1. Write Access Operation 1

The following is the recommended procedure for executing a write transaction using the Internal Flash Controller IP:

**Note:** This procedure assumes that the target partition has been properly erased prior to initiating the write operation.

Refer to the [Erase Operation](#) section.

1. Set INT\_ENABLE.done\_en to 1 to enable the interrupt that indicates sending command to flash is done.

2. Configure the TRANSACTION\_ADDR register to specify the target partition and address for the access operation.

For more information, refer to the following fields in the [TRANSACTION\\_ADDR Register](#) section:

- TRANSACTION\_ADDR.transaction\_partition

- TRANSACTION\_ADDR.transaction\_offset

3. Configure the TRANSACTION\_CTRL register to specify the type of transaction – *write access* in this case. For more information, refer to the following fields in the [TRANSACTION\\_CTRL Register](#) section:

- TRANSACTION\_CTRL.transaction\_type – Set to *write access* (2'b00).

- TRANSACTION\_CTRL.transaction\_bytes\_m1 – Set the number of bytes to write. The maximum number of bytes for a write transaction is 256 so you may set this up to 'd255.

Ensure that the two key fields listed above are properly set.

4. Flush the WR FIFO by writing to the FIFO\_CTRL register. For more information, refer to the [FIFO\\_CTRL Register](#) section.

5. Write data to the WR\_FIFO\_DATA register repeatedly; up to N times, where N is determined by two factors:

- Configured FIFO depth of WR FIFO

- TRANSACTION\_CTRL.transaction\_bytes\_m1 setting

Each write to WR\_FIFO\_DATA transfers four data bytes. A single write transaction can accommodate a maximum of 256 data bytes, which corresponds to 64 writes to the WR\_FIFO\_DATA register.

**Note:** When writing to the WR\_FIFO\_DATA register, ensure that the write FIFO is not full to avoid data loss or write errors. You may optionally check the FIFO\_STATUS.wr\_fifo\_full flag before each write operation to the WR\_FIFO\_DATA register. If FIFO\_STATUS.wr\_fifo\_full is set to 1, defer the write operation until space becomes available.

6. Initiate the transaction by setting TRANSACTION\_CTRL.start\_transaction to 1. For more information, refer to the [TRANSACTION\\_CTRL Register](#) section.

7. Poll FIFO\_STATUS.done until it is set to 1. This indicates that the command has been successfully sent to the flash and the controller can queue the next command before interrupt service routine (ISR) processes are complete. It does not indicate completion of the flash operation.

8. After polling FIFO\_STATUS.done, monitor the int\_o signal, enabled in Step 1, for assertion. This interrupt confirms that the flash operation has completed.

9. Poll INT\_STATUS.done\_int until it is set to 1 to verify the interrupt, then clear the INT\_STATUS register. For more information, refer to the [INT\\_STATUS Register](#) section.

10. Optional: Initiate the next operation (erase, write access, or read access).

[Figure 2.5](#) and [Figure 2.6](#) show the relationship between the data bytes pushed in the WR FIFO and the data bytes written in the flash memory. Data to be written must be sent through the WR\_FIFO\_DATA register. Each valid write access to the WR\_FIFO\_DATA register pushes four bytes of data. In an empty WR FIFO, the first write access to WR\_FIFO\_DATA is pushed as Data0. The second write access is pushed as Data1 and so on. A total of 64 FIFO levels can accommodate the maximum number of bytes (256 bytes) to be written in one transaction.

The address of the transaction is computed by the IP using the TRANSACTION\_ADDR settings. The data is written to the flash memory starting from the computed transaction address. The next byte is written to transaction address + 1 until the total number of bytes to be written is completed. Start the write access to the flash memory by setting TRANSACTION\_CTRL.start\_transaction to 1 with TRANSACTION\_CTRL.transaction\_type = 0b00. The total number of bytes to be written is set in the TRANSACTION\_CTRL.transaction\_bytes\_m1 field.

Take note of the page boundaries (last eight bits of the write address bits = 0x00). *Write address + total number of bytes to be written* must not cross the page boundaries. If you want to write 256 bytes of data, the write address must be set to a page boundary (last eight bits of the write address bits = 0x00). If the page boundary is reached, the write address wraps around the start of the page.

Figure 2.5. FIFO and Flash Memory Relationship (Big Endian)

Figure 2.6. FIFO and Flash Memory Relationship (Little Endian)

## 2.6.2. Write Access Operation 2

The following is the recommended procedure for executing a write transaction with additional monitoring using the Internal Flash Controller IP:

**Note:** It is assumed that the target partition has been properly erased prior to initiating the write operation.

1. Set INT\_ENABLE.done\_en to 1 to enable the interrupt that indicates sending command to flash is done. Additionally, if applicable, set INT\_ENABLE.wr\_fifo\_almost\_full/almost\_empty/full to 1 depending on your monitoring scheme.

2. Configure the TRANSACTION\_ADDR register to specify the target partition and address for the access operation. For more information, refer to the following fields in the [TRANSACTION\\_ADDR Register](#) section:

- TRANSACTION\_ADDR.transaction\_partition

- TRANSACTION\_ADDR.transaction\_offset

3. Configure the TRANSACTION\_CTRL register to specify the type of transaction – *write access* in this case. For more information, refer to the following fields in the [TRANSACTION\\_CTRL Register](#) section:

- TRANSACTION\_CTRL.transaction\_type – Set to *write access* (2'b00).

- TRANSACTION\_CTRL.transaction\_bytes\_m1 – Set the number of bytes to write. The maximum number of bytes for a write transaction is 256 so you may set this up to 'd255.

Ensure that the two key fields listed above are properly set.

4. Flush the WR FIFO by writing to the FIFO\_CTRL register. For more information, refer to [FIFO\\_CTRL Register](#) section.

5. Depending on the monitoring scheme and the WR FIFO depth setting, follow the appropriate steps to write data to the WR\_FIFO\_DATA register repeatedly; up to N times, where N is determined by two factors:

- Configured FIFO depth of WR FIFO

- TRANSACTION\_CTRL.transaction\_bytes\_m1 setting

Each write to WR\_FIFO\_DATA transfers four data bytes. A single write transaction can accommodate a maximum of 256 data bytes, which corresponds to 64 writes to the WR\_FIFO\_DATA register.

**Note:** When writing to the WR\_FIFO\_DATA register, ensure that the WR FIFO is not full to avoid data loss or write errors. You may optionally check the FIFO\_STATUS.wr\_fifo\_full flag before each write operation to the WR\_FIFO\_DATA register. If FIFO\_STATUS.wr\_fifo\_full is set to 1, defer the write operation until space becomes available.

The following are the monitoring schemes:

- Polling-Based Monitoring

**Note:** After each write to WR\_FIFO\_DATA, check the relevant FIFO\_STATUS flag based on the desired monitoring behavior.

- If monitoring FIFO\_STATUS.wr\_fifo\_almost\_empty or wr\_fifo\_empty:

- a. Write data to the WR\_FIFO\_DATA register as long as the flag remains set.

- b. Pause writing to WR\_FIFO\_DATA once the flag is cleared.

- c. Initiate the transaction by setting TRANSACTION\_CTRL.start\_transaction to 1. For more information, refer to the [TRANSACTION\\_CTRL Register](#) section.

- d. Resume writing once the wr\_fifo\_almost\_empty or wr\_fifo\_empty is set.

- e. Repeat these steps until all data has been written.

- If monitoring FIFO\_STATUS.wr\_fifo\_almost\_full or wr\_fifo\_full:

- a. Write data to the WR\_FIFO\_DATA register as long as the flag remains clear.

- b. Pause writing to WR\_FIFO\_DATA once the flag is set.

- c. Initiate the transaction by setting TRANSACTION\_CTRL.start\_transaction to 1. For more information, refer to the [TRANSACTION\\_CTRL Register](#) section.

- d. Resume writing once the wr\_fifo\_almost\_full or wr\_fifo\_full flag is cleared.

- e. Repeat these steps until all data has been written.

- Interrupt-Based Monitoring

**Note:** When interrupts are enabled for wr\_fifo\_status flags, after each write to WR\_FIFO\_DATA, monitor the int\_o signal. For interrupt-driven writes, use polling to initially fill the FIFO until it reaches the configured

threshold (full or almost full). After the initial fill, subsequent writes can be managed by the ISR based on the FIFO status interrupts. This ensures efficient startup without waiting for interrupts when the FIFO is empty.

- a. Write data to the WR\_FIFO\_DATA register until int\_o asserts.

- b. Upon int\_o assertion, check and clear the INT\_STATUS register to acknowledge the interrupt.

- c. Based on the flag set, pause writing to WR\_FIFO\_DATA.

- d. Initiate the transaction by setting TRANSACTION\_CTRL.start\_transaction to 1. For more information, refer to the [TRANSACTION\\_CTRL Register](#) section.

- e. Resume writing once the FIFO\_STATUS.wr\_fifo\_almost\_empty or wr\_fifo\_empty flag is cleared.

- f. Repeat Steps a through d until all data has been written.

6. After all data has been written, poll FIFO\_STATUS.done until it is set to 1. This indicates that the command has been successfully sent to the flash and the controller can queue the next command before ISR processes are complete. It does not indicate completion of the flash operation.

7. After polling FIFO\_STATUS.done, monitor the int\_o signal, enabled in Step 1 (associated with INT\_ENABLE.done\_en), for assertion. This interrupt confirms that the flash operation has completed.

8. Poll INT\_STATUS.done\_int until it is set to 1 to verify the interrupt, then clear the INT\_STATUS register. For more information, refer to the [INT\\_STATUS Register](#) section.

9. Optional: Initiate the next operation (erase, write access, or read access).

### 2.6.3. Read Access Operation 1

The following is the recommended procedure for executing a read transaction using the Internal Flash Controller IP:

1. Set INT\_ENABLE.done\_en to 1 to enable the interrupt that indicates sending command to flash is done.

2. Configure the TRANSACTION\_ADDR register to specify the target partition and address for the access operation. For more information, refer to the following fields in the [TRANSACTION\\_ADDR Register](#) section.

- TRANSACTION\_ADDR.transaction\_partition

- TRANSACTION\_ADDR.transaction\_offset

3. Configure the TRANSACTION\_CTRL register to specify the type of transaction – *read access* in this case. For more information, refer to the following fields in the [TRANSACTION\\_CTRL Register](#) section:

- TRANSACTION\_CTRL.transaction\_type – Set to *read access* (2'b01).

- TRANSACTION\_CTRL.access\_mode – Set to either QUAD or STANDARD depending on the configured device.

- TRANSACTION\_CTRL.transaction\_bytes\_m1 – Set the number of bytes to read.

- TRANSACTION\_CTRL.read\_mode – Set to either fast read or normal read.Ensure that the four key fields listed above are properly set.

4. Flush the RD FIFO by writing to the FIFO\_CTRL register. For more information, refer to the [FIFO\\_CTRL Register](#) section.

5. Initiate the transaction by setting the TRANSACTION\_CTRL.start\_transaction field to 1. For more information, refer to the [TRANSACTION\\_CTRL Register](#) section.

6. Poll FIFO\_STATUS.rd\_fifo\_empty until it is 0.

7. Read data from the RD\_FIFO\_DATA register.

8. Repeat Steps 6 and 7 until the specified number of bytes, as defined by the TRANSACTION\_CTRL.transaction\_bytes\_m1 setting, has been read.

9. Poll FIFO\_STATUS.done until it is set to 1. This indicates that the command has been successfully sent to the flash and the controller can queue the next command before ISR processes are complete. It does not indicate completion of the flash operation.

10. After polling FIFO\_STATUS.done, monitor the int\_o signal, enabled in Step 1, for assertion. This interrupt confirms that the flash operation has completed.

11. Poll INT\_STATUS.done\_int until it is set to 1 to verify the interrupt, then clear the INT\_STATUS register. For more information, refer to the [INT\\_STATUS Register](#) section.

12. Optional: Initiate the next operation (erase, write access, or read access).

**Note:** In an empty RD FIFO, the first four bytes read from the flash memory are pushed as Data0 in the RD FIFO. The second four bytes read are pushed as Data1, followed by subsequent sets as Data2, Data3, and so on. Data to be read must be accessed through the RD\_FIFO\_DATA register. Each valid read access to the RD\_FIFO\_DATA register retrieves four bytes of data.

The address of the transaction is computed by the IP using the TRANSACTION\_ADDR settings. Start the read access to the flash memory by setting TRANSACTION\_CTRL.start\_transaction to 1 with TRANSACTION\_CTRL.transaction\_type = 2'b01. The data is read from the flash memory starting from the computed transaction address. The next byte is read from transaction address + 1 until the total number of bytes to be read is completed. The total number of bytes to be read is set in the TRANSACTION\_CTRL.transaction\_bytes\_m1 field.

## 2.6.4. Read Access Operation 2

The following is the recommended procedure for executing a read transaction with additional monitoring using the Internal Flash Controller IP:

1. Set INT\_ENABLE.done\_en to 1 to enable the interrupt that indicates sending command to flash is done. Additionally, if monitoring the INT\_STATUS.rd\_fifo\_full flag, set INT\_ENABLE.rd\_fifo\_full to 1 to enable the corresponding interrupt.

2. Configure the TRANSACTION\_ADDR register to specify the target partition and address for the access operation. For more information, refer to the following fields in the [TRANSACTION\\_ADDR Register](#) section:

- TRANSACTION\_ADDR.transaction\_partition

- TRANSACTION\_ADDR.transaction\_offset

3. Configure the TRANSACTION\_CTRL register to specify the type of transaction – *read access* in this case. For more information, refer to the following fields in the [TRANSACTION\\_CTRL Register](#) section:

- TRANSACTION\_CTRL.transaction\_type – Set to *read access* (2'b01).

- TRANSACTION\_CTRL.access\_mode – Set to either QUAD or STANDARD depending on the configured device.