# Lattice Radiant Software 3.0 User Guide

## Copyright

Copyright © 2021 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopify Pro are trademarks of Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. Modelsim and Questa are trademarks or registered trademarks of Siemens Industry Software Inc. or its subsidiaries in the United States or other countries. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

# **Type Conventions Used in This Document**

| Convention        | Meaning or Use                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------|

| Bold              | Items in the user interface that you select or click. Text that you type into the user interface. |

| <italic></italic> | Variables in commands, code syntax, and path names.                                               |

| Ctrl+L            | Press the two keys at the same time.                                                              |

| Courier           | Code examples. Messages, reports, and prompts from the software.                                  |

|                   | Omitted material in a line of code.                                                               |

|                   | Omitted lines in code and report examples.                                                        |

| [ ]               | Optional items in syntax descriptions. In bus specifications, the brackets are required.          |

| ( )               | Grouped items in syntax descriptions.                                                             |

| { }               | Repeatable items in syntax descriptions.                                                          |

| 1                 | A choice between items in syntax descriptions.                                                    |

|                   |                                                                                                   |

Chapter 1

# **Contents**

Introduction 8

|           | Radiant Software Overview 8 User Guide Organization 9                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | Getting Started 10 Prerequisites 10 Creating a New Project 11 Opening an Existing Project 14 Importing a Lattice Diamond Project 15 Next Steps 15                                                                                         |

| Chapter 3 | Design Environment Fundamentals 16 Overview 16 Project-Based Environment 17 Process Flow 18 Shared Memory 19 Context-Sensitive Data Views 20                                                                                              |

| Chapter 4 | User Interface Operation 22  Start Page 22  Menus and Toolbars 23  Reports and Messages Views 23  File List Views 24  Tool View Area 25  Output and Tcl Console 26  Basic UI Controls 26  File List 27  Source Template 27  IP Catalog 29 |

```

Hierarchy 31

Reports 31

Tool Views 32

Tcl Console 33

Output 33

Message 34

Find Results 34

Common Tasks 34

Controlling Views 35

Cross-Probing 36

Chapter 5

Working with Projects

Overview 40

Implementations 42

Adding Implementations 42

Cloning Implementations 43

Input Files 44

Pre-Synthesis Constraint Files 45

Post-Synthesis Constraint Files 45

Debug Files 46

Script Files 46

Analysis Files 47

Programming Files 47

Strategies 47

Area 49

Timing 50

User-Defined 51

Common Tasks 51

Creating a Project 51

Changing the Target Device 52

Setting the Top Level of the Design 52

Editing Files 52

Saving Project Data 53

Chapter 6

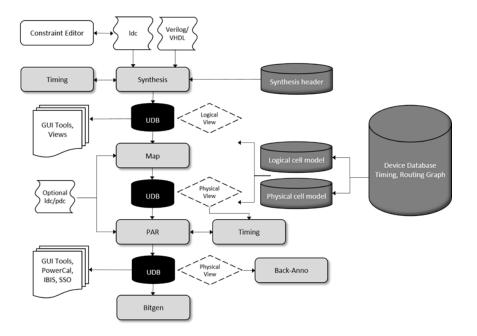

Radiant Software Design Flow

54

Overview 54

Design Flow Processes 55

Running Processes 55

IP Encryption Flow 56

HDL File Encryption Flow 58

HDL File Encryption Steps 59

Implementation Flow and Tasks 62

Synthesis Constraint Creation 62

Constraint Creation 64

Simulation Flow 65

Simulation Wizard Flow 66

```

Process 29

Task Detail View 30

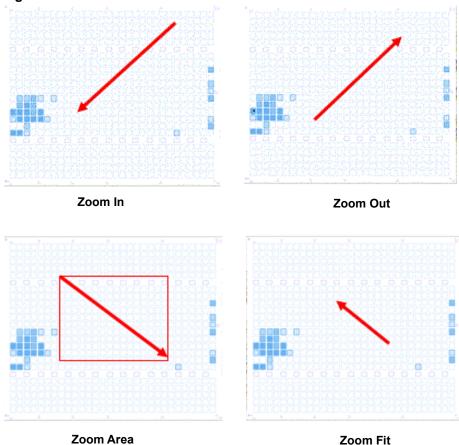

#### Start Page 70 Reports 70 Tools 72 Timing Constraint Editor 72 Constraint Propagation **74** Device Constraint Editor 74 Netlist Analyzer 76 Physical Designer 76 Timing Analyzer 79 Reveal Inserter 80 Reveal Analyzer 80 Reveal Controller 80 Power Calculator 81 ECO Editor 82 Programmer 83 Run Manager 84 Synplify Pro for Lattice 84 Mentor ModelSim 85 Simulation Wizard 85 Source Template 86 IP Catalog 86 IP Packager 87 SEI Editor 87 Common Tasks 87 Controlling Tool Views 88 Using Zoom Controls 89 Displaying Tool Tips 91 Setting Display Options 91 **Chapter 8 Command Line Reference Guide** 92 Command Line Program Overview 92 Command Line Basics 94 Command Line Data Flow 94 Command Line General Guidelines 95 Command Line Syntax Conventions 96 Setting Up the Environment to Run Command Line 97 Invoking Core Tool Command Line Programs 98 Invoking Core Tool Command Line Tool Help 98 Command Line Tool Usage 99 Running cmpl libs.tcl from the Command Line 100 Running HDL Encryption from the Command Line 102 Running SYNTHESIS from the Command Line 109 Running Postsyn from the Command Line 115 Running MAP from the Command Line 116 Running PAR from the Command Line 118 Running Timing from the Command Line 124 Running Backannotation from the Command Line 126 Running Bit Generation from the Command Line 129

**Working with Tools and Views**

View Menu Highlights 69

Overview 69

69

Chapter 7

Running Programmer from the Command Line 132

Running Various Utilities from the Command Line 135

Using Command Files 139

Using Command Line Shell Scripts 141

#### Chapter 9 Tcl Command Reference Guide 144

Running the Tcl Console 145

Accessing Command Help in the Tcl Console 147

Creating and Running Custom Tcl Scripts 147

Running Tcl Scripts When Launching the Radiant Software 150

Radiant Software Tool Tcl Command Syntax 151

Radiant Software Tcl Console Commands 151

Radiant Software Timing Constraints Tcl Commands 154

Radiant Software Physical Constraints Tcl Commands 156

Radiant Software Project Tcl Commands 158

Simulation Libraries Compilation Tcl Commands 164

Reveal Inserter Tcl Commands 166

Reveal Analyzer Tcl Commands 170

Power Calculator Tcl Commands 174

Programmer Tcl Commands 175

Engineering Change Order Tcl Commands 178

#### Chapter 10 Advanced Topics 180

Shared Memory Environment 180

Clear Tool Memory 180

Environment and Tool Options 181

Batch Tool Operation 182

Tcl Scripts 182

Creating Tcl Scripts from Command History 182

Creating Tcl Scripts from Scratch 183

Sample Tcl Script 183

Running Tcl Scripts 184

Project Archiving 184

File Descriptions 185

**Revision History** 188

# Chapter 1

# Introduction

Lattice Radiant<sup>®</sup> software is the leading-edge software design environment for cost- sensitive, low-power Lattice Field Programmable Gate Arrays (FPGA) architectures. The Radiant software integrated tool environment provides a modern, comprehensive user interface for controlling the Lattice Semiconductor FPGA implementation process. Its combination of new and enhanced features allows users to complete designs faster, more easily, and with better results than ever before.

This user guide describes the main features, usage, and key concepts of the Radiant software design environment. It should be used in conjunction with the Release Notes and reference documentation included with the product software. The Release Notes document is also available on the Lattice Web site and provides a list of supported devices.

## **Radiant Software Overview**

The Radiant software uses an expanded project-based design flow and integrated tool views so that design alternatives and what-if scenarios can easily be created and analyzed. The *Implementations* and *Strategies* concepts provide a convenient way for users to try alternate design structures and manage multiple tool settings.

System-level information—including process flow, hierarchy, and file lists—is available, along with integrated HDL code checking and consolidated reporting features.

A fast Timing Analysis loop and Programmer provide capabilities in the integrated framework. The cross-probing feature and the shared memory architecture ensure fast performance and better memory utilization.

The Radiant software is highly customizable and provides Tcl scripting capabilities from either its built-in console or from an external shell.

The Radiant software has many of the same features as Lattice Diamond software, and adds new features, such as:

- Constraints support utilizing industry standard SDC format.

- Efficient, easy-to-use integrated graphical user interface (GUI) with a new look-and-feel that gives users more efficient access to popular tools.

Unified timing analysis engine with enhanced timing reports for faster design timing closure.

# **User Guide Organization**

This user guide contains all the basic information for using the Radiant software. It is organized in a logical sequence from introductory material, through operational descriptions, to advanced topics.

Key concepts and work flows are explained in "Design Environment Fundamentals" on page 16 and "Radiant Software Design Flow" on page 54.

Basic operation of the design environment is described in "User Interface Operation" on page 22.

The chapter "Working with Projects" on page 40 shows how to set up project implementations and strategies.

The chapter "Working with Tools and Views" on page 69 describes the many tool views available.

# Chapter 2

# **Getting Started**

This chapter explains how to run the Radiant software and open or create a project. For more information about project fundamentals, see the chapters "Design Environment Fundamentals" on page 16 and "Working with Projects" on page 40.

# **Prerequisites**

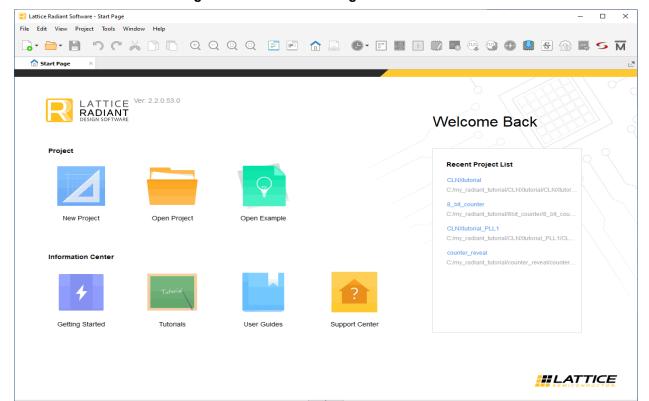

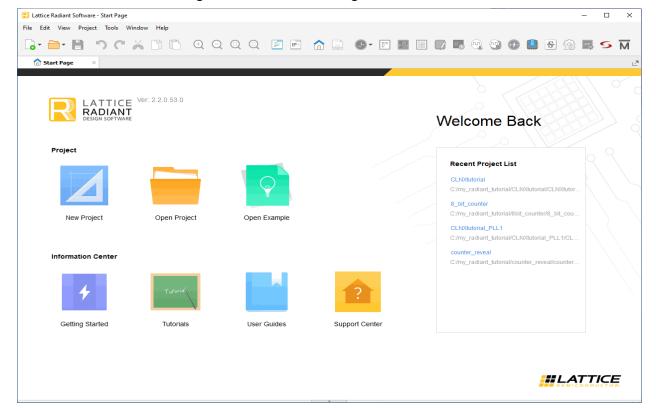

To run the Radiant software, select **Radiant Software** from the installation location. This opens the default Start Page, shown in Figure 1.

Lattice Veri 3 0.1181.0

| Start Page | Star

Figure 1: Default Start Page

# **Creating a New Project**

A project is a collection of all files necessary to create and download your design to the selected device. The New Project wizard guides you through the steps of specifying a project name and location, selecting a target device, and adding existing sources to the new project.

#### Note

Do not place more than one project in the same directory.

#### To create a new project:

From the Radiant main window, click the New Project button, or choose File > New > Project.

The New Project confirmation window opens, shown in Figure 2.

**Figure 2: New Project Confirmation Window**

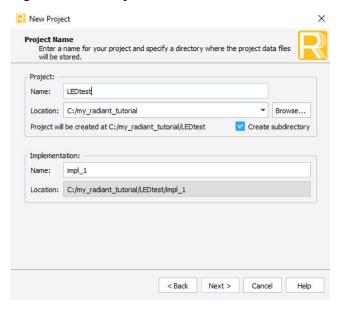

2. Click **Next**. The New Project wizard opens, shown in Figure 3.

Figure 3: New Project Wizard

- 3. In the Project Name dialog box, do the following:

- Under Project, specify the name for the new project.

- File names for Radiant software projects and project source files must start with a letter (A-Z, a-z) and must contain only alphanumeric characters (A-Z, a-z, 0-9) and underscores (\_). Spaces are allowed.

- To specify a location for your project, click **Browse**. In the Project Location dialog box, you can specify a desired location.

- Under Implementation, specify the name for the first version of the project. You can have more than one version, or "implementation," of the project to experiment with. For more information on implementations, refer to "Implementations" on page 42.

- To create a sub-directory with the same name as your location directory, click Create Subdirectory. This will allow you to keep your project implementations separate. If this box is left unchecked, no subdirectory will be created in the project directory.

- When you finish, click Next.

- In the Add Source dialog box, do the following if you have an existing source file that you want to add to the project. If there are no existing source files, click Next.

- a. Click Add Source. You can import HDL files at this time. In the Import File dialog box, browse for the source file you want to add, select it, and click Open.

The source file is then displayed in the Source files field.

- b. Repeat the above to add more files.

- c. To copy the added source files to the implementation directory, select Copy source to implementation directory. If you prefer to reference these files, clear this option.

- d. To create empty Lattice Design Constraint (.ldc) file and Physical Constraint File (.pdc) files that can be edited at a later time, select Create empty constraint files. Refer to the chapter "Implementations" on page 42 for more information about constraint files.

- e. When you finish, click Next.

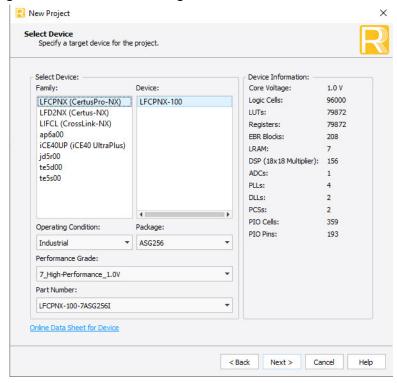

- 5. In the Select Device dialog box, shown in Figure 4, select a device family and a specific device within that family. Then choose the options you want for that device. When you finish, click **Next**.

Figure 4: Select Device Dialog Box

- In the Select Synthesis Tool dialog box, select the synthesis tool that you want to use. This choice can be changed at any time. When you finish, click Next.

- 7. In the Project Information dialog box, make sure the project settings are correct.

#### **Note**

If you want to change some of the settings, click **Back** to modify them in the previous dialog boxes of the New Project Wizard.

Click **Finish**. The newly created project, shown in Figure 5, is now created and open.

File Edit View Project Tools Window Help

▶

Synthesize Design

→

▶

Map Design

→

▶

Place & Route Design

→

▶

Export Files

8\_bit\_counter Project Summary Reports □ Timing

□ Strategy1

□ impl1 (Lattice LSE)

□ Input Files

□ source/count\_attr.v

□ Pre-Synthesis Constraint Files **Project Summary** Strategy1 Operating Condition IND Part Number LIECI -40-7BG400I Synthesis Lattice LSE ▶

Synthesis Reports LIFCL Timing Errors: Family: Lattice LSE

Symplify Pro

source/impl1.sdc

Post-Synthesis Constraint Files 2021/04/05 08:42:46 ▶ Amap Reports Device: LIFCL-40 Project Created: Package: CARGA400 Project Undated 2020/11/06 09:40:31 ▶

☐ Place & Route Reports Project File: source/impl1.pdc Debug Files C:/my\_radiant\_tutorial/8bit\_counter/impl1 Implementation Lo ▶

Export Reports Script Files

Analysis Files Resource Usage Programming Files LUT4: IO Buffers PFU Regis count - count\_attr.v ▼ ▼ 8 0 Errors 🛕 0 Warnings 0 3 Infos 📮 Group by ID Search ▼ Project (3 infos) 0 2149992 INFO -▶ **1** 2049992 INFO - C:/my\_radiant\_tutorial/8bit\_counter/source/count\_attr.v(2,8-2,13) (VERI-1018) compiling module 'count □ File List P Source Template □ IP Catalog □ Tri Console □ Output □ Message

Figure 5: Opened Project

Select the **File List** tab under the left pane, to view the Test project file list.

To close a project, choose File > Close Project.

# **Opening an Existing Project**

Use one of the following methods to open an existing Radiant software project:

- On the Start Page, click the Open Project button.

- From the File menu, choose Open > Project.

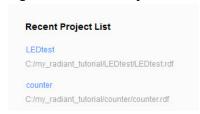

- On the Start Page, select the desired project from the Recent Projects

List. Alternatively, choose a recent project from the File > Recent

Projects menu.

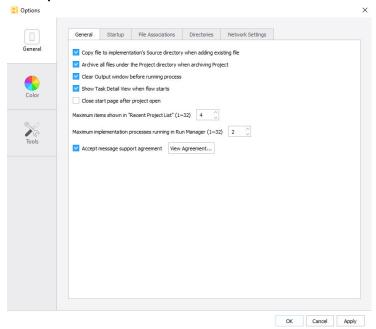

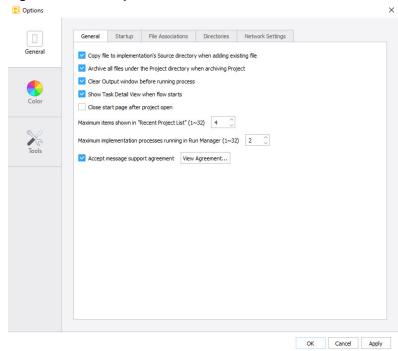

You can use the Options dialog box to increase the number of projects that are shown in the Recent Projects list and to automatically load the previous project at startup. Choose **Tools > Options** to open the dialog box. To increase the number of recent projects listed, click the **General** tab and enter a number for "Maximum items shown in Recent Project List" (up to 32). To automatically open the previous project during startup, click the **Startup** tab and then choose **Open Previous Project** from the "At Lattice Radiant Software startup" menu.

Figure 6: Recent Project List

# **Importing a Lattice Diamond Project**

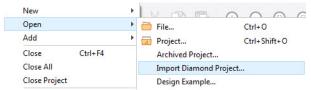

To import a Lattice Diamond project into the Radiant software, choose **File > Open > Import Diamond Project**.

Figure 7: Import Lattice Diamond Project

The file browser applies an \*.ldf file filter to help you find Lattice Diamond project files. The Lattice Diamond project is converted to a Radiant project.

For more information about importing Lattice Diamond projects into the Radiant software, refer to the *Lattice Radiant Software Guide for Diamond Users*.

# **Next Steps**

After you have a project opened in the Radiant software, you can go sequentially through the rest of this user guide to learn how to work with the entire design environment, or you can go directly to any topic of interest.

- ► The chapters "Design Environment Fundamentals" on page 16 and "Radiant Software Design Flow" on page 54 provide explanations of key concepts.

- "User Interface Operation" on page 22 provides descriptions of the functions and controls that are available in the Radiant software environment.

- ► The chapters "Working with Projects" on page 40 and "Working with Tools and Views" on page 69 explain how to run processes and use the design tools.

- "Tcl Command Reference Guide" on page 956 provides an introduction to the scripting capabilities available, plus command-line shell examples.

- "Advanced Topics" on page 180 provides further details about environment options, shared memory, and Tcl scripting.

# Chapter 3

# **Design Environment Fundamentals**

This chapter provides background and discussion on the technology and methodology underlying the Radiant software design environment. Important key concepts and terminology are defined.

## Overview

Understanding some of the fundamental concepts behind the Radiant software framework technology will increase your proficiency with the tool and allow you to quickly come up to speed on its use.

The Radiant software is a next-generation software design environment that uses a new project-based methodology. A single project can contain multiple implementations and strategies to provide easily managed alternate design structures and tool settings.

The process flow is managed at a system level with run management controls and reporting. Context-sensitive views ensure that you only see the data that is available for the current state in the process flow.

The shared memory technology enables many of the advanced functions in the Radiant software. Easy cross-probing between tool views and faster process loops are among the benefits.

#### Note

By loading the Radiant software multiple times, you can run different Radiant projects simultaneously. However, you must not load the same project in more than one Radiant software instance, as software conflicts can occur.

The Radiant software can also be run remotely. Refer to the Lattice Radiant Software Installation Guide for Windows or Lattice Radiant Software Installation Guide for Linux for more information.

# **Project-Based Environment**

A project in the Radiant software consists of the following file types:

- HDL source files

- Constraint files

- Reveal debug files

- Script files for simulation

- Analysis files for power calculation and timing analysis

- Programming files

The Radiant software also includes settings for the targeted device and the different tools. The project data is organized into implementations, which define the project structural elements, and strategies, which are collections of tool settings.

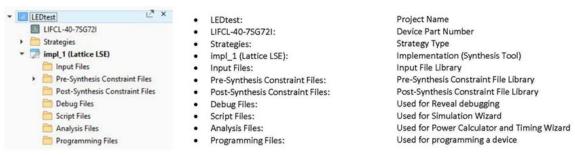

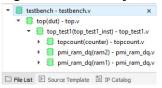

The following File List shows the items in a sample project.

Figure 8: File List

Each item that is displayed in **bold** means that it has been selected as the active item for an implementation. An implementation displayed in **bold** means that it has been selected as the currently active implementation for the project. Your project must have one active implementation, and the implementation must have one active strategy. Optional items, such as Reveal hardware debugger files, can be set as active or inactive.

The project is the top-level organizational element in the Radiant software, and it can contain multiple implementations and multiple strategies. This enables you to try different design approaches within the same project. If you want to have a Verilog version of your design, for example, make an implementation that consists of only the Verilog source files. If you want another version of the design with primarily Verilog files but a Structural Verilog (.vm) netlist for one module, create a new implementation using the Verilog and .vm source files. Each implementation can have Verilog, VHDL or Structural Verilog source or mixed of them. The same project and design is used, but with a different set of modular blocks.

Similarly, if you want to try different implementation tool options, you can create a new strategy with the new option values.

You manage these multiple implementations and strategies for your project by setting them as active. There can only be a single active implementation with its one active strategy at a time.

### **Process Flow**

A process is a specific task in the overall processing of a source or project. Typical processing tasks include synthesizing, mapping, placing, and routing. You can view the available processes for a design in the Process Toolbar.

Figure 9: Process Toolbar

Click the Task Detail View 📒 to see detailed information of the processes.

Processes are grouped into categories according to their functions.

#### Synthesize Design

Click on this process and Lattice Synthesis Engine (LSE) runs to synthesize the design. By default, this process runs the LSE tool.

If you are using Synplify Pro, choose Synplify Pro as the synthesis tool (**Project > Active Implementation > Select Synthesis Tool**).

#### Post-Synthesis Timing Analysis

Runs timing analysis after the Synthesize Design process.

#### Post-Synthesis Simulation File

Generates a netlist file < file\_name > \_syn.vo used for functional verification.

#### Map Design

This process maps a design to an FPGA. Map Design is the process of converting a design represented as a network of device-independent components (such as gates and flip-flops) into a network of device-specific components (for example, configurable logic blocks).

#### Map Timing Analysis

Runs timing analysis after the Map Design process.

#### Place & Route Design

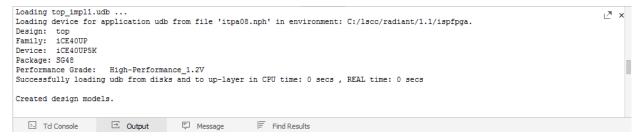

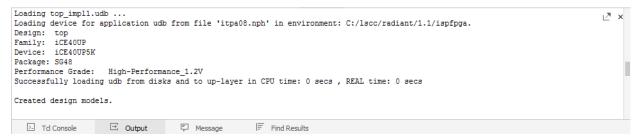

After a design has undergone the necessary translation to bring it into the Unified Database (.udb) format, you can run the Place & Route Design process. This process takes a mapped physical design .udb file, places and routes the design, and then outputs a file that can then be processed by the design implementation tools.

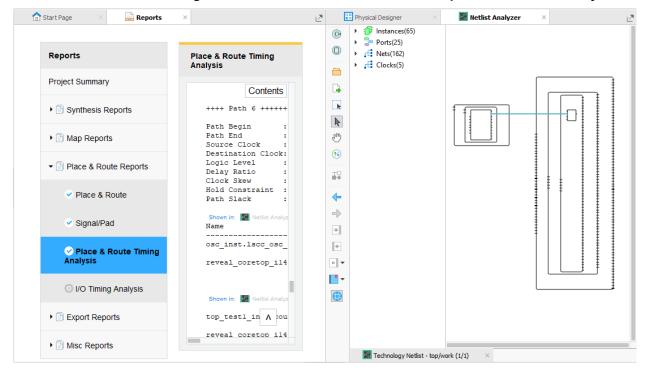

#### Place & Route Timing Analysis

Runs timing analysis after Place & Route process.

#### I/O Timing Analysis

Runs I/O timing analysis that allows you to view the path delay tables and Timing Analyzer report of your timing constraints after placement and routing.

#### Export Files

You can check the desired file you want to export and run this process.

#### Bitstream File

This process takes a fully routed physical design as input and produces a configuration bitstream (bit images). The bitstream file contains all of the configuration information from the physical design defining the internal logic and interconnections of the FPGA, as well as device-specific information from other files associated with the target device.

#### IBIS Model

This process generates a design-specific IBIS (I/O Buffer Information Specification) model file (crp.ide

IBIS models provide a standardized way of representing the electrical characteristics of a digital IC's pins (input, output, and I/O buffers).

#### Gate-Level Simulation File

This process backannotates the routed design with timing information so that you may run a simulation of your design. The backannotated design is a Verilog netlist.

The Reports view allows you to examine and print process reports.

Messages are displayed in the Messages window at the bottom of the Radiant software main window.

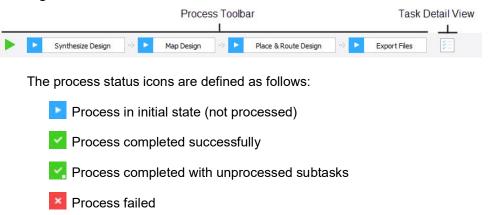

The process status icons are defined as follows:

- Process in initial state (not processed)

- Process completed successfully

- Process completed with unprocessed subtasks

- Process failed

# Shared Memory

The Radiant software uses a shared memory architecture. All tool and data views look at the same design data at any point in time. This means that when you change a data element in one view of your design, all other views will see the change, whether they are active or not.

When project data has been changed but not yet saved, an asterisk (\*) is displayed in the title tab of the view.

Figure 10: Title Tab with Changed Content Indication

Notice that the asterisks indicating changed data will appear in all views referencing the changed data.

If a tool view becomes unavailable, the Radiant software environment will need to be closed and restarted.

## **Context-Sensitive Data Views**

The data in shared memory reflects the state or context of the overall process flow. This means that views such as Device Constraint Editor Spreadsheet View will display only the data that is currently available, depending on process steps that have been completed.

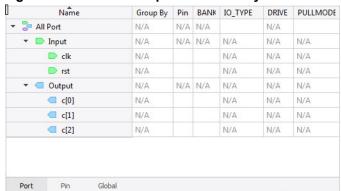

For example, Figure 11 shows the Process flow before Synthesis. Therefore, Spreadsheet View shows no IO Type or PULLMODE.

Figure 11: Process Completed Before Synthesis

After Synthesis has been completed, Spreadsheet View displays IO Type and PULLMODE assignments, as shown in Figure 12.

Group By Pin BANK IO\_TYPE DRIVE PULLMODE ▼ 📴 All Port N/A N/A N/A N/A ▼ D Input N/A N/A N/A N/A N/A N/A LVCMOS33 NA rst N/A 100K ▼ 🔝 Clock N/A N/A N/A N/A N/A LVCMOS33 NA n clk 100K N/A N/A N/A N/A N/A N/A Output LVCMOS33 8 c[2] N/A NA LVCMOS33 8 NA c[1] N/A **c**[0] LVCMOS33 8

Figure 12: Process Completed Through Synthesis

When you see the "Loading Data" message displayed in Figure 13, it means that a process has been completed and that the shared memory is being updated with new data.

Figure 13: Loading Data

Pin

Port

Global

All tool views are dynamically updated when new data becomes available. This means that when you rerun an earlier process while a view is open and displaying data, the view will remain open but dimmed because its data is no longer available.

# Chapter 4

# **User Interface Operation**

The Radiant user interface (UI) provides a comprehensive, integrated tool environment. The UI is very flexible and configurable, enabling you to store constraints for the layout you choose.

This chapter describes the user interface, controls, and basic operation of the Radiant software. Each major element of the interface is explained. The last section in the chapter describes common user interface tasks.

## **Start Page**

The Start Page contains three major sections, as shown in Figure 14.

Figure 14: Default Start Page

- **Project**: This section allows you to create a new project; open an existing Project, and open an example.

- Information Center: This section has a links to Getting Started, Tutorials, User Guides, and Support Center.

- ▶ Recent Project List: Provides a quick way to load a recent project you've been working on.

The Start Page appears in the View area by default when the Radiant software is first launched, and can be opened from the View tab on the menu.

The Start Page can be closed, opened, detached, and attached using the Attach button. See "Basic UI Controls" on page 26.

## **Menus and Toolbars**

At the top of the main window is the menu and toolbar area. High-level controls for accessing tools, managing files and projects, and controlling the layout are contained here. All toolbar functionality is also contained in the menus. The menus also have functions for system, project and toolbar control.

The Process Toolbar lists all the processes available, such as Synthesize Design, Map Design, Place & Route Design, and Export Files. A process is a specific task in the overall processing of a source or project. You can view the available processes for a design in the Process Toolbar. Click Task Detail **View** E to see detailed information of the processes available.

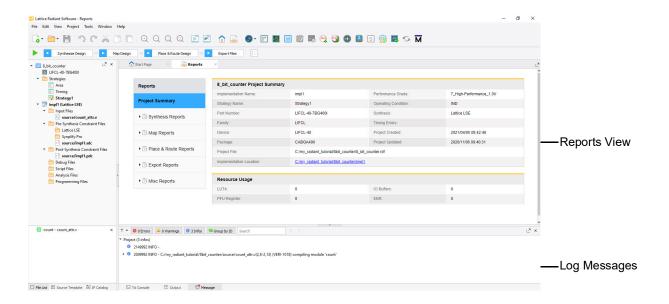

# **Reports and Messages Views**

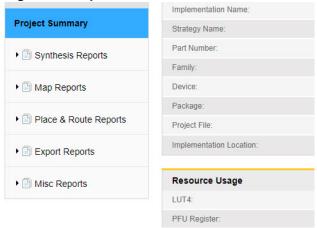

The Reports view allows you to examine and print process reports. There are two panes in the Reports view. The left pane lists the reports. The right pane displays the reports.

Log messages are displayed in the Output frame of the Radiant software main window.

Figure 15: Reports and Log Message Views

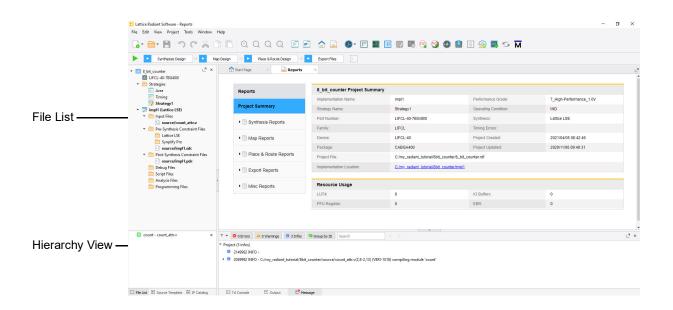

## **File List Views**

In the middle of the main window on the left side is the File List area. This is where the overall project and process flow is displayed and controlled.

Figure 16: File List Area

Tabs at the bottom of the File List area allow you to select between the following views:

- File List shows the files in the project organized by implementations and strategies. This is not a hierarchical listing of the design.

- Source Template provides templates for creating VHDL, Verilog, and Constraint files.

- IP Catalog lists available modules/intellectual properties (IP).

Underneath the File List is the Hierarchy View area. It allows you to view the hierarchical design representation. Hierarchy view shares the left pane with File List view.

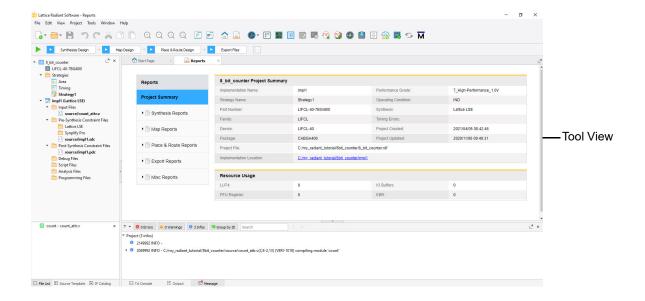

## **Tool View Area**

In the middle of the main window on the right side is the Tool View area. This is where the Start Page, Reports View, and all the Tool views are displayed.

Figure 17: Tool View Area

Multiple tools can be displayed at the same time. The tool tabs include controls for grouping the tool views as well as integrating all tool views back into the main window.

Each tool view is specific to its tool and can contain additional toolbars and multiple panes or windows controlled by additional tabs. The chapter "Working with Tools and Views" on page 69 provides more details about each tool and view.

Figure 18: Multiple Tools

# **Output and Tcl Console**

Near the right bottom of the main window is the Tcl Console, Output, and Message area.

Tabs at the bottom of this area allow you to select between Tcl Console, Output, and Message. Tool output is automatically displayed in the Output tab, and Errors and Warnings in the Message tab.

Figure 19: Output and Tcl Console Area

## **Basic UI Controls**

The Radiant software environment is based on modern industry standard user interface concepts. The menus, toolbars, and mouse pointer all behave in familiar ways. You can resize any of the window panes, drag and drop elements, right-click a design element to see available actions, and hold the mouse pointer over an object to view the tool tip. Window panes can also be detached from the main window and operated as independent windows.

## **File List**

The File List is a project view that shows the files in the project, including implementations and strategies. It is not a hierarchical listing of the design, but rather a list of all the design source, configuration and control files that make up the project.

Figure 20: File List

At the top of the File List is the project name. Directly below the project name is the target device, followed by the strategies, and then the implementations. There must be one active implementation, and it must have one active strategy. Active elements are indicated in **bold**.

You can right-click any file or item in the File List to access a pop-up menu of currently available actions for that item. The pop-up menu contents vary, depending on the type of item selected.

The File List view can be hidden by clicking the small arrow in right border: "Click to show/hide side panel."

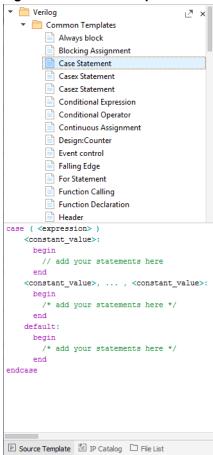

# Source Template

The Source Template is a project view that provides templates for creating VHDL, Verilog, and constraint files. Templates increase the speed and accuracy of design entry. You can drag and drop a template directly to the source file. You can also create your own templates.

To access templates, choose **View > Show Views > Source Template**, or click icon in the toolbar, or click on the **Source Template** tab in the bottom-left pane, to locate and access the following templates:

- Verilog, including common and Parameterized Module Instantiation (PMI),

Primitives, Attributes, Encryption, and User Templates

- VHDL, including common, PMI, Primitives, Attributes, Encryption, and User Templates

- Constraints for LSE, including Timing and Physical constraints and User Templates

#### Note

For more information on PMI, refer to the Radiant software online help. See **User Guides > Entering the Design > Designing with Soft IP, Modules, and PMI > PMI or IP Catalog?**

You can simply drag any template and drop it into your source file.

Figure 21: Source Template

# **IP Catalog**

IP Catalog enables you to customize a collection of functional blocks from Lattice Semiconductor. Through the IP Catalog, you can access two types of functional blocks, Modules and IP.

To access IP catalog, choose **View > Show Views > IP Catalog**, or click icon in the toolbar, or click on the **IP Catalog** tab in the bottom-left pane.

Figure 22: IP Catalog

Each module is configurable with a unique set of properties. Once generated, the module or IP appears in your design's File List.

## **Process**

A process is a specific task in the overall processing of a source or project. Typical processing tasks include synthesizing, mapping, placing, and routing. You can view the available processes for a design in the Process Toolbar.

Figure 23: Process Toolbar

For more detail of different designs and Export Files available, see "Process Flow" on page 18.

## Task Detail View

Click Task Detail View 🛅 to see detailed information of each process.

The default design flow processes are marked by check marks. To enable the remaining tasks, either check-mark the specific task and rerun the process step, or double-click the task's name. You can also right-click on the task to show the context menu.

Once the process has finished, the process status icon next to the task replaces the gray dot.

Figure 24: Task Detail View

Processes are grouped into categories according to their functions. To learn more about each process, view "Design Flow Processes" on page 55.

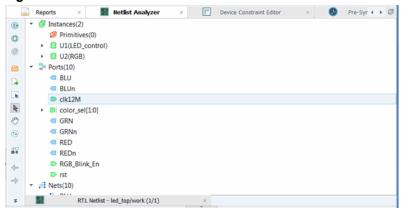

# Hierarchy

The Hierarchy view is a project view that displays the design hierarchy and is displayed by default. The hierarchical view is available when File List tab is selected.

Figure 25: Hierarchy View

If you would prefer that it not open by default, simply close Hierarchy View. The next time you launch the Radiant software, the Hierarchy View will not be opened. You can open it manually by selecting it from the View > Show View menu.

Right-click any of the objects in the Hierarchy View to see the available actions.

Figure 26: Hierarchy Item Pop-up Menu

The Hierarchy view can be selected, closed, and opened.

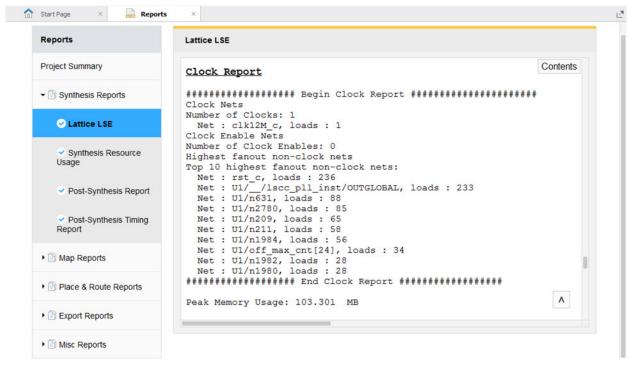

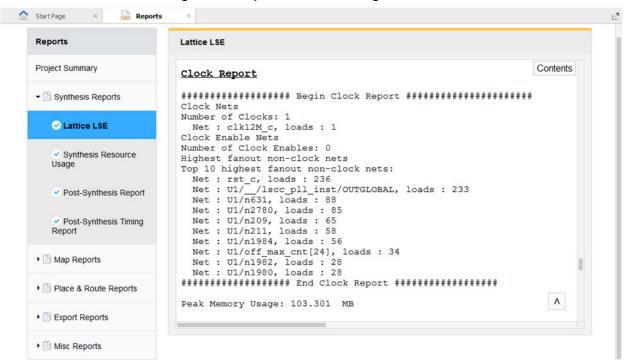

# Reports

The Reports View provides a centralized reporting mechanism in the Tools view area. The Reports View is automatically displayed and updated when processes are run. It provides a separate tab for the current implementation, enabling you to compare results quickly.

The right pane displays the report for the selected step. You can also click the icon in the toolbar.

Figure 27: Reports View

The Reports pane on the right shows the detail of the project summary and resource usage.

The Report View can be selected, closed, opened, detached, and attached with the Attach button. See "Basic UI Controls" on page 26.

## **Tool Views**

The Tool view area of the UI displays the tools that are currently active. Each tool that you have opened from the toolbar or the Tools menu is displayed. The Reports and Start page, which can be opened from the toolbar or the Windows menu, are also displayed. When multiple tools are active, the display can be controlled with the tab group functions in the Window menu. See "Common Tasks" on page 34 for more information on tab group functions.

Each tool view is specific to its tool and can contain additional toolbars, multiple panes, or multiple windows controlled by additional tabs. See "Working with Tools and Views" on page 69 for descriptions of each tool and view, plus details on controlling their display.

The Tool views can be selected, closed, opened, detached, and attached using the Attach button. See "Basic UI Controls" on page 26

Figure 28: Tool View Tab Title

## Tcl Console

The Tcl Console is an integrated console for Tcl scripting. You can enter Tcl commands in the console to control all of the functionality of the Radiant software. Use the Tcl help command (help <tool\_name>\*) to display a list of valid extended Tcl commands.

Figure 29: Tcl Console

```

> neip prj*

∠" ×

Commands

| Description

prj activate impl

| Activate implementation in the current project

prj_add_source

| Add sources to the current project

prj_archive

| Archive the current project

| Clean up the implementation result files in the current project

prj_clean_impl

prj_clone_impl

| Clone an existing implementation

prj_close

| Close the current project

prj_copy_strategy

| Create a new strategy by copying from an existing strategy

prj_create

| Create a new project

| Create a new implementation in the current project

prj_create_impl

prj_create_strategy

| Create a new strategy with default setting

prj_disable_source

\ | \ \mbox{Disbale} the design sources from the current project

| Enable the design sources from the current project

prj_enable_source

Import an existing strategy file

prj_import_strategy

prj_list_strategy

| List value of strategy items

```

## **Output**

The Output View is a read-only area where tool output is displayed.

Figure 30: Output View

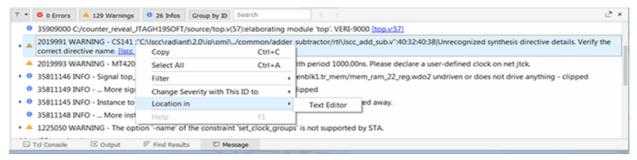

## Message

There are three message types available:

- Errors are displayed in red.

- Warnings are displayed in orange.

- General Information is displayed in blue.

A red dot in the Message tab provides a visual notification that a new message/warning was received. Once you view the notification, the dot disappears.

Right-clicking a message provides a menu of commands, including Location in > Text Editor, which opens the source file in the Source Editor and highlights the location of the problem.

Figure 31: Message Display

## Find Results

The Edit > Find in Files command enables you to search for information in the files within your project directory. The search results are then displayed in the Find Results view.

Figure 32: Find Results View

```

.dk12M_c(dk12M_c)); /* synthesis lineinfo="@4(158[4],158[15])"*/

RED_c, GRN_c, BLU_c, GND_net, color_sel_c_1, dk12M_c);

input dk12M_c;

wire dk24M_f* synthesis is_dock=1 */; /* synthesis lineinfo="@3(104[6],104[12])"*

wire dk12M_c /* synthesis is_dock=1 */; /* synthesis lineinfo="@4(83[2],83[8])"*/

FD1P3XZ grn_peak_i1 (.D(grn_set[0]),.SP(VCC_net),.CK(dk24M),.SR(rst_c),

FD1P3XZ curr_blu_j17 (.D(culr_blu_j17__N_451[17]),.SP(VCC_net),.CK(dk24M),

FD1P3XZ RGB_color_s_i1 (.D(culr_blu_j17__N_451[6]),.SP(VCC_net),.CK(dk24M),

FD1P3XZ dur_blu_j16 (.D(culr_blu_j17__N_451[6]),.SP(VCC_net),.CK(dk24M),

FD1P3XZ curr_blu_j15 (.D(culr_blu_j17__N_451[15]),.SP(VCC_net),.CK(dk24M),

FD1P3XZ ourr_blu_j15 (.D(culr_blu_j17__N_451[15]),.SP(VCC_net),.CK(dk24M),

FD1P3XZ ourr_blu_j15 (.D(culr_blu_j17__N_451[15]),.SP(VCC_net),.CK(dk24M),

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(97)

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(110):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(119):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(121):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(122):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(250):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(261):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(265):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(269):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(273):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(277):

C:/my_radiant_tutorial/LEDtest/impl_1/led_top_prim.v(281):

☐ Td Console ☐ Output ☐ Message ☐ Find Results

```

## Common Tasks

The Radiant software UI controls many tools and processes. The following sections describe some of the more commonly performed tasks.

# **Controlling Views**

All of the views in the Radiant software are controlled in a similar manner, even though the information they contain varies widely. Here are some of the most common operations:

- Open Use the View > Show Views menu selections or right-click in the menu or toolbar areas to select a view from the pop-up menu.

- Select If a view is already open you can select its tab to bring it to the front.

- ▶ Detach Click the detach button in the upper right corner of the view.

- ▶ Attach Click the attach button ☐ in the upper right corner of the view.

- Move Click and hold a view's tab, and then drag and drop the view to a different position among the open views.

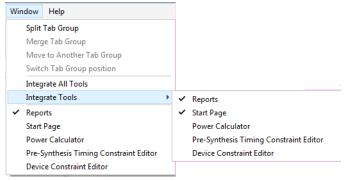

**Using a Tab Group** You can use the Window menu to split off a view and control it as a separate tab group. This allows you to examine two open views side by side. The controls work as follows:

- ▶ Split Tab Group displays two views side by side. See Figure 33.

- Move to Another Tab Group moves the selected tab to the other tab group. See Figure 34.

- Merge Tab Group merges a split tab group back into the primary view

- ▶ Switch Tab Group Position switches the positions of the two tab groups.

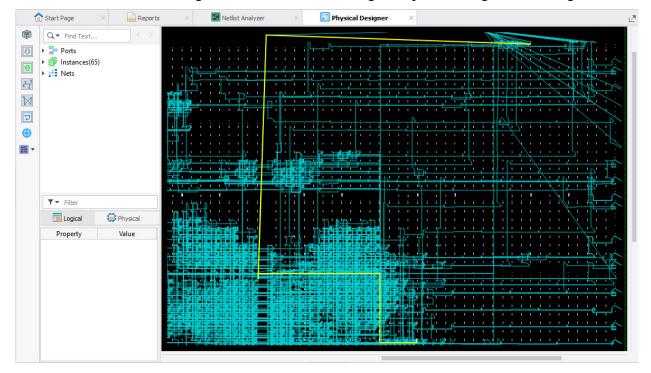

Figure 33: After Split Tab Group Command Used on Physical Designer

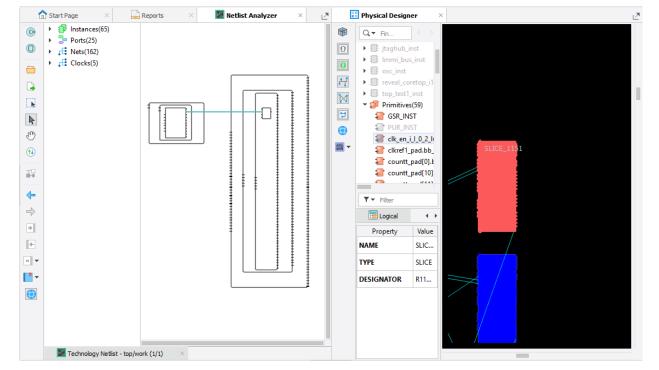

Figure 34: After Move to Another Tab Group Used on Netlist Analyzer

# **Cross-Probing**

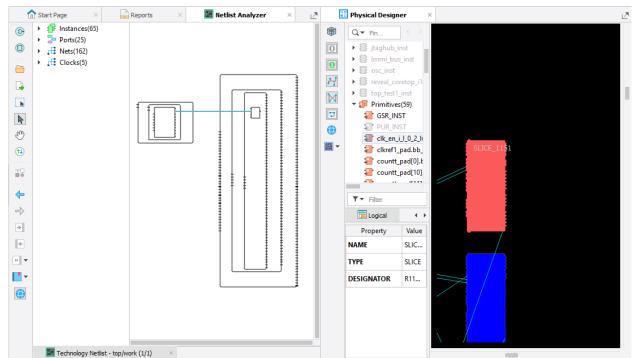

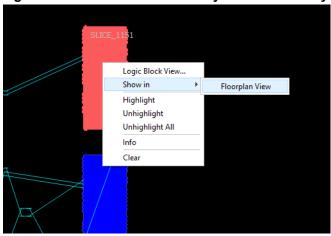

It is possible to select a data object in one view and see that same data object in a different view or views. Right-click an object to see if cross-probing is available. If it is, you will see a **Show In** sub-menu with the available views listed. If you select a view that is not yet open, the Radiant software will open it automatically. Cross-probing is available between Floorplan View and Physical View of Physical Designer, and from Netlist Analyzer to Physical Designer.

Figure 35: Show In Menu from Physical View of Physical Designer

During the Radiant flow, various timing analyses and reports are created. You can view a specific path in Netlist Analyzer, Physical Designer's Floorplan View, and Physical Designer's Physical View. This allows for flexibility and reduced debugging effort.

#### NOTE

Cross-probing to Netlist Analyzer is available only if the selected synthesis tool is LSE.

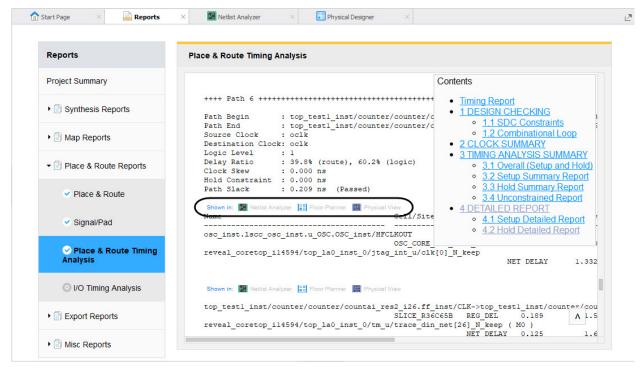

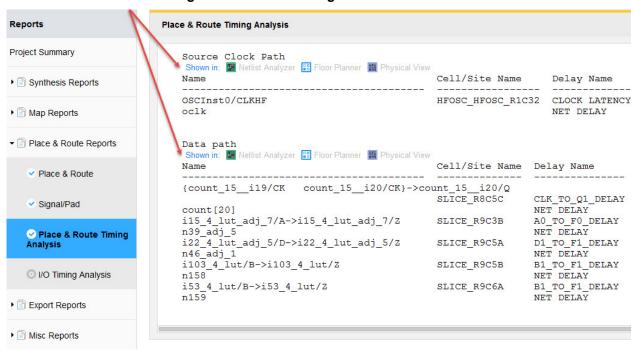

In the Reports tab, view any timing analysis report and identify a path to view. If cross-probing is available, the specific icon tools become visible, as shown in the following figure.

Figure 36: Available tools for Path Cross-Probing

Click on an icon and the tool opens with the selected path.

In some cases, the tool is unable to find the path. The message "Can't show the schematic of this timing path." appears. In an encrypted design, in some cases, cross-probing is not available. The message "Cannot open encrypted design." appears.

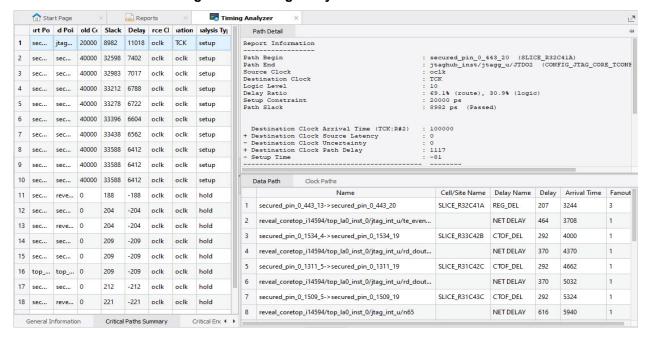

The following figures show cross-probing a path from the Place & Route Timing Analysis report to Netlist Analyzer, Physical Designer's Floorplan View, and Physical Designer's Physical View.

Figure 37: Path Cross-Probing in Reports

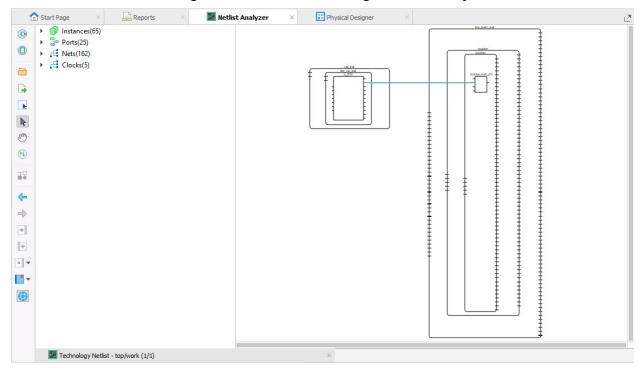

By clicking on the Netlist Analyzer icon, you can preview the data path in Netlist Analyzer.

Figure 38: Path Cross-Probing in Netlist Analyzer

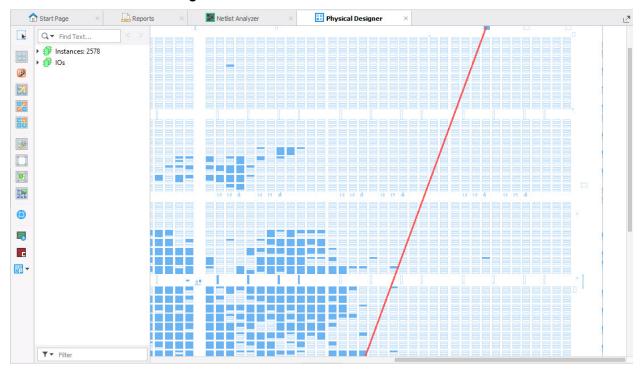

Similarly, by clicking on the Floor Planner icon, you can easily view the same path in Physical Designer's Placement Mode.

Figure 39: Path Cross-Probing in Physical Designer's Placement Mode

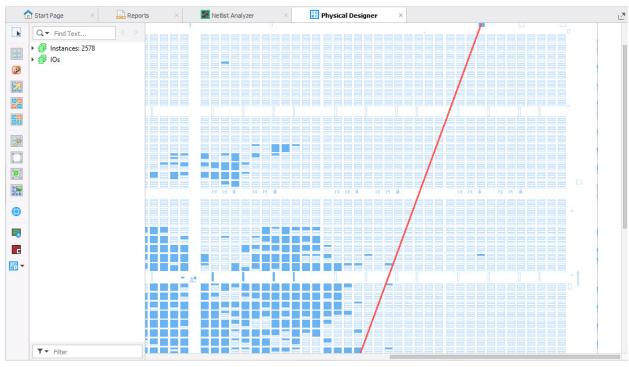

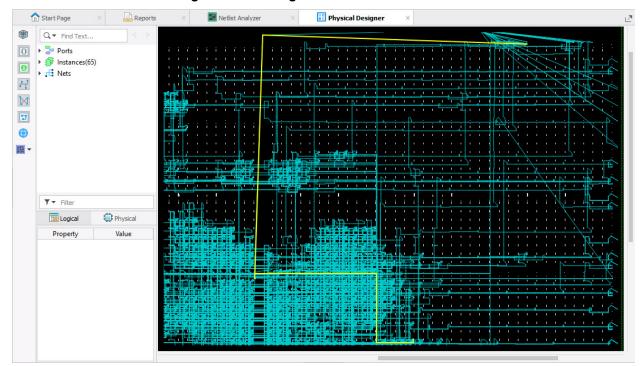

The same path is viewable in Physical Designer's Routing Mode by clicking on the Physical View icon in a timing report.

Figure 40: Path Cross-Probing in Physical Designer's Routing Mode

# Chapter 5

# **Working with Projects**

This chapter covers projects and their elements. Implementations and strategies are explained and some common project tasks are shown.

#### Overview

A project is the top organizational element in the Radiant software design environment. Projects consist of design, constraint, configuration and analysis files. Only one project can be open at a time, and a single project can include multiple design structures and tool settings.

You can create, open, or import a project from the Start Page. Refer to "Getting Started" on page 10 for instructions on creating a new project.

Figure 41: Default Start Page

The File List view shows a project and its main elements.

Figure 42: Project Files in File List

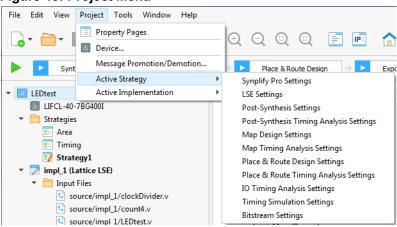

The Project menu commands enable you to do the following:

- Examine the project properties.

- Change the target device.

- Change the severity level of warning messages.

- Set the synthesis tool.

- Show the active strategy tool settings.

- Set the top level design unit.

Figure 43: Project Menu

### **Implementations**

An implementation is the structure of a design and can be thought of as *what* is in the design. For example, one implementation might use inferred memory while another implementation uses instantiated memory. Implementations also define the constraint and analysis parameters for a project.

There can be multiple implementations in a project, but only one implementation can be active at a time. And there must be one active implementation. Every implementation has an associated active strategy. Strategies are a shared pool of resources for all implementations and are discussed in the next section. An implementation is created whenever you create a new project.

Implementations consist of the following files:

- Input files

- Pre-Synthesis constraint files

- Post-Synthesis constraint files

- Debug files

- Script files

- Analysis files

- Programming files

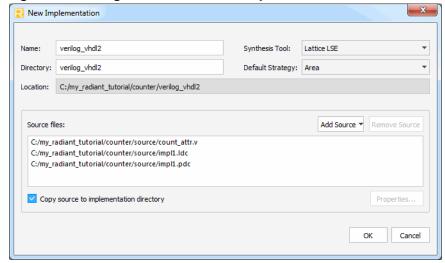

# **Adding Implementations**

#### To add a new implementation to an existing project:

1. Right-click the project name in the File List project view.

Select **Add > New Implementation**. In the New Implementation dialog box, you can set the implementation name, directory, default strategy, and add source files. When you select **Add Source** you have a choice of browsing for the source files or using a source from an existing implementation.

Name: verilog\_vhdl2 Synthesis Tool: Lattice LSE

Directory: verilog\_vhdl2 Default Strategy: Area

Location: C:/my\_radiant\_tutorial/counter/verilog\_vhdl2

Source files:

C:/my\_radiant\_tutorial/counter/source/count\_attr.v

C:/my\_radiant\_tutorial/counter/source/impl1.ldc

C:/my\_radiant\_tutorial/counter/source/impl1.pdc

C:/my\_radiant\_tutorial/counter/source/impl1.pdc

C:/my\_radiant\_tutorial/counter/source/impl1.pdc

OK Cancel

Figure 44: New Implementation

Notice that you have the option to "Copy source to implementation directory." If this option is selected, the source files will be copied from the existing implementation to the new implementation, and you will be working with different source files in the two implementations. If you want the two implementations to share the same source files and stay in sync, make sure that this option is not selected.

To make an implementation active, right-click its name in the File List and choose **Set as Active Implementation**.

To add a file to an implementation, right-click the implementation name or any file folder in the implementation and choose **Add > New File** or **Add > Existing File**.

# **Cloning Implementations**

#### To clone an implementation:

- 1. In the File List view, right-click on the name of the implementation that you want to copy and choose **Clone Implementation**.

- The Clone Implementation dialog box opens.

- 2. In the dialog box, enter a name for the new implementation. This name also becomes the default name for the folder of the implementation.

- 3. Change the name of the implementation's folder in the Directory text box, if desired.

- 4. Decide how you want to handle files that are outside of the original implementation directory. Select one of the following options:

- Continue to use the existing references

The same files will be used by both implementations.

#### Copy files to new implementation source directory

The new implementation will have its own copies that can be changed without effecting the original implementation.

- The Synthesis Tool text box specifies the currently selected synthesis tool.

Go to Project > Active Implementation > Select Synthesis Tool to update your selection.

- 6. The Default Strategy text box specifies the currently selected default strategy.

- 7. Click OK.

## **Input Files**

Input files are the design source files for the project. Input files can be any combination of Verilog, SystemVerilog, and VHDL.

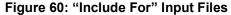

Right-click an input file name to open a pop-up menu of possible actions for that file.

Figure 45: Input File Actions

You can use the "Include for" commands to specify that a source file be included for both synthesis and simulation, synthesis only, or simulation only.

## **Pre-Synthesis Constraint Files**

Synopsys timing constraints are specified in the new .fdc file format. Legacy .sdc formats are still supported in the Radiant software and Synopsys has provided a script called sdc2fdc, which does a one-time conversion of .sdc files to the new .fdc format. More information about this script can be found in the Synplify Pro release notes.

An .fdc file can be added to an implementation if the selected synthesis tool is Synplify Pro. When using Synplify Pro or the Lattice Synthesis Engine (LSE), the constraints files can be saved as an .sdc file. If the selected synthesis tool is LSE, a Lattice design constraint (.ldc) synthesis file can be added. Constraints in the .ldc file use the Synopsys constraint format.

An implementation can have multiple synthesis constraint files. Only one synthesis constraint file can be active at a time. Unlike Post-Synthesis constraints, a synthesis constraint file must be set as active by the user.

# **Post-Synthesis Constraint Files**

Post-Synthesis constraint files (.pdc) contain both timing and non-timing constraint .pdc source files for storing logical timing/physical constraints. Constraints that are added using the Device Constraint Editor are saved to the active .pdc file. The active post-synthesis design constraint file is then used as input for post-synthesis processes.

An implementation can have multiple .pdc files, but only one can be active at a time.

Figure 46: Sample .pdc File

```

impl1.pdc

ldc set location -site P5 [get ports clk]

#ldc_create_region -name RgnA -site R8C2D -width 18 -height 12

#ldc create_group -name UgrpA [get_cells counter1]

#ldc_set_location -region RgnA [ldc_get_groups UgrpB]

#ldc create group -name UgrpC -bbox {2 3} [get cells counter3]

#ldc_set_location -site R8C25D [ldc_get_groups UgrpC]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[2]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[3]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[0]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count2t[1]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[0]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[1]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[2]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[3]}]

14

ldc set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[4]}]

16

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[5]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[6]}]

ldc_set_port -iobuf {IO_TYPE=LVCMOS25} [get_ports {count3t[7]}]

#ldc_set_location -site 35 [get_ports clk1]

create_clock -period 15 [get_nets counter1/clk1_c]

```

Figure 47 shows a high-level flow of how constraints from multiple sources can be used and modified in the Radiant software.

Figure 47: Radiant software Constraints Flow Chart

# **Debug Files**

The files in the Debug folder are project files for Reveal Inserter. They are used to insert hardware debug into your design. There can be multiple debug files, and one can be set as active. To insert hardware debug into your design, right-click a debug file name and choose **Set as Active Debug File** from the pop-up menu. The debug file name becomes bold, indicating that it is active. It is not required to have an active debug file.

# **Script Files**

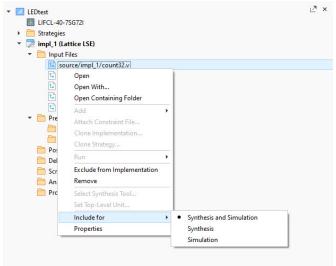

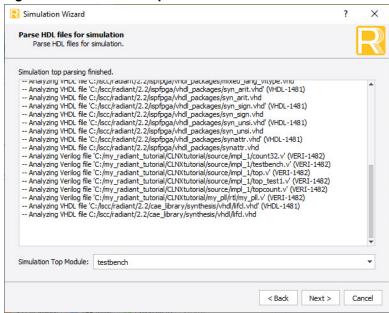

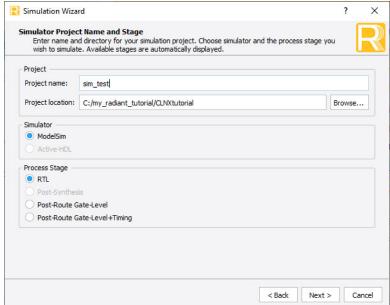

The Script Files folder contains the scripts that are generated by the Simulation Wizard. After you run the Simulation Wizard, the steps are stored in a simulation project file (.spf), which can be used to control the launching of the simulator.

? X Simulation Wizard Simulator: Active-HDL Project Name: sim1 Project Location: C:/my\_radiant\_tutorial/tce\_ldc\_test/tce\_ldc\_test Simulation Stage: RTL C:/my\_radiant\_tutorial/tce\_ldc\_test/tce\_ldc\_test/source/typepackage.vhd C:/my\_radiant\_tutorial/tce\_ldc\_test/tce\_ldc\_test/source/LEDtest.v C:/mv radiant tutorial/tce ldc test/tce ldc test/source/count4.v C:/my\_radiant\_tutorial/tce\_ldc\_test/tce\_ldc\_test/source/count8.vhd C:/my radiant tutorial/tce ldc test/tce ldc test/source/clockDivider.v C:/my\_radiant\_tutorial/tce\_ldc\_test/tce\_ldc\_test/source/topcount.v C:/my\_radiant\_tutorial/tce\_ldc\_test/tce\_ldc\_test/source/testbench.v Simulation Libraries: ovi\_ice40up Simulation Top Module: testbench Run simulator Add top-level signals to waveform display Run simulation Cancel

Figure 48: Simulation Script File

# **Analysis Files**

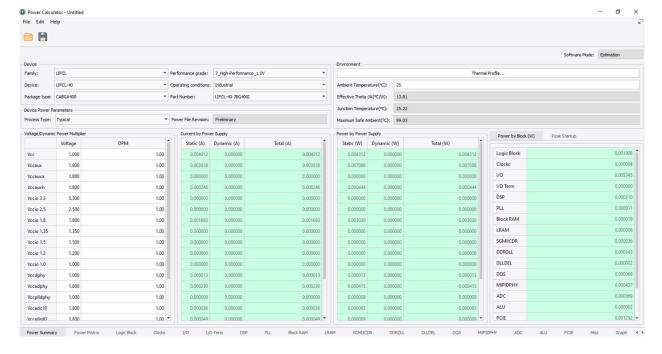

The Analysis Files folder contains Power Calculator files (.pcf). The folder can contain multiple analysis files, and one (or none) can be set as active. The active or non-active status of an analysis file affects the behavior of the associated tool view.

# **Programming Files**

Programming files (.xcf) are configuration scan chain files used by the Radiant Programmer for programming devices. The .xcf file contains information about each device, the data files targeted, and the operations to be performed.

An implementation can have multiple .xcf files, but only one can be active at a time. The file must be set as active by the user.

# **Strategies**

Strategies are collections of all the implementation-related tool settings in one convenient location. Strategies can be thought of as recipes for how the design will be implemented. An implementation defines what is in the design, and a strategy defines how that design will be run. There can be many strategies, but only one can be active at a time. There must be one active strategy for each implementation.

The Radiant software provides two predefined strategies: Area and Timing. It also enables you to create customized strategies. Predefined strategies cannot be edited, but they can be cloned, modified, and saved as customized user strategies. Customized user strategies can be edited, cloned, and removed. All strategies are available to all of the implementations, and any strategy can be set as the active one for an implementation.

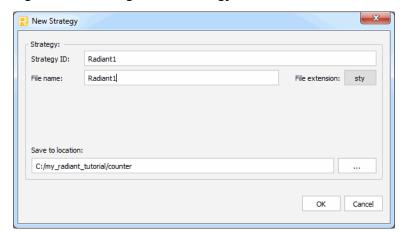

To create a new strategy from scratch, choose File > New > Strategy. In the New Strategy dialog box, enter a name for the new strategy. Specify a file name for the new strategy and choose a directory to save the strategy file (.sty).

Figure 49: Creating a New Strategy from Scratch

The new strategy is with all the default settings of the current design. You can modify its settings in the Strategies dialog box.

If you want to save the strategy changes to your current project, choose File > Save Project from the Radiant software main window.

To create a new strategy from an existing one, right-click the existing strategy and choose Clone <strategy name> Strategy. Set the new strategy's ID and file name.

Clone Strategy1 Strategy Strategy: Strategy ID: strategy2 strategy2 File extension: sty File name: Save to location: C:/my\_radiant\_tutorial/counter Cancel

Figure 50: Cloning to Create a New Strategy

To make a strategy active, right-click the strategy name and choose Set as Active Strategy.

To change the settings in a strategy:

- 1. Double-click the strategy name in the File List view

- 2. Select the option type to modify

- 3. Double-click the Value of the option to be changed

The default values are displayed in plain blue text. Modified values are displayed in italic bold text.

Strategies are design data independent and can be exported and used in multiple projects.

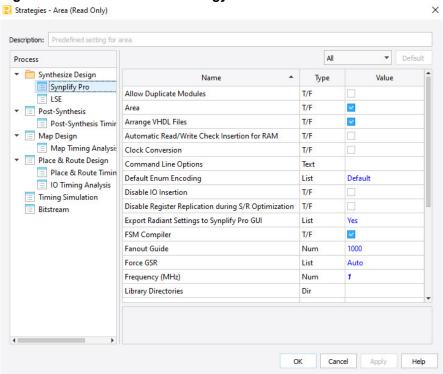

#### Area

The Area strategy is a predefined strategy for area optimization. Its purpose is to minimize the total logic gates used while enabling the tight packing option available in Map.

Applying this strategy to large and dense designs might cause difficulties in the place and route process, such as longer time or incomplete routing.

Figure 51: Area Predefined Strategy

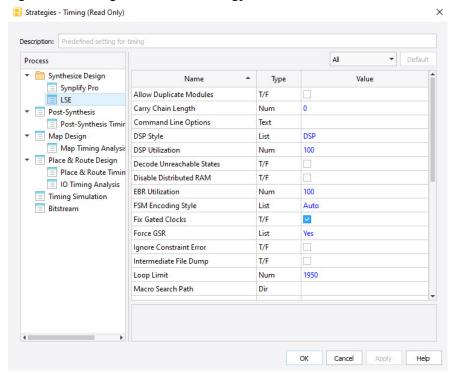

# **Timing**

The Timing strategy is a predefined strategy for timing optimization. Its purpose is to achieve timing closure. The Timing strategy uses a very high effort level in placement and routing. Use this strategy if you are trying to reach the maximum frequency on your design. If you cannot meet your timing requirements with this strategy, you can clone it and create a customized strategy with refined settings for your design. This strategy might increase your place-and-route run time compared to the Area strategy.

Figure 52: Timing Predefined Strategy

#### **User-Defined**

You can define your own customized strategy by cloning and modifying any existing strategy. You can start from either a predefined or a customized strategy.

#### **Common Tasks**

Working with projects includes many tasks, including: creating the project, editing design files, modifying tool settings, trying different implementations and strategies, and saving your data.

# **Creating a Project**

See "Creating a New Project" on page 11 for step-by-step instructions.

# **Changing the Target Device**

There are two ways to access the Device Selector dialog box for changing the target device:

- Double-click the device in the project File List view or right-click it and choose Edit.

- Choose Project > Device.

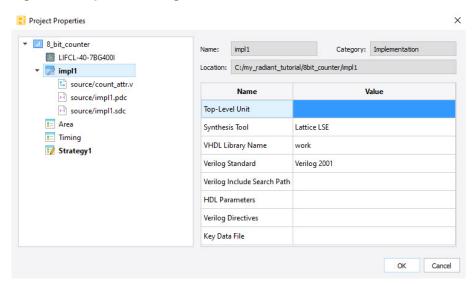

## Setting the Top Level of the Design

If multiple top levels exist in the hierarchy of your HDL source files, you will need to set the top-level design unit. After generating the hierarchy, choose **Project > Active Implementation > Set Top-Level Unit**. Alternatively, right-click the implementation and choose this command from the pop-up menu.

Figure 53: Top-Level Design Unit

In the Project Properties dialog box, select **Value** next to **Top-Level Unit** and select the desired top level from the list.

You can also use the Hierarchy View to set the top-level. Right-click a level you want to be the top-level in the Hierarchy View and choose **Set Top-Level Unit**.

# **Editing Files**

You can open any of the files for editing by double-clicking or by right-clicking and choosing **Open** or **Open with**.

# **Saving Project Data**

In the File menu are the following selections for saving your design and project data:

- Save saves the currently active item.

- ▶ Save As saves the active item using a different file name.

- Save All saves all changed documents.

- Save Project saves the current project.

- ▶ Save Project As saves the active project using a different project name.

- Archive Project creates a zip file of the current project in a location you specify.

# Chapter 6

# Radiant Software Design Flow

This chapter describes the design flow in the Radiant software. Running processes and controlling the flow for alternate what-if scenarios are explained.

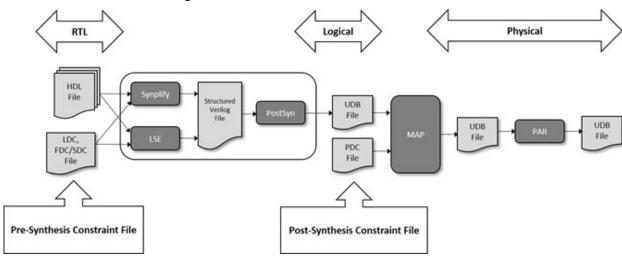

#### Overview

The FPGA implementation design flow in the Radiant software provides extensive what-if analysis capabilities for your design. The design flow is displayed in the Task Detail View at the right end of the Process Toolbar.

Export Files 0 Synthesize Design Lattice Synthesis Engine Post-Synthesis Timing Analysis Post-Synthesis Simulation File ✓ Map Design Map Timing Analysis ✓ Place & Route Design ✓ Place & Route Timing Analysis I/O Timing Analysis Export Files ✓ Bitstream File IBIS Model Gate-Level Simulation File Double click a task to run the flow

Right click to show context menu

Figure 54: Design Flow Shown in Task Detail View

# **Design Flow Processes**

The design flow is organized into discrete processes, where each step allows you to focus on a different aspect of the FPGA implementation.

**Synthesize Design** This process runs the selected synthesis tool (Lattice Synthesis Engine is the default) in batch mode to synthesize your HDL design.

- Synthesis Tool identifies the selected synthesis tool, Lattice Synthesis Engine or Synplify Pro.

- Post-Synthesis Timing Analysis generates timing analysis files.

- Post-Synthesis Simulation File generates a post-synthesis netlist file <file name> syn.vo used for Post-Synthesis Simulation.

**Map Design** This process maps the design to the target FPGA and produces a mapped Unified Database (.udb) design file. Map Design converts a design's logical components into placeable components.

Map Timing Analysis - generates timing analysis files.

**Place & Route Design** This process takes mapped physical design files and places and routes the design. The output can be processed by the design implementation tools. Timing analysis files can also be generated.

- Place & Route Timing Analysis generates timing analysis files.

- ► I/O Timing Analysis generates I/O timing analysis files.

**Export Files** This process generates the IBIS, simulation, and programming files that you have selected for export:

- ▶ Bitstream File generates a configuration bitstream (bit images) file, which contains all of the design's configuration information that defines the internal logic and interconnections of the FPGA, as well as device-specific information from other files.

- ▶ IBIS Model generates a design-specific I/O Buffer Information Specification model file (.ibs). IBIS models provide a standardized way of representing the electrical characteristics of a digital IC's pins (input, output, and I/O buffers).

- Gate-Level Simulation File generates a Verilog netlist of the routed design that is back annotated with timing information. This generated .vo file enables you to run a timing simulation of your design.

The files for export can also be generated separately by double-clicking each one.

## **Running Processes**

You can perform the following actions for each step in the process flow:

- Run runs the process, if it has not yet been run.

- Force Run- reruns a process that has already been run.

- Force Run From Start reruns all processes from the start to the selected process.

- Stop stops a running process.

- Clean Up Process clears the process state and puts a process into an initial state as if it had not been run.

The state of each process step is indicated with an icon to the left of the process. The process status icons description is described in "Process" on page 29

The Reports View displays detailed information about the process results, including the last process run. The Messages section shows warning and error messages and allows you to filter the types of messages that are displayed. See "Reports" on page 31.

Figure 55: Reports View of Last Process Run

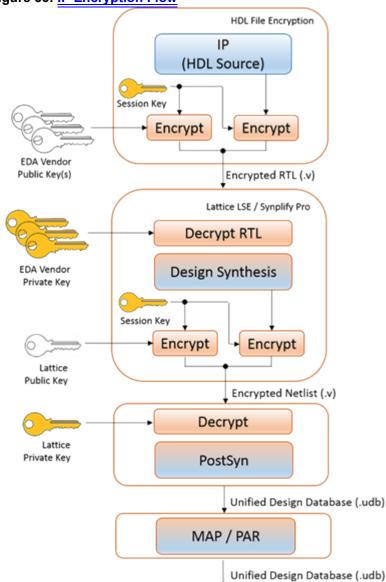

### **IP Encryption Flow**

IP encryption flow enables you to protect your IP design. Following the industry standard, the Radiant software, through the IP encryption flow, allows the partnership between the IP Vendor, supported EDA vendor, and Lattice Semiconductor.

Figure 56: IP Encryption Flow

The encryption flow uses symmetric and asymmetric encryption methods to maximize the design security. The symmetric method only involves a single symmetric key for both, encryption and decryption. The asymmetric method involves the public-private key pair. The public key is published by a vendor and is used by the Radiant software. The private key is never revealed to the public.

The Radiant software supports these cryptographic algorithms:

- ▶ AES-128/AES-256: symmetric algorithm used to encrypt the content of the HDL source file.

- RSA-2048: asymmetric algorithm used to obfuscate a key used in HDL file encryption. The RSA is defined by the public-private key pair. You must be familiar with both keys in order to perform RSA decryption.

# **HDL File Encryption Flow**

The current software version supports encryption of a single HDL source file per a single command.

The overall HDL file encryption flow is summarized in these steps:

- The source file of the IP design is AES encrypted using a symmetric session key. The AES encryption uses the CBC-128 or CBC-256 algorithm. In the source files, this section is referred to as a data block.

- The session key is RSA encrypted using the vendor's Public Key. In the source files, this section is referred to as a key block. Multiple key blocks may be present in the source file.

- The encrypted Session key and the encrypted design are merged to a file generally named the Encrypted RTL.

Each encrypted source file contains a single data block and one or more key blocks. The number of key blocks depends on the number of provided vendor's public keys.

#### Note

To decrypt an encrypted source file, you must perform the IP encryption flow steps in the reverse order.

During the next step in the design flow, typically synthesis, the Encrypted RTL is decrypted to access the original IP design, as shown in the following figure.

**HDL Source File AES** encryption Session Key **RSA** encryption RSA Public Kevs Encrypted key **Encrypted data** of EDA Vendors Encrypted RTL

Figure 57: HDL Encryption Flow

By separating the encryption of data and key, you can use public keys from different vendors to encrypt the same HDL file.

For more information on how to perform HDL encryption, refer to "Running HDL Encryption from the Command Line" on page 914.

# **HDL File Encryption Steps**

This section provides step-by-step instructions on how to encrypt an HDL file.

The Radiant software provides the key templates you can simply drag-and-drop into an HDL file. Each key template is specific to an EDA vendor providing the value of a public key.

To view the templates in Project Navigator, go to the Source Template tool. Open the **Verilog > Encryption Templates** folder and select the EDA-specific key template.

Currently, the Radiant software supports these encryption templates:

- Lattice Semiconductor

- Synplicity-1

- Synplicity-2

- Mentor

- Synopsys

- Aldec

- Cadence

- ▶ Combined Sample: provides an example of file holding multiple keys.

#### Step 1: Prepare the HDL file.

Annotate the HDL source file with protected pragmas. Protected pragmas provide information regarding the type of the key used to encrypt the HDL file, the name of the key, and the encryption algorithm.

In this example, the HDL source file will be encrypted by the Lattice Public Key.

```

'pragma protect version=1

'pragma protect encoding=(enctype="base64")

// optional information

'pragma protect author="<Your_Name>"

'pragma protect author_info="<Your_Information>"

```

# Step 2: Specify the portion of the HDL source file to encrypt.

Annotate the HDL file to specify the encryption. Only the portion defined within these protected pragmas is encrypted.

```

'pragma protect begin

// HDL portion that should be encrypted

'pragma protect end

```

#### Step 3: Prepare key.

Define the key with which the HDL file should be encrypted. Each key definition must contain the following information:

- key keyowner: specify the owner of the key

- key\_keyname: specify the name of the key. Same owner may provide multiple keys.

- key\_keymethod: specify the used cryptographic algorithm. Current version supports RSA algorithm.

- key\_public\_key: speficy the exact value of the key.

The key definition can be done in two ways:

**Defining the key in the key.txt file:** The public encryption key or keys can be defined in any .txt file. The key file may contain a single public key or a list of all available public keys. In the Radiant software, all common EDA vendor public keys are located in <a href="mailto:rectory">Radiant\_install\_directory</a>/ispfpga/data/key.txt file.

The following is an example of Lattice Public Key defined in key.txt file:

```

'pragma protect key_keyowner= "Lattice Semiconductor"

'pragma protect key_keyname= "LSCC_RADIANT_2"

'pragma protect key_method="rsa"

'pragma protect key_public_key

MIIBIjANBgkqhkiG9w0BAQEFAAOCAQ8AMIIBCGKCAQEA0EZKUUhbuB6vSsc70hQJ

iNAWJR5unW/OWp/LFI71eAl3s9bOYE2OlKdxbai+ndIeo8xFt2btxetUzuR6Srvh

xR2Sj9BbW1QToo2u8JfzD3X7AmRvlwKRX8708DPo4LDHZMA3qh0kfDDWkp2Eausf

LzE2cVxgq7fy/bDhUeN8xKQCSKJ7aguG6kOI6ROoZz21ljzDLUQzhm2qYF8SpU1o

tD8/uw53wLfSuhR3MBOB++xcn2imvSLqdgHWuhX6CtzIx5CD4y8inCbcLy/0Qrf6

sdTN5SAg2OZhjeNdzmqSWqhL2JTDw+Ou2fWzhEd0i/HN0y4NMr6h9fNn8nqxRyE7

IwIDAQAB

```

**Defining the key directly in the HDL file:** You may define the Public Key directly in the HDL file. You may define one or more keys.

```

'pragma protect key_keyowner= "Lattice Semiconductor"

'pragma protect key_keyname= "LSCC_RADIANT_2"

'pragma protect key_method="rsa"

'pragma protect key_method="rsa"

'pragma protect key_public_key

MIIBIjANBgkqhkiG9w0BAQEFAAOCAQ8AMIIBCgKCAQEA0EZKUUhbuB6vSsc70hQJ

iNAWJR5unW/OWp/LFI71eAl3s9bOYE2OlKdxbai+ndleo8xFt2btxetUzuR6Srvh

xR2Sj9BbW1QToo2u8JfzD3X7AmRvlwKRX8708DPo4LDHZMA3qh0kfDDWkp2Eausf

LzE2cVxgq7fy/bDhUeN8xKQCSKJ7aguG6kOI6ROoZz21ljzDLUQzhm2qYF8SpU1o

tD8/uw53wLfSuhR3MBOB++xcn2imvSLqdgHWuhX6CtZIx5CD4y8inCbcLy/0Qrf6

sdTN5SAg2OZhjeNdzmqSWqhL2JTDw+Ou2fWzhEd0i/HN0y4NMr6h9fNn8nqxRyE7

IWIDAOAB

```

If the key is defined directly in the HDL file, you don't need to provide the -k option in the <code>encrypt</code> hdl command.

#### **Note**

The key defined directly in an HDL source file has preference over the key defined in the key.txt file.

# Step 4: Select the encryption algorithm for data encryption.

The Radiant software supports both a 128-bit and a 256-bit advanced encryption standard (AES) with CBC mode. Select the type of algorithm by defining one of the two options. The default is set to 256-bit AES with CBC mode.

```

`pragma protect data_method="aes128-cbc"

or

`pragma protect data method="aes256-cbc"

```

#### Step 5: Run the encrypt\_hdl Tcl command.

In the Tcl console window, type in the command to encrypt an HDL file. The option -k may or may not be used depending the location of the key file. The language selection (-1) and creation of new output file (-0) are optional. The default is Verilog. If you don't specify the output file, the tool generates a new output file named <input\_file\_name>\_enc.v.

If the key was defined in the key.txt file: The command will encrypt the HDL file with all keys defined in the key.txt file.

```

encrypt_hdl -k <keyfile> -l <verilog | vhdl> -o <output_file>

<input_file>

```

#### If the key was defined directly in the HDL file:

```

encrypt_hdl -l <verilog | vhdl> -o <output_file> <input_file>

```

The encrypted file is located at the path specified in the <code>encrypt\_hdl</code> command.

# Step 6: Activate the encrypted HDL source file in the project file.

In the File List view, add the generated file to the project. Right-click on the encrypted file and choose **Include in Implementation**.

To see an example of a Verilog or VHDL pragma-annotated HDL source file, see "Defining Pragmas" on page 916.

# Implementation Flow and Tasks

Implementations organize the structure of your design and allow you to try alternate structures and tool settings to determine which ones will give you the best results.

To help determine which scenario best meets your project goals, use a different implementation of a design using the same tool strategy, or run the same implementation with different strategies. Each implementation has an associated active strategy, and when you create a new implementation you must select its active strategy.

To try a new implementation with different strategies, you must create a new implementation/strategy combination.

- 1. Right-click the project name in File List.

- 2. Choose Add > New Implementation.

- 3. In the dialog box, choose a source file from an existing implementation using the Add Source drop-down menu.

- 4. Choose a strategy using the Default Strategy drop-down menu.

Figure 58: Adding a Source to a New Implementation

To use the same source for new and existing implementations, make sure that the "Copy source to implementation directory" option is not selected. This will ensure that your source is kept in sync between the two implementations.

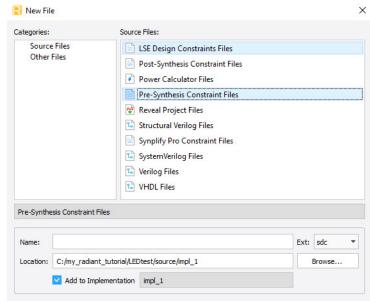

## **Synthesis Constraint Creation**

Synthesis constraints can be added to a design implementation in the format of the Synopsys Design Constraint language, while constraints can be added in the Synopsys standard timing constraints format in the form of FPGA Design Constraint (LDC, PDC, or FDC format) files.

If you are using the Lattice Synthesis Engine, the synthesis constraints will be included in an .ldc file. If you are using Synplify Pro for synthesis, the constraints will be included in an .fdc file. The older .sdc file format is also supported for constraints.

To create a new synthesis constraint file, right-click the Synthesis Constraint Files folder in the File List pane and choose **Add > New File**. In the New File dialog box, select one of the following and give the file a name:

- Pre-Synthesis Constraint Files (.ldc)

- Post-Synthesis Constraint Files (.pdc)

- Synplify Pro Constraint Files (.fdc)

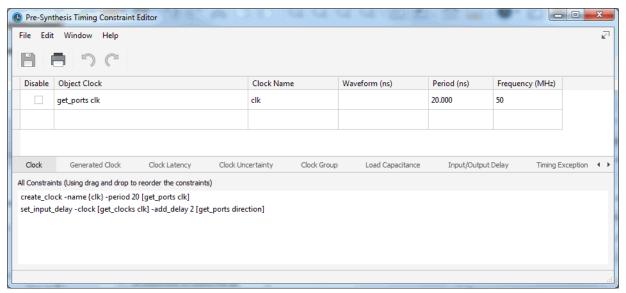

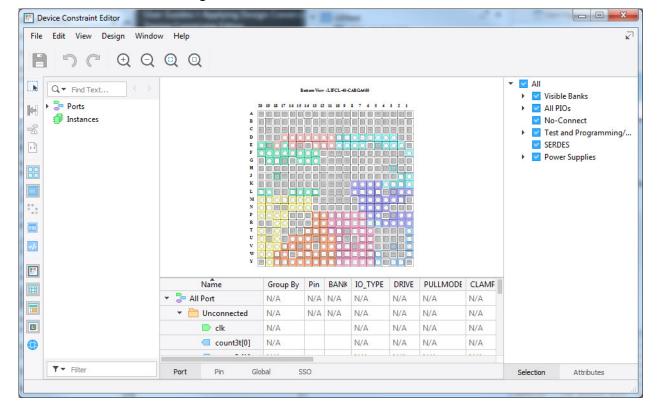

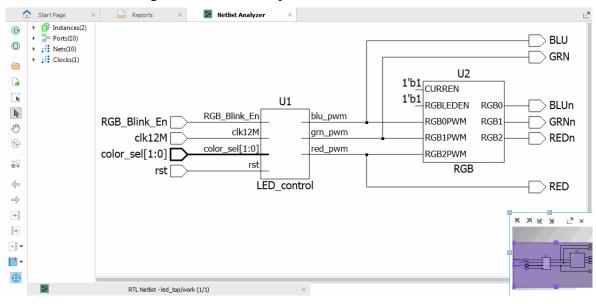

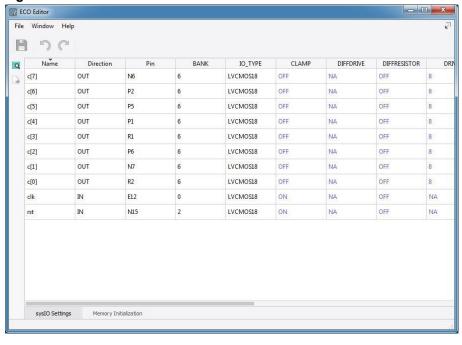

Figure 59: New Synthesis Constraint Files