# MIPI CSI-2 Virtual Channel Aggregation with CrossLink-NX Devices

**Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents                            |    |

|-------------------------------------|----|

| Acronyms in This Document           |    |

| 1. Introduction                     | 6  |

| 1.1. Supported Device and IP        | 6  |

| 1.2. Features List                  | 6  |

| 1.3. Block Diagram                  | 6  |

| 1.4. RX and TX Permutations         |    |

| 2. Parameters and Port List         | 10 |

| 2.1. Synthesis Directives           | 10 |

| 2.2. Simulation Directives          | 14 |

| 2.3. Top-Level I/O                  | 17 |

| 3. Design and Module Description    |    |

| 3.1. rx0*_unit                      | 20 |

| 3.1.1. rx_dphy_0*                   | 20 |

| 3.1.2. csi2_parser                  | 22 |

| 3.1.3. rx_buffer                    | 23 |

| 3.2. tdm_ctrl                       |    |

| 3.3. tx_dphy_if                     |    |

| 3.4. tx_dphy                        | 27 |

| 3.5. int_osc                        |    |

| 3.6. int_gpll                       |    |

| 4. Design and File Modifications    |    |

| 4.1. Top-Level RTL                  |    |

| 4.2. rx0*_unit                      |    |

| 4.3. Post Synthesis Constraint File |    |

| 5. Design Simulation                |    |

| 6. Known Limitations                |    |

| 7. Design Package and Project Setup |    |

| 8. Resource Utilization             |    |

| References                          |    |

| Technical Support Assistance        |    |

| Revision History                    | 42 |

# **Figures**

| Figure 1.1. CSI-2 Virtual Channel Aggregation Block Diagram        | 7  |

|--------------------------------------------------------------------|----|

| Figure 1.2. Clocking Scheme Example                                |    |

| Figure 1.3. Microsoft Excel Calculator                             |    |

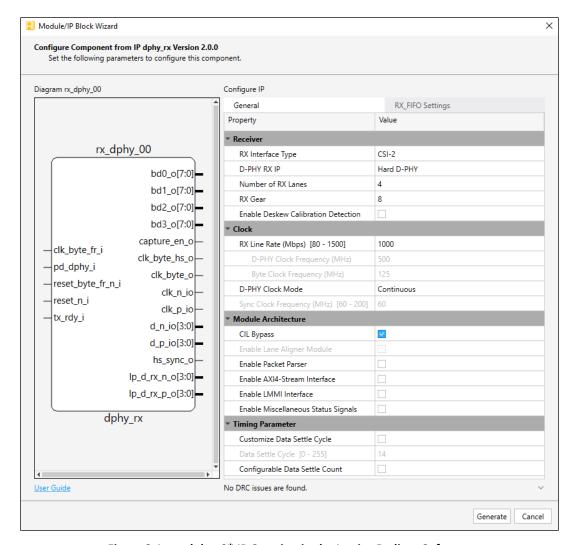

| Figure 3.1. rx dphy 0* IP Creation in the Lattice Radiant Software | 21 |

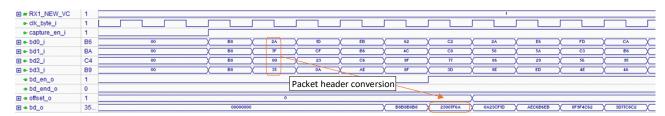

| Figure 3.2. Short Packet Detection and VC Replacement              | 23 |

| Figure 3.3. Long Packet Detection and VC Replacement               | 23 |

| Figure 3.4. End of Long Packet with Trailer Bytes                  | 23 |

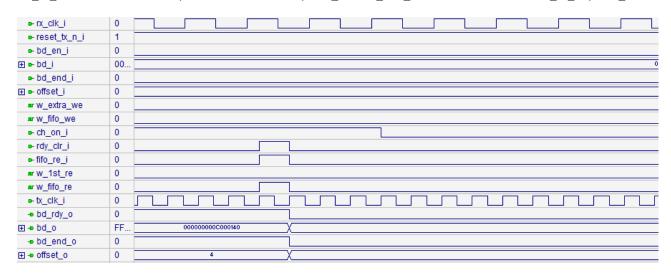

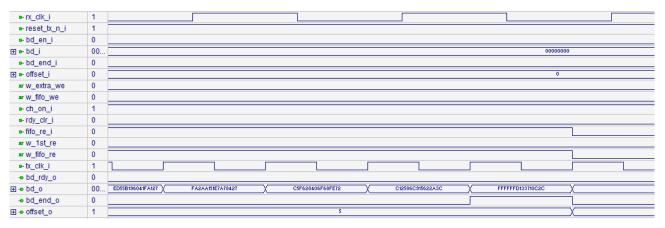

| Figure 3.5. Short Packet Write                                     | 24 |

| Figure 3.6. Beginning of Long Packet Write                         | 24 |

| Figure 3.7. End of Long Packet Write                               | 25 |

| Figure 3.8. Short Packet Read                                      | 25 |

| Figure 3.9. End of Long Packet Read                                | 25 |

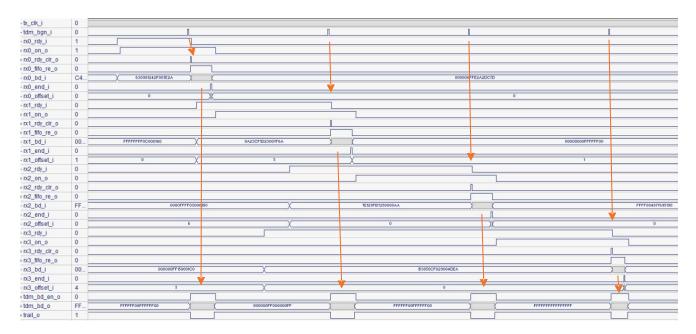

| Figure 3.10. Global Sequence of tdm_ctrl                           | 26 |

| Figure 3.11. Trailer Byte Appending                                | 26 |

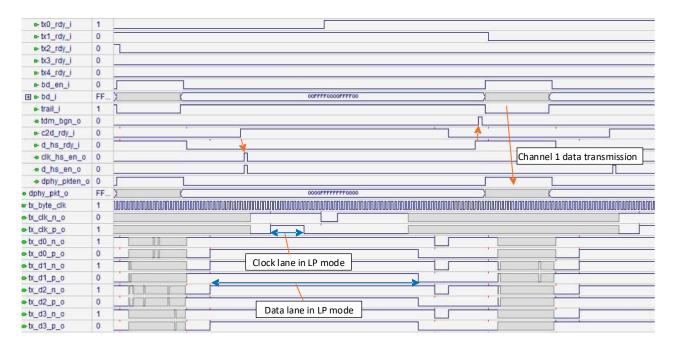

| Figure 3.12. Global Operation of tx_dphy_if                        | 27 |

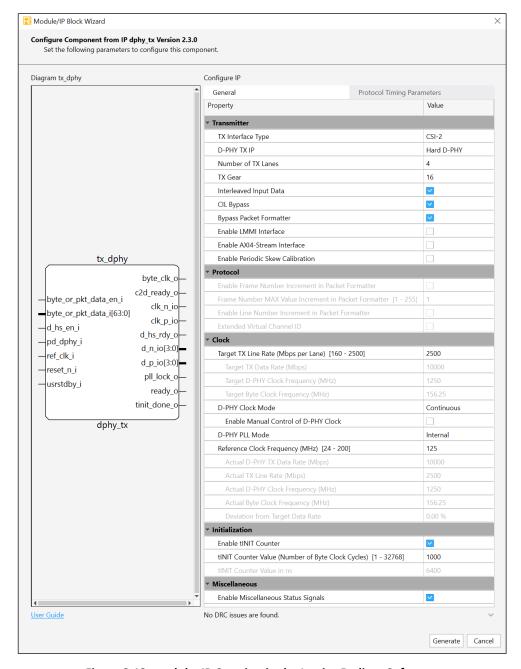

| Figure 3.13. tx_dphy IP Creation in the Lattice Radiant Software   | 28 |

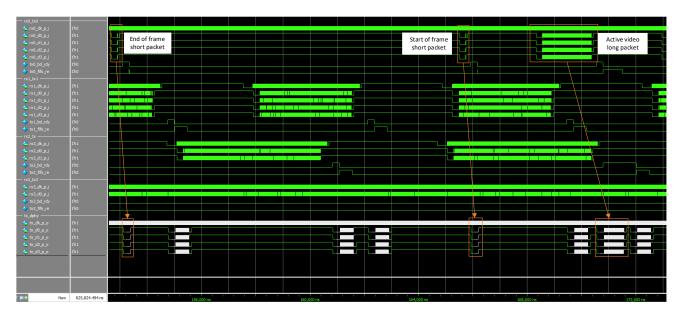

| Figure 5.1. Functional Simulation Example                          |    |

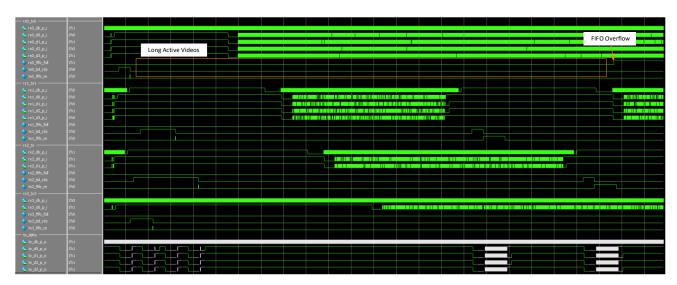

| Figure 5.2. FIFO Overflow                                          | 35 |

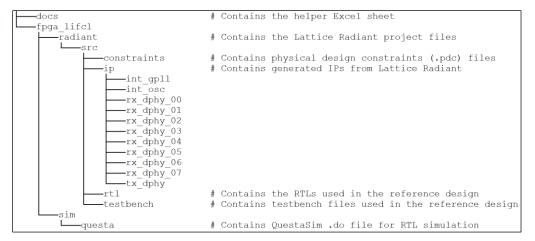

| Figure 7.1. Directory Structure                                    |    |

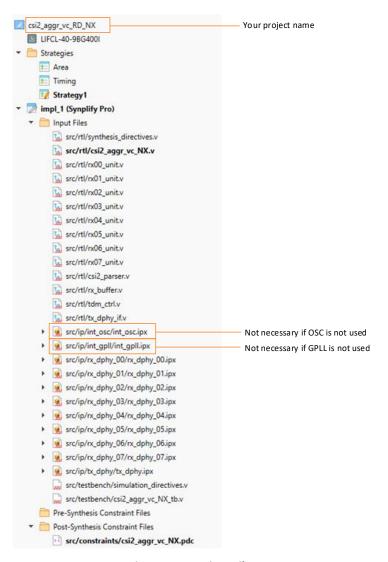

| Figure 7.2. Project Files                                          | 38 |

|                                                                    |    |

| Tables                                                             |    |

| Table 1.1. Supported Device and IP                                 | 6  |

| Table 2.1. Synthesis Directives                                    | 10 |

| Table 2.2. Simulation Directives                                   | 14 |

| Table 2.3. CSI-2 VC Aggregation Top-Level I/O                      | 17 |

| Table 8.1. Resource Utilization Examples                           | 39 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                          |

|---------|-------------------------------------|

| AP      | Application Processor               |

| CSI-2   | Camera Serial Interface 2           |

| DDR     | Double Data Rate                    |

| EBR     | Embedded Block RAM                  |

| ECC     | Error Correction Code               |

| HS      | High Speed                          |

| ID      | Identification Data                 |

| LP      | Low Power                           |

| LUT     | Look Up Table                       |

| MIPI    | Mobile Industry Processor Interface |

| PLL     | Phase Locked Loop                   |

| GPLL    | General Purpose PLL                 |

| RX      | Receiver                            |

| TDM     | Time Domain Multiplexing            |

| TX      | Transmitter                         |

| VC      | Virtual Channel                     |

## 1. Introduction

The majority of image sensors and application processors (AP) in the consumer market use the Mobile Industry Processor Interface (MIPI®) Camera Serial Interface 2 (CSI-2) as a video signal interface. In some cases, the AP has to take multiple image data for various applications without increasing the physical interface signals.

The Lattice Semiconductor MIPI CSI-2 virtual channel aggregation reference design with CrossLink™- NX devices offers up to eight-channel aggregation. A different virtual channel identification (ID) is assigned to each receiver (RX) channel. CrossLink-NX devices have two MIPI hard macro IPs which can be used as MIPI TX or RX module (D-PHY Hard IP). The RX module can also be realized by a soft macro utilizing general DDR modules (D-PHY Soft IP).

The reference design is available on the MIPI CSI-2 Virtual Channel Aggregation Reference Design web page.

## 1.1. Supported Device and IP

This reference design supports the following devices with IP versions.

Table 1.1. Supported Device and IP

| Device Family | Part Number | Compatible IP                      |

|---------------|-------------|------------------------------------|

| CrossLink-NX  | LIFCL-40    | D-PHY Receiver IP version 2.0.0    |

| Crosslink-NX  | LIFCL-17    | D-PHY Transmitter IP version 2.3.0 |

The IPs above are supported by the Lattice Radiant™ software version 2025.1 or later.

#### 1.2. Features List

- Two to eight independent RX channels can be aggregated.

- You can assign a unique virtual channel ID (0 to 15) to each RX channel.

- Each RX channel can have one, two, or four lanes.

- Number of TX lanes can be one, two, or four.

- Maximum RX bandwidth is 1.5 Gbps per lane.

- Maximum TX bandwidth is 2.5 Gbps per lane by using Hard D-PHY.

- Non-continuous clock mode on RX channels is possible as long as the continuous byte clock with the same frequency as the stoppable byte clock can be obtained internally or fed directly from the pin. Each RX clock can be independent and does not have to come from the same clock source.

## 1.3. Block Diagram

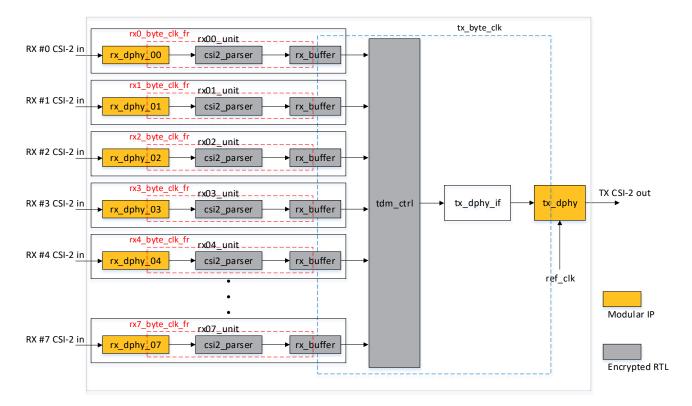

Figure 1.1 shows the block level diagram of the MIPI CSI-2 virtual channel aggregation reference design with eight RX channels.

As TX D-PHY PLL has an input clock frequency requirement of between 24 MHz and 200 MHz, another on-chip GPLL may have to be used to create an appropriate clock.

Figure 1.1. CSI-2 Virtual Channel Aggregation Block Diagram

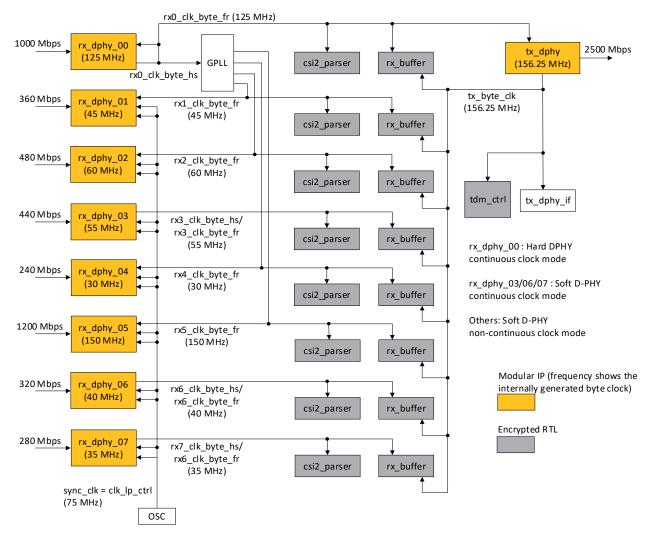

Figure 1.2. shows a clocking scheme example. In this example, RX channel #0 is in continuous clock mode and all other RX channels are in non-continuous clock mode. Sync clock (> 60 MHz) is required for RX Soft D-PHY IP and a clock to drive LP (Low Power) HS (High Speed) mode detection logic is required in non-continuous clock mode. The internal oscillator is used to generate ~75 MHz clock for these purposes. GPLL generates four continuous byte clocks for the four RX channels with non-continuous clock mode utilizing the continuous byte clock that comes from rx\_dphy\_00 as a reference clock.

Figure 1.2. Clocking Scheme Example

#### 1.4. RX and TX Permutations

This design allows all RX channels to be independent on number of lanes, bandwidth, and clock mode as long as the total RX bandwidth (plus some overhead) does not exceed the TX capability of 2.5 Gbps per lane. The amount of overhead varies by the number of RX channels, the horizontal blanking period of each RX channels, the active line period, etc., but less than 5% is enough for ordinary cases.

The Microsoft® Excel calculator (docs/vc\_aggr\_NX\_clock.xlsx) included in the reference design package is for you to get the byte clock and number of required Embedded Block RAM (EBR) for the design. This calculator is useful to estimate the required TX bandwidth and configure D-PHY RX and TX IP. A sample entry is shown in Figure 1.3. The setting in the calculator is matched the configuration shown in Figure 1.2.. By entering the values and modes indicated by the boxes, you can get the byte clock frequency and number of required EBR. Refer to RX FIFO section for details. Also, refer to the rx buffer section to select the value of actual RX Buffer Depth.

Note that some permutations may not be feasible by LIFCL-17 because of limited I/O and resources.

| nannel Aggregation with CrossLink-NX RD F | requeries | culculator |                  |                    |                   |                   |                     |                  |             |    |                                 |

|-------------------------------------------|-----------|------------|------------------|--------------------|-------------------|-------------------|---------------------|------------------|-------------|----|---------------------------------|

| Number of RX Channels                     | 8         | CH #0      | CH #1            | CH #2              | CH #3             | CH #4             | CH #5               | CH #6            | CH #7       |    |                                 |

| DPHY IP                                   |           | HARD       | SOFT             | SOFT               | SOFT              | SOFT              | SOFT                | SOFT             | SOFT        | 1  |                                 |

| RX Rate per lane (Mbps)                   |           | 1000       | 360              | 480                | 440               | 240               | 1200                | 320              | 280         |    |                                 |

| RX DPHY Clock Frequency (MHz)             |           | 500        | 180              | 240                | 220               | 120               | 600                 | 160              | 140         |    |                                 |

| RX DPHY Clock Period (ps)                 |           | 2000       | 5555.555556      | 4166.666667        | 4545.454545       | 8333.333333       | 1666.666667         | 6250             | 7142.857143 |    |                                 |

| Number of RX Lanes                        |           | 4          | 4                | 2                  | 1                 | 1                 | 1                   | 2                | 2           | 10 | total EBR for soft lane aligner |

| RX Gear (fixed to 8)                      |           | 8          | 8                | 8                  | 8                 | 8                 | 8                   | 8                | 8           |    |                                 |

| RX Data Type                              |           | RAW10      | RAW12            | RAW14              | RAW8              | RGB888            | YUV420_10           | YUV420_8         | YUV422_10   |    |                                 |

| Horizontal Resolution                     |           | 720        | 480              | 480                | 1920              | 240               | 480                 | 480              | 240         |    |                                 |

| Word Count                                |           | 900        | 720              | 840                | 1920              | 720               | 1200                | 960              | 600         |    |                                 |

| min. RX Buffer Depth                      |           | 112.5      | 90               | 105                | 240               | 90                | 150                 | 120              | 75          |    |                                 |

| actual RX Buffer Depth                    |           | 1024       | 1024             | 512                | 512               | 1024              | 1024                | 512              | 512         | 1  |                                 |

| actual EBR used for RX Buffer             |           | 4          | 4                | 2                  | 2                 | 4                 | 4                   | 2                | 2           | 24 | total EBR for RX Buffer         |

| RX Byte Clock Frequency                   |           | 125        | 45               | 60                 | 55                | 30                | 150                 | 40               | 35          |    |                                 |

| RX DPHY Clock Mode                        |           | continuous | non-continuous   | non-continuous     | continuous        | non-continuous    | non-continuous      | continuous       | continuous  |    |                                 |

| source of continuous byte clock           |           | self       | GPLL_op          | GPLL_os            | self              | GPLL_os2          | GPLL_os3            | self             | self        |    |                                 |

| Recommended RX FIFO type                  |           | SINGLE     | SINGLE           | SINGLE             | OFF               | SINGLE            | SINGLE              | OFF              | OFF         |    |                                 |

| Recommended RX FIFO depth                 |           | 8          | 16               | 16                 | NA                | 16                | 16                  | NA               | NA          |    |                                 |

| Recommended RX FIFO delay                 |           | 1          | 4                | 4                  | NA                | 4                 | 4                   | NA               | NA          |    |                                 |

| # of EBR used for RX FIFO                 |           | 1          | 1                | 1                  | 0                 | 1                 | 1                   | 0                | 0           | 5  | total EBR for RX FIFO           |

| Number of TX Lanes                        | 4         |            |                  |                    |                   |                   |                     |                  |             | 39 | Total EBR used (max. 84)        |

| TX Gear                                   | 16        |            |                  |                    |                   |                   |                     |                  |             |    |                                 |

| min. TX Rate per lane (Mbps)              | 2370      |            | Note: Only modif | fy the boxed cells |                   |                   |                     |                  |             |    |                                 |

| min. TX DPHY Clock Frequency (MHz)        | 1185      |            | Note: "source of | continuous byte    | clock" are inform | native and do not | affect clock freque | ency or EBR coun | it.         |    |                                 |

| min. TX Byte Clock Frequency (MHz)        | 148.125   |            |                  |                    |                   |                   |                     |                  |             |    |                                 |

| actual TX Rate per lane (Mbps)            | 2500      |            |                  |                    |                   |                   |                     |                  |             |    |                                 |

| actual TX DPHY Clock Frequency (MHz)      | 1250      |            |                  |                    |                   |                   |                     |                  |             |    |                                 |

| actual TX Byte Clock Frequency (MHz)      | 156.25    |            |                  |                    |                   |                   |                     |                  |             |    |                                 |

Figure 1.3. Microsoft Excel Calculator

## 2. Parameters and Port List

There are two directive files for this reference design:

- synthesis\_directives.v used for design compilation by the Lattice Radiant software and for simulation.

- *simulation\_directives.v* used for simulation.

You can modify these directives according to your own configuration. The settings in these files must match RX and TX D-PHY IP settings created by the Lattice Radiant software.

## 2.1. Synthesis Directives

Table 2.1 shows the synthesis directives that affect this reference design. These are used for both synthesis and simulation. As shown in Table 2.1 and Table 2.2, some parameter selections are restricted by other parameter settings.

**Table 2.1. Synthesis Directives**

| Category                 | Directive      | Remarks                                                                                                                            |

|--------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------|

| External reference clock | EXT_REF_CLK    | Enable this when the reference clock is fed from a pin.                                                                            |

|                          | NUM_RX_CH_2    |                                                                                                                                    |

|                          | NUM_RX_CH_3    |                                                                                                                                    |

|                          | NUM_RX_CH_4    |                                                                                                                                    |

| RX channel count         | NUM_RX_CH_5    | Number of RX channels aggregated. Only one of these four directives must be defined.                                               |

|                          | NUM_RX_CH_6    | directives must be defined.                                                                                                        |

|                          | NUM_RX_CH_7    |                                                                                                                                    |

|                          | NUM_RX_CH_8    |                                                                                                                                    |

|                          | NUM_RX0_LANE_1 |                                                                                                                                    |

|                          | NUM_RX0_LANE_2 | Number of lanes in RX channel 0. Only one of these three directives must be defined.                                               |

|                          | NUM_RX0_LANE_4 | inust be defined.                                                                                                                  |

|                          | NUM_RX1_LANE_1 |                                                                                                                                    |

|                          | NUM_RX1_LANE_2 | Number of lanes in RX channel 1. Only one of these three directives must be defined.                                               |

|                          | NUM_RX1_LANE_4 | inust be defined.                                                                                                                  |

|                          | NUM_RX2_LANE_1 |                                                                                                                                    |

|                          | NUM_RX2_LANE_2 | Number of lanes in RX channel 2. Only one of these three directives must be defined. Effective when RX channel count is 3 or more. |

|                          | NUM_RX2_LANE_4 | inust be defined. Effective when KX channel count is 3 of more.                                                                    |

|                          | NUM_RX3_LANE_1 | N                                                                                                                                  |

|                          | NUM_RX3_LANE_2 | Number of lanes in RX channel 3. Only one of these three directives must be defined. Effective when RX channel count is 4 or more. |

| RX channel lane count    | NUM_RX3_LANE_4 | must be defined. Effective when the channel count is 4 of more.                                                                    |

| KX Channel lane count    | NUM_RX4_LANE_1 |                                                                                                                                    |

|                          | NUM_RX4_LANE_2 | Number of lanes in RX channel 4. Only one of these three directives must be defined. Effective when RX channel count is 5 or more. |

|                          | NUM_RX4_LANE_4 | must be defined. Effective when KX channel count is 3 of more.                                                                     |

|                          | NUM_RX5_LANE_1 |                                                                                                                                    |

|                          | NUM_RX5_LANE_2 | Number of lanes in RX channel 4. Only one of these three directives must be defined. Effective when RX channel count is 6 or more. |

|                          | NUM_RX5_LANE_4 | must be defined. Effective when the channel count is 0 of more.                                                                    |

|                          | NUM_RX6_LANE_1 |                                                                                                                                    |

|                          | NUM_RX6_LANE_2 | Number of lanes in RX channel 4. Only one of these three directives must be defined. Effective when RX channel count is 7 or more. |

|                          | NUM_RX6_LANE_4 | must be defined. Effective when the channel count is 7 of more.                                                                    |

|                          | NUM_RX7_LANE_1 |                                                                                                                                    |

|                          | NUM_RX7_LANE_2 | Number of lanes in RX channel 4. Only one of these three directives must be defined. Effective when RX channel count is 8.         |

|                          | NUM_RX7_LANE_4 | mast se defined. Effective when the challier count is o.                                                                           |

|                          | RXO_GEAR_8     | Only one of these directives must be selected. Gear 16 can be used                                                                 |

| RX D-PHY Clock Gear      | RXO_GEAR_16    | for only 1- and 2-lane configurations of Hard D-PHY.                                                                               |

|                          | RX1_GEAR_8     | Only one of these directives must be selected. Gear 16 can be used                                                                 |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Category                         | Directive            | Remarks                                                                                                                          |

|----------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                  | RX1_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX2_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used                                                               |

|                                  | RX2_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX3_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used                                                               |

|                                  | RX3_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX4_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used                                                               |

|                                  | RX4_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX5_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used                                                               |

|                                  | RX5_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX6_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used                                                               |

|                                  | RX6_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX7_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used                                                               |

|                                  | RX7_GEAR_16          | for only 1- and 2-lane configurations for Hard D-PHY.                                                                            |

|                                  | RX0_DPHY_HARD        |                                                                                                                                  |

|                                  | RX1_DPHY_HARD        |                                                                                                                                  |

|                                  | RX2_DPHY_HARD        |                                                                                                                                  |

| RX Hard D-PHY channel            | RX3_DPHY_HARD        | Specify RX channel that uses Hard D-PHY. Only one of these eight directives must be defined. If none of these is defined, all RX |

| TOX TIATO D T TIT CHAINICI       | RX4_DPHY_HARD        | channels use Soft D-PHY.                                                                                                         |

|                                  | RX5_DPHY_HARD        |                                                                                                                                  |

|                                  | RX6_DPHY_HARD        |                                                                                                                                  |

|                                  | RX7_DPHY_HARD        |                                                                                                                                  |

|                                  | RX0_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 0. Only one of these two                                                                          |

|                                  | RXO_CLK_MODE_HS_LP   | directives must be defined.                                                                                                      |

|                                  | RX1_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 1. Only one of these two                                                                          |

|                                  | RX1_CLK_MODE_HS_LP   | directives must be defined.                                                                                                      |

|                                  | RX2_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 2. Only one of these two                                                                          |

|                                  | RX2_CLK_MODE_HS_LP   | directives must be defined.                                                                                                      |

|                                  | RX3_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 3. Only one of these two                                                                          |

| RX D-PHY Clock Mode <sup>1</sup> | RX3_CLK_MODE_HS_LP   | directives must be defined.                                                                                                      |

|                                  | RX4_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 4. Only one of these two                                                                          |

|                                  | RX4_CLK_MODE_HS_LP   | directives must be defined.                                                                                                      |

|                                  | RX5_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 5. Only one of these two                                                                          |

|                                  | RX5_CLK_MODE_HS_LP   | directives must be defined.                                                                                                      |

|                                  | RX6_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 6. Only one of these two directives must be defined.                                              |

|                                  | RX6_CLK_MODE_HS_LP   |                                                                                                                                  |

|                                  | RX7_CLK_MODE_HS_ONLY | RX D-PHY Clock mode on channel 7. Only one of these two directives must be defined.                                              |

|                                  | RX7_CLK_MODE_HS_LP   |                                                                                                                                  |

|                                  | RX0_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

|                                  | RX1_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

|                                  | RX2_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

| VC ID pass through <sup>2</sup>  | RX3_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

|                                  | RX4_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

|                                  | RX5_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

|                                  | RX6_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

|                                  | RX7_VC_PASS_THROUGH  | Enable when VC ID is passed through without change.                                                                              |

| Category                         | Directive                   | Remarks                                                                                                                          |

|----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                  | RX0_NEW_VC {value}          | Channel 0 Virtual Channel ID; 0 – 15                                                                                             |

|                                  | RX1_NEW_VC {value}          | Channel 1 Virtual Channel ID; 0 – 15                                                                                             |

|                                  | RX2_NEW_VC {value}          | Channel 2 Virtual Channel ID; 0 – 15                                                                                             |

| DV 1 1V0 1 2                     | RX3_NEW_VC {value}          | Channel 3 Virtual Channel ID; 0 – 15                                                                                             |

| RX channel VC value <sup>3</sup> | RX4_NEW_VC {value}          | Channel 4 Virtual Channel ID; 0 – 15                                                                                             |

|                                  | RX5_NEW_VC {value}          | Channel 5 Virtual Channel ID; 0 – 15                                                                                             |

|                                  | RX6_NEW_VC {value}          | Channel 6 Virtual Channel ID; 0 – 15                                                                                             |

|                                  | RX7_NEW_VC {value}          | Channel 7 Virtual Channel ID; 0 – 15                                                                                             |

|                                  | RX0_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

|                                  | RX1_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

|                                  | RX2_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

| RX Channel Frame                 | RX3_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

| Counter <sup>4</sup>             | RX4_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

|                                  | RX5_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

|                                  | RX6_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

|                                  | RX7_FRAME_COUNT             | Enable when Data Field of Frame Start/End Short Packet is replaced with the Frame Counter value.                                 |

|                                  | RX0_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.  Effective when RX0_FRAME_COUNT is defined. Must be 2 – 65535.   |

|                                  | RX1_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.  Effective when RX1_FRAME_COUNT is defined. Must be 2 – 65535.   |

|                                  | RX2_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.  Effective when RX2_FRAME_COUNT is defined. Must be 2 – 65535.   |

| Maximum value of the             | RX3_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.<br>Effective when RX3_FRAME_COUNT is defined. Must be 2 – 65535. |

| frame counter                    | RX4_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.<br>Effective when RX4_FRAME_COUNT is defined. Must be 2 – 65535. |

|                                  | RX5_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.<br>Effective when RX4_FRAME_COUNT is defined. Must be 2 – 65535. |

|                                  | RX6_FRAME_COUNT_MAX {value} | Frame counter value goes back to 1 after it reaches this value.<br>Effective when RX4_FRAME_COUNT is defined. Must be 2 – 65535. |

|                                  | RX7_FRAME_COUNT_MAX         | Frame counter value goes back to 1 after it reaches this value.                                                                  |

|                                  | {value}                     | Effective when RX4_FRAME_COUNT is defined. Must be 2 – 65535.                                                                    |

|                                  | RXO_BUFFER_DEPTH_*          | RX channel 0 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

|                                  | RX1_BUFFER_DEPTH_*          | RX channel 1 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

|                                  | RX2_BUFFER_DEPTH_*          | RX channel 2 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

| RX Buffer Depth <sup>5</sup>     | RX3_BUFFER_DEPTH_*          | RX channel 3 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

| ·                                | RX4_BUFFER_DEPTH_*          | RX channel 4 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

|                                  | RX5_BUFFER_DEPTH_*          | RX channel 5 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

|                                  | RX6_BUFFER_DEPTH_*          | RX channel 6 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

|                                  | RX7_BUFFER_DEPTH_*          | RX channel 7 FIFO Depth. * must be 512, 1024, 2048, or 4096.                                                                     |

| TX channel lane count            | NUM_TX_LANE_1 NUM_TX_LANE_2 | Number of lanes in TX channel. Only one of these three directives must be defined.                                               |

|                                  | NUM_TX_LANE_4               |                                                                                                                                  |

| Category             | Directive           | Remarks                                                       |

|----------------------|---------------------|---------------------------------------------------------------|

| TX D-PHY Clock Gear  | TX_GEAR_8           | TX D-PHY Clock Gear. Only one of these two directives must be |

| TA D-PHT Clock Geal  | TX_GEAR_16          | defined.                                                      |

| TX D-PHY Clock Mode  | TX_CLK_MODE_HS_ONLY | TX D-PHY Clock mode. Only one of these two directives must be |

| TX D-PHY Clock Wlode | TX_CLK_MODE_HS_LP   | defined.                                                      |

#### Notes:

- 1. HS\_LP mode means *non-continuous clock mode* and HS\_ONLY means *continuous clock mode*. HS\_LP mode works only if RX continuous byte clock (clk\_byte\_fr\_i) for corresponding RX channel can be generated internally or directly fed from I/O pin with the same frequency as the stoppable byte clock (clk\_byte\_hs\_o).

- 2. You cannot assign the same VC value on different RX channels when this is defined.

- 3. Incoming VC values on RX CSI-2 data are overwritten by these VC values when RX\*\_VC\_PASS\_THROUGH is not defined. Values 4 and above are only supported by CSI-2 version 2.0 and above. If the opponent device supports only CSI-2 version 1.1, VC values of 4-15 must not be used.

- 4. When this is defined, the Data Field is replaced with the 16-bit counter value which begins with 1 after power on/reset and goes back to 1 after it reaches RX\*\_FRAME\_COUNT\_MAX. The Data Field is passed through when this is not defined.

- 5. This value affects the necessary EBR used in the device. Number of necessary EBR per RX channel is (BUFFER\_DEPTH/512) × 2 (in case of NUM\_TX\_LANE\_4 and TX\_GEAR\_16), or (BUFFER\_DEPTH/512) × 1 (others).

- Total number of EBR used in this design must not exceed 84 for LIFCL-40 and 24 for LIFCL-17.

# 2.2. Simulation Directives

Table 2.2 shows the simulation directives for this reference design.

**Table 2.2. Simulation Directives**

| Table 2.2. Simulation Direct   | Directive                   | Remarks                                                                                                         |

|--------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

| Reference clock period         | REF_CLK_PERIOD {value}      | Reference clock period in ps                                                                                    |

| ,                              | RXO DPHY CLK PERIOD (value) | RX D-PHY clock period on Channel 0 in ps                                                                        |

|                                | RX1 DPHY CLK PERIOD (value) | RX D-PHY clock period on Channel 1 in ps                                                                        |

|                                | RX2_DPHY_CLK_PERIOD {value} | RX D-PHY clock period on Channel 2 in ps                                                                        |

|                                | RX3_DPHY_CLK_PERIOD {value} | RX D-PHY clock period on Channel 3 in ps                                                                        |

| RX D-PHY clock period          | RX4 DPHY CLK PERIOD (value) | RX D-PHY clock period on Channel 4 in ps                                                                        |

|                                | RX5_DPHY_CLK_PERIOD {value} | RX D-PHY clock period on Channel 5 in ps                                                                        |

|                                | RX6 DPHY CLK PERIOD {value} | RX D-PHY clock period on Channel 6 in ps                                                                        |

|                                | RX7_DPHY_CLK_PERIOD {value} | RX D-PHY clock period on Channel 7 in ps                                                                        |

|                                | RXO_FREQ_TGT {value}        | RX byte clock frequency on Channel 0 in MHz                                                                     |

|                                | RX1_FREQ_TGT {value}        | RX byte clock frequency on Channel 1 in MHz                                                                     |

|                                | RX2_FREQ_TGT {value}        | RX byte clock frequency on Channel 2 in MHz                                                                     |

|                                | RX3_FREQ_TGT {value}        | RX byte clock frequency on Channel 3 in MHz                                                                     |

| RX Byte clock frequency        |                             |                                                                                                                 |

|                                | RX4_FREQ_TGT {value}        | RX byte clock frequency on Channel 4 in MHz                                                                     |

|                                | RX5_FREQ_TGT {value}        | RX byte clock frequency on Channel 5 in MHz                                                                     |

|                                | RX6_FREQ_TGT {value}        | RX byte clock frequency on Channel 6 in MHz                                                                     |

| TV by to also by from your and | RX7_FREQ_TGT {value}        | RX byte clock frequency on Channel 7 in MHz                                                                     |

| TX byte clock frequency        | TX_FREQ_TGT {value}         | TX byte clock frequency in MHz                                                                                  |

| TX D-PHY clock period          | TX_DPHY_CLK_PERIOD {value}  | TX D-PHY clock period in ps                                                                                     |

| Frame Start Detection          | TX_WAIT_LESS_15MS           | Always enable this directive.                                                                                   |

|                                | VC_CH0 {value}              | VC value on incoming RX Channel 0; 0 – 15                                                                       |

|                                | VC_CH1 {value}              | VC value on incoming RX Channel 1; 0 – 15                                                                       |

|                                | VC_CH2 {value}              | VC value on incoming RX Channel 2; 0 – 15                                                                       |

| VC value on RX channel         | VC_CH3 {value}              | VC value on incoming RX Channel 3; 0 – 15                                                                       |

|                                | VC_CH4 {value}              | VC value on incoming RX Channel 4; 0 – 15                                                                       |

|                                | VC_CH5 {value}              | VC value on incoming RX Channel 5; 0 – 15                                                                       |

|                                | VC_CH6 {value}              | VC value on incoming RX Channel 6; 0 – 15                                                                       |

|                                | VC_CH7 {value}              | VC value on incoming RX Channel 7; 0 – 15                                                                       |

|                                | CH0_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

|                                | CH1_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

|                                | CH2_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

| Frame Number in Frame          | CH3_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

| Start/End Short Packets        | CH4_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

|                                | CH5_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

|                                | CH6_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

|                                | CH7_FNUM_EMBED              | Frame number is embedded in Data Field of Frame Start/End Short packet. The value "0" is filled when undefined. |

| Maximum value of Frame         | CH0_FNUM_MAX {value}        | The maximum value of the frame number; 2 - 65535                                                                |

| Number                         | CH1_FNUM_MAX {value}        | The maximum value of the frame number; 2 – 65535                                                                |

| Category                                 | Directive                  | Remarks                                                                                              |

|------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------|

|                                          | CH2_FNUM_MAX {value}       | The maximum value of the frame number; 2 – 65535                                                     |

|                                          | CH3_FNUM_MAX {value}       | The maximum value of the frame number; 2 – 65535                                                     |

|                                          | CH4_FNUM_MAX {value}       | The maximum value of the frame number; 2 - 65535                                                     |

|                                          | CH5_FNUM_MAX {value}       | The maximum value of the frame number; 2 - 65535                                                     |

|                                          | CH6_FNUM_MAX {value}       | The maximum value of the frame number; 2 - 65535                                                     |

|                                          | CH7_FNUM_MAX {value}       | The maximum value of the frame number; 2 - 65535                                                     |

|                                          | CH0_DELAY {value}          | Initial delay to activate RX Channel 0 in ps                                                         |

|                                          | CH1_DELAY {value}          | Initial delay to activate RX Channel 1 in ps                                                         |

|                                          | CH2_DELAY {value}          | Initial delay to activate RX Channel 2 in ps                                                         |

|                                          | CH3_DELAY {value}          | Initial delay to activate RX Channel 3 in ps                                                         |

| Initial delay on RX channel              | CH4_DELAY {value}          | Initial delay to activate RX Channel 4 in ps                                                         |

|                                          | CH5_DELAY {value}          | Initial delay to activate RX Channel 5 in ps                                                         |

|                                          | CH6_DELAY {value}          | Initial delay to activate RX Channel 6 in ps                                                         |

|                                          | CH7_DELAY {value}          | Initial delay to activate RX Channel 7 in ps                                                         |

|                                          | CHO DPHY LPS GAP {value}   | Gap time on RX Channel 0 in ps                                                                       |

|                                          | CH1_DPHY_LPS_GAP {value}   | Gap time on RX Channel 1 in ps                                                                       |

|                                          | CH2 DPHY LPS GAP {value}   | Gap time on RX Channel 2 in ps                                                                       |

| Gap (LP) time between                    | CH3_DPHY_LPS_GAP {value}   | Gap time on RX Channel 3 in ps                                                                       |

| active lines on RX Channel               | CH4 DPHY LPS GAP {value}   | Gap time on RX Channel 4 in ps                                                                       |

|                                          | CH5 DPHY LPS GAP {value}   | Gap time on RX Channel 5 in ps                                                                       |

|                                          | CH6 DPHY LPS GAP {value}   | Gap time on RX Channel 6 in ps                                                                       |

|                                          | CH7_DPHY_LPS_GAP {value}   | Gap time on RX Channel 7 in ps                                                                       |

|                                          | CHO DPHY FRAME GAP (value) | Gap time on RX Channel 0 in ps                                                                       |

|                                          | CH1 DPHY FRAME GAP {value} | Gap time on RX Channel 1 in ps                                                                       |

|                                          | CH2 DPHY FRAME GAP {value} | Gap time on RX Channel 2 in ps                                                                       |

| Gap (LP) time between                    | CH3_DPHY_FRAME_GAP {value} | Gap time on RX Channel 3 in ps                                                                       |

| Frame End and Frame Start on RX Channel  | CH4_DPHY_FRAME_GAP {value} | Gap time on RX Channel 4 in ps                                                                       |

| Oli KA Cildililei                        | CH5 DPHY FRAME GAP {value} | Gap time on RX Channel 4 in ps                                                                       |

|                                          | CH6 DPHY FRAME GAP {value} | Gap time on RX Channel 4 in ps                                                                       |

|                                          | CH7_DPHY_FRAME_GAP {value} | Gap time on RX Channel 4 in ps                                                                       |

|                                          | CH0_NUM_FRAMES {value}     | Number of frames to feed                                                                             |

|                                          | CHO NUM LINES (value)      | Number of active lines per frame                                                                     |

| Video data configuration on RX Channel 0 | CHO NUM PIXELS (value)     | Number of pixels per line                                                                            |

| AX CHAINELO                              | CH0_DT_*                   | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                          | CH1_NUM_PIXELS {value}     | Number of pixels per line                                                                            |

| V. 1                                     | CH1_NUM_LINES {value}      | Number of active lines per frame                                                                     |

| Video data configuration on RX Channel 1 | CH1_NUM_PIXELS {value}     | Number of pixels per line                                                                            |

| KX Channel 1                             | CH1_DT_*                   | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                          | CH2_NUM_FRAMES {value}     | Number of frames to feed                                                                             |

| Middle data                              | CH2_NUM_LINES {value}      | Number of active lines per frame                                                                     |

| Video data configuration on RX Channel 2 | CH2_NUM_PIXELS {value}     | Number of pixels per line                                                                            |

|                                          | CH2_DT_*                   | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                          | CH3_NUM_FRAMES {value}     | Number of frames to feed                                                                             |

| Video data configuration on              | CH3_NUM_LINES {value}      | Number of active lines per frame                                                                     |

| RX Channel 3                             | CH3_NUM_PIXELS {value}     | Number of pixels per line                                                                            |

| Category                                    | Directive              | Remarks                                                                                              |

|---------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------|

|                                             | CH3_DT_*               | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                             | CH4_NUM_FRAMES {value} | Number of frames to feed                                                                             |

| Video dete configuration on                 | CH4_NUM_LINES {value}  | Number of active lines per frame                                                                     |

| Video data configuration on<br>RX Channel 4 | CH4_NUM_PIXELS {value} | Number of pixels per line                                                                            |

| Tot Chamier 1                               | CH4_DT_*               | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                             | CH5_NUM_FRAMES {value} | Number of frames to feed                                                                             |

| Video dete configuration on                 | CH5_NUM_LINES {value}  | Number of active lines per frame                                                                     |

| Video data configuration on RX Channel 5    | CH5_NUM_PIXELS {value} | Number of pixels per line                                                                            |

| NA CHAIIIEI 3                               | CH5_DT_*               | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                             | CH6_NUM_FRAMES {value} | Number of frames to feed                                                                             |

| Video dete configuration on                 | CH6_NUM_LINES {value}  | Number of active lines per frame                                                                     |

| Video data configuration on RX Channel 6    | CH6_NUM_PIXELS {value} | Number of pixels per line                                                                            |

| TXX CHairier 0                              | CH6_DT_*               | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

|                                             | CH7_NUM_FRAMES {value} | Number of frames to feed                                                                             |

| Video dete configuration on                 | CH7_NUM_LINES {value}  | Number of active lines per frame                                                                     |

| Video data configuration on RX Channel 7    | CH7_NUM_PIXELS {value} | Number of pixels per line                                                                            |

|                                             | CH7_DT_*               | Data Type; * must be RAW8, RAW10, RAW12, RAW14, RGB888, YUV420_10, YUV420_8, YUV422_10, or YUV422_8. |

| Internal signal monitoring                  | MISC_ON                | Enables internal signal monitored by the testbench. Always enable this directive.                    |

# 2.3. Top-Level I/O

Table 2.3 shows the top-level I/O of this reference design. Actual I/O depend on your channel and lane configurations. All necessary I/O ports are automatically declared by compiler directives.

Table 2.3. CSI-2 VC Aggregation Top-Level I/O

| Port Name        | Direction | Description                                                                                 |  |  |  |

|------------------|-----------|---------------------------------------------------------------------------------------------|--|--|--|

| Clocks and Res   | ets       |                                                                                             |  |  |  |

| ref_clk_i        | I         | Input reference clock. This port is declared only when EXT_REF_CLK is defined in            |  |  |  |

| (optional)       |           | synthesis_directives.v.                                                                     |  |  |  |

| reset_n_i        | I         | Asynchronous active low system reset                                                        |  |  |  |

| CSI-2 RX Interfa | ace       |                                                                                             |  |  |  |

| rx0_clk_p_i      | I         | Positive differential RX Ch0 D-PHY input clock                                              |  |  |  |

| rx0_clk_n_i      | I         | Negative differential RX Ch0 D-PHY input clock                                              |  |  |  |

| rx0_d0_p_i       | I         | Positive differential RX Ch0 D-PHY input data 0                                             |  |  |  |

| rx0_d0_n_i       | I         | Negative differential RX Ch0 D-PHY input data 0                                             |  |  |  |

| rx0_d1_p_i       | I         | Positive differential RX Ch0 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx0_d1_n_i       | I         | Negative differential RX Ch0 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx0_d2_p_i       | 1         | Positive differential RX Ch0 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx0_d2_n_i       | 1         | Negative differential RX Ch0 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx0_d3_p_i       | 1         | Positive differential RX Ch0 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |  |

| rx0_d3_n_i       | 1         | Negative differential RX Ch0 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |  |

| rx1_clk_p_i      | I         | Positive differential RX Ch1 D-PHY input clock                                              |  |  |  |

| rx1_clk_n_i      | I         | Negative differential RX Ch1 D-PHY input clock                                              |  |  |  |

| rx1_d0_p_i       | I         | Positive differential RX Ch1 D-PHY input data 0                                             |  |  |  |

| rx1_d0_n_i       | I         | Negative differential RX Ch1 D-PHY input data 0                                             |  |  |  |

| rx1_d1_p_i       | I         | Positive differential RX Ch1 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx1_d1_n_i       | I         | Negative differential RX Ch1 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx1_d2_p_i       | I         | Positive differential RX Ch1 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx1_d2_n_i       | I         | Negative differential RX Ch1 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx1_d3_p_i       | I         | Positive differential RX Ch1 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |  |

| rx1_d3_n_i       | I         | Negative differential RX Ch1 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |  |

| rx2_clk_p_i      | I         | Positive differential RX Ch2 D-PHY input clock                                              |  |  |  |

| rx2_clk_n_i      | I         | Negative differential RX Ch2 D-PHY input clock                                              |  |  |  |

| rx2_d0_p_i       | I         | Positive differential RX Ch2 D-PHY input data 0                                             |  |  |  |

| rx2_d0_n_i       | I         | Negative differential RX Ch2 D-PHY input data 0                                             |  |  |  |

| rx2_d1_p_i       | I         | Positive differential RX Ch2 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx2_d1_n_i       | Į.        | Negative differential RX Ch2 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx2_d2_p_i       | I         | Positive differential RX Ch2 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx2_d2_n_i       | I         | Negative differential RX Ch2 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx2_d3_p_i       | 1         | Positive differential RX Ch2 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |  |

| rx2_d3_n_i       | I         | Negative differential RX Ch2 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |  |

| rx3_clk_p_i      | I         | Positive differential RX Ch3 D-PHY input clock                                              |  |  |  |

| rx3_clk_n_i      | ı         | Negative differential RX Ch3 D-PHY input clock                                              |  |  |  |

| rx3_d0_p_i       | ı         | Positive differential RX Ch3 D-PHY input data 0                                             |  |  |  |

| rx3_d0_n_i       | 1         | Negative differential RX Ch3 D-PHY input data 0                                             |  |  |  |

| rx3_d1_p_i       | ı         | Positive differential RX Ch3 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx3_d1_n_i       | ı         | Negative differential RX Ch3 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |  |

| rx3_d2_p_i       | I         | Positive differential RX Ch3 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |  |

| rx3_d2_n_i       | i         | Negative differential RX Ch3 D-PHY input data 2 (in case of 4 lane configuration)           |  |  |  |

| Port Name                | Direction                                    | Description                                                                                 |  |

|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------|--|

| rx3_d3_p_i               | I                                            | Positive differential RX Ch3 D-PHY input data 3 (in case of 4 lane configuration)           |  |

| rx3_d3_n_i               | I                                            | Negative differential RX Ch3 D-PHY input data 3 (in case of 4 lane configuration)           |  |

| rx4_clk_p_i              | I                                            | Positive differential RX Ch4 D-PHY input clock                                              |  |

| rx4_clk_n_i              | ı                                            | Negative differential RX Ch4 D-PHY input clock                                              |  |

| rx4_d0_p_i               | ı                                            | Positive differential RX Ch4 D-PHY input data 0                                             |  |

| rx4_d0_n_i               | ı                                            | Negative differential RX Ch4 D-PHY input data 0                                             |  |

| rx4_d1_p_i               | ı                                            | Positive differential RX Ch4 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |

| rx4_d1_n_i               | ı                                            | Negative differential RX Ch4 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |

| rx4_d2_p_i               | ı                                            | Positive differential RX Ch4 D-PHY input data 2 (in case of 4-lane configuration)           |  |

| rx4_d2_n_i               | ı                                            | Negative differential RX Ch4 D-PHY input data 2 (in case of 4-lane configuration)           |  |

| rx4_d3_p_i               | 1                                            | Positive differential RX Ch4 D-PHY input data 3 (in case of 4-lane configuration)           |  |

| rx4_d3_n_i               | i                                            | Negative differential RX Ch4 D-PHY input data 3 (in case of 4-lane configuration)           |  |

| rx5_clk_p_i              | i                                            | Positive differential RX Ch5 D-PHY input clock                                              |  |

| rx5_clk_n_i              | i                                            | Negative differential RX Ch5 D-PHY input clock                                              |  |

| rx5_d0_p_i               | i                                            | Positive differential RX Ch5 D-PHY input data 0                                             |  |

| rx5_d0_p_i               | i                                            | Negative differential RX Ch5 D-PHY input data 0                                             |  |

| rx5_d1_p_i               | i                                            | Positive differential RX Ch5 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |

| rx5_d1_p_i               | i                                            | Negative differential RX Ch5 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |

| rx5_d2_p_i               | i                                            | Positive differential RX Ch5 D-PHY input data 2 (in case of 4-lane configuration)           |  |

| rx5_d2_p_i<br>rx5_d2_n_i | <u> </u>                                     | Negative differential RX Ch5 D-PHY input data 2 (in case of 4-lane configuration)           |  |

| rx5_d3_p_i               | <u>'</u>                                     | Positive differential RX Ch5 D-PHY input data 2 (in case of 4-lane configuration)           |  |

|                          |                                              | Negative differential RX Ch5 D-PHY input data 3 (in case of 4-lane configuration)           |  |

| rx5_d3_n_i               |                                              |                                                                                             |  |

| rx6_clk_p_i              |                                              | Positive differential RX Ch6 D-PHY input clock                                              |  |

| rx6_clk_n_i              |                                              | Negative differential RX Ch6 D-PHY input clock                                              |  |

| rx6_d0_p_i               | !                                            | Positive differential RX Ch6 D-PHY input data 0                                             |  |

| rx6_d0_n_i               |                                              | Negative differential RX Ch6 D-PHY input data 0                                             |  |

| rx6_d1_p_i               |                                              | Positive differential RX Ch6 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |

| rx6_d1_n_i               | <u> </u>                                     | Negative differential RX Ch6 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |

| rx6_d2_p_i               |                                              | Positive differential RX Ch6 D-PHY input data 2 (in case of 4-lane configuration)           |  |

| rx6_d2_n_i               |                                              | Negative differential RX Ch6 D-PHY input data 2 (in case of 4-lane configuration)           |  |

| rx6_d3_p_i               | <u>                                     </u> | Positive differential RX Ch6 D-PHY input data 3 (in case of 4-lane configuration)           |  |

| rx6_d3_n_i               | <u> </u>                                     | Negative differential RX Ch6 D-PHY input data 3 (in case of 4-lane configuration)           |  |

| rx7_clk_p_i              |                                              | Positive differential RX Ch7 D-PHY input clock                                              |  |

| rx7_clk_n_i              | <u> </u>                                     | Negative differential RX Ch7 D-PHY input clock                                              |  |

| rx7_d0_p_i               | <u> </u>                                     | Positive differential RX Ch7 D-PHY input data 0                                             |  |

| rx7_d0_n_i               | 1                                            | Negative differential RX Ch7 D-PHY input data 0                                             |  |

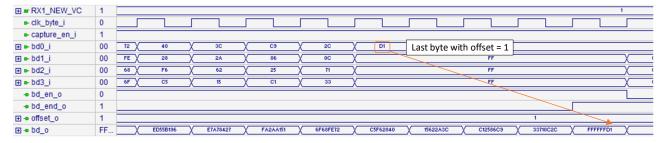

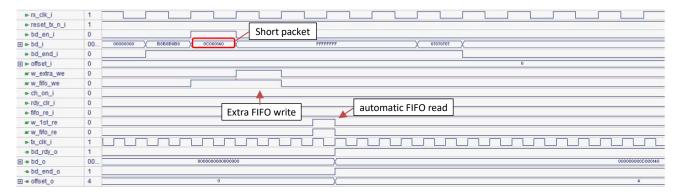

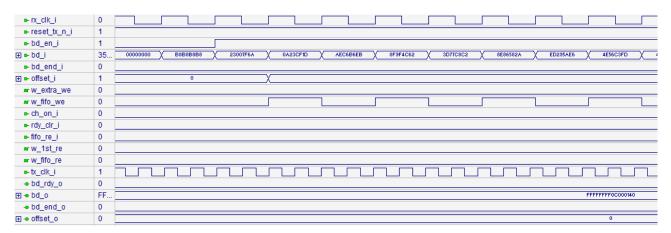

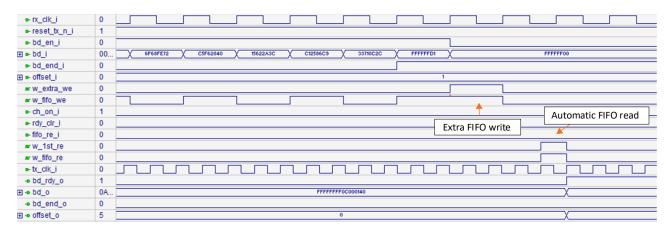

| rx7_d1_p_i               |                                              | Positive differential RX Ch7 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |