# **DDR3 SDRAM Controller IP Core for Nexus Devices**

IP Version: v2.3.0

## **User Guide**

FPGA-IPUG-02086-2.2

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents | S                                  | 3  |

|----------|------------------------------------|----|

| Abbrevia | ations in This Document            |    |

| 1. Intr  | roduction                          | 8  |

| 1.1.     | Quick Facts                        | 8  |

| 1.2.     | IP Support Summary                 | 8  |

| 1.3.     | Features                           | 9  |

| 1.4.     | Licensing and Ordering Information | 10 |

| 1.5.     | Hardware Support                   | 10 |

| 1.6.     | Minimum Device Requirements        |    |

| 1.7.     | Naming Conventions                 | 11 |

| 1.7.     | .1. Nomenclature                   |    |

| 1.7.     | .2. Signal Names                   |    |

| 1.8.     | Limitations                        |    |

| 2. Fun   | nctional Description               |    |

| 2.1.     | IP Architecture                    |    |

| 2.1.     | .1. AXI4/APB Bridge Interface      |    |

| 2.1.     |                                    |    |

| 2.1.     | •                                  |    |

| 2.2.     | Clocking and Reset                 |    |

| 2.3.     | User Interfaces                    |    |

| 2.3.     |                                    |    |

| 2.3.     |                                    |    |

| 2.4.     | DDR3 Calibration                   |    |

| 2.4.     |                                    |    |

| 2.4.     | • •                                |    |

| 2.5.     | DDR3 Operation Description         |    |

| 2.5.     | ·                                  |    |

| 2.5.     |                                    |    |

| 2.5.     |                                    |    |

| 2.5      |                                    |    |

| 2.5      |                                    |    |

| 2.5      |                                    |    |

| 2.5.     |                                    |    |

| 2.5      |                                    |    |

| 2.5.     |                                    |    |

|          | Parameter Description              |    |

| 3.1.     | ·                                  |    |

| 3.2.     | Memory Device Setting              |    |

| 3.3.     | Memory Device Timing               |    |

| 3.4.     | Example Design                     |    |

|          | nal Description                    |    |

| 4.1.     | Clock and Reset                    |    |

| 4.2.     | APB Config Interface               |    |

| 4.3.     | AXI4 Data Interface                |    |

| 4.4.     | Native Interface                   |    |

| 4.5.     | DDR3 Memory Interface              |    |

|          | gister Description                 |    |

| _        | R3 SDRAM Controller Example Design |    |

| 6.1.     | Overview                           |    |

| 6.2.     | Synthesis Example Design           |    |

| 6.3.     | Simulation Example Design          |    |

|          | signing and Simulating the IP      |    |

| ,. Des   | Signing and Sindlating the II      | 47 |

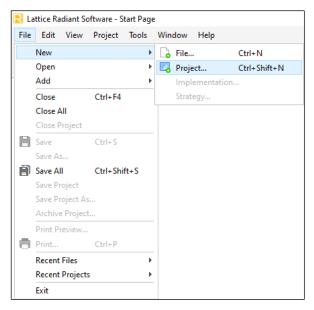

| 7.1. Generating the IP                   | 47 |

|------------------------------------------|----|

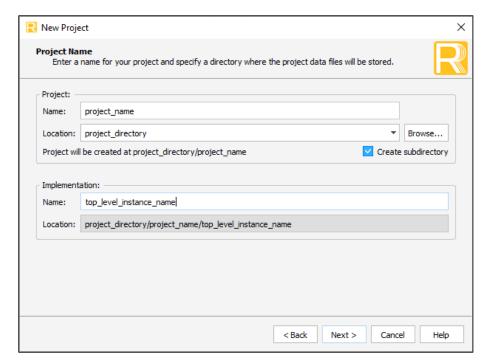

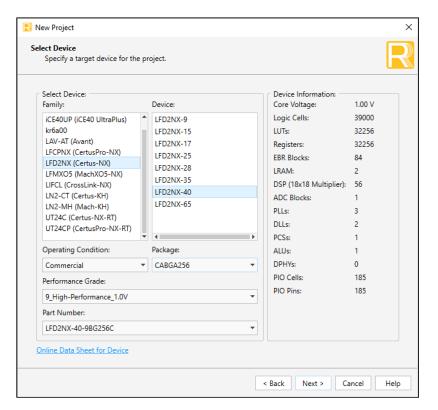

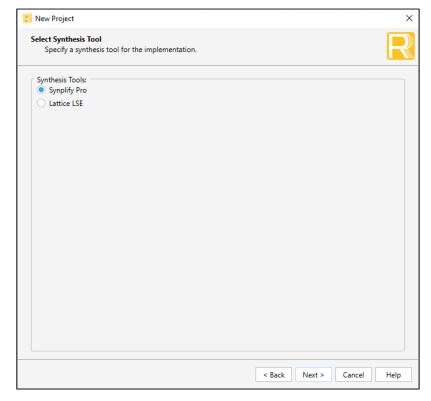

| 7.1.1. Creating a Radiant Project        |    |

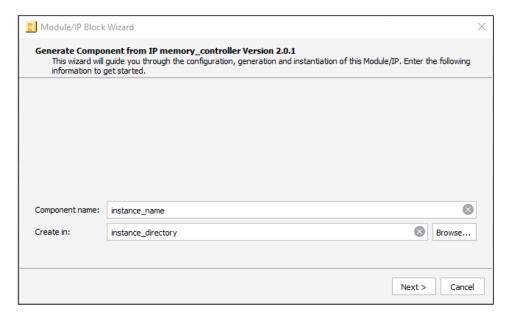

| 7.1.2. Configuring and Generating the IP | 49 |

| 7.2. Design Implementation               | 52 |

| 7.2.1. Pin Placement                     | 52 |

| 7.2.2. Constraints                       |    |

| 7.3. Example Design Hardware Evaluation  | 54 |

| 7.3.1. Preparing the Bitstream           | 55 |

| 7.3.2. Running on Hardware               | 56 |

| 7.4. Example Design Simulation           | 60 |

| 8. Debugging                             | 64 |

| 8.1. Debug with the Example Design       | 64 |

| 8.2. Debug with Reveal Analyzer          |    |

| 8.2.1. Write Leveling                    | 66 |

| 8.2.2. Read Training (DQS Gate)          | 67 |

| 8.2.3. Write Training                    | 67 |

| 8.2.4. Read Data Eye Training            | 68 |

| Appendix A. Resource Utilization         | 69 |

| Appendix B. Known Issue                  | 72 |

| References                               | 72 |

| Technical Support Assistance             | 73 |

| Revision History                         |    |

## Figures

| Figure 2.1. Memory Controller IP Core Functional Diagram       | 12 |

|----------------------------------------------------------------|----|

| Figure 2.2. External PLL Reset Steps                           | 14 |

| Figure 2.3. Before Write Training                              | 18 |

| Figure 2.4. After Write Training                               | 19 |

| Figure 2.5. Result                                             | 19 |

| Figure 2.6. Before Read Data Eye Training                      | 19 |

| Figure 2.7. After Read Data Eye Training                       | 20 |

| Figure 2.8. Result                                             | 20 |

| Figure 2.9. Timing of Command and Address                      | 23 |

| Figure 2.10. Local-to-Memory Address Mapping for Memory Access | 23 |

| Figure 2.11. Mapped Address for the Example                    | 24 |

| Figure 2.12. One-Clock vs. Two-Clock Write Data Delay          | 25 |

| Figure 2.13. User-Side Read Operation                          |    |

| Figure 2.14. User-to-Memory Address Mapping for MR Programming | 27 |

| Figure 6.1. Memory Controller IP Core Functional Diagram       |    |

| Figure 7.1. Creating a New Radiant Project                     | 47 |

| Figure 7.2. New Project Settings                               | 48 |

| Figure 7.3. Project Device Settings                            | 48 |

| Figure 7.4. Project Synthesis Tool Selection                   | 49 |

| Figure 7.5. IP Instance Settings                               | 50 |

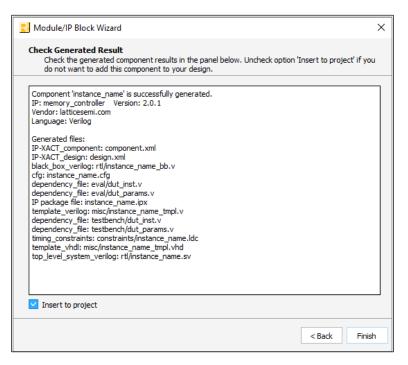

| Figure 7.6. IP Generation Result                               |    |

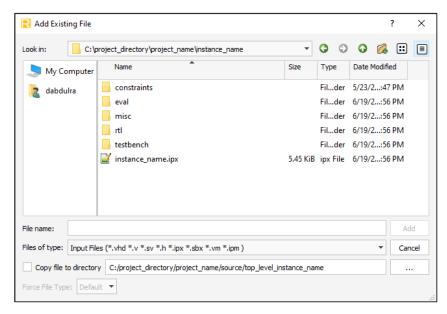

| Figure 7.7. Add Existing File Dialog Box                       |    |

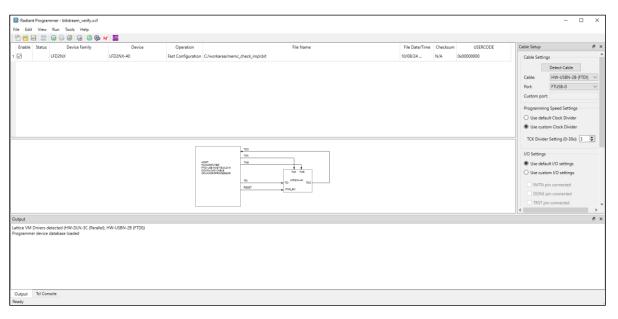

| Figure 7.8. Radiant Programmer                                 |    |

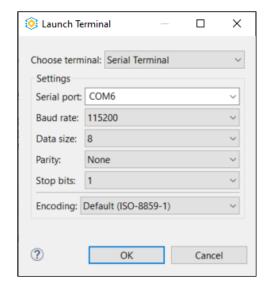

| Figure 7.9. Serial Terminal Settings                           |    |

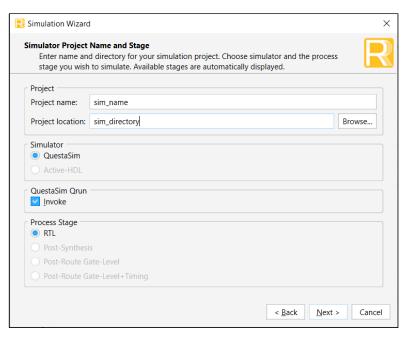

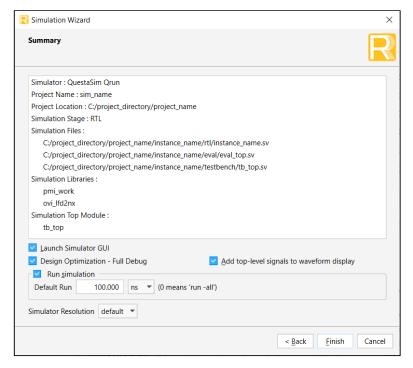

| Figure 7.10. Simulation Wizard                                 |    |

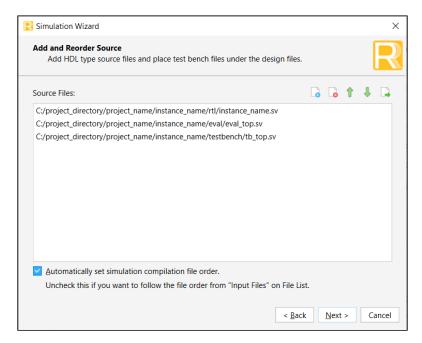

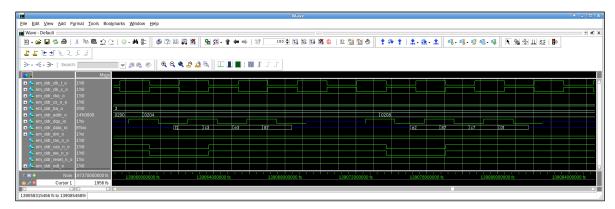

| Figure 7.11. Adding and Reordering Simulation Source Files     |    |

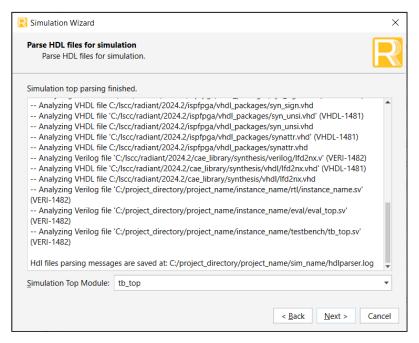

| Figure 7.12. Parsing Simulation HDL Files                      |    |

| Figure 7.13. Simulation Summary                                |    |

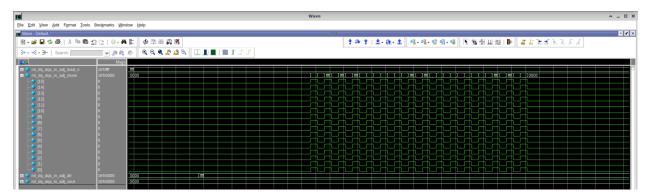

| Figure 7.14. Simulation Result Waveform                        |    |

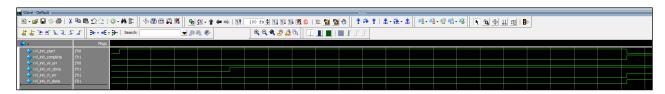

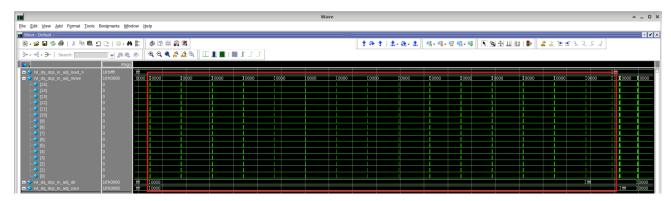

| Figure 8.1. DDR3 Training Passes                               |    |

| Figure 8.2. DDR3 Read Training Failure                         |    |

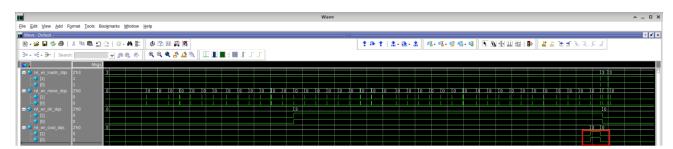

| Figure 8.3. DDR3 Write Leveling output for DQS0                |    |

| Figure 8.4. DDR3 Read Training (DQS Gate)                      |    |

| Figure 8.5. DDR3 Write Training                                |    |

| Figure 8.6. DDR3 DQ-DQS Course Adjustment                      |    |

| Figure 8.7. DDR3 Read Data Eye Training                        | 68 |

## **Tables**

| Table 1.1. Quick Facts                                             | 8  |

|--------------------------------------------------------------------|----|

| Table 1.2. DDR3 SDRAM Controller IP Support Readiness              | 8  |

| Table 1.3. Features Overview                                       |    |

| Table 1.4. Minimum Device Requirements                             | 11 |

| Table 2.1. Supported AXI4 Transactions                             | 15 |

| Table 2.2. Address Mapping                                         | 16 |

| Table 2.3. AXI4 to Memory Address Mapping Example                  | 16 |

| Table 2.4. Native Interface Functional Groups                      | 21 |

| Table 2.5. Address Mapping Example                                 | 24 |

| Table 2.6. Defined User Commands                                   | 24 |

| Table 2.7. Transmit MAC Statistics Vector                          | 27 |

| Table 2.8. Initialization Default Values for Mode Register Setting | 27 |

| Table 3.1. Device Information Attributes                           | 29 |

| Table 3.2. Clock Settings Attributes                               |    |

| Table 3.3. Memory Configuration Attributes                         | 30 |

| Table 3.4. Local Interface Attributes                              | 30 |

| Table 3.5. Additional Configuration Group Attributes               | 30 |

| Table 3.6. General Definitions                                     |    |

| Table 3.7. Address Attributes                                      |    |

| Table 3.8. Auto Refresh Control Attributes                         |    |

| Table 3.9. Mode Register Initial Setting Attributes                |    |

| Table 3.10. Memory Device Setting                                  |    |

| Table 3.11. Command and Address Timing Attributes                  |    |

| Table 3.12. Calibration Timing Attributes                          |    |

| Table 3.13. Refresh, Reset and Power Down Timing Attributes        |    |

| Table 3.14. Write Leveling and ODT Timing Attributes               |    |

| Table 3.15. Memory Device Timing Definitions                       |    |

| Table 3.16 Example Design                                          |    |

| Table 4.1. Clock and Reset Port Definitions                        |    |

| Table 4.2. APB Interface Port Definitions                          |    |

| Table 4.3. AXI4 Interface Port Definitions                         |    |

| Table 4.4. Native Interface Port Definitions                       |    |

| Table 4.5. DDR3 Interface Port Definitions                         |    |

| Table 5.1. APB Interface Register Map                              |    |

| Table 6.1. Supported Example Design Configurations                 |    |

| Table 7.1. Memory Controller Attribute Guidelines                  |    |

| Table 7.2. Generated File List                                     |    |

| Table 7.3. Project Constraints                                     |    |

| Table 7.4. Contents of eval/traffic_gen                            |    |

| Table 8.1. Reveal Analyzer Signal Definitions                      |    |

| Table A.1 Resource Utilization for IP Core v2.2.0                  |    |

| Table A.2. Resource Utilization for IP Core v2.2.0                 | 70 |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                |

|--------------|-------------------------------------------|

| SDRAM        | Synchronous Dynamic Random Access Memory  |

| APB          | Advanced Peripheral Bus                   |

| BL           | Burst Length                              |

| CA           | Column Address                            |

| CS           | Chip Select                               |

| DDR3         | Double Data Rate Generation 3             |

| DFI          | DDR PHY                                   |

| DM           | Data Mask                                 |

| DQ           | Data                                      |

| DQS          | Data Strobe                               |

| ECC          | Error Correction Code                     |

| ECLK         | Edge Clock                                |

| FPGA         | Field Programmable Gate Array             |

| I/F          | Interface                                 |

| JEDEC        | Joint Electron Device Engineering Council |

| MC           | Memory Controller                         |

| MR           | Mode Register                             |

| MRS          | Mode Register Set                         |

| ODT          | On-Die Termination                        |

| PRBS         | Pseudorandom Binary Sequence              |

| PVT          | Process, Voltage, and Temperature         |

| RTL          | Register Transfer Level                   |

| SCLK         | System Clock                              |

| SDR          | Single Data Rate                          |

| SDRAM        | Synchronous Dynamic Random Access Memory  |

| SSTL         | Stub-Series Terminated Logic              |

| TCL          | Tool Command Language                     |

| VREF         | Voltage Reference                         |

## 1. Introduction

The Lattice Double Data Rate Synchronous Dynamic Random Access Memory (DDR3 SDRAM) Controller IP Core is a general-purpose memory controller that interfaces with industry standard DDR3 memory devices compliant with JESD79-3C, DDR3 SDRAM Standard. This IP provides a generic command interface to user applications.

DDR3 SDRAM Controller IP reduces the effort required to integrate the DDR3 memory controller with the user application design and minimizes the need to directly deal with the DDR3 memory interface.

#### 1.1. Quick Facts

The following table presents a summary of the DDR3 Memory Controller for Nexus Devices.

**Table 1.1. Quick Facts**

| IP Requirements      | Supported Devices                   | CrossLink™-NX (LIFCL-40), Certus™-NX (LFD2NX-15, LFD2NX-25, LFD2NX-28, LFD2NX-40), MachXO5™-NX (LFMXO5-15D, LFMXO5-15D-AQA, LFMXO5-15D-HBN, LFMXO5-25, LFMXO5-55T, LFMXO5-55TD, LFMXO5-100T), CertusPro™-NX |

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | IP Changes <sup>1</sup>             | For a list of changes to the IP, refer to the DDR3 SDRAM Controller IP Release Notes (FPGA-RN-02032).                                                                                                       |

| Resource Utilization | Supported User Interfaces           | Data Access (Native or AXI4) Configuration Access (Native or APB)                                                                                                                                           |

|                      | Resources                           | Refer to Table A.1                                                                                                                                                                                          |

|                      | Lattice Implementation <sup>2</sup> | IP Core v2.3.0 – Lattice Radiant Software 2025.2                                                                                                                                                            |

| Design Tool Support  | Synthesis                           | Lattice Synthesis Engine Synopsys® Synplify Pro for Lattice                                                                                                                                                 |

|                      | Simulation                          | Questasim                                                                                                                                                                                                   |

| Driver Support       | API Reference                       | Refer to the Certus-NX DDR3 Memory Controller Driver User Guide (FPGA-TN-02401).                                                                                                                            |

#### Notes:

- 1. In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

- 2. Lattice Implementation indicates the IP version release coinciding with the software version release. Check the software for IP version compatibility with earlier or later software versions.

## 1.2. IP Support Summary

Table 1.2. DDR3 SDRAM Controller IP Support Readiness

| Device<br>Family | IP   | Rank   | Gearing<br>Ratio | DDR<br>Width | Data Rate (Mbps) | Hardware Validated | Radiant Timing Model     |

|------------------|------|--------|------------------|--------------|------------------|--------------------|--------------------------|

| Nexus            | DDR3 | Single | 4:1              | x8           | 600              | Yes                |                          |

|                  |      |        |                  |              | 666              | No                 |                          |

|                  |      |        |                  |              | 800              | No                 |                          |

|                  |      |        |                  | x16          | 600              | Yes                |                          |

|                  |      |        |                  |              | 666              | No                 |                          |

|                  |      |        |                  |              | 800              | No                 | Droliminan (1            |

|                  |      |        |                  | x24          | 600              | No                 | Preliminary <sup>1</sup> |

|                  |      |        |                  |              | 666              | No                 |                          |

|                  |      |        |                  |              | 800              | No                 |                          |

|                  |      |        |                  | x32          | 600              | No                 |                          |

|                  |      |        |                  |              | 666              | No                 |                          |

|                  |      |        |                  |              | 800              | No                 |                          |

FPGA-IPUG-02086-2.2

| Device<br>Family | IP | Rank | Gearing<br>Ratio | DDR<br>Width | Data Rate (Mbps) | Hardware Validated | Radiant Timing Model |

|------------------|----|------|------------------|--------------|------------------|--------------------|----------------------|

|                  |    |      | 8:1              | x8           | 600              | Yes                |                      |

|                  |    |      |                  |              | 666              | No                 |                      |

|                  |    |      |                  |              | 800              | Yes                |                      |

|                  |    |      |                  |              | 1,066            | Yes                |                      |

|                  |    |      |                  | x16          | 600              | Yes                |                      |

|                  |    |      |                  |              | 666              | No                 |                      |

|                  |    |      |                  |              | 800              | Yes                |                      |

|                  |    |      |                  |              | 1,066            | Yes                |                      |

|                  |    |      |                  | x24          | 600              | No                 |                      |

|                  |    |      |                  |              | 666              | No                 |                      |

|                  |    |      |                  |              | 800              | No                 |                      |

|                  |    |      |                  |              | 1,066            | No                 |                      |

|                  |    |      |                  | x32          | 600              | No                 |                      |

|                  |    |      |                  |              | 666              | No                 |                      |

|                  |    |      |                  |              | 800              | No                 |                      |

|                  |    |      |                  |              | 1,066            | No                 |                      |

#### Note:

1. Timing model is preliminary as the DDR characterization is not finalized.

#### 1.3. Features

The key features of DDR3 SDRAM Controller IP Core include:

- Memory data path widths of 8, 16, 24, 32 bits

- Selectable gearing ratios: 4:1, 8:1

- x8 and x16 device configurations

- Programmable burst lengths of 8 (fixed), chopped 4 or 8 (on-the-fly), or chopped 4 (fixed)

- Programmable read and write CAS latency set

- Read burst type of nibble sequential or interleave

- Automatic DDR3 SDRAM initialization and refresh

- Automatic write levelling for each DQS

- Automatic read training for each DQS

- Power Down mode with no DRAM data retention

- Dynamic On-Die Termination (ODT) controls

- Termination Data Strobe (TDQS) for x8 widths only

- I/O primitives manage read skews (read levelling equivalent)

- Automatic programmable interval refresh or user-initiated refresh

- Option for controlling memory reset outside the controller

The DDR3 SDRAM Controller IP Core supports the following devices:

- Interfaces to industry standard DDR3 SDRAM components and modules compliant with JESD79-3C, DDR3 SDRAM Standard

- Interfaces to DDR3 SDRAM at speeds up to 533 MHz/1,066 Mbps

#### **Table 1.3. Features Overview**

| Key Features                                         | DDR3 Support Details            |

|------------------------------------------------------|---------------------------------|

| Device Format                                        | Component                       |

| Data Widths                                          | X8, x16, x24 <sup>1</sup> , x32 |

| Data User Interface                                  | NATIVE, AXI4                    |

| Configuration Interface                              | NATIVE, APB                     |

| Maximum Command Speed                                | 533 Mbps                        |

| Maximum Data Speed                                   | 1,066 Mbps                      |

| HW Managed Periodic Events <sup>2</sup>              |                                 |

| Refresh                                              | All bank auto refresh           |

| ZQ Calibration                                       | Yes                             |

| Low Power Features                                   | Self-refresh with power down    |

| Other Features <sup>2</sup>                          |                                 |

| Error Correction Code (ECC)                          | No                              |

| Dual rank                                            | No                              |

| Data Bus Inversion (DBI)                             | No                              |

| Temperature Tracking                                 | Yes                             |

| Refresh Adaptation (derate) to Temperature Variation | Yes                             |

| On-Die Termination (ODT)                             | Yes                             |

| Training <sup>2</sup>                                |                                 |

| Initialization                                       | Yes                             |

| Command Training                                     | No                              |

| Write Leveling                                       | Yes                             |

| Read Training                                        | Yes                             |

| Write Training                                       | Yes                             |

| VREF Training                                        | No                              |

#### Notes:

- 1. Data Width x24 is supported only when data user interface is configured as NATIVE.

- 2. Yes implies that a configurable option exists to enable or disable the feature. No implies that the feature is currently not supported.

## 1.4. Licensing and Ordering Information

The DDR3 Memory Controller IP for Nexus Devices is provided at no additional cost with the Lattice Radiant Software.

## 1.5. Hardware Support

Refer to the Example Design for more information on the board used.

#### 1.6. Minimum Device Requirements

The following table summarizes the minimum device requirements for the Memory Controller IP Core.

**Table 1.4. Minimum Device Requirements**

|                                             |                               |                   | Supported Speed Grades                 |              |  |

|---------------------------------------------|-------------------------------|-------------------|----------------------------------------|--------------|--|

| DDR3 Interface Speed                        | Gearing Ratio DDR3 Data Width |                   | Certus-NX, CrossLink-NX and MachXO5-NX | CertusPro-NX |  |

| 300 MHz (600 Mbps) to<br>333 MHz (666 Mbps) | 4:1                           | x8, x16, x24, x32 | 8, 9                                   | 7, 8, 9      |  |

| 400 MHz (800 Mbps)                          | 4:1                           | x8, x16, x24, x32 | 9                                      | 9            |  |

| 300 MHz (600 Mbps) to<br>400 MHz (800 Mbps) | 8:1                           | x8, x16, x24, x32 | 7, 8, 9                                | 7, 8, 9      |  |

| 533 MHz (1,066 Mbps)                        | 8:1                           | x8, x16, x24, x32 | 8, 9                                   | 8, 9         |  |

## 1.7. Naming Conventions

This section provides information regarding terminology used within this document.

#### 1.7.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.7.2. Signal Names

Signal Names that end with:

- n is active low

- \_i are input signals

- \_o are output signals

- \_io are bi-directional input/output signals

#### 1.8. Limitations

- The AXI interface supports a maximum burst length of 64 beats.

- The AXI interface lacks a dedicated clock; the output clock port is sclk o.

- The Lattice LSE synthesis engine causes difficulty in closing timing, especially for the eval\_top's RISC-V and its

interfacing modules. The DDR3 SDRAM Controller IP Core closes timing correctly.

- The Example Design does not support (both on hardware and simulation) having Gearing Ratio set to 4:1 and Burst Length set to On-the-fly. However, this configuration is a supported feature of the IP.

## 2. Functional Description

#### 2.1. IP Architecture

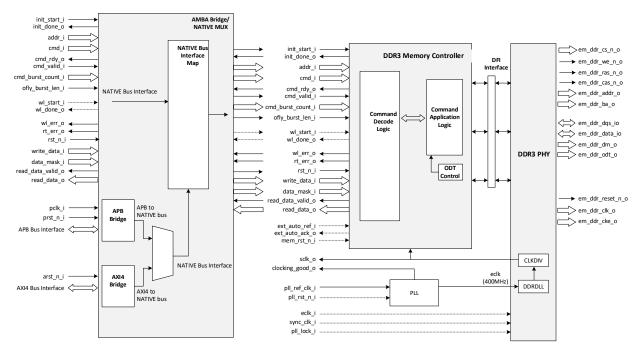

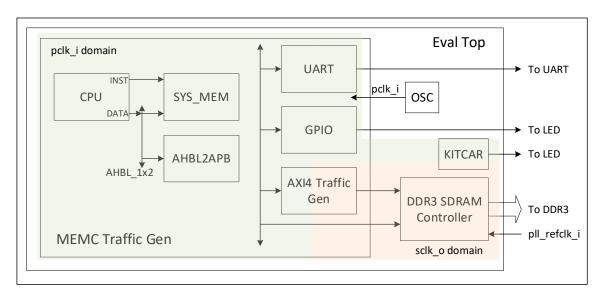

The DDR3 memory controller consists of four submodules: AXI4/APB Bridge Interface Module, Soft Memory Controller (MC) module, Soft Physical Interface (PHY) module and Soft Training Engine. The following subsections briefly describe the operation of each submodule. Figure 2.1 provides a high-level block diagram illustrating the main functional blocks used to implement the DDR3 SDRAM Controller IP Core functions.

Figure 2.1. Memory Controller IP Core Functional Diagram

#### 2.1.1. AXI4/APB Bridge Interface

The DDR3 memory controller contains the APB bridge interface for handling configuration access and AXI4 bridge interface for handling data access.

#### 2.1.1.1. APB Bridge Interface

This interface module implements the APB slave interface, handling all configuration-related operations. This involves initialization and executing user commands. You can access the status register via the APB interface module. This interface runs on its own clock and reset. For further details, refer to the APB section.

#### 2.1.1.2. AXI4 Bridge Interface

This interface module implements the AXI4 slave interface, handling write and read operations. This interface runs on SCLK but has a separate reset from the system reset. For further details, refer to the AXI4 section.

#### 2.1.2. Soft Memory Controller

The DDR3 Memory Controller module contains Command Decode Logic (CDL) block, the Command Application Logic (CAL) block, and On-Die Termination (ODT) Control block.

#### 2.1.2.1. Command Decode Logic

The Command Decode Logic (CDL) block accepts user commands from the local interface and decodes them to generate a sequence of internal memory commands based on the current command and the status of current bank and row. The intelligent bank management logic tracks the open/close status of every bank and stores the row address of every opened bank. The controller implements a command pipeline to improve throughput. With this capability, the next command in the queue is decoded while the current command is presented at the memory interface.

#### 2.1.2.2. Command Application Logic

The Command Application Logic (CAL) block accepts the decoded internal command sequence from the Command Decode Logic and translates each sequence into memory commands that meet the operational sequence and timing requirements of the memory device. The CDL and CAL blocks work in parallel to fill and empty the command queue, respectively.

#### 2.1.2.3. On-Die Termination Control

The ODT feature improves the signal integrity of the memory channel by allowing the DDR3 SDRAM Controller IP Core to independently turn on or off the termination resistance for any or all DDR3 SDRAM devices.

#### 2.1.3. Soft PHY and Soft Training Engine

Please refer to the DDR3 SDRAM PHY IP Core User Guide (FPGA-IPUG-02098).

## 2.2. Clocking and Reset

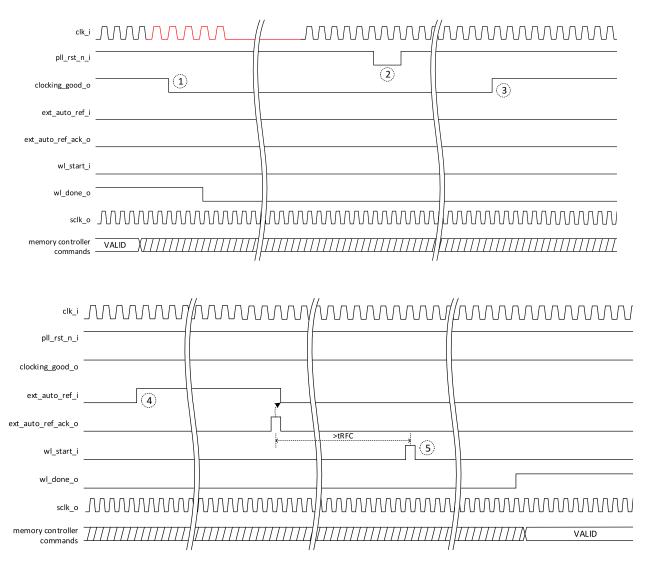

You can reset the PLL module independently if the PLL lock is lost. For this setup, both initialization and read training are skipped, and only write leveling is required. Check the following attributes in the Module/IP Block Wizard to enable this setup: Enable PLL and Enable External PLL Reset.

Figure 2.2. shows the recommended steps for resetting the PLL and resuming the valid operation of the controller.

- 1. The clocking\_good\_o deasserts when PLL lock is lost due to the PLL reference clock (clk\_i),

- 2. Assert pll rst n i to reset the PLL module after the PLL reference clock returns to normal

- 3. Wait until the clocking good o asserts, indicating a stable clocking condition.

- 4. Assert ext\_auto\_ref to execute a memory refresh. Hold ext\_auto\_ref then deassert the signal at the same edge of the sampling clock when ext\_auto\_ref ack\_o goes high.

- 5. Assert wl\_start\_i for 1 sclk\_o cycle to perform write leveling. Wait until wl\_done\_o goes high, indicating the completion of the write leveling.

#### Note:

\*You can skip both step 4 and step 5 if you do not select the Write Leveling attribute.

Figure 2.2. External PLL Reset Steps

#### 2.3. User Interfaces

#### 2.3.1. Data Interface Protocols

The Data Path Logic interfaces with the DDR3 I/O modules and generates the read data and read data valid signals during read operations. This block implements all the logic needed to ensure that the data writes and reads to and from the memory are transferred to the local user interface in a deterministic and coherent manner.

#### 2.3.1.1. Native

The native interface provides direct access to the Soft Memory Controller command, address, command valid, data and data valid ports. Refer to the DDR3 Operation Description for more details on how to use the native interface for data access.

#### 2.3.1.2. AXI4

The AXI4 interface is available in IP Core v2.1.0 and operates on the sclk\_o signal. However, it is reset via the arst\_n\_i and rst\_n\_i signals. Resetting this interface via the arst\_n\_i triggers a reset to the Soft Memory Controller but not the Soft PHY and Soft Training Engine. Resetting the rst\_n\_i resets this interface, the Soft Memory Controller, and the Soft PHY and Soft Training Engine. Refer to the Clocking and Reset section of this user guide for more details.

The Memory Controller IP supports the following AXI4 types of burst transfers:

- Burst Type:

- SINGLE: single burst (1 beat)

- INCR: incrementing burst that does not wrap at address boundaries (4 or 8 beats)

- Burst Size :

- [8, 16, 32, 64] beats

- Burst Address:

- Unaligned addressing is supported.

The AXI4 protocol supports only a single outstanding transaction per bus master. Both read and write operations cannot happen concurrently and are arbitrated in a round-robin fashion, with both given equal priority. All responses are returned in order. For more information regarding the AXI4 protocol, refer to the AMBA AXI4 Protocol Specification.

**Table 2.1. Supported AXI4 Transactions**

| Transaction<br>Type | AXI<br>Data<br>Width | LENGTH | AxSIZE        | Comment                                     |

|---------------------|----------------------|--------|---------------|---------------------------------------------|

| Read/Write          | 32                   | 0      | [0,1,2]       | [1,2,4] Byte transferred                    |

| Read/Write          | 32                   | 1      | [0,1,2]       | [2,4,8] Byte transferred                    |

| Read/Write          | 32                   | 32     | [0,1,2]       | [32,64,128] Byte transferred                |

| Read/Write          | 32                   | 64     | [0,1,2]       | [64,128,256] Byte transferred               |

| Read/Write          | 64                   | 0      | [0,1,2,3]     | [1,2,4,8] Byte transferred                  |

| Read/Write          | 64                   | 1      | [0,1,2,3]     | [2,4,8,16] Byte transferred                 |

| Read/Write          | 64                   | 32     | [0,1,2,3]     | [32,64,128,256] Byte transferred            |

| Read/Write          | 64                   | 64     | [0,1,2,3]     | [64,128,256,512] Byte transferred           |

| Read/Write          | 128                  | 0      | [0,1,2,3,4]   | [1,2,4, 8,16] Byte transferred              |

| Read/Write          | 128                  | 1      | [0,1,2,3,4]   | [2,4,8, 16,32] Byte transferred             |

| Read/Write          | 128                  | 32     | [0,1,2,3,4]   | [32,64,128,256,512] Byte transferred        |

| Read/Write          | 128                  | 64     | [0,1,2,3,4]   | [64,128,256,512,1024] Byte transferred      |

| Read/Write          | 256                  | 0      | [0,1,2,3,4,5] | [1,2,4, 8,16,32] Byte transferred           |

| Read/Write          | 256                  | 1      | [0,1,2,3,4,5] | [2,4,8,16,32,64] Byte transferred           |

| Read/Write          | 256                  | 32     | [0,1,2,3,4,5] | [32,64,128,256,512,1024] Byte transferred   |

| Read/Write          | 256                  | 64     | [0,1,2,3,4,5] | [64,128,256,512,1024,2048] Byte transferred |

#### Table 2.2. Address Mapping

| Memory Address         | Size                                                                                                                                                              | Local Address Map                                 |                         |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------|--|--|--|

| Row                    | ROW_WIDTH = 13, 14, 15, 16 (depending on DDR Density and Configuration                                                                                            | ROW_H = ROW_L + ROW_WIDTH-1<br>ROW_L = BANK_H + 1 | AxADDR[ROW_H:<br>ROW_L] |  |  |  |

| Bank                   | BSIZE = 3                                                                                                                                                         | BANK_H = COL_H +BSIZE -1<br>BANK_L = COL_H + 1    | AxADDR[BANK_H: BANK _L] |  |  |  |

| Column                 | COL_WIDTH = 10, 11, 12 (depending on DDR Density and Configuration)                                                                                               | COL_H = COL_L + ACTUAL_COL_WIDTH - 1 COL_L = 0    | AxADDR[COL_H: COL_L]    |  |  |  |

| Actual Column<br>Width | If DDR Bus Width == 32; ACTUAL_COL_WIDTH = COL_WIDTH+2 If DDR Bus Width == 16: ACTUAL_COL_WIDTH = COL_WIDTH+1 If DDR Bus Width == 8: ACTUAL_COL_WIDTH = COL_WIDTH | N/A                                               |                         |  |  |  |

#### Table 2.3. AXI4 to Memory Address Mapping Example

| Memory Address      | Example User Value                       | Actual Line Size | Local Address Map  |

|---------------------|------------------------------------------|------------------|--------------------|

| Actual Column Width | DDR Bus Width = 32                       | 12               | -                  |

| Column Width (COLW) | DDR_DENSITY = 1Gb<br>Configuration = x16 | 10               | axi_axaddr_i[11:0] |

| Bank Width (BANKW)  | 3 (Fixed for DDR3)                       | 3                | axi_axddr_i[14:12] |

| Row Width (ROWW)    | DDR_DENSITY = 1Gb<br>Configuration=x16   | 13               | axi_axddr_i[27:15] |

| Rank Width (RANKW)  | Number of Ranks = 1                      | 0                | -                  |

| Total Local Ad      | dress Line Size                          | 30               | *addr_i[29:0]      |

#### 2.3.2. Configuration Interface Protocol

#### 2.3.2.1. Native

The native interface provides direct access to the Soft Memory Controller command, address, command valid, data and data valid ports. Refer to the DDR3 Operation Description for more details on how to use the *native* interface for configuration access.

#### 2.3.2.2. APB

The APB interface is available in IP Core v2.1.0 and operates on its own clock and reset. This interface implements a register map for control configuration, status readback, and executing user commands. Refer to the Register Description section for more details.

#### 2.4. DDR3 Calibration

The DDR3 PHY module provides PHY interface to the memory device. It implements soft logic in the FPGA fabric for initialization, write leveling, read training, and read/write data paths. It utilizes hard logic, called DDR3 I/O modules, for a 4:1 or 8:1 gearing ratio and DDR3 memory interface. The DDR3 I/O modules are hardware primitives that directly interface with the DDR3 memory, including the IDDR/ODDR/TDDR resource indicated in Table A.1. These primitives implement all the interface signals required for memory access. They convert the single data rate (SDR) data to double rate (DDR3) data for write operation and perform the DDR3 to SDR conversion in read mode.

The DDR3 PHY also ensures that the clock domain crossing margin between ECLK to SCLK stays the same for the IDDR and ODDR buses that produce 4:1 or 8:1 gearing ratio. Without proper synchronization, the bit order on different elements might be out of sync with each other, and the entire bus could be scrambled. Clock synchronization ensures that all DDR components start from the same edge clock cycle.

For 400 MHz DDR3 memory clock operation and a 4:1 gearing ratio, the Memory Controller Module operates with a 200 MHz system clock (SCLK), and the I/O logic in the DDR3 PHY Module works with a 400 MHz edge clock (ECLK). This operating clock ratio and the double data rate transfer lead to a user-side data bus that is four times the width of the memory-side data bus. For example, a 32-bit memory-side data width requires a 128-bit read data bus and a 128-bit write data bus at the user-side interface.

For 400 MHz DDR3 memory clock operation and an 8:1 gearing ratio, the Memory Controller Module operates with a 100 MHz system clock (SCLK), and the I/O logic in the DDR3 PHY Module works with a 400 MHz edge clock (ECLK). This operating clock ratio and the double data rate transfer leads to a user-side data bus that is eight times the width of the memory-side data bus. For example, a 32-bit memory-side data width requires a 256-bit read data bus and a 256-bit write data bus at the user-side interface.

#### 2.4.1. Initialization and Training Sequence

The Initialization block performs the DDR3 memory initialization sequence as defined by the JEDEC protocol. After powering on or resetting the DDR3 controller, you must initialize the memory before sending any command to the controller. You need to assert the init\_start input to the DDR3 controller to start the memory initialization sequence. The init\_done\_o signal indicates the completion of initialization.

#### 2.4.1.1. Write Leveling

The write leveling block adjusts the DQS-to-CLK relationship for each memory device using the write level mode of the DDR3 SDRAM when the fly-by topology is implemented. Write leveling is always done immediately after a memory initialization sequence. When the init\_done\_o signal is asserted after the initialization process, it also indicates the completion of write leveling. If the write leveling process is not successful, the wl\_err\_o signal is also asserted along with the init\_done\_o signal. To ensure the DQS-to-CLK alignment is optimal, the first DQ sample coming back from the DDR3 must not be a 1. If it is a 1, there will be an auto adjustment to the CLK delay, in which case the CLK will be delayed until the first DQ sample coming back from the DDR3 is a 0. This happens before the actual write-leveling operation begins. The CLK delay should not be arbitrarily set to a large number. The default should be used. In cases where the default does not work, set it to 0, and let the IP auto-adjust the CLK delay to the correct value. Setting it high may cause write-leveling to fail, as it will be unable to successfully align DQS to CLK.

The DDR3 memory module adopts fly-by topology for the address, command, control, and clock signals for better signal integrity. This reduces the number of stubs and length but causes flight time skew between the DQS and CLK. Therefore, DDR3 allows the controller to compensate for the skew of the DQS signal delays to those signals at the DDR3 DRAM side through its write leveling capability. Route the PCB for the on-board memory application using the fly-by topology. Otherwise, write leveling failures occur due to the lack of guaranteed DQS to CLK edge relationship at the beginning of write level training. For this reason, disable the write leveling option if the PCB does not use fly-by routing for write leveling.

The write leveling scheme of the DDR3 SDRAM Controller IP core follows all the steps stipulated in the JEDEC specification. For more details on write leveling, refer to the JEDEC specification JESD79-3C.

#### 2.4.1.2. Read Training (DQS Gate)

For every read operation, you must initialize the DDR3 I/O primitives of the LIFCL family device at the appropriate time to identify the incoming DQS preamble. Upon proper detection of the preamble, the primitive DQSBUF extracts a clean signal from the incoming DQS signal from the memory and generates BTDETECT, BURSTDETECT and DATAVALID output signals that indicate the correct timing window of the valid read data.

The memory controller generates a positioning signal, READ[3:0], to the primitive DQSBUF that is used for the above-mentioned operation. In addition to the READ[3:0] input, a fine control input signal RDCLKSEL[3:0] and an output signals BTDETECT and BURSTDETECT of the DQSBUF block are provided to the controller to accomplish the READ[3:0] signal positioning.

Due to the DQS round trip delay, which includes PCB routing and I/O pad delays, proper internal positioning of the READ[3:0] signal with respect to the incoming preamble is crucial for successful read operations. The LIFCL family DQSBUF block supports a dynamic READ[3:0] signal positioning function called read training. This function enables the memory controller to position the internal READ[3:0] signal within an appropriate timing window by progressively shifting the READ[3:0] signal and monitoring positioning results.

This read training is performed as part of the memory initialization process, after the write leveling operation is complete. During the read training, the memory controller generates the READ[3:0] pulse, positions this signal using RDCLKSEL[3:0] and monitors the BTDETECT output of DQSBUF for the result of the current position. The READ[3:0] signal is set high before the read preamble starts. When the READ[3:0] pulse is properly positioned, the preamble is detected correctly, and the BTDETECT and BURSTDETECT are asserted. This guarantees that the generated DATAVALID signal indicates the correct read valid time window.

The READ[3:0] signal is generated in the system clock (sclk\_o) domain and stays asserted for the total burst length of the read operation.

A minimum burst length of four times the memory bus length is used in the read training process. The memory controller can determine proper position alignment when there are no failures on BTDETECT assertions during the multiple trials. If there is a failure, the memory controller shifts the READ[3:0] signal position and tries again until it detects no BTDETECT failure.

The memory controller stores the delay value of the successful position of the READ[3:0] signal for each DQS group. It uses these delay values during a normal read operation to correctly detect the preamble first, followed by the generation of DATAVALID signal.

#### 2.4.1.3. Extended Training

The extended training provides more robust calibration performance, where the DQ/DM-to-DQS phase adjustment is done to achieve the optimal phase relationship. The extended training is only performed with the example-design. The result will be displayed and should be used to configure the IP parameters appropriately.

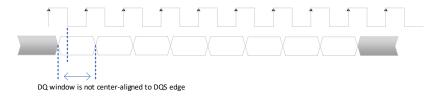

#### 2.4.1.3.1 Write Training

Write training delays each DQS relative to DQ during write operations to optimize the data window. During this stage, a coarse adjustment is performed to obtain an initial valid DQ-DQS phase alignment on both write and read. Once a valid DQ-DQS coarse alignment is achieved for both write and read, the fine-tuning of the write DQ-DQS adjustment is performed. This is done by performing a write followed by a read, and DQ is delayed in the positive (incremental) direction. This is done repeatedly until the data being read back no longer matches the data written. This determines the maximum boundary. The DQ-DQS phase is then reset to the default position. The same sequence is performed, but this time with DQ being delayed in the negative (decremental) direction. A data mismatch indicates the minimum boundary. The optimal position is then calculated as the midpoint between the maximum and the minimum boundary.

Figure 2.3. Before Write Training

Figure 2.4. After Write Training

The write training is performed as part of the example-design sequence, and the resulting window and optimal position will be displayed, as the example below:

```

Starting Write DQ/DM Calibration

W

Write DQ/DM Maximum Delay Value: 2

Write DQ/DM Minimum Delay Value: -94

Write DQ/DM Optimal Delay Value: -46

```

Figure 2.5. Result

This example illustrates a window size of 96 delay taps (one tap equals 12.5 ps), with the maximum boundary at 2 and the minimum boundary at –94. The optimal DQ-DQS phase is taken based on the midpoint of this window, which is –46.

The corresponding parameters from the IP configuration GUI should be updated accordingly:

- Write DQ/DM Delay Direction: Decrement (negative indicates decrement)

- Write DQ/DM Delay Value: 46

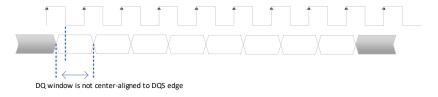

#### 2.4.1.3.2 Read Data Eye Training

The read data eye training center-aligns DQS relative to the DQ window. There are two scenarios in this step.

- **Default DQ-DQS position results in a bad read:** During this step, a write is performed followed by a read, and DQ is delayed in the positive (incremental) direction. This is repeated until the data read back matches the data written. The minimum boundary is determined. This step is repeated until the data read back no longer matches the data written. The maximum boundary is determined. The optimal DQ-DQS phase relationship is calculated by taking the midpoint between the maximum and the minimum boundary.

- **Default DQ-DQS position results in a good read:** During this step, a write is performed followed by a read, and DQ is delayed in the positive (incremental) direction. This is repeated until the data read back does not match the data written. The maximum boundary is determined. The same sequence is repeated, but this time DQ is delayed in the negative (decremental) direction. A data mismatch indicates the minimum boundary. The optimal DQ-DQS phase relationship is calculated by taking the midpoint between the maximum and the minimum boundary.

Figure 2.6. Before Read Data Eye Training

Figure 2.7. After Read Data Eye Training

The read data-eye training is performed as part of the example-design sequence, and the resulting window and optimal position will be displayed as shown in the example below:

```

Starting Read DQ Calibration

R

Read DQ Maximum Delay Value: 50

Read DQ Minimum Delay Value: 0

Read DQ Optimal Delay Value: 9

Read DQ Phase Adjustment Optimal Delay Value: 0

```

Figure 2.8. Result

This example shows how calibration determines the optimal delay for DQ relative to DQS.

- Window size: 82 delay taps (each tap = 12.5 ps)

- Boundaries:

- Maximum: +50 taps

- Minimum: –32 taps (calculated, not displayed)

- Display values:

- Maximum delay shown: 50 taps

- Minimum delay shown: 0 tap (the physical delay element cannot apply negative delay).

The negative boundary (-32) is theoretical and calculated. You can achieve an effective negative delay by adjusting the internal DQ sampling phase (reducing the DQ-to-DQS phase below  $90^{\circ}$ ), as described in the IP user guide. The display shows the minimum delay value (0), which differs from the minimum boundary (-32).

#### **Optimal Delay**

- The midpoint of the window is +9 taps, indicating that the best alignment is achieved by adding nine taps to DQ.

- Since this is a positive delay, no phase adjustment is needed. Therefore:

- Read DQ Delay Value: 9

- Read DQ Phase Adjustment Direction: Increment

- Read DQ Phase Adjustment Value: 0

#### Read DQ Phase Adjustment Value Explained

Why zero (0) is correct:

The delay element cannot apply negative delay. In this case, the optimal delay (+9 taps) is achievable by the DQ delay element alone, so no extra phase shift is needed.

When it would be nonzero:

If the calculated optimal delay were negative (such as -10 taps), the tool would set the DQ delay to zero (0) and apply a phase adjustment equivalent to -10 taps internally.

© 2019-2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02086-2.2

#### 2.4.2. Initialization and Training with APB Interface

When the APB interface is enabled, the init start i port is no longer be available. Initialization is initiated using the APB interface. Refer to the Register Description section for more details on the register map. You should execute the following steps to start the initialization and training sequence of the DDR3 SDRAM:

- Initiate an APB write transaction to address offset 0x00. The data to be written should be 'b1001. Set bit 3 to enable configuration mode and bit 0 to trigger the initialization.

- 2. Perform an APB read transaction to address offset 0x04. Check if bit 0 is driven HIGH.

- 3. Repeat step 2 until bit 0 is driven HIGH. This indicates that initialization is complete.

- 4. Perform an APB write transaction to address offset 0x00. The data to be written should be 'b0000. Set bit 3 to '0' to switch from configuration mode to data mode.

## 2.5. DDR3 Operation Description

The native interface of the DDR3 SDRAM Controller IP Core consists of five independent functional groups. Each functional group and its associated local interface signals as listed in Table 2.4.

**Table 2.4. Native Interface Functional Groups**

| Functional Group       | Native Interface Signals                                 |

|------------------------|----------------------------------------------------------|

| Initialization Control | init_start_i, init_done_o, rt_done_o, rt_err_o, wl_err_o |

| Command and Address    | addr_i, cmd_i, cmd_rdy_o, cmd_valid_, cmd_burst_cnt_i    |

| Data Write             | datain_rdy_o, write_data_i, data_mask_i                  |

| Data Read              | read_data_o, read_data_valid_o                           |

| Auto Refresh           | ext_auto_ref_i, ext_auto_ref_ack_o                       |

When the AXI4 and APB Interfaces are enabled, these modules interfaces directly with the native interface within the memory controller. The APB Interface drives the Initialization Control group and the Command and Address group. The AXI4 interface drives the Command and Address, Data Write, and Data Read groups. Auto Refresh is available only on the native interface. To handle the resource contention between AXI4 and APB on the Command and Address group, use the Enable APB Config bit from the APB Control Reg. Write a '1' to this bit to give the APB Interface access to the Command and Address group. Writing a '0' to this bit returns access to the AXI4 Interface. Refer to the APB section for more details.

#### 2.5.1. Initialization Control

You must initialize DDR3 memory devices before the memory controller can access them. The memory controller starts the memory initialization sequence when the init\_start\_i signal is asserted. Once asserted, the init\_start\_i signal needs to be held high until the initialization process is completed. The init done o signal is asserted high for one clock cycle, indicating that the core has completed the initialization sequence and is now ready to access the memory. You must negate the init\_start\_i signal as soon as the init\_done\_o signal is sampled high at the rising edge of sclk\_o. Memory initialization is required only once, immediately after the system reset.

The JESD79-3C standard specifies the following minimum reset assert time requirements:

- During power-up initialization: 200 ns

- During reset initialization with stable power: 100 ns

You are responsible for ensuring that the above minimum reset assert duration is met.

As part of Initialization, the memory controller ensures a minimum gap of 500 µs between em ddr reset n i deassertion and em\_ddr\_cke\_o assertion.

The IP Core performs write levelling for all available ranks and stores the write level delay values.

Read training is also performed during the initialization process to find the best-read pulse position that detects the incoming read DQS preamble timing. Since DDR3 memory does not use a DLL function, the clock-to-DQS driving time can vary significantly with process, voltage, and temperature (PVT) variations. Because of this, periodic retraining of the

read pulse position may be necessary to guarantee stable read transactions over the PVT variations during normal operation.

#### 2.5.2. Command and Address

Once the memory initialization is complete, the core waits for user commands to set up and access the memory. The user logic needs to provide the command, address, and control signals to the core. Commands and addresses are delivered to the core using the Command Decoding Registers.

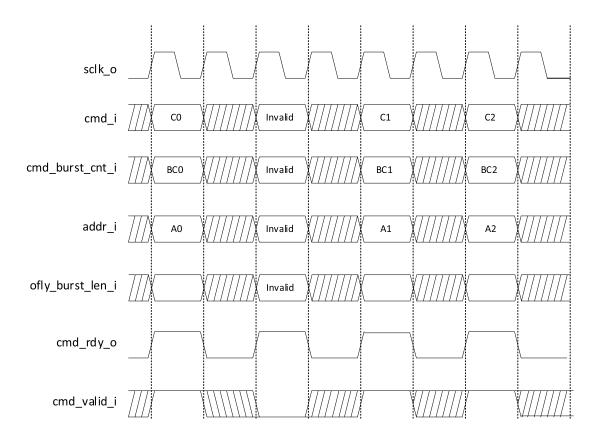

The DDR3 SDRAM Controller IP Core informs the user logic that it is ready to receive a command by asserting the cmd\_rdy\_o signal for one cycle. If the core finds the cmd\_valid\_i signal asserted by the user logic while its cmd\_rdy\_o is asserted, it takes the cmd\_i input as a valid user command. Usually, cmd\_valid\_i is de-asserted at the rising edge of the clock that samples cmd\_rdy\_o high. The core also accepts the addr\_i input as a valid start address or mode register programming data, depending on the command type. Along with the addr\_i input, the core also accepts the signals cmd\_burst\_cnt\_i and ofly\_burst\_len\_i. If cmd\_valid\_i is not asserted, the cmd\_i and addr\_i inputs become invalid, and the core ignores them. The cmd\_i, addr\_i, cmd\_burst\_cnt\_i, ofly\_burst\_len\_i and cmd\_valid\_i inputs are ignored while cmd\_rdy\_o is de-asserted. The cmd\_rdy\_o signal is asserted again to accept the next command.

The core is designed to ensure maximum throughput at a burst length of eight by asserting cmd\_rdy\_o once every two-clock cycle, unless the command queue is full or there is an intervention on the memory interface (such as Auto-Refresh cycles.)

When the core is in the command burst operation, it extensively occupies the data bus. During this time, the IP Core negates cmd\_rdy\_o until the command burst is completed. While the IP Core is operating in command burst mode, it can keep maximum throughput by internally replicating the command. The memory controller can repeat the given READ or WRITE command up to 32 times. The cmd\_burst\_cnt\_i[4:0] input is used to set the number of repeats of the given command. The core allows the command burst function to access the memory addresses within the current page. When the core reaches the boundary of the current page while accessing the memory in the command burst mode, the next address to be accessed by the core becomes the beginning of the same page. This causes overwriting of contents or reading unexpected data. You must therefore track the accessible address range in the current page, while the command burst operation is performed. If an application requires a fixed command burst size, using 2-, 4-, 8-, 16- or 32-burst with burst-aligned column address is recommended to ensure that the command burst accesses do not cross the page boundary.

When cmd\_burst\_cnt\_i and ofly\_burst\_len\_i are 0, the controller performs 32 commands (reads or writes). The cmd\_burst\_cnt\_i input is sampled the same way as the cmd signal. The timing diagram of Command and Address group signals is shown in Figure 2.9. When cmd\_burst\_cnt\_i is sampled with a value greater than 00001, and the command queue becomes full, the cmd\_rdy\_o signal is not asserted, and the memory address is automatically increased by the core until the current command burst cycle is completed.

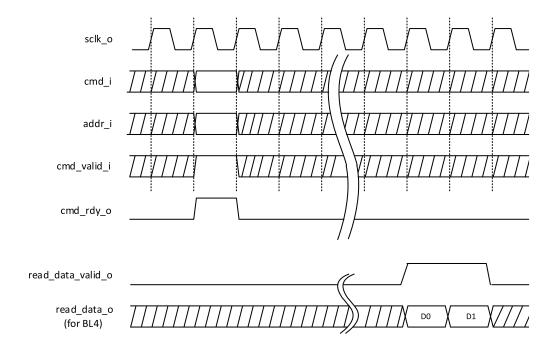

Figure 2.9. Timing of Command and Address

#### 2.5.2.1. Address Mapping

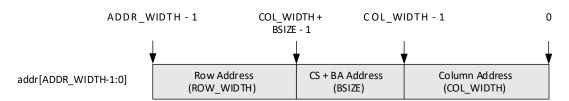

Mapping local addresses to memory addresses is an important part of system design when implementing a memory controller function. You must know how the local address lines from the memory controller connect to those address lines from the memory because proper local-to-memory address mapping is crucial to meet system requirements in applications such as a video frame buffer controller. Even for other applications, careful address mapping is generally necessary to optimize system performance. On the memory side, the address (A), bank address (BA) and chip select (CS) inputs are used for addressing a memory device. You can obtain this information from a given data sheet. Figure 2.10 shows the local-to-memory address mapping of the Lattice DDR3 memory controller cores.

Figure 2.10. Local-to-Memory Address Mapping for Memory Access

ADDR\_WIDTH is calculated by the sum of COL\_WIDTH, ROW\_WIDTH and BSIZE. BSIZE is determined by the sum of the BANK\_WIDTH and CS\_WIDTH. For DDR3 devices, the bank address size is always 3. When the number of chip select is 1, 2, or 4, the chip select address size becomes 0, 1, or 2, respectively. An example of a typical address mapping is shown in Table 2.5 and Figure 2.11.

**Table 2.5. Address Mapping Example**

| Attribute Name                  | Example User Value | Actual Line Size | Local Address Map |

|---------------------------------|--------------------|------------------|-------------------|

| Column Size                     | 11                 | 11               | addr_i[10:0]      |

| Bank Size*                      | 8                  | 3                | addr_i[13:11]     |

| Rank Size (or Chip Select Size) | Dual               | 1                | addr_i[14]        |

| Row Size                        | 14                 | 14               | addr_i[28:15]     |

| Total Local Ad                  | dress Line Size    | 29               | addr_i[28:0]      |

<sup>\*</sup>Note: Bank Size is not set in Module/IP Block Wizard, this is fixed for DDR3.

Figure 2.11. Mapped Address for the Example

#### 2.5.3. User Commands

You initiate a request to the memory controller by loading a specific command code in cmd input along with other information such as memory address. The command on the cmd bus must be a valid command. Lattice defines a set of valid memory commands as shown in Table 2.6. All other values are reserved and considered invalid.

**Table 2.6. Defined User Commands**

| Command                    | Mnemonic     | cmd_i[3:0] |

|----------------------------|--------------|------------|

| Read                       | READ         | 4'b0001    |

| Write                      | WRITE        | 4'b0010    |

| Read with Auto Pre-charge  | READA        | 4'b0011    |

| Write with Auto Pre-charge | WRITEA       | 4'b0100    |

| Power down Entry           | PDOWN_ENT    | 4'b0101    |

| Load Mode Register         | LOAD_MR      | 4'b0110    |

| Self-Refresh Entry         | SEL_REF_ENT  | 4'b1000    |

| Self-Refresh Exit          | SEL_REF_EXIT | 4'b1001    |

| Power down Entry           | PDOWN_EXIT   | 4'b1011    |

| ZQ Calibration Long        | ZQ_LNG       | 4'b1100    |

| ZQ Calibration Short       | ZQ_SHRT      | 4'b1101    |

#### Notes:

- The controller accepts only the command codes listed above as legal commands. It discards any other command code as an invalid command.

- The controller discards Self-Refresh Entry or Power Down Entry command if the memory is already in Self Refresh mode or Power Down mode respectively.

- The controller discards Self-Refresh Exit or Power Down Exit command if the memory is already not in Self Refresh mode or Power Down mode respectively.

- The controller issues a refresh before every self-refresh entry command.

#### 2.5.4. WRITE

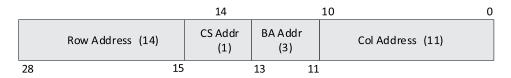

You initiate a memory write operation by asserting cmd\_valid\_i along with the WRITE or WRITEA command and the address. After the WRITE command is accepted, the memory controller core asserts the datain\_rdy\_o signal when it is ready to receive the write data from the user logic to write into the memory. Since the duration from the time a write command is accepted to the time the datain\_rdy\_o signal is asserted is not fixed, the user logic needs to monitor the datain\_rdy\_o signal. Once datain\_rdy\_o is asserted, the core expects valid data on the write\_data bus one or two clock cycles after the datain\_rdy signal is asserted. You can program the write data delay by setting the value for *Data ready to Write Data delay* attribute, providing flexible backend application support. For example, setting the value to 2 ensures that the core takes the write data in proper time when the local user interface of the core is connected to a synchronous FIFO module inside the user logic. Figure 2.12 shows two examples of the local user interface data write timing. Both cases are in BL8 (Burst Length 8) mode. The upper diagram shows the case of one clock cycle delay of write data, while the lower one displays a two clock-cycle delay case. The memory controller considers D0, DM0 through D5, DM5 valid write data.

The controller decodes the addr input to extract the current row and current bank addresses and checks if the current row in the memory device is already opened. If there is no opened row in current bank, the controller generates an ACTIVE command to the memory to open the current row first. Then the memory controller issues a WRITE command to the memory. If there is already an opened row in the current bank and the current row address is different from the opened row, the controller generates a PRECHARGE command to close opened row in the bank. This is followed by an ACTIVE command to open the current row. Then the memory controller issues a WRITE command to the memory. If the current row is already opened, the controller sends only a WRITE command (without any ACTIVE or PRECHARGE commands) to the memory.

Figure 2.12. One-Clock vs. Two-Clock Write Data Delay

\*Note: WrRqDDelay is Data ready to Write Data delay attribute, which is currently fixed to 1.

#### 2.5.5. WRITEA

WRITEA is treated the same way as the WRITE command, except that the IP Core issues a Write with Auto Precharge command to the memory, instead of just a Write command. This causes the memory to automatically close the current row upon completing the write operation. The AXI4 Interface does not send the WRITEA command for write transactions.

#### 2.5.6. READ

When the READ command is accepted, the memory controller core accesses the memory to read the addressed data and brings the data back to the local user interface. Once the read data is available on the local user interface, the memory controller core asserts the read\_data\_valid\_o signal to tell the user logic that the valid read data is on the read\_data\_o bus. The read data timing on the local user interface is shown in Figure 2.13. The read operation follows the same row status checking scheme as mentioned in the write operation. Depending on the current row status, the memory controller generates ACTIVE and PRECHARGE commands, as required. Refer to the description mentioned in Write operation for more details.

Figure 2.13. User-Side Read Operation

#### 2.5.7. READA

READA is treated the same way as the READ command except that the IP Core issues a Read with Auto Precharge command to the memory instead of a Read command. This makes the memory automatically close the current row after completing the read operation. The AXI4 Interface doesn't send the READ command for read transactions.

#### 2.5.8. Mode Register Programming

The DDR3 SDRAM memory devices are programmed using the mode registers MR0, MR1, MR2, and MR3. The bank address signal (em\_ddr\_ba\_o) chooses one of the mode registers, while the programming data is delivered through the address signal (em\_ddr\_addr\_o). The memory data signal is not used for the Mode Register programming.

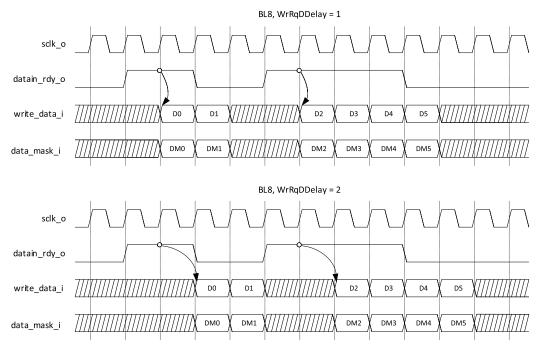

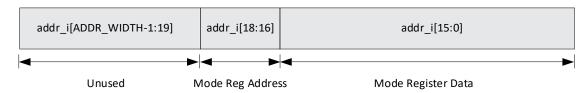

The Lattice DDR3 SDRAM Controller IP Core uses the local address bus, addr\_i, to program these registers. The core accepts a user command, LOAD\_MR, to initiate the programming of mode registers. When LOAD\_MR is applied on the cmd\_i signal, the user logic must provide the information for the targeted mode register and the programming data on the addr\_i signal. When the target mode register is programmed, the memory controller core is also configured to support the new memory setting. Figure 2.14 shows how the local address lines are allocated for the programming of memory registers.

Figure 2.14. User-to-Memory Address Mapping for MR Programming

The lower side of the addr\_i provides the register programming data, starting from bit 0 for LSB. The programming data requires 16 bits of the local address lines. You need three more bits to choose a target register as listed in Table 2.7. All other upper address lines remain unused during LOAD MR command.

Table 2.7. Transmit MAC Statistics Vector

| Mode Register | (addr_i[18:16]) |

|---------------|-----------------|

| MRO           | 3′b000          |

| MR1           | 3′b001          |

| MR2           | 3'b010          |

| MR3           | 3'b011          |

The initialization process uses the mode register initial values selected through the Module/IP Block Wizard during IP configuration. If the user logic does not further program these registers using the LOAD\_MR user command, they remain in the configurations programmed during the initialization process.

Table 2.8 shows the list of available parameters and their initial default values.

Table 2.8. Initialization Default Values for Mode Register Setting

| Mode Register | Register Field                  | Default Value | Description     | Local Address                                       | Module/IP Block<br>Wizard Setting |

|---------------|---------------------------------|---------------|-----------------|-----------------------------------------------------|-----------------------------------|

|               | Burst Length                    | 2'b00         | BL = 8          | addr_i[1:0]                                         | Yes                               |

|               | Read Burst Type                 | 1'b0          | Sequential      | addr_i[3]                                           | Yes                               |

|               | CAS Latency                     | 3'b000        | CL = 5          | addr_i[6:4], addr_i[2]                              | Yes                               |

|               | Mode                            | 1'b0          | Normal          | addr_i[7]                                           | No                                |

| MR0           | DLL Reset                       | 1'b1          | DLL Reset = Yes | addr_i[8]                                           | No                                |

|               | WR Recovery                     | 3'b010        | 6               | addr_i[11:9]                                        | Yes                               |

|               | DLL Control for<br>Precharge PD | 1'b1          | Fast            | addr_i[12]                                          | Yes                               |

|               | All Others                      | 0             | _               | addr_i[ROW_WIDTH-1:13]                              | No                                |

|               | DLL Enable                      | 1'b0          | DLL Enable      | addr_i[0]                                           | No                                |

|               | ODI Control                     | 2'b00         | RZQ/6           | addr_i[5],addr_i[1]                                 | Yes                               |

|               | RTT_Nom                         | 3'b001        | RZQ/4           | addr_i[9],addr_i[6],addr_i[2]                       | Yes                               |

|               | Additive Latency                | 2'b00         | Disabled        | addr_i[4:3]                                         | No                                |

| MR1           | Write Level<br>Enable           | 1'b0          | Disabled        | addr_i[7]                                           | No                                |

|               | TDQS Enable                     | 1'b0          | Disabled        | addr_i[11]                                          | No                                |

|               | Qoff                            | 1'b0          | Enable          | addr_i[12]                                          | No                                |

|               | All Others                      | 0             | _               | addr_i[ROW_WIDTH-1:13]                              | No                                |

|               | CAS Write<br>Latency            | 3'b000        | 5               | addr[5:3]                                           | Yes                               |

| MR2           | Rtt_WR                          | 2'b01         | RZQ/4           | addr_i[10:9]                                        | Yes                               |

| All Others    |                                 | 0             | _               | addr_i[ROW_WIDTH-1:11],<br>addr_i[8:6], addr_i[2:0] | No                                |

| MR3           | All                             | 0             | _               | addr_i[ROW_WIDTH-1:0]                               | No                                |

FPGA-IPUG-02086-2.2

#### 2.5.9. REFRESH Support

Since DDR3 memories have at least an 8-deep Auto Refresh command queue as per JEDEC specification, Lattice's DDR3 memory controller core supports up to eight Auto Refresh commands in one burst. The core has an internal auto refresh generator that sends out a set of consecutive Auto Refresh commands to the memory at once when it reaches the time period of the refresh intervals (*TREFI* attribute) times the *Auto Refresh Burst Count* attribute as selected in the Module/IP Block Wizard.

It is recommended that the maximum number be used if the DDR3 interface throughput is a major concern of the system. If it is set to 8, for example, the core sends a set of eight consecutive Auto Refresh commands to the memory at once when it reaches the time period of the eight refresh intervals (*TREFI* × 8). Bursting refresh cycles increases the DDR3 bus throughput because it helps keep core intervention to a minimum. When a refresh burst is used, the controller issues a Precharge command only for the first Refresh command, and the subsequent Refresh commands of the burst are issued without the associated Precharge commands. This is to improves the DDR3 throughput. The TREFI is internally compensated with a minor margin (2 to 4 SCLK cycles, depending on DDR clock frequency) to ensure that, cumulatively, it never exceed 8 × TREFI maximum allowable refresh period.

Alternatively, you enable the External Auto Refresh Port, which adds an input signal ext\_auto\_ref and an output signal ext\_auto\_ref\_ack to the core. In this case the internal auto refresh generator is disabled, and the core sends out a burst of refresh commands, as directed by Auto refresh burst count, every time the ext\_auto\_ref is asserted. The output signal ext\_auto\_ref ack indicates the completion of the refresh burst.

In an application where explicit memory refresh is not necessary, you enable the External Auto Refresh Port and keep the ext\_auto\_ref signal deasserted.

## **IP Parameter Description**

Table 3.6 shows the configurable attributes of the DDR3 SDRAM Controller IP Core along with the description for each attribute. You can configure the attributes through the IP Catalog's Module/IP Block Wizard of the Lattice Radiant software. The attributes are arranged into tabs, and related attributes are grouped together. The three tabs are as

#### General Tab