# **MIPI DSI/CSI-2 to OpenLDI LVDS Interface Bridge**

## **Reference Design**

FPGA-RD-02060-1.3

December 2025

## Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. **LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS.** LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Inclusive Language

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language [FAQ 6878](#) for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# Contents

|                                          |    |

|------------------------------------------|----|

| Contents.....                            | 3  |

| Acronyms in This Document .....          | 6  |

| 1. Introduction .....                    | 7  |

| 1.1. Supported Devices and IP.....       | 7  |

| 1.2. Features.....                       | 7  |

| 1.3. Block Diagram.....                  | 7  |

| 1.4. RX and TX Permutations.....         | 8  |

| 2. Parameters and Port List .....        | 10 |

| 2.1. Synthesis Directives.....           | 10 |

| 2.2. Simulation Directives.....          | 12 |

| 2.3. Top-Level I/O .....                 | 13 |

| 3. Design and Module Description .....   | 15 |

| 3.1. rx_dphy.....                        | 15 |

| 3.2. byte2pixel.....                     | 16 |

| 3.3. rgb2rgb .....                       | 18 |

| 3.3.1. Sync Signal Generation.....       | 18 |

| 3.3.2. Active Data Trimming .....        | 19 |

| 3.4. raw2rgb .....                       | 20 |

| 3.4.1. RGB Data Creation.....            | 20 |

| 3.4.2. Sync Signal Generation.....       | 21 |

| 3.4.3. Active Data Trimming .....        | 21 |

| 3.5. tx_lvds .....                       | 21 |

| 3.6. int_gpll.....                       | 24 |

| 3.7. i2c_slave .....                     | 26 |

| 4. Design and File Modification .....    | 30 |

| 4.1. Top Level RTL.....                  | 30 |

| 4.2. RX D-PHY IP .....                   | 30 |

| 5. Design Simulation .....               | 31 |

| 6. Design Package and Project Setup..... | 35 |

| 7. Resource Utilization.....             | 37 |

| References .....                         | 38 |

| Technical Support Assistance .....       | 39 |

| Revision History .....                   | 40 |

## Figures

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| Figure 1.1. DSI/CSI-2 to OpenLDI LVDS Interface Bridge Block Diagram ..... | 8  |

| Figure 1.2. Bandwidth and Clock Frequency Calculator .....                 | 9  |

| Figure 3.1. rx_dphy IP Creation in Clarity Designer .....                  | 15 |

| Figure 3.2. byte2pixel IP Creation in Clarity Designer.....                | 16 |

| Figure 3.3. Interface Timing Diagram for DSI.....                          | 17 |

| Figure 3.4. Global Output Timing Diagram for DSI .....                     | 17 |

| Figure 3.5. Interface Timing Diagram for CSI-2.....                        | 18 |

| Figure 3.6. Global Output Timing Diagram for CSI-2 .....                   | 18 |

| Figure 3.7. HSYNC Generation .....                                         | 19 |

| Figure 3.8. HSYNC Masked by LV .....                                       | 19 |

| Figure 3.9. Bayer Pattern of RAW Data.....                                 | 20 |

| Figure 3.10. RGB Data Creation from RAW Data .....                         | 20 |

| Figure 3.11. tx_dphy IP Creation in Clarity Designer .....                 | 21 |

| Figure 3.12. Single Channel LVDS Output of RGB888 .....                    | 22 |

| Figure 3.13. Dual Channel LVDS Output of RGB888 .....                      | 23 |

| Figure 3.14. Single Channel LVDS Output of RGB666 .....                    | 23 |

| Figure 3.15. Dual Channel LVDS Output of RGB666 .....                      | 24 |

| Figure 3.16. GPLL IP Creation.....                                         | 25 |

| Figure 3.17. I <sup>2</sup> C IP Creation #1 .....                         | 27 |

| Figure 3.18. I <sup>2</sup> C IP Creation #2 .....                         | 28 |

| Figure 3.19. I <sup>2</sup> C IP Creation #3 .....                         | 28 |

| Figure 5.1. Script File Modification .....                                 | 31 |

| Figure 5.2. Global Timing of DSI RGB888 without Vertical Trimming.....     | 32 |

| Figure 5.3. Global Timing of CSI-2 RGB888 .....                            | 33 |

| Figure 5.4. Global Timing of CSI-2 RAW10 without Vertical Trimming.....    | 33 |

| Figure 5.5. Global Timing of CSI-2 RAW10 with Vertical Trimming .....      | 34 |

| Figure 6.1. Directory Structure .....                                      | 35 |

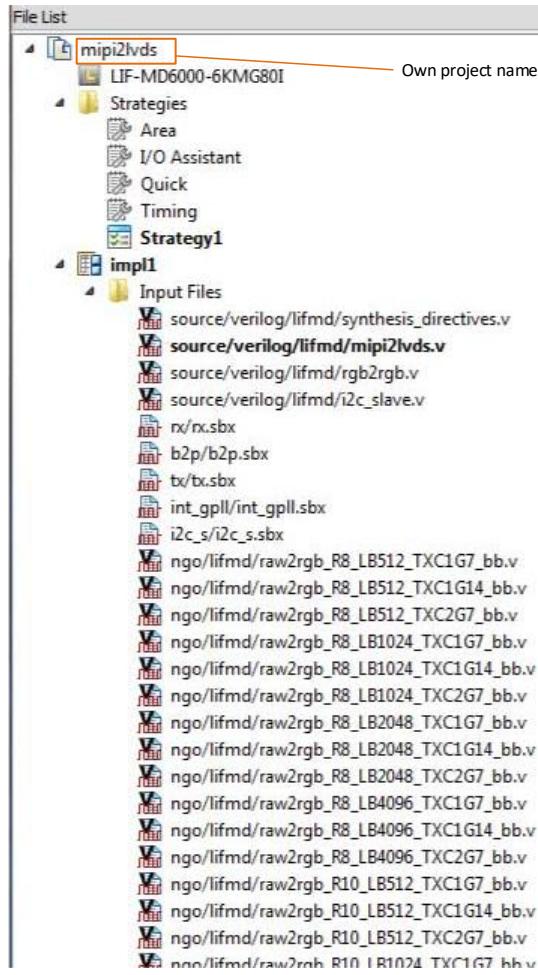

| Figure 6.2. Project Files.....                                             | 36 |

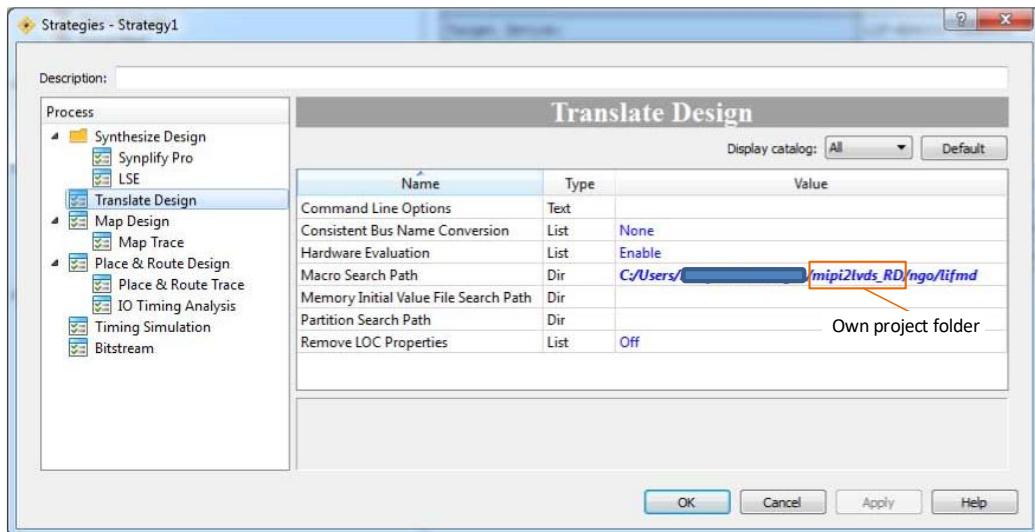

| Figure 6.3. Path Setting for .ngo Files .....                              | 36 |

## Tables

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| Table 1.1. Supported Devices and IP .....                                 | 7  |

| Table 1.2. RX and TX Permutation .....                                    | 8  |

| Table 2.1. Synthesis Directives.....                                      | 10 |

| Table 2.2. Simulation Directives .....                                    | 12 |

| Table 2.3. DSI/CSI-2 to OpenLDI LVDS Interface Bridge Top Level I/O ..... | 13 |

| Table 3.1. I <sup>2</sup> C Slave Register Map .....                      | 29 |

| Table 7.1. Resource Utilization Examples .....                            | 37 |

## Acronyms in This Document

A list of acronyms used in this document.

| Acronym | Definition                          |

|---------|-------------------------------------|

| AP      | Application Processor               |

| DSI     | Display Serial Interface            |

| CSI-2   | Camera Serial Interface 2           |

| DDR     | Double Data Rate                    |

| FV      | Frame Valid                         |

| GPLL    | General Purpose PLL                 |

| HBP     | Horizontal Back Porch               |

| HFP     | Horizontal Front Porch              |

| HS      | High Speed                          |

| LP      | Low Power                           |

| LV      | Line Valid                          |

| LVDS    | Low Voltage Differential Signal     |

| MIPI    | Mobile Industry Processor Interface |

| OpenLDI | Open LVDS Display Interface         |

| PLL     | Phase Locked Loop                   |

| RD      | Reference Design                    |

| RX      | Receiver                            |

| TX      | Transmitter                         |

| VBP     | Vertical Back Porch                 |

| VFP     | Vertical Front Porch                |

| VCO     | Voltage Controlled Oscillator       |

## 1. Introduction

Mobile Industry Processor Interface (MIPI®) Display Serial Interface (DSI) is one of the most popular display interfaces in the consumer market today. On the other hand, OpenLDI LVDS is still popular in some areas as the main predecessor of display interface. Most image sensors and application processors (AP) in the consumer market use MIPI Camera Serial Interface 2 (CSI-2) as a video signal interface. In some cases, the interface and/or format conversion is useful to connect devices which cannot connect directly.

The Lattice Semiconductor MIPI DSI/CSI-2 to OpenLDI LVDS Interface Bridge reference design for CrossLink™ devices takes DSI or CSI-2 MIPI data and converts them to OpenLDI format on LVDS. The MIPI RX module can also be realized by a MIPI hard macro-IP or soft macro utilizing general DDR modules (D-PHY Soft IP) while LVDS TX module is realized by soft macro utilizing general DDR modules.

### 1.1. Supported Devices and IP

This reference design supports the following devices with IP versions shown below.

**Table 1.1. Supported Devices and IP**

| Device Family | Part Number | Compatible IP                                                                                                                                                                            |

|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CrossLink     | LIF-MD6000  | <ul style="list-style-type: none"> <li>• D-PHY Receiver IP version 1.6</li> <li>• Byte-to-Pixel Converter IP version 1.3</li> <li>• LVDS Transmitter Interface IP version 1.2</li> </ul> |

|               | LIA-MD6000  |                                                                                                                                                                                          |

| CrossLinkPlus | LIF-MDF6000 | <ul style="list-style-type: none"> <li>• D-PHY Receiver IP version 1.6</li> <li>• Byte-to-Pixel Converter IP version 1.3</li> <li>• LVDS Transmitter Interface IP version 1.2</li> </ul> |

**Note:** CrossLink refers to both CrossLink and CrossLinkPlus in this document unless noted.

### 1.2. Features

- Single DSI input (RGB888 or RGB666) to single or dual channel LVDS outputs (RGB888 or RGB666)

- Single CSI-2 input (RGB888, RAW8, RAW10, or RAW12) to single or dual channel RGB888 LVDS outputs (RGB888)

- RX channel can have one, two, or four lanes with the bandwidth up to 1.2 Gbps per lane using RX D-PHY Soft IP.

- The bandwidth can be up to 1.5 Gbps per lane when Gear 16 and RX Hard D-PHY IP is used.

- The number of TX data lanes is three (RGB666) or four (RGB888) per TX channel.

- Maximum TX bandwidth is 1.2 Gbps per lane.

- Image cropping option is available in case of CSI-2 input.

- Dynamic parameter setting is possible via I2C in case of CSI-2 input.

### 1.3. Block Diagram

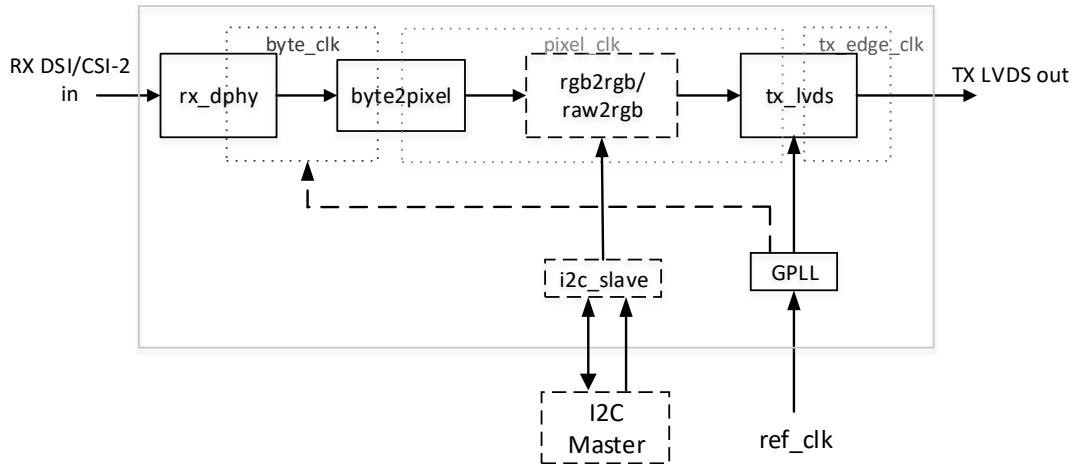

Figure 1.1 shows the block level diagram of the MIPI DSI/CSI-2 to OpenLDI LVDS Interface Bridge reference design with single TX channel.

There exist two main clock domains for main video data path: byte clock and pixel clock. GPLL is required to generate the edge clock of LVDS TX module. Also, it might be used to generate the continuous byte clock when RX D-PHY is in HS\_LP mode. I2C Slave modules enable parameter change on the fly if necessary for CSI-2 RX.

Figure 1.1. DSI/CSI-2 to OpenLDI LVDS Interface Bridge Block Diagram

## 1.4. RX and TX Permutations

Table 1.2 shows the available permutations of RX and TX configurations. Some permutations exist only for DSI and some only for CSI-2 due to the limitations of the Byte-to-Pixel IP used in this reference design. Note that TX Data Type is the same as the RX Data Type in the case of DSI. The TX Data Type is always RGB888 in the case of CSI-2.

In the case of dual channel TX with RGB888, ten LVDS output pairs are required. This means that the two I/O Banks must be set to 2.5 V since Bank 1 has only 14 I/O and Bank 2 has only 16 I/O (LIF-MD6000-6KMG80I). On the other hand, one of these two Banks must be set to 1.2 V when using Soft D-PHY on MIPI RX channel. To avoid this, Hard D-PHY IP has to be used on RX channel.

Table 1.2. RX and TX Permutation

| D-PHY Type | Data Type                     | Number of RX Lanes | RX Gear | Number of Pixels/ Pixel Clock | TX Gear | Number of TX Channel |

|------------|-------------------------------|--------------------|---------|-------------------------------|---------|----------------------|

| DSI        | RGB888 or RGB666              | 1                  | 8       | 1                             | 7       | 1                    |

|            |                               |                    | 16      | 1                             | 7       | 1                    |

|            |                               | 2                  | 8       | 1                             | 7       | 1                    |

|            |                               |                    | 16      | 1                             | 7       | 1                    |

|            |                               |                    |         | 2                             | 7       | 2                    |

|            |                               |                    |         |                               | 14      | 1                    |

|            |                               | 4                  | 8       | 1                             | 7       | 1                    |

|            |                               |                    |         | 2                             | 7       | 2                    |

|            |                               |                    | 16      | 14                            | 1       |                      |

|            |                               |                    |         | 7                             | 2       |                      |

|            |                               |                    |         | 14                            | 1       |                      |

|            |                               |                    |         | 4                             | 14      | 2                    |

|            |                               |                    |         |                               | 7       | 1                    |

|            |                               |                    |         |                               | 14      | 1                    |

| CSI-2      | RGB888, RAW8, RAW10, or RAW12 | 1                  | 8       | 1                             | 7       | 1                    |

|            |                               |                    | 16      | 1                             | 7       | 1                    |

|            |                               |                    |         | 2                             | 7       | 2                    |

|            |                               |                    |         |                               | 14      | 1                    |

|            |                               | 2                  | 8       | 1                             | 7       | 1                    |

|            |                               |                    |         | 2                             | 7       | 2                    |

|            |                               |                    | 16      | 14                            | 1       |                      |

|            |                               |                    |         | 7                             | 2       |                      |

|            |                               |                    |         | 14                            | 1       |                      |

|            |                               |                    |         | 7                             | 1       |                      |

|            |                               |                    |         | 2                             | 2       |                      |

|            |                               |                    |         |                               | 14      | 1                    |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at [www.latticesemi.com/legal](http://www.latticesemi.com/legal). All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| D-PHY Type | Data Type | Number of RX Lanes | RX Gear | Number of Pixels/<br>Pixel Clock | TX Gear | Number of TX Channel |

|------------|-----------|--------------------|---------|----------------------------------|---------|----------------------|

|            |           | 4                  | 8       | 1                                | 7       | 1                    |

|            |           |                    |         | 2                                | 7       | 2                    |

|            |           |                    |         |                                  | 14      | 1                    |

|            |           |                    | 16      | 2                                | 7       | 2                    |

|            |           |                    |         |                                  | 14      | 1                    |

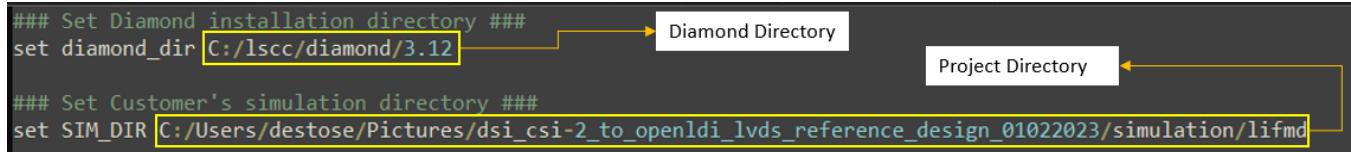

The Microsoft Excel sheet (mipi2lvds\_clock.xlsx) is provided to get the byte clock, TX edge clock, and others from RX bandwidth, in addition to other information. This sheet is useful in configuring IPs. A sample entry is shown in [Figure 1.2](#). By entering MIPI bandwidth and other information, the Byte clock, LVDS bandwidth, and TX ECLK are automatically calculated. The results can be used to configure TX LVDS IP and GPL.

| DSI/CSI-2 to OpenLDI/FPD-Link/LVDS Interface Bridge RD Frequency Calculator        |        |      |

|------------------------------------------------------------------------------------|--------|------|

| RX Interface                                                                       | CSI-2  |      |

| RX Data Type                                                                       | RGB888 |      |

| RX Line Rate                                                                       | 600    | Mbps |

| RX DPHY Clock Frequency                                                            | 300    | MHz  |

| Number of RX Lanes                                                                 | 4      |      |

| RX Gear                                                                            | 8      |      |

| TX Data Type                                                                       | RGB888 |      |

| Byte Clock Frequency                                                               | 75     | MHz  |

| Number of TX Channels                                                              | 1      |      |

| TX Gear                                                                            | 7      |      |

| Pixel Clock Frequency                                                              | 100    | MHz  |

| TX Line Rate                                                                       | 700    | Mbps |

| TX LVDS ECLK Frequency                                                             | 350    | MHz  |

| TX LVDS Output Clock Frequency                                                     | 100    | MHz  |

| .8 TX LVDS ECLK comes from CLKOP of PLL.                                           |        |      |

| .9 Continuous Byte Clock comes from PLL (CLKOS) or from I/O in case of HS_LP mode. |        |      |

**Figure 1.2. Bandwidth and Clock Frequency Calculator**

## 2. Parameters and Port List

There are two directive files for this reference design:

- synthesis\_directives.v – used for design compilation by Lattice Diamond® and for simulation.

- simulation\_directives.v – used for simulation.

The user can modify these directives according to the user's own configuration. The settings in these files must match RX D-PHY IP, Byte-to-Pixel IP, and TX LVDS IP settings created by Clarity Designer.

### 2.1. Synthesis Directives

Table 2.1 shows the synthesis directives that affect this reference design. These are used for both synthesis and simulation. As shown in Table 2.1 and Table 2.2, some parameter selections are restricted by other parameter settings.

**Table 2.1. Synthesis Directives**

| Category                              | Directive           | Remarks                                                                                                                                                                                                          |

|---------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External reference clock <sup>1</sup> | EXT_REF_CLK         | Enable this when the reference clock is fed from a pin.                                                                                                                                                          |

| RX D-PHY Type                         | RX_TYPE_DSI         | Define the D-PHY type on the RX channel. Only one of these directives must be defined.                                                                                                                           |

|                                       | RX_TYPE_CSI2        |                                                                                                                                                                                                                  |

| RX Data Type                          | RX_RGB888           | Define the data type on the RX channel. Only one of these directives must be defined. In the case of DSI, only RGB888 and RGB666 are allowed. In case of CSI-2, only RGB888, RAW8, RAW10, and RAW12 are allowed. |

|                                       | RX_RGB666           |                                                                                                                                                                                                                  |

|                                       | RX_RAW8             |                                                                                                                                                                                                                  |

|                                       | RX_RAW10            |                                                                                                                                                                                                                  |

|                                       | RX_RAW12            |                                                                                                                                                                                                                  |

| Number of RX Channel Lanes            | NUM_RX_LANE_1       | Number of lanes in the RX channel. Only one of these three directives must be defined.                                                                                                                           |

|                                       | NUM_RX_LANE_2       |                                                                                                                                                                                                                  |

|                                       | NUM_RX_LANE_4       |                                                                                                                                                                                                                  |

| RX D-PHY Clock Gear                   | RX_GEAR_8           | Number of RX clock gears on the RX channel. Only one of these directives must be defined.                                                                                                                        |

|                                       | RX_GEAR_16          |                                                                                                                                                                                                                  |

| RX Hard D-PHY                         | RX_DPHY_HARD        | Enable this to use Hard D-PHY. If undefined, Soft D-PHY is used.                                                                                                                                                 |

| RX D-PHY Clock Mode <sup>2</sup>      | RX_CLK_MODE_HS_ONLY | RX D-PHY clock mode. Only one of these two directives must be defined.                                                                                                                                           |

|                                       | RX_CLK_MODE_HS_LP   |                                                                                                                                                                                                                  |

| Hard D-PHY Word Alignment             | WORD_ALIGN          | Enable word aligner in RX Hard D-PHY IP. Ignored when Hard D-PHY is not used.                                                                                                                                    |

| Line Buffer Depth                     | LB_DEPTH_512        | Define the depth of the line buffer in case the RX Data Type is RAW8, RAW10, or RAW12. This depth must be equal or greater than the active pixel count per line, irrespective of the data type.                  |

|                                       | LB_DEPTH_1024       |                                                                                                                                                                                                                  |

|                                       | LB_DEPTH_2048       |                                                                                                                                                                                                                  |

|                                       | LB_DEPTH_4096       |                                                                                                                                                                                                                  |

| Sync Signal Polarity                  | SYNC_POLARITY_POS   | Define sync signal (VSYNC, HSYNC) polarity. Only one of these two directives must be defined.                                                                                                                    |

|                                       | SYNC_POLARITY_NEG   |                                                                                                                                                                                                                  |

| Data Enable Polarity                  | DE_POLARITY_POS     | Define data enable (DE) polarity. Only one of these two directives must be defined.                                                                                                                              |

|                                       | DE_POLARITY_NEG     |                                                                                                                                                                                                                  |

| TX Data Type <sup>3</sup>             | TX_RGB888           | Define the data type on TX channel. Only one of these two directives must be defined. RGB666 must be defined in the case of RX_RGB666. RGB888 must be defined in all other cases.                                |

|                                       | TX_RGB666           |                                                                                                                                                                                                                  |

| Number of TX Channels                 | NUM_TX_CH_1         | Number of channels in TX. Only one of these two directives must be defined. Two channel is only allowed for DSI input.                                                                                           |

|                                       | NUM_TX_CH_2         |                                                                                                                                                                                                                  |

| TX LVDS Gear                          | TX_GEAR_7           | Number of TX clock gears on RX channel. Only one of these directives must be defined.                                                                                                                            |

|                                       | TX_GEAR_14          |                                                                                                                                                                                                                  |

| Category                                          | Directive                 | Remarks                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter set by I <sup>2</sup> C                 | USE_I2C                   | Define this to use I <sup>2</sup> C I/F to set the parameters on the fly. This is applicable to CSI-2 input only.                                                                                                                                                                                                                      |

| I <sup>2</sup> C Slave Address (MSB) <sup>4</sup> | I2C_SLAVE_ADR_MSB {value} | Define MSB 5bits of I <sup>2</sup> C Slave Address. Value must be 5'h00 – 5'h1F. Applicable only when USE_I2C is defined. This value overwrites the value set in Clarity when IP is created.                                                                                                                                           |

| Software Reset Register <sup>5</sup>              | SW_RST_N {value}          | Default value of the software reset register of I <sup>2</sup> C Slave module. Value must be 1'b0 or 1'b1 Applicable only when USE_I2C is defined. Active low.                                                                                                                                                                         |

| Shift Register Delay <sup>6</sup>                 | SR_DELAY {value}          | Define shift register delay. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 8'd2 – 8'd255. Applicable only to CSI-2 input with RGB888.                                                                          |

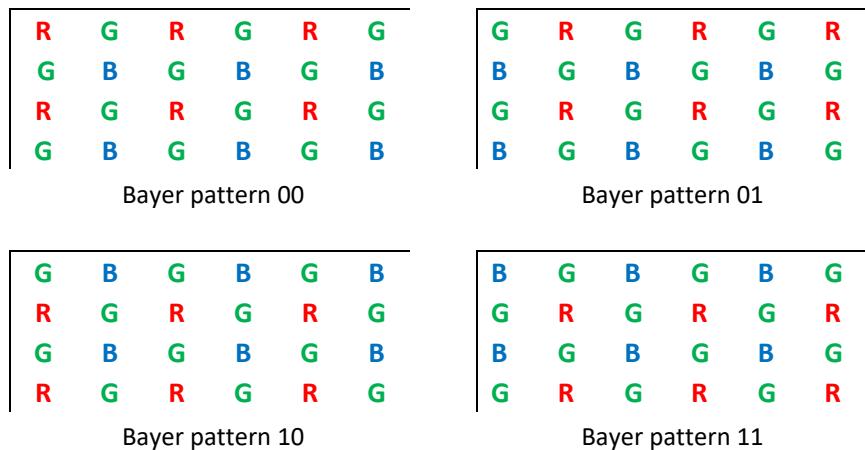

| Bayer Pattern <sup>7</sup>                        | BAYER_PATTERN {value}     | Define the Bayer pattern. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 2'b00 – 2'b11. Applicable only to CSI-2 input with RAW8/RAW10/RAW12.                                                                   |

| Horizontal Front Porch <sup>8</sup>               | HFP {value}               | Define the horizontal front porch. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 8'd1 – 8'd255. Applicable only to CSI-2 input.                                                                                |

| HSYNC Pulse Length <sup>8</sup>                   | HS_LENGTH {value}         | Define HSYNC pulse length. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 8'd1 – 8'd255. Applicable only to CSI-2 input.                                                                                        |

| Vertical Front Porch <sup>9</sup>                 | VFP {value}               | Define the vertical front porch. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 6'd1 – 6'd63. Applicable only to CSI-2 input.                                                                                   |

| VSYNC Pulse Length <sup>9</sup>                   | VS_LENGTH {value}         | Define VSYNC pulse length. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 6'd1 – 6'd63. Applicable only to CSI-2 input.                                                                                         |

| Left Pixel Trimming <sup>10</sup>                 | LEFT_TRIM {value}         | Define the number of pixels to be trimmed before TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 6'd0 – 6'd63. Applicable only to CSI-2 input.                                                               |

| Horizontal Active Pixels on TX <sup>10</sup>      | H_TX_PEL {value}          | Define the number of active pixels to send on TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 12'd1 – 12'd4095. The value must be even in case of TX_GEAR_14 or NUM_TX_CH_2. Applicable only to CSI-2 input. |

| Top Line Trimming <sup>11</sup>                   | TOP_TRIM {value}          | Define the number of lines to be trimmed before TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 6'd0 – 6'd63. Applicable only to CSI-2 input.                                                                |

| Vertical Active Lines on TX <sup>11</sup>         | V_TX_LINE {value}         | Define the number of active lines to be sent on TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 12'd1 – 12'd4095. Applicable only to CSI-2 input.                                                            |

**Notes:**

1. The external clock is required in most cases since the clock ratio between RX side and TX side is usually not simple.

2. HS\_LP mode means non-continuous clock mode and HS\_ONLY means continuous clock mode. HS\_LP mode works only if RX byte clock can be generated internally or directly fed from I/O pin.

3. TX data type must match RX data type in case of RGB input. RGB888 output is used for all RAW input.

4. LSB two bits of I2C slave address is automatically set when I2C IP is created by Clarity.

5. Logical OR between this register and system reset (reset\_n\_i) is used to reset modules other than I2C slave module.

6. Refer to the [Sync Signal Generation](#) section for details.

7. Refer to the [RGB Data Creation](#) section for pattern details.

8. (HFP + HS\_LENGTH) must be less than the horizontal blanking period after the byte-to-pixel conversion. It is the user's responsibility to manage this. Small values are recommended if the user has no idea about the length of the blanking period.

9. (VFP + VS\_LENGTH) must be less than the vertical blanking period after the byte-to-pixel conversion. It is the user's responsibility to manage this. Small values are recommended if the user has no idea about the length of the blanking period.

10. (LEFT\_TRIM + H\_TX\_PEL) cannot exceed the horizontal active pixel count of the incoming RX data. It is the user's responsibility to manage this.

11. (TOP\_TRIM + V\_TX\_LINE) cannot exceed the vertical active line count of the incoming RX data. It is the user's responsibility to manage this.

## 2.2. Simulation Directives

[Table 2.2](#) shows the simulation directives for this reference design.

**Table 2.2. Simulation Directives**

| Category                                          | Directive                     | Remarks                                                                                                                                                              |

|---------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Simulation setup                                  | SIM                           | Define to select the right behavioral model in simulation.                                                                                                           |

| Reference clock period                            | REF_CLK {value}               | Reference clock period in ps                                                                                                                                         |

| RX D-PHY clock period                             | DPHY_CLK {value}              | RX DPHY clock period in ps                                                                                                                                           |

| Number of frames to run                           | NUM_FRAMES {value}            | Number of video frames fed by testbench                                                                                                                              |

| Number of active lines                            | NUM_LINES {value}             | Number of active video lines per frame                                                                                                                               |

| Number of active pixels                           | NUM_PIXELS {value}            | Number of active video pixels per line                                                                                                                               |

| HSYNC period in DSI                               | DSI_HSA_PAYLOAD {value}       | HSYNC active count in the unit of payload byte. Applicable to DSI RX.                                                                                                |

| Blanking period in DSI                            | DSI_BLLP_PAYLOAD {value}      | Blanking period in the unit of payload byte. Used in HS_ONLY mode. Applicable to DSI RX.                                                                             |

| Horizontal Back Porch in DSI <sup>1</sup>         | DSI_HBP_PAYLOAD {value}       | Horizontal Back Porch or Low Power period in the unit of payload byte count. Used in HS_LP mode or non-burst sync pulse in HS_ONLY mode. Applicable to DSI RX.       |

| Horizontal Front Porch in DSI <sup>1</sup>        | DSI_HFP_PAYLOAD {value}       | Horizontal Front Porch or Low Power period in the unit of payload byte count. Used in HS_LP mode or non-burst sync pulse in HS_ONLY mode. Applicable to DSI RX.      |

| VSYNC period in DSI                               | DSI_VSA_LINES {value}         | Number of VSYNC active lines. Applicable to DSI RX.                                                                                                                  |

| Vertical Back Porch in DSI                        | DSI_VBP_LINES {value}         | Number of Vertical Back Porch lines. Applicable to DSI RX.                                                                                                           |

| Vertical Front Porch in DSI                       | DSI_VFP_LINES {value}         | Number of Vertical Front Porch lines. Applicable to DSI RX.                                                                                                          |

| EOTP packet on/off in DSI                         | DSI_ETOP_ENABLE {value}       | Enable/Disable EOTP (End of Transmission Packet). Applicable to DSI RX. Value must be 1 (enable) or 0 (disable).                                                     |

| Blanking period in DSI                            | DSI_LPS_BLLP_DURATION {value} | Blanking (LP) period in ps. Used in HS_LP mode. Applicable to DSI RX.                                                                                                |

| Horizontal Back Porch period in DSI <sup>1</sup>  | DSI_LPS_HBP_DURATION {value}  | Horizontal Back Porch period (using LP mode) in ps. Used for non-burst sync events and burst mode in HS_LP mode. Applicable to DSI RX.                               |

| Horizontal Front Porch period in DSI <sup>1</sup> | DSI_LPS_HFP_DURATION {value}  | Horizontal Front Porch period (using LP mode) in ps. Used for non-burst sync events and burst mode in HS_LP mode. Applicable to DSI RX.                              |

| Initial delay on RX channel                       | READY_DURATION {value}        | Initial delay to activate RX channel in ps.                                                                                                                          |

| Line Gap period in CSI-2                          | DPHY_LPS_GAP {value}          | Line Gap time in ps. Applicable to CSI-2 RX.                                                                                                                         |

| Frame Gap period                                  | FRAME_LPM_DELAY {value}       | Frame Gap time in ps. This is LP period between Frame End and Frame Start in case of CSI-2 and LP period after VFP period end and before VSYNC start in case of DSI. |

| Category                                    | Directive                 | Remarks                                                                                                                                                                           |

|---------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software Reset Register <sup>2</sup>        | I2C_SW_RST_N {value}      | Write value to the software reset register of I <sup>2</sup> C Slave module. Value must be 1'b0 or 1'b1. Applicable only when USE_I2C is defined. Active low.                     |

| Shift Register Delay <sup>3</sup>           | I2C_SR_DELAY {value}      | Write value to the shift register delay register of I <sup>2</sup> C Slave. The value must be 8'd2 – 5'd255. Applicable only to CSI-2 input with RGB888.                          |

| Bayer Pattern <sup>4</sup>                  | I2C_BAYER_PATTERN {value} | Write value to the Bayer pattern register of I <sup>2</sup> C Slave. Value must be 2'b00 – 2'b11. Applicable only to CSI-2 input with RAW8/RAW10/RAW12.                           |

| Horizontal Front Porch <sup>5</sup>         | I2C_HFP {value}           | Write value to the horizontal front porch register of I <sup>2</sup> C Slave. Value must be 8'd1 – 8'd255. Applicable only to CSI-2 input.                                        |

| HSYNC Pulse Length <sup>5</sup>             | I2C_HS_LENGTH {value}     | Write value to HSYNC pulse length register of I <sup>2</sup> C Slave. Value must be 8'd1 – 8'd255. Applicable only to CSI-2 input.                                                |

| Vertical Front Porch <sup>6</sup>           | I2C_VFP {value}           | Write value to the vertical front porch register of I <sup>2</sup> C Slave. Value must be 6'd1 – 6'd63. Applicable only to CSI-2 input.                                           |

| VSYNC Pulse Length <sup>6</sup>             | I2C_VS_LENGTH {value}     | Write value to VSYNC pulse length register of I <sup>2</sup> C Slave. Value must be 6'd1 – 6'd63. Applicable only to CSI-2 input.                                                 |

| Left Pixel Trimming <sup>7</sup>            | I2C_LEFT_TRIM {value}     | Write Value to the pixel trim register of I <sup>2</sup> C Slave. Value must be 6'd0 – 6'd63. Applicable only to CSI-2 input.                                                     |

| Horizontal Active Pixels on TX <sup>7</sup> | I2C_H_TX_PEL {value}      | Write value to the active pixel register of I <sup>2</sup> C Slave. Value must be 13'd1 – 13'd8191. The value must be even in case of TX_GEAR_14. Applicable only to CSI-2 input. |

| Top Line Trimming <sup>8</sup>              | I2C_TOP_TRIM {value}      | Write value to the line trim register of I <sup>2</sup> C Slave. Value must be 6'd0 – 6'd63. Applicable only to CSI-2 input.                                                      |

| Vertical Active Lines on TX <sup>8</sup>    | I2C_V_TX_LINE {value}     | Write value to the active line register of I <sup>2</sup> C. Value must be 12'd1 – 12'd4095. Applicable only to CSI-2 input.                                                      |

**Notes:**

1. Refer to MIPI® Alliance Specification for Display Serial Interface (DSI) Version 1.1 for details.

2. Logical OR between this register and system reset (reset\_n\_i) is used to reset modules other than I<sup>2</sup>C slave module.

3. Refer to the [Sync Signal Generation](#) section for details.

4. Refer to the [RGB Data Creation](#) section for pattern details.

5. (I2C\_HFP + I2C\_HS\_LENGTH) must be less than the horizontal blanking period after the byte-to-pixel conversion. It is the user's responsibility to manage this. Small values are recommended if the user has no idea about the length of the blanking period.

6. (I2C\_VFP + I2C\_VS\_LENGTH) must be less than the vertical blanking period after the byte-to-pixel conversion. It is the user's responsibility to manage this. Small values are recommended if the user has no idea about the length of the blanking period.

7. (I2C\_LEFT\_TRIM + I2C\_H\_TX\_PEL) cannot exceed the horizontal active pixel count of the incoming RX data. It is the user's responsibility to manage this.

8. (I2C\_TOP\_TRIM + I2C\_V\_TX\_LINE) cannot exceed the vertical active line count of the incoming RX data. It is the user's responsibility to manage this.

## 2.3. Top-Level I/O

Table 2.3 shows the top level I/O of this reference design. Actual I/O depends on the customer's channel and lane configurations. All necessary I/O ports are automatically declared by compiler directives.

**Table 2.3. DSI/CSI-2 to OpenLDI LVDS Interface Bridge Top Level I/O**

| Port Name                                        | Direction | Description                                                                                                                                                           |

|--------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Clocks and Resets</b>                         |           |                                                                                                                                                                       |

| ref_clk_i                                        | I         | Input reference clock. Used to feed a clock to TX D-PHY PLL directly or indirectly. This port is declared only when EXT_REF_CLK is defined in synthesis_directives.v. |

| reset_n_i                                        | I         | Asynchronous active low system reset                                                                                                                                  |

| <b>Control Interface (optional for CSI-2 RX)</b> |           |                                                                                                                                                                       |

| scl                                              | I/O       | I <sup>2</sup> C clock                                                                                                                                                |

| Port Name                     | Direction | Description                                                                                                                         |

|-------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| sda                           | I/O       | I <sup>2</sup> C data                                                                                                               |

| <b>DSI/CSI-2 RX Interface</b> |           |                                                                                                                                     |

| rx_clk_p_i                    | I         | Positive differential RX D-PHY input clock                                                                                          |

| rx_clk_n_i                    | I         | Negative differential RX D-PHY input clock                                                                                          |

| rx_d0_p_i                     | I         | Positive differential RX D-PHY input data 0                                                                                         |

| rx_d0_n_i                     | I         | Negative differential RX D-PHY input data 0                                                                                         |

| rx_d1_p_i                     | I         | Positive differential RX D-PHY input data 1 (in case of 2-lane or 4-lane configuration)                                             |

| rx_d1_n_i                     | I         | Negative differential RX D-PHY input data 1 (in case of 2-lane or 4-lane configuration)                                             |

| rx_d2_p_i                     | I         | Positive differential RX D-PHY input data 2 (in case of 4-lane configuration)                                                       |

| rx_d2_n_i                     | I         | Negative differential RX D-PHY input data 2 (in case of 4-lane configuration)                                                       |

| rx_d3_p_i                     | I         | Positive differential RX D-PHY input data 3 (in case of 4-lane configuration)                                                       |

| rx_d3_n_i                     | I         | Negative differential RX D-PHY input data 3 (in case of 4-lane configuration)                                                       |

| <b>LVDS TX Interface</b>      |           |                                                                                                                                     |

| tx0_clk_p_o                   | O         | Positive differential TX LVDS output clock                                                                                          |

| tx0_clk_n_o                   | O         | Negative differential TX LVDS output clock                                                                                          |

| tx0_d0_p_o                    | O         | Positive differential TX LVDS output data 0                                                                                         |

| tx0_d0_n_o                    | O         | Negative differential TX LVDS output data 0                                                                                         |

| tx0_d1_p_o                    | O         | Positive differential TX LVDS output data 1                                                                                         |

| tx0_d1_n_o                    | O         | Negative differential TX LVDS output data 1                                                                                         |

| tx0_d2_p_o                    | O         | Positive differential TX LVDS output data 2                                                                                         |

| tx0_d2_n_o                    | O         | Negative differential TX LVDS output data 2                                                                                         |

| tx0_d3_p_o                    | O         | Positive differential TX LVDS output data 3 (in case of TX_RGB888)                                                                  |

| tx0_d3_n_o                    | O         | Negative differential TX LVDS output data 3 (in case of TX_RGB888)                                                                  |

| tx1_clk_p_o                   | O         | Positive differential TX LVDS output clock on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                 |

| tx1_clk_n_o                   | O         | Negative differential TX LVDS output clock on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                 |

| tx1_d0_p_o                    | O         | Positive differential TX LVDS output data 0 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                |

| tx1_d0_n_o                    | O         | Negative differential TX LVDS output data 0 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                |

| tx1_d1_p_o                    | O         | Positive differential TX LVDS output data 1 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                |

| tx1_d1_n_o                    | O         | Negative differential TX LVDS output data 1 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                |

| tx1_d2_p_o                    | O         | Positive differential TX LVDS output data 2 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                |

| tx1_d2_n_o                    | O         | Negative differential TX LVDS output data 2 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration)                |

| tx1_d3_p_o                    | O         | Positive differential TX LVDS output data 3 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration with TX_RGB888) |

| tx1_d3_n_o                    | O         | Negative differential TX LVDS output data 3 on 2 <sup>nd</sup> TX channel (in case of dual TX channel configuration with TX_RGB888) |

### 3. Design and Module Description

The top-level design (mipi2lvds.v) consists of the following modules:

- rx\_dphy

- byte2pixel

- rgb2rgb (used only for CSI-2 RGB888)

- raw2rgb (used only for CSI-2 RAW8/RAW10/RAW12)

- tx\_lvds

- int\_gpll

- i2c\_slave (optional for CSI-2)

The top-level design has a reset synchronization logic.

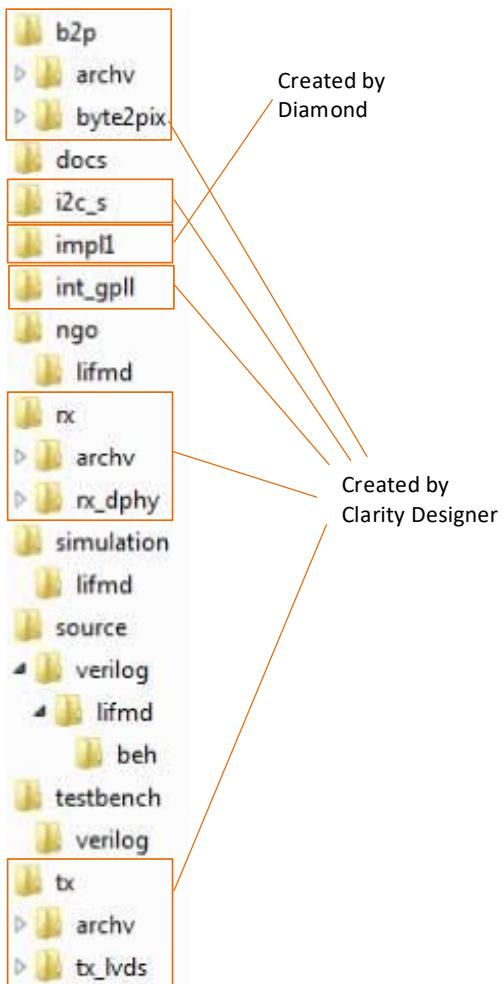

#### 3.1. rx\_dphy

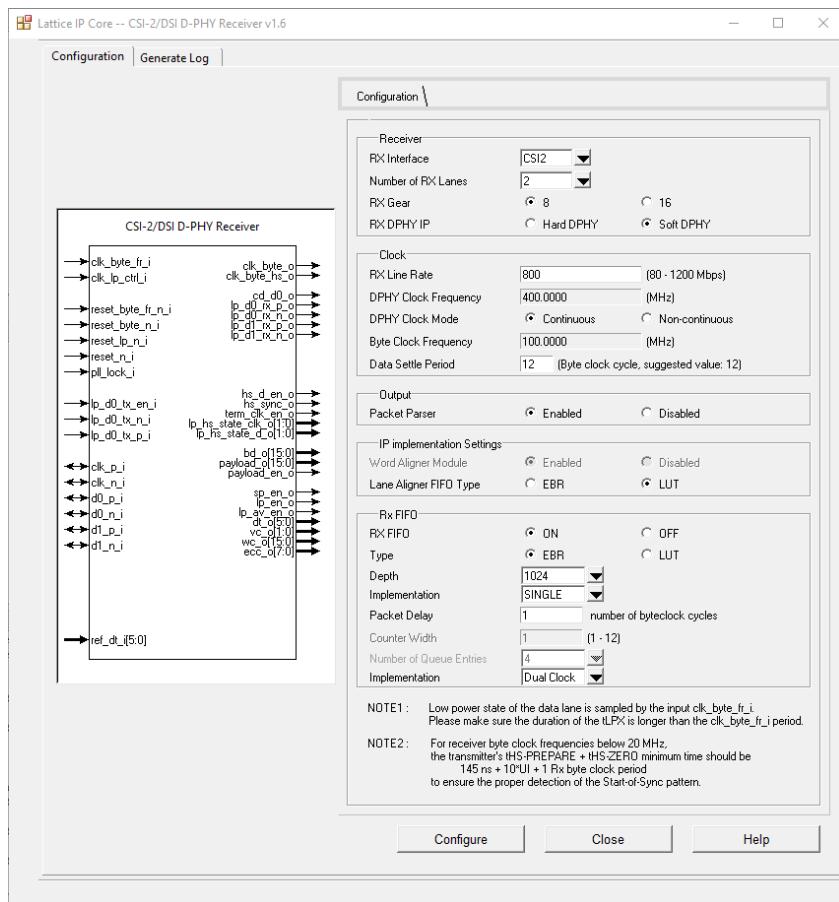

This module must be created for the RX channel according to channel conditions, such as the number of lanes, bandwidth, and others. [Figure 3.1](#) shows an example of IP interface settings in Clarity for the CSI-2/DSI D-PHY Receiver Submodule IP. The user can use the .sbx file (rx/rx.sbx) included in the sample project and reconfigure according to the user's needs. Refer to [CSI-2/DSI D-PHY Receiver Submodule IP User Guide \(FPGA-IPUG-02025\)](#) for details.

**Figure 3.1. rx\_dphy IP Creation in Clarity Designer**

The following provides the guidelines and parameter settings required for this reference design.

- RX Interface – Select DSI or CSI-2.

- Number of RX Lanes – Set according to channel configuration. The value must match NUM\_RX\_LANE\_\* setting.

- RX Gear – Select 8 or 16; 16 is recommended when the RX byte clock speed exceeds 100 MHz with Gear 8.

- RX D-PHY IP – Select Soft D-PHY or Hard D-PHY. Must match with the setting in synthesis\_directives.v.

- RX Line Rate – Set according to channel configuration. 800 or below is recommended for 4 lane configuration.

- D-PHY Clock Mode – Select Continuous or Non-continuous. Must match RX\*\_CLK\_MODE\_\* setting (Continuous = HS\_ONLY, Non-continuous = HS\_LP).

- Packet Parser – Select Enabled.

- Word Aligner Module – Select Enabled.

- Lane Aligner Module – Select Enabled when 2 or 4 lane configurations. FIFO Depth of 8 and EBR is recommended.

This module takes serial DSI/CSI-2 data and outputs pixel data after de-serialization in DSI/CSI-2 High Speed mode and protocol decoding. If a user is creating this IP from scratch, it is recommended to set the design name to rx and the module name to rx\_dphy. This way, the user does not need to modify the instance name of this IP in the top-level design, as well as the simulation setup file. Otherwise, the user must modify the names accordingly.

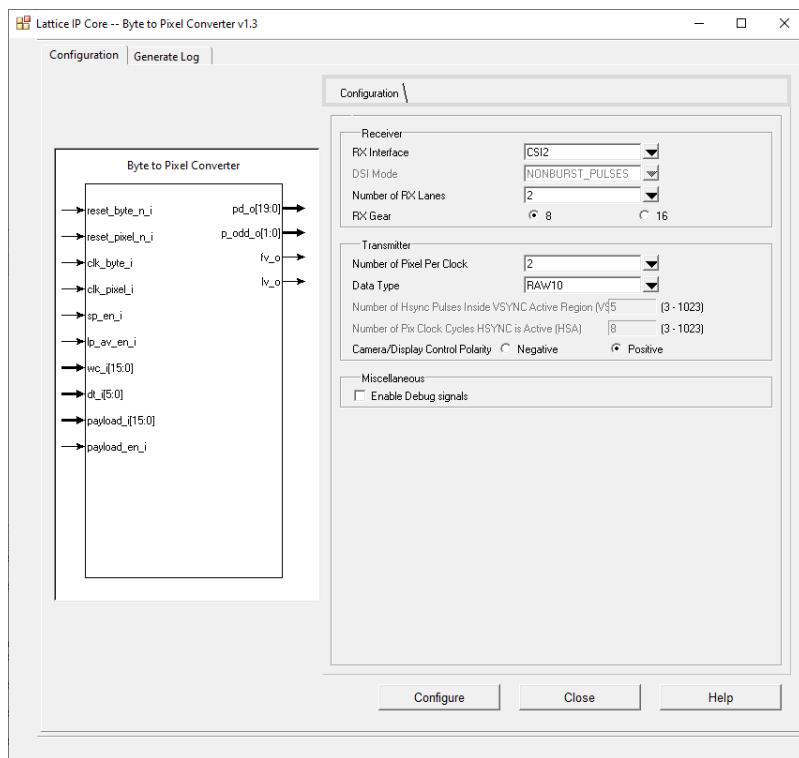

### 3.2. byte2pixel

This module must be created for the RX channel according to D-PHY type, data type, the number of lanes, RX Gear, and others. [Figure 3.2](#) shows an example of IP interface settings in Clarity for the byte2pixel IP. The user can use the .sbx file (b2p/b2p.sbx) included in the sample project and reconfigure according to user's needs. Refer to [Byte-to-Pixel Converter IP User Guide \(FPGA-IPUG-02027\)](#) for details.

**Figure 3.2. byte2pixel IP Creation in Clarity Designer**

The following provides the guidelines and parameter settings required for this reference design.

- RX Interface – Select DSI or CSI-2. Set the same type as RX D-PHY IP.

- Number of RX Lanes – Set the same value as RX D-PHY IP.

- RX Gear – Set the same value as RX D\_PHY IP.

- Number of Pixel Per Clock – Set 1, 2, or 4. 4 is applicable only to two TX channels with TX Gear 14. 2 is applicable to one TX channel with TX Gear 14 or two TX channels with TX Gear 7. Selection is limited in some configurations (refer to [Table 1.2](#)).

- Data Type – Set RGB888 or RGB666 for DSI and RGB888, RAW8, RAW10, or RAW12 for CSI-2. Others are not supported in this reference design.

- Camera/Display Control Polarity – Set Positive. Polarity setting of sync and data enable is done outside of this IP.

If a user is creating this IP from scratch, it is recommended to set the design name to b2p and the module name to byte2pix so that user do not need to modify the instance name of this IP in the top-level design as well as the simulation setup file. Otherwise, the user must modify the names accordingly.

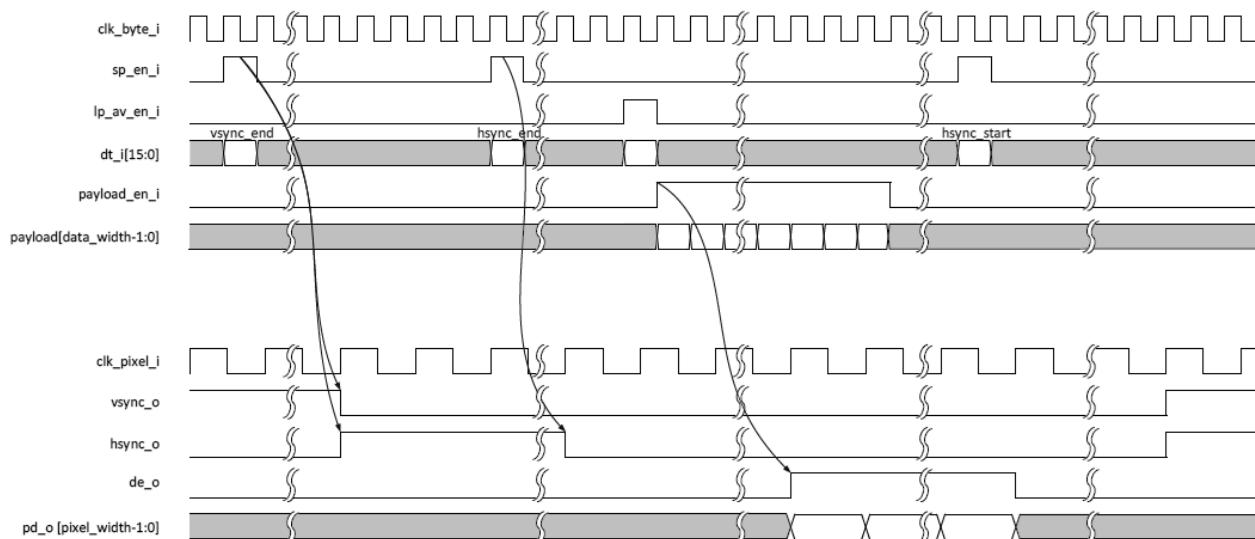

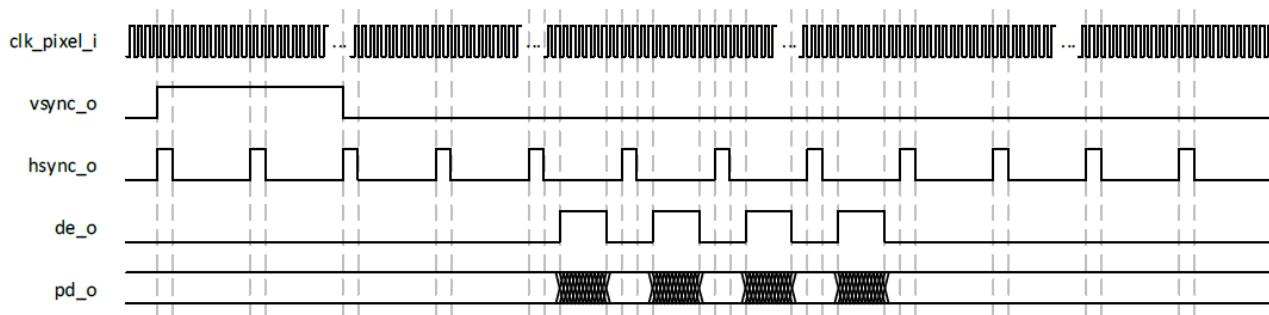

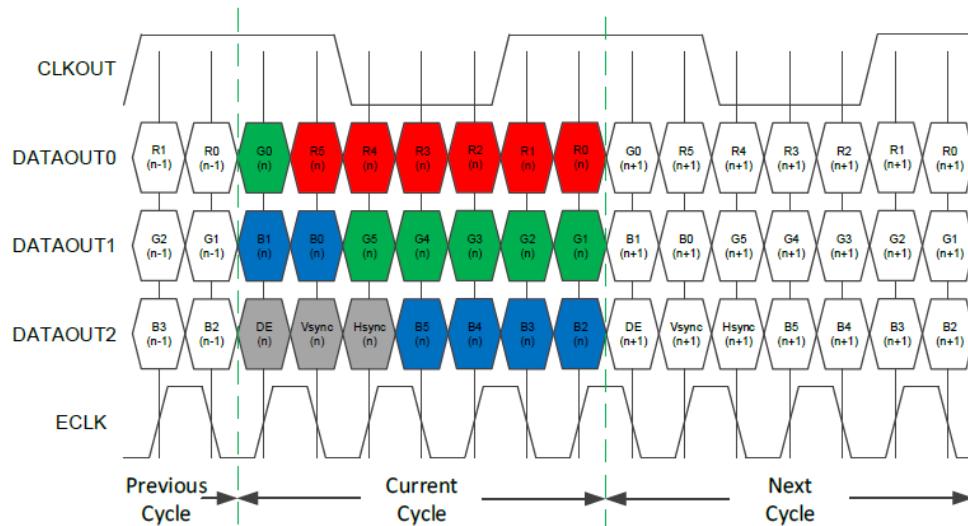

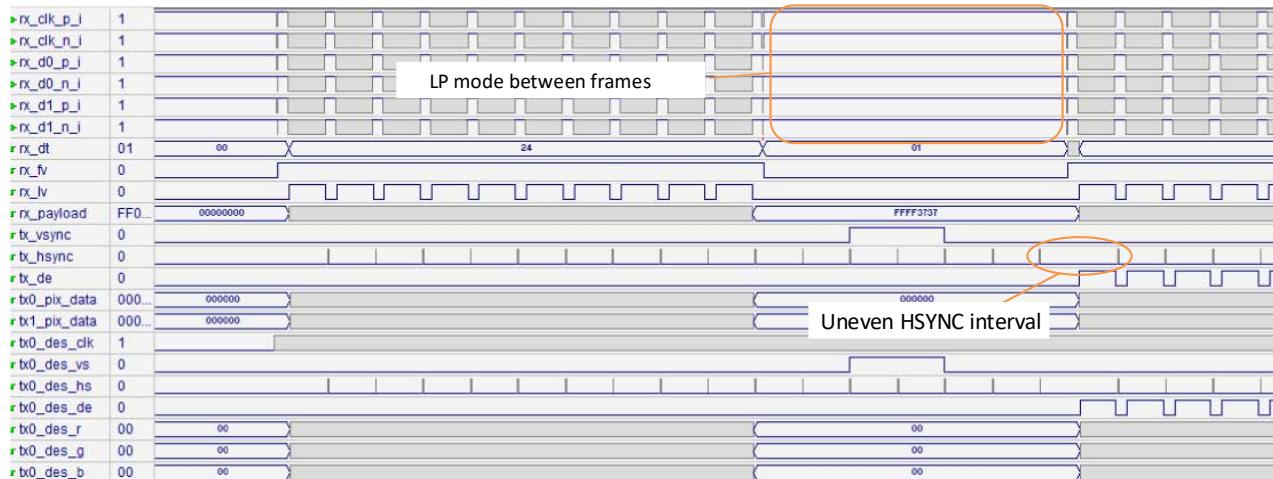

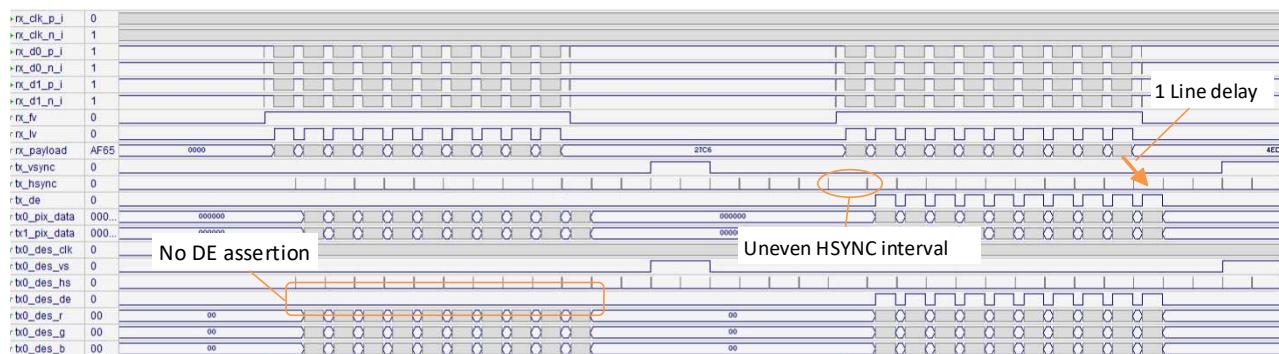

This module receives byte data from RX D-PHY along with packet enable signal, among others, and reorganizes the data to form the desired pixel data via FIFO according to the data type specified. FIFO is used as a data buffer as well as clock domain conversion. Byte data are written to FIFO in byte clock domain and read in pixel clock domain. Pixel clock is provided from TX LVDS module. Depending on the D-PHY type (DSI or CSI-2), different types of sync and data enable signals are generated. [Figure 3.3](#) shows the interface timing diagram for DSI. VSYNC, HSYNC, and DE are generated based on short packet enable and payload enable signals. In case of DSI, these signals are sent to LVDS TX module as is. Depending on the configuration, output data (pd\_o) could have one, two, or four pixels per pixel clock. [Figure 3.4](#) shows global output timing for DSI. Due to the clock domain crossing, the pulse length and/or sync signal intervals may vary slightly.

**Figure 3.3. Interface Timing Diagram for DSI**

**Figure 3.4. Global Output Timing Diagram for DSI**

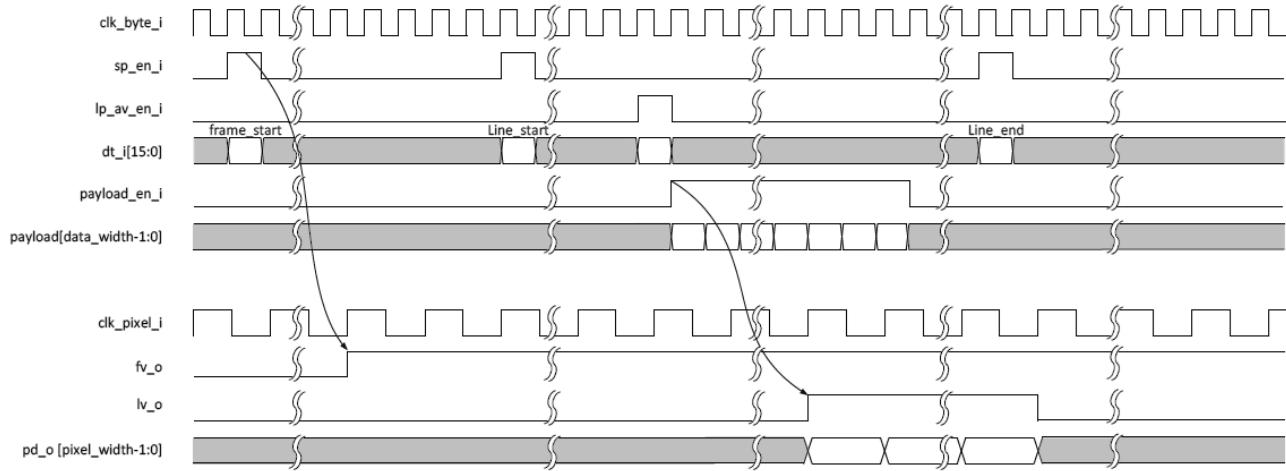

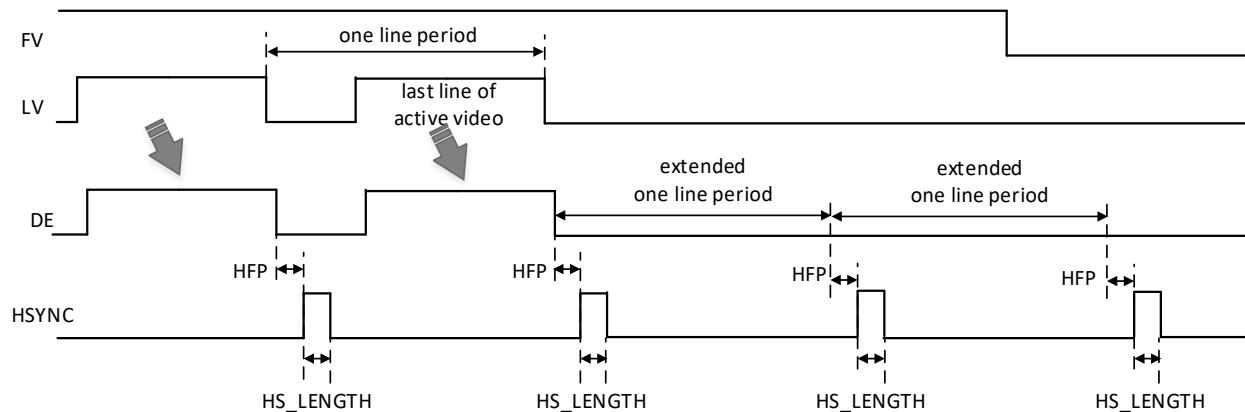

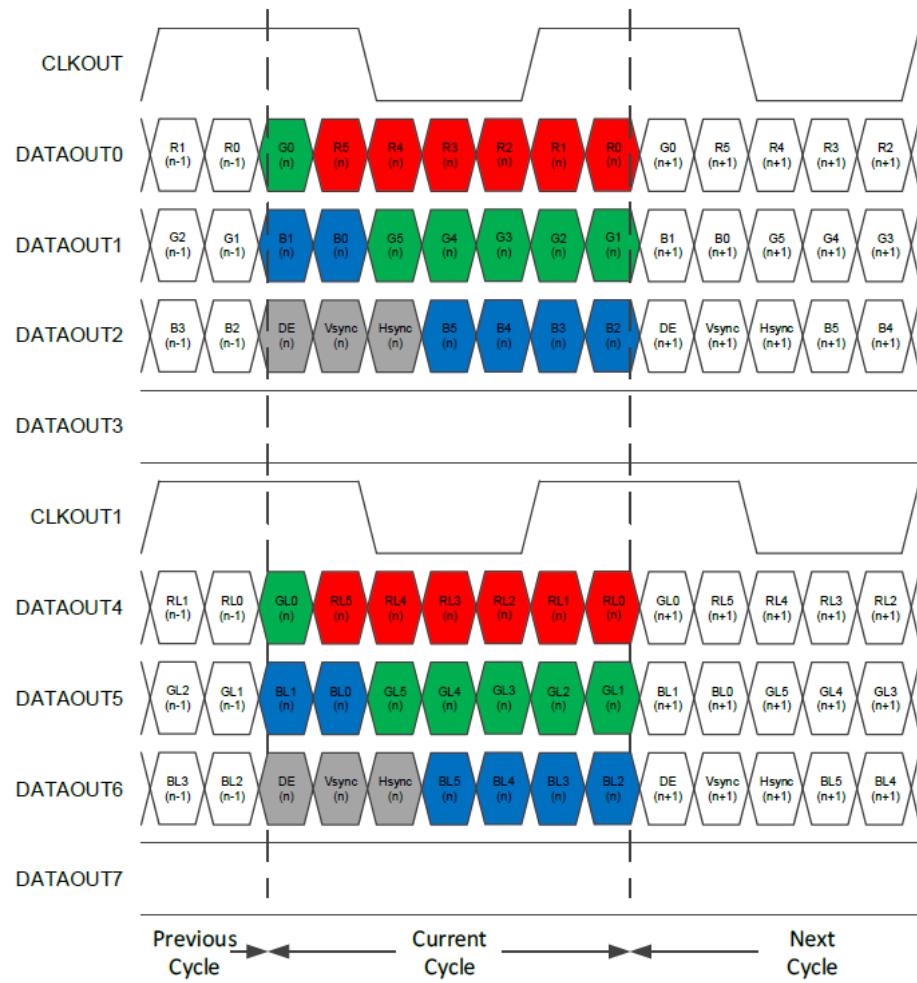

[Figure 3.5](#) shows the interface timing diagram for CSI-2. FV and LV are generated based on short packet enable and payload enable signals. [Figure 3.6](#) shows global output timing for CSI-2. In the case of CSI-2, sync signals (VSYNC, HSYNC) must be created from FV and LV to match the interface format of LVDS. Also, in case of RAW8/RAW10/RAW12, RGB pixel data must be created from RAW data. For these purposes, an additional module (rgb2rgb or raw2rgb) is required for CSI-2 between byte2pixel and tx\_lvds. In the case of TX Gear 14 or two TX channel outputs, output data (pd\_o) has two pixels per pixel

clock. Note that TX Gear 14 and two TX channel configuration must not happen together in case of CSI-2 (refer to [Table 1.2](#)).

**Figure 3.5. Interface Timing Diagram for CSI-2**

**Figure 3.6. Global Output Timing Diagram for CSI-2**

### 3.3. rgb2rgb

This module is instantiated for CSI-2 RX with RGB888 and has two major functions, sync signal generation and video data trimming.

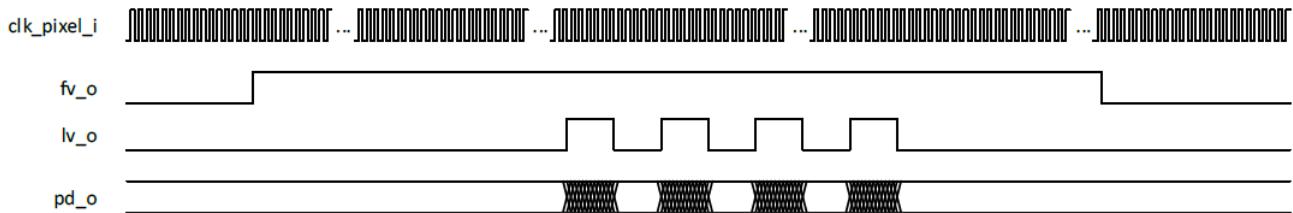

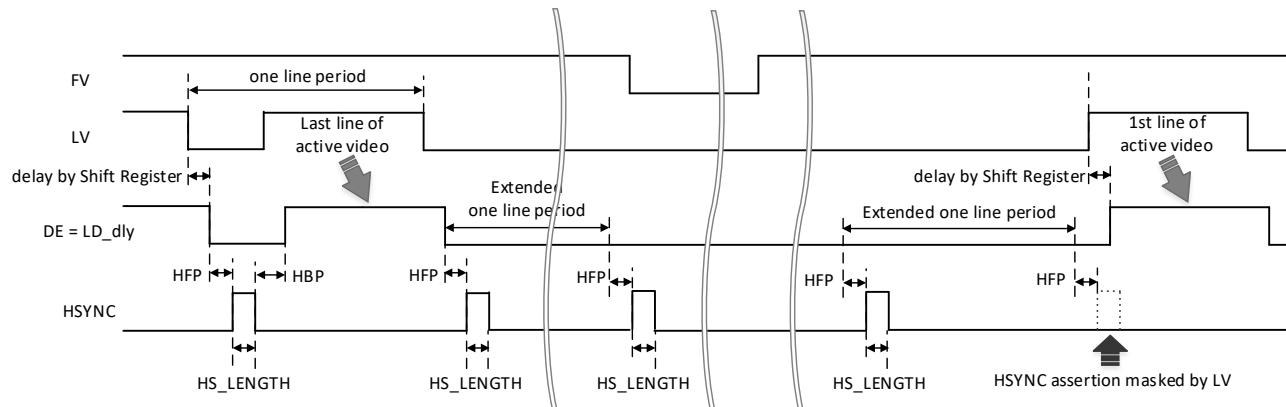

#### 3.3.1. Sync Signal Generation

Since sync signal format is different between CSI-2 and LVDS, VSYNC and HSYNC signals must be created from FV and LV comes from byte2pixel. For that purpose, the following parameters are prepared:

- HFP (Horizontal Front Porch)

- HS\_LENGTH (Horizontal Sync Length)

- VFP (Vertical Front Porch)

- VS\_LENGTH (Vertical Sync Length)

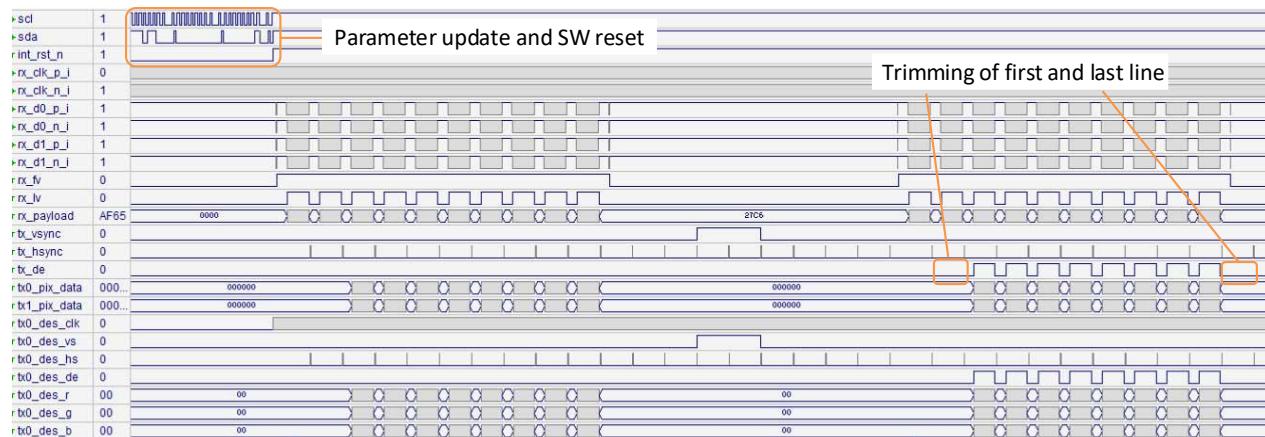

The above parameter values can be changed through register writes when USE\_I2C is defined. Otherwise, the values specified in `synthesis_directives.v` are applied. Note that (HFP + HS\_LENGTH) must be shorter than the horizontal blanking period. Otherwise, HSYNC active period and DE active period overlap, and we cannot expect the anticipated image on the display. If the user has no idea about the length of the horizontal blanking period, small values should be set. For example, HFP = 2, HS\_LENGTH = 2, and others, if the display accepts it. In addition, (VFP + VS\_LENGTH) must be smaller than the vertical blanking period for the same reason. HFP and VFP counts begin at the end of non-trimmed active pixel and active line. That means the actual blanking periods are larger than HFP or VFP if trimming happens on the right edge or bottom edge.

Figure 3.7. HSYNC Generation

During the vertical blanking period, HSYNC is generated by extending the line interval obtained by LV falling edges during the active line period as shown in Figure 3.7. One potential problem, however, is that HSYNC assertion could happen when the first DE of the next frame comes since there is no guarantee that the length of the vertical blanking period is multiple of one horizontal line period. To avoid this situation, a shift register is provided. FV/LV and payload data are all written to the shift register FIFO and comes out after the specified pixel clock cycle delay set by the parameter SR\_DELAY. Figure 3.8 shows the masking of HSYNC which overlaps DE period. If the display has the minimum requirement of HBP (Horizontal Blanking Period: period from the end of HSYNC to the beginning of DE), SR\_DELAY value should satisfy the following equation:

$$SR\_DELAY > HS\_LENGTH + \text{minimum HBP}$$

VSYNC/HSYNC assertions are controlled based on these delayed signals, but HSYNC assertion is disabled when the original LV is active. By changing this parameter value, the user can change the HSYNC mask period. This parameter can also be changed through register write when USE\_I2C is defined.

Figure 3.8. HSYNC Masked by LV

Since VSYNC generation is based on the assertion timing of HSYNC, and HSYNC assertion is based on the falling edge of LV, VSYNC of the current outgoing frame requires the previous incoming video timings. Therefore, no VSYNC assertion happens for the first incoming video frame and DE is masked for that frame. Valid VSYNC and video data outputs begin from the second incoming frame.

### 3.3.2. Active Data Trimming

In some cases, video data from sensor devices have an area that is larger than what is required by the display. For this reason, edge trimming capability is provided using following parameters:

- **LEFT\_TRIM** (trimming pixels from the left edge)

- H\_TX\_PEL (active pixel count)

- TOP\_TRIM (trimming lines from the top edge)

- V\_TX\_LINE (active line count)

The above parameter values can be changed through register write when USE\_I2C is defined. Otherwise, the values specified in synthesis\_directives.v are applied. Note that (LEFT\_TRIM + H\_TX\_PEL) must not exceed the original horizontal active pixel count, otherwise output image is corrupted. In addition, (TOP\_TRIM + V\_TX\_LINE) must not exceed the original active line count for the same reason. In the case of TX Gear 14, H\_TX\_PEL must be an even value.

### 3.4. raw2rgb

This module is instantiated for CSI-2 RX with RAW8/RAW10/RAW12 and has three major functions: RGB data creation, sync signal generation and video data trimming.

#### 3.4.1. RGB Data Creation

In the case of RAW data format, one pixel contains only one-color component of RGB. Therefore, missing color components must be created by interpolation to form RGB888. Figure 3.9 shows four scenarios of Bayer patterns of the color components at the top-left pixels come from the image sensor.

Figure 3.9. Bayer Pattern of RAW Data

Missing color components are created by interpolation using the neighborhood pixels. Figure 3.10 shows examples of interpolations to create all three-color components for the center pixel. Either 2-pixel averaging, or 4-pixel averaging is applied, depending on the location of the pixel, to create the missing color components.

|                                                                              |                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{ccc} B & G & B \\ G & \boxed{R} & G \\ B & G & B \end{array}$ | $\begin{aligned} R_{(\text{interpolated})} &= R_{(\text{center})} \\ G_{(\text{interpolated})} &= (G_{(\text{top})} + G_{(\text{bottom})} + G_{(\text{left})} + G_{(\text{right})}) / 4 \\ B_{(\text{interpolated})} &= (B_{(\text{top-left})} + B_{(\text{top-right})} + B_{(\text{bottom-left})} + B_{(\text{bottom-right})}) / 4 \end{aligned}$ |

| $\begin{array}{ccc} G & B & G \\ R & \boxed{G} & R \\ G & B & G \end{array}$ | $\begin{aligned} R_{(\text{interpolated})} &= (R_{(\text{left})} + R_{(\text{right})}) / 2 \\ G_{(\text{interpolated})} &= G_{(\text{center})} \\ B_{(\text{interpolated})} &= (B_{(\text{top})} + B_{(\text{bottom})}) / 2 \end{aligned}$                                                                                                         |

Figure 3.10. RGB Data Creation from RAW Data

Due to the necessity of vertical interpolation, this module has two-line buffers with the depth specified by the directive LB\_DEPTH\_\*. In the case of edge and corner pixel interpolations (top line, bottom line, left edge, right edge), mirroring is

applied to cover the non-existing pixels. For example, there is no top pixels for the first line pixel interpolation and the bottom (second line) pixels are used instead of the non-existing top pixels. The same method applies to left edge, right edge, and bottom-line pixel interpolations. Note that the first line output is roughly aligned with the second incoming line due to the line buffering delay.

### 3.4.2. Sync Signal Generation

The scheme is same as CSI-2 RGB888 input except for the non-existence of the shift register. In case of RAW data processing, a single line process delay happens due to the line buffer mentioned in the [RGB Data Creation](#) section, the HSYNC masking feature is not required using the shift register. Refer to the [Sync Signal Generation](#) section for details.

### 3.4.3. Active Data Trimming

The scheme is same as CSI-2 RGB888 input. Refer to the [Active Data Trimming](#) section for details.

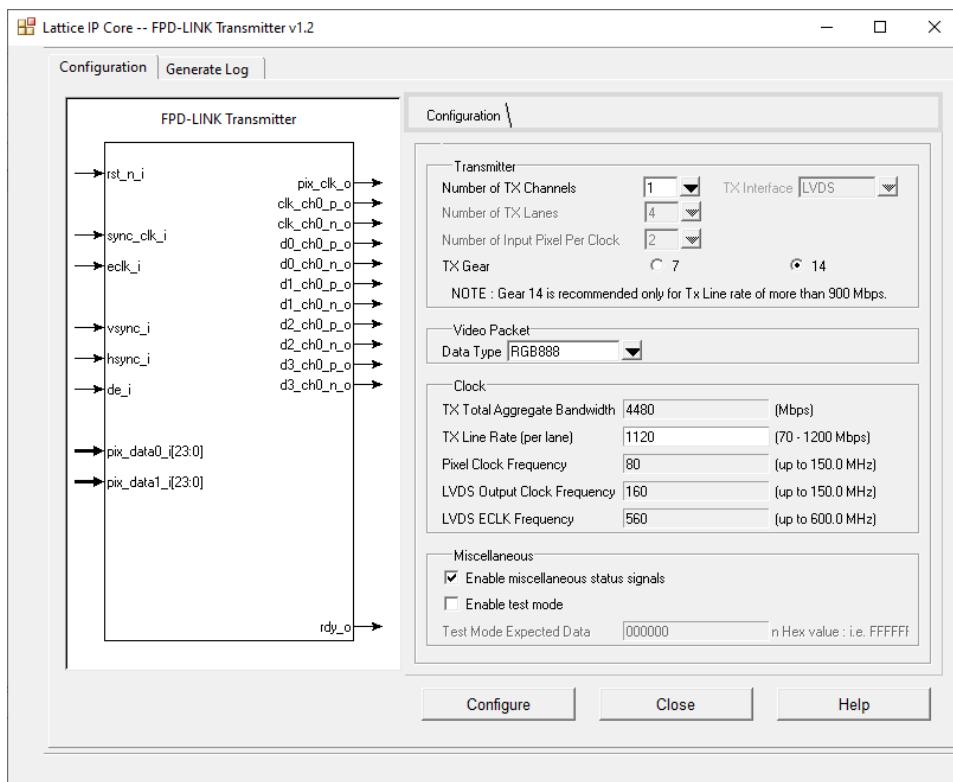

## 3.5. tx\_lvds

The user must create this module according to channel conditions, such as number of lanes, bandwidth, and others. [Figure 3.11](#) shows an example IP interface setting in Clarity Designer for the OpenLDI/LVDS Transmitter IP. The user can use the sbx file (tx/ttx.sbx) included in the sample project and re-configure according to the user's needs. Refer to [OpenLDI/FPD-LINK/LVDS Transmitter Interface IP User Guide \(FPGA-IPUG-02022\)](#) for details.

Figure 3.11. tx\_dphy IP Creation in Clarity Designer

The following provides the guidelines and parameter settings required for this reference design.

- Number of TX Channels – Set according to channel configuration. Must match NUM\_TX\_CH\_\* setting. Refer to [Table 1.2](#) for possible TX channel setting.

- TX Gear – Set 7 or 14. Must match TX\_GEAR\_\* in synthesis\_directives.v.

- Data Type – Select RGB666 in case of RX\_RGB666. Otherwise, select RGB888.

- TX Line Rate – Set the value derived from the equation below.

- Enable miscellaneous status signals – Must be enabled (checked).

- Enable test mode – Must be disabled (unchecked).

This module takes the pixel data and outputs LVDS data after 7:1 or 14:1 serialization. If the user is creating this IP from scratch, it is recommended to set the design name to tx and module name to tx\_lvds so that user do not need to modify the instance name of this IP in the top-level design as well as simulation setup file. Otherwise, the user needs to modify the names accordingly.

TX Line Rate is derived from the following equation:

$$TX\_lane\_bandwidth = \frac{RX\_lane\_bandwidth * number\_of\_RX\_lane * 7}{RX\_pixel\_bus\_width * number\_of\_TX\_channel}$$

Example 1: CSI-2 RAW10 RX with 4-lane at RX lane bandwidth = 400 Mbps

$$TX \text{ lane bandwidth} = (400 \times 4 \times 7) / (10 \times 1) = 1120 \text{ Mbps.}$$

Example 2: DSI RGB888 RX with 4-lane at RX lane bandwidth = 1200 Mbps with dual channel TX outputs

$$TX \text{ lane bandwidth} = (1200 \times 4 \times 7) / (24 \times 2) = 700 \text{ Mbps.}$$

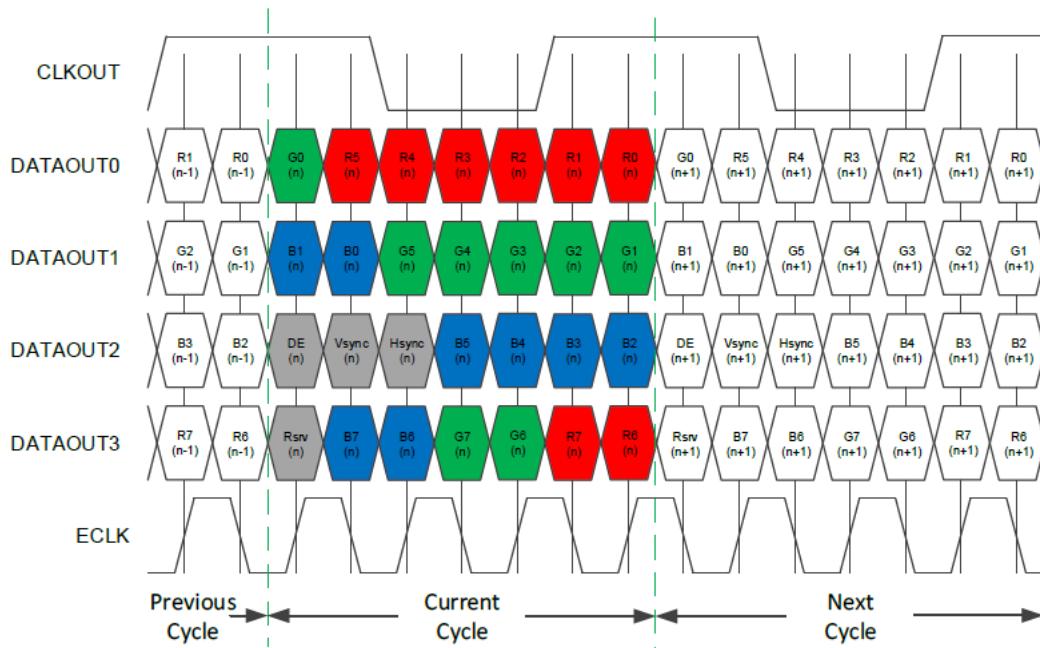

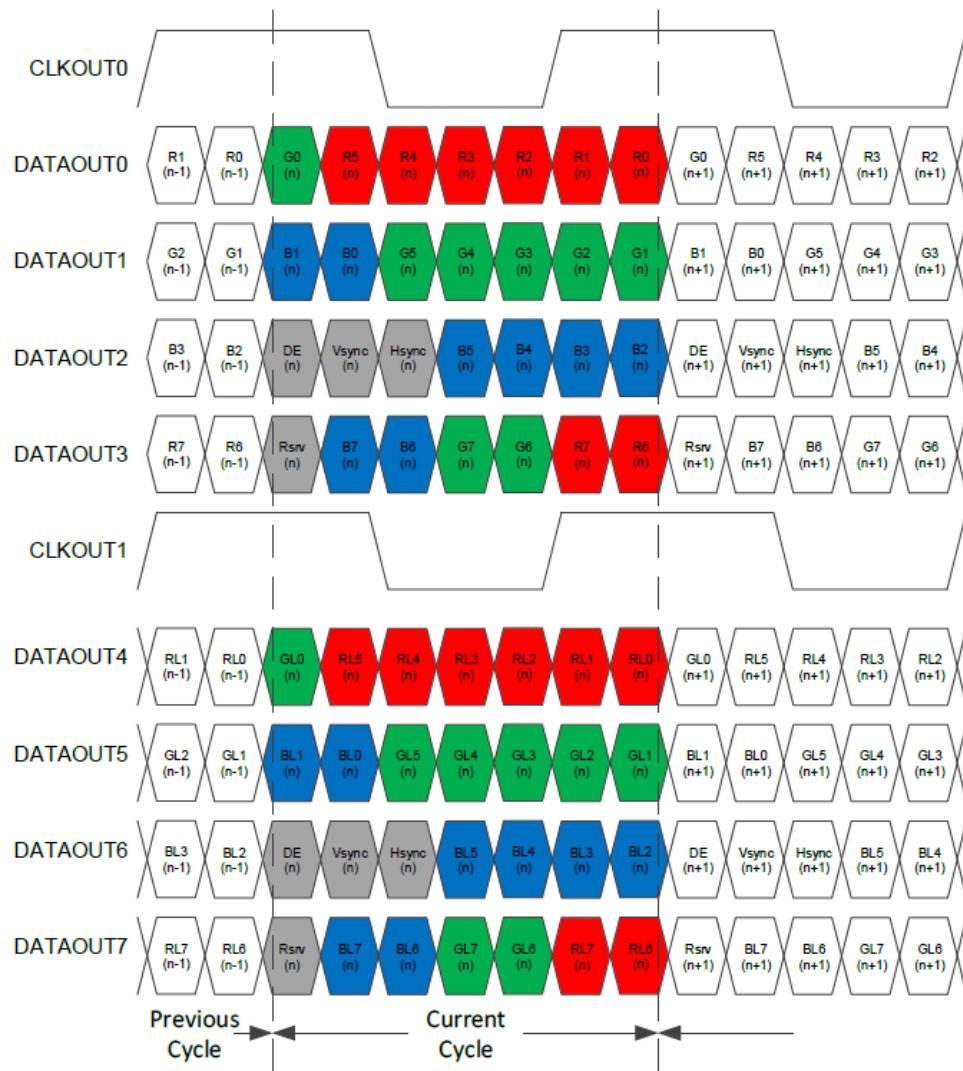

Figure 3.12 to Figure 3.15 show the output data timings of single and dual channel configuration with RGB888 and RGB666. RGB888 uses four data lanes per channel and RGB666 uses three data lanes per channel.

Figure 3.12. Single Channel LVDS Output of RGB888

Figure 3.13. Dual Channel LVDS Output of RGB888

Figure 3.14. Single Channel LVDS Output of RGB666

Figure 3.15. Dual Channel LVDS Output of RGB666

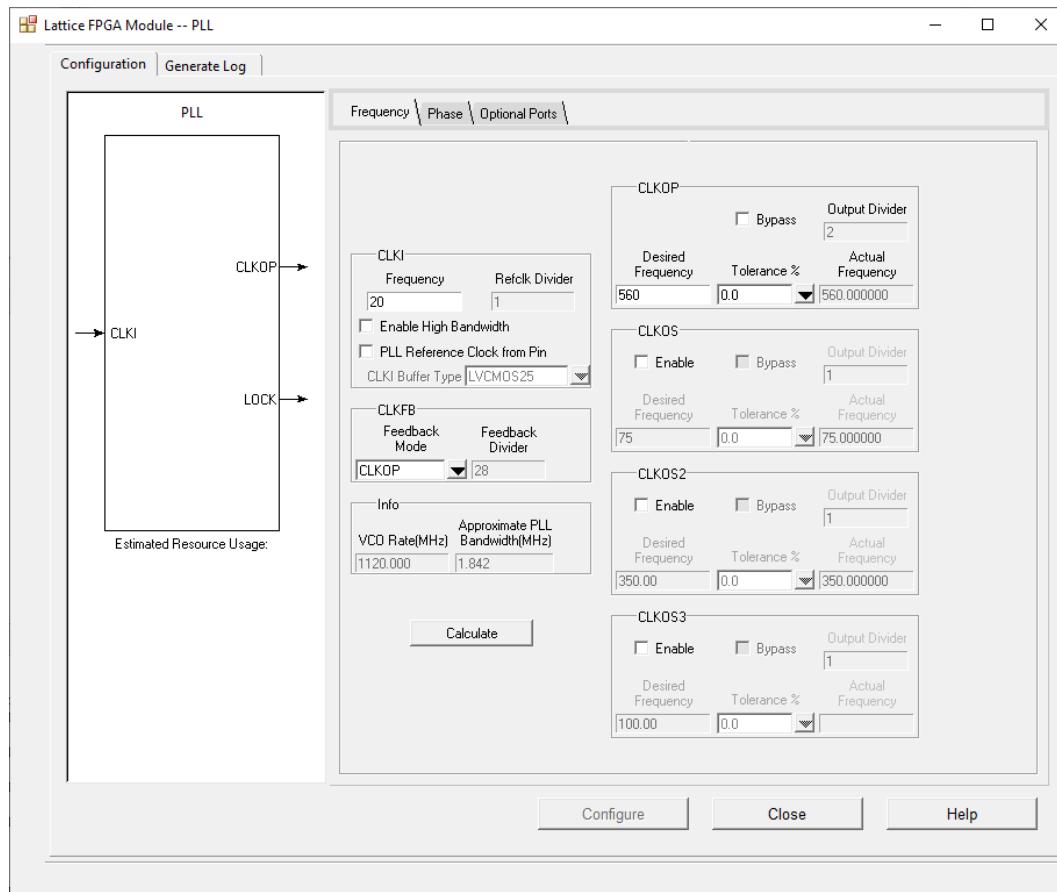

### 3.6. int\_gpll

The user must create GPL module to feed the edge clock to tx\_lvds. Additionally, the continuous byte clock could be generated when RX D-PHY is in HS\_LP mode. The user can use the sbx file (int\_gpll/int\_gpll.sbx) included in the sample project and re-configure according to user's needs. In case that user makes this IP from scratch, it is recommended to set the design name to int\_gpll so that the user does not need to modify the instance name of this IP in the top-level design as well as simulation setup file. Otherwise, the user needs to modify the names accordingly.

Figure 3.16. GPLL IP Creation

The TX edge clock frequency is half of the TX lane bandwidth set for tx\_lvds. This clock must be assigned to CLKOP. If the byte clock must be generated, assign it to CLKOS. Note that the VCO clock of GPLL must be a common multiple of these two clocks. There is a case wherein TX edge clock and byte clock cannot be generated together. In this instance, give up generating the byte clock by GPLL and perform either of the following options:

- Change RX D-PHY to HS\_ONLY mode; or

- Feed the continuous byte clock directly from one of the available I/O pins.

If the RX D-PHY is in HS\_ONLY mode and GPLL can generate the TX edge clock using the byte clock as the input clock of GPLL (CLKI), the external reference clock is not necessary. int\_gpll instantiation based on the configuration is shown below as a code snippet of mipi2lvds.v:

```

//////////

////// GPLL instantiation

////// User has to modify this if necessary

//////////

`ifdef EXT_REF_CLK

`ifdef RX_CLK_MODE_HS_LP

int_gpll pll_inst (

.CLKI (ref_clk_i),           // ref clock

.CLKOP (pll_eclk),          // tx edge clock

.CLKOS (pll_byte_clk),      // byte clock

.LOCK (pll_lock)

);

`elsif RX_CLK_HS_ONLY

int_gpll pll_inst (

.CLKI (ref_clk_i), // cannot create eclk from byte clock

.CLKOP (pll_eclk),

.LOCK (pll_lock)

);

`endif

`elsif RX_CLK_HS_ONLY

int_gpll pll_inst (

.CLKI (rx_clk_byte_fr),

.CLKOP (pll_eclk),

.LOCK (pll_lock)

);

`endif

//////////

```

If user can use ref\_clk\_i (or simply divided clock of this) as byte\_clk in HS\_LP mode, the user should disable CLKOS and add the following in mipi2lvds.v:

```

assign pll_byte_clk = ref_clk_i; // ref_clk_i could be simply divided clock of this

```

### 3.7. i2c\_slave

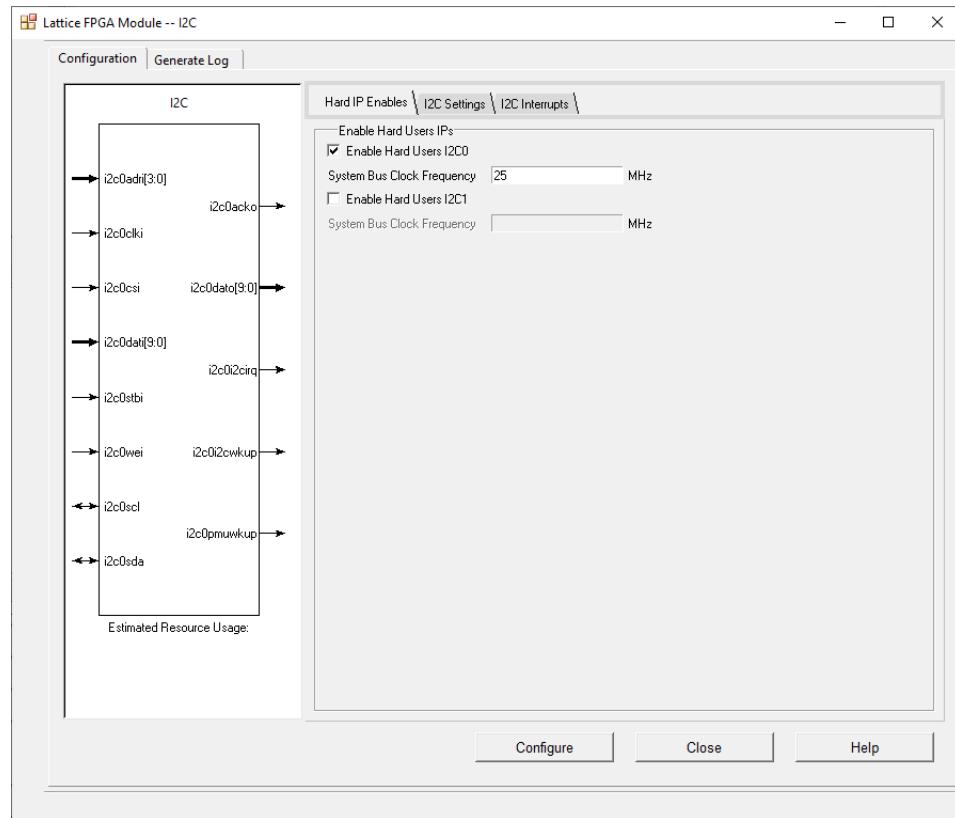

This module is instantiated when USE\_I2C is defined and enables the user to change CSI-2 related parameters on the fly through I2C connections. I2C Hard IP is instantiated and used as an I2C slave device. The user can use the .sbx file (i2c\_s/i2c\_s.sbx) included in the sample project and re-configure. In case that user make this IP from scratch, it is recommended to set the design name to i2c\_s so that user do not need to modify the instance name of this IP in the top-level design as well as simulation setup file. Otherwise, the user needs to modify the names accordingly. There exist two I2C Hard IP modules in CrossLink and I2C0 is used in this IP as shown in [Figure 3.17](#). The user must change the setting if the other IP (I2C1) is used. Also, the System Bus clock frequency must be changed according to the clock fed to this module.

Figure 3.17. I<sup>2</sup>C IP Creation #1

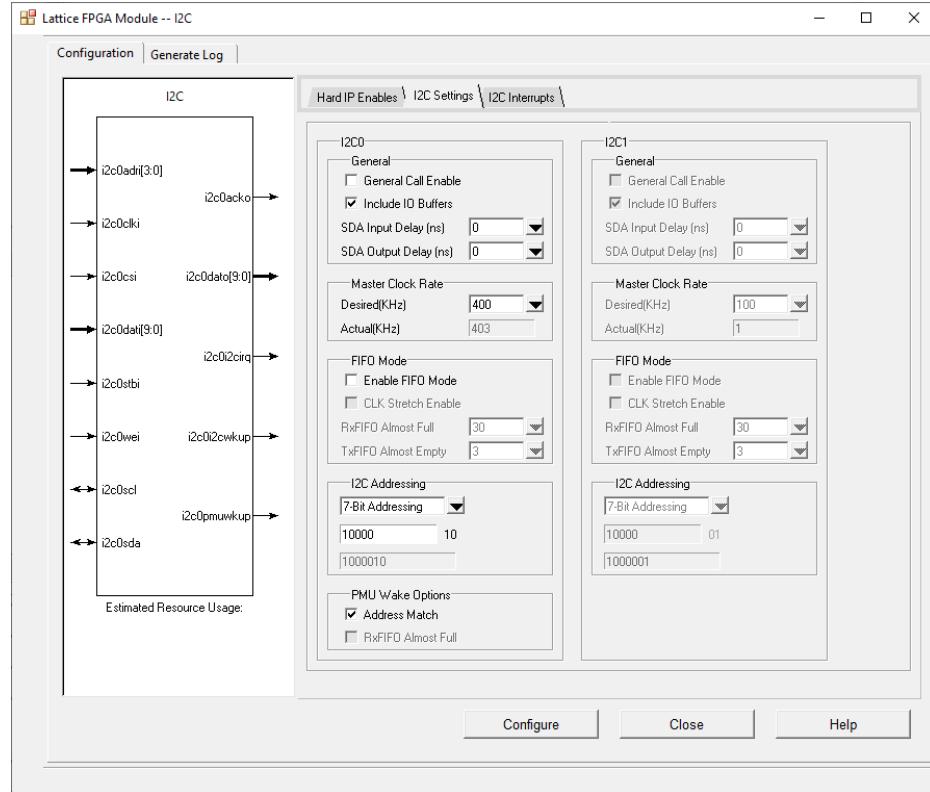

Figure 3.18 shows the basic settings of I2C IP. The user can change the settings according to own needs, but the following should be enforced:

- FIFO Mode must be disabled (unchecked)

- Address Match must be enabled (checked)

MSB 5 bits of I2C slave address can be set here. In the case of I2C0, LSB 2 bits are fixed to 2'b10.

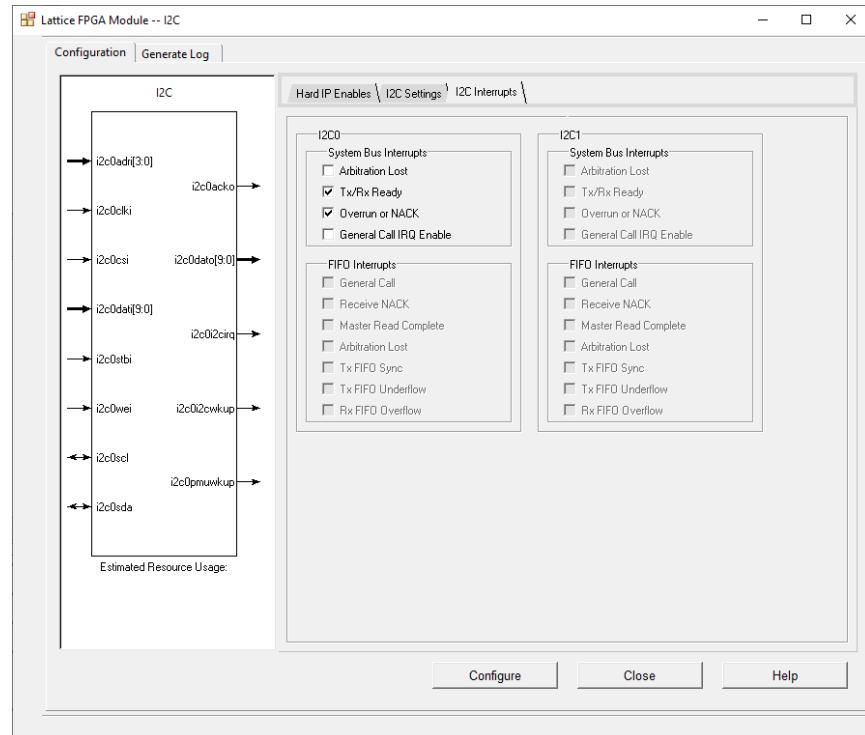

Figure 3.19 shows the interrupt settings. At least Tx/Rx Ready must be enabled (checked).

Figure 3.18. I<sup>2</sup>C IP Creation #2

Figure 3.19. I<sup>2</sup>C IP Creation #3

This module is equipped with parameter registers of 4-bit address area of I2C sub address shown in [Table 3.1](#).

**Table 3.1. I<sup>2</sup>C Slave Register Map**

| Sub address | Name          | Bits   | Description                                                                                                                            |

|-------------|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0           | SW Reset      | [0]    | Software reset register. When this is active, all modules except for i2c_slave are in reset condition. Active low.                     |

| 1           | SR Delay      | [7:0]  | Shift Register delay register. Sync and data from byte2pixel are delayed before processed in rgb2rgb. The value must be 8'd2 – 8'd255. |