# **Tri-Speed Ethernet IP**

IP Version: v2.2.0

# **User Guide**

FPGA-IPUG-02084-2.5

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Content      | S                                                       | 3  |

|--------------|---------------------------------------------------------|----|

| Abbrevia     | ations in This Document                                 | 11 |

| 1. Inti      | roduction                                               | 12 |

| 1.1.         | Overview of the IP                                      | 12 |

| 1.2.         | Quick Facts                                             | 12 |

| 1.3.         | IP Support Summary                                      | 13 |

| 1.4.         | Features                                                |    |

| 1.5.         | Licensing and Ordering Information                      | 14 |

| 1.6.         | Hardware Support                                        |    |

| 1.7.         | Naming Conventions                                      |    |

| 1.7          |                                                         |    |

| 1.7          |                                                         |    |

| 2. Fur       | nctional Description                                    |    |

| 2.1.         | IP Architecture Overview                                |    |

| 2.1          |                                                         |    |

| 2.1          | ·                                                       |    |

| 2.1          |                                                         |    |

| 2.1          |                                                         |    |

| 2.1          | · · · ·                                                 |    |

| 2.1          | ·                                                       |    |

| 2.2.         | Clocking                                                |    |

| 2.2          |                                                         |    |

| 2.2          |                                                         |    |

| 2.2          |                                                         |    |

| 2.3.         | Reset                                                   |    |

| 2.3          |                                                         |    |

| 2.4.         | User Interfaces                                         |    |

| 2.4          |                                                         |    |

| 2.4          |                                                         |    |

| 2.5.         | Datapath                                                |    |

| 2.5          | ·                                                       |    |

| _            | .2. Transmit MAC                                        |    |

| 2.6.         | Statistics Vector                                       |    |

| 2.7.         | Lane Merging                                            |    |

|              | 1.1. Lane Merging for SERDES Primitive of Avant Devices |    |

| 2.8.         | Hardware Requirements (Avant Devices)                   |    |

|              | Parameter Description                                   |    |

| 3.1.         | General Attributes                                      |    |

| 3.2.         | MAC Only Mode Attributes                                |    |

| 3.3.         | SGMII (LVDS) Only Mode Attributes                       |    |

| 3.4.         | SGMII (SERDES) Only Mode Attributes (Nexus Devices)     |    |

| 3.5.         | SGMII (SERDES) Only Mode Attributes (Avant Devices)     |    |

| 3.6.         | MAC + SGMII (LVDS) Mode Attributes                      |    |

| 3.7.         | MAC + SGMII (SERDES) Mode Attributes                    |    |

| 3.8.         | Statistics Counter Configuration                        |    |

|              | nal Description                                         |    |

| 4. 3igi      | Clock Interface                                         |    |

| 4.1.<br>4.2. | Reset Interface                                         |    |

| 4.2.<br>4.3. | AXI4-Stream Transmit Interface                          |    |

| 4.3.<br>4.4. | AXI4-Stream Receive Interface                           |    |

| 4.4.<br>4.5. | Transmit MAC Control and Status Interface               |    |

|              | Receive MAC Control and Status Interface                |    |

| 4.6.         | Receive IVIAC CUITITOT and Status IIITETTACE            | 62 |

|    | 4.7. F | PHY Interface                                                    | 63  |

|----|--------|------------------------------------------------------------------|-----|

|    | 4.7.1. | MII/GMII Interface                                               | 63  |

|    | 4.7.2. | Gigabit MAC Interface                                            | 64  |

|    | 4.7.3. | SGMII Easy Connect Interface                                     | 64  |

|    | 4.7.4. | RGMII Interface                                                  | 65  |

|    | 4.7.5. | RMII Interface                                                   | 65  |

|    | 4.8. H | Host Interface                                                   | 66  |

|    | 4.8.1. | APB Host Interface                                               | 66  |

|    | 4.8.2. | AHB-Lite Host Interface                                          | 66  |

|    | 4.8.3. | AXI4-Lite Host Interface                                         | 67  |

|    | 4.9. I | Management Interface                                             | 67  |

|    |        | nterrupt Interface                                               |     |

|    |        | Miscellaneous Interface                                          |     |

|    |        | SGMII (LVDS) Only Interfaces                                     |     |

|    |        | SGMII (SERDES) Only Interfaces                                   |     |

|    |        | SGMII (SERDES) Only Interfaces, Nexus SERDES Primitive, MPCS     |     |

|    |        | SGMII (SERDES) Only Interfaces, Avant SERDES Primitive, MPPHY    |     |

|    |        | MAC + SGMII (LVDS) Interfaces                                    |     |

|    |        | MAC + SGMII (SERDES) Interfaces                                  |     |

|    |        | . MAC + SGMII (SERDES) Interfaces, Nexus SERDES Primitive, MPCS  |     |

|    |        | . MAC + SGMII (SERDES) Interfaces, Avant SERDES Primitive, MPPHY |     |

| 5. |        | er Description                                                   |     |

|    | _      | Ox000] Mode Register                                             |     |

|    |        | 0x004] Transmit and Receive Control Register                     |     |

|    |        | 0x008] Maximum Packet Size Register                              |     |

|    | _      | Ox00C] IPG (Inter-Packet Gap) Register                           |     |

|    |        | 0x010 – 0x014] MAC Address Register (0,1)                        |     |

|    |        | 0x018] Transmit and Receive Status Register                      |     |

|    | _      | 0x010] VLAN Tag Register                                         |     |

|    |        | 0x020] GMII Management Register Access Control Register          |     |

|    |        | 0x024] GMII Management Access Data Register                      |     |

|    |        | 0x028 – 0x02C] Multicast Table Registers (0,1)                   |     |

|    |        | 0x030] Pause Opcode Register                                     |     |

|    |        | 0x034] TX FIFO Almost Full Threshold Register                    |     |

|    | _      | 0x038] TX FIFO Almost Empty Threshold Register                   |     |

|    | -      | Ox036] RX FIFO Almost Full Threshold Register                    |     |

|    | _      |                                                                  |     |

|    |        | 0x040] RX FIFO Almost Empty Threshold Register                   |     |

|    |        | 0x044] Interrupt Status Register                                 |     |

|    | _      | 0x048] Interrupt Enable Register                                 |     |

|    |        | 0x04C – 0x220] Statistics Counters                               |     |

|    |        | (0x400 – 0x50C) SGMII and Gb Ethernet PCS Soft IP Register       |     |

|    |        | GGMII and Gb Ethernet PCS Soft IP Register                       |     |

|    | 5.20.1 |                                                                  |     |

|    | 5.20.2 |                                                                  |     |

|    | 5.20.3 | , ,                                                              |     |

|    | 5.20.4 | ,                                                                |     |

|    | 5.20.5 |                                                                  |     |

|    | 5.20.6 |                                                                  |     |

|    | 5.20.7 |                                                                  |     |

|    | 5.20.8 |                                                                  |     |

|    | 5.20.9 |                                                                  |     |

|    |        | 0. [0x029] PCS Control Register 9                                |     |

| _  |        | 1. [0x02A] PCS Control Register 10                               |     |

| 6. | Examp  | le Design                                                        | 107 |

|    |        |                                                                  |     |

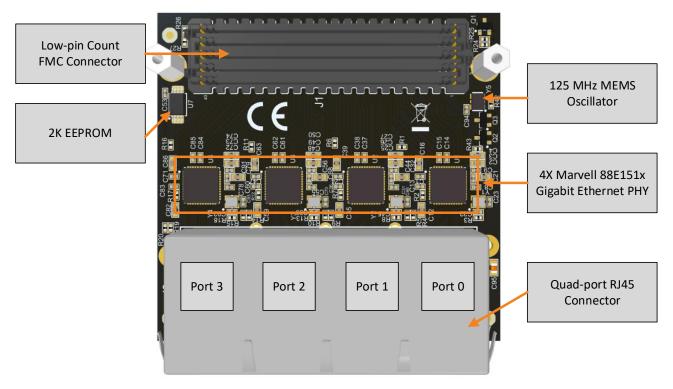

| 6.1.    | Design Boards and Ethernet FMC Overview                                                            | 107 |

|---------|----------------------------------------------------------------------------------------------------|-----|

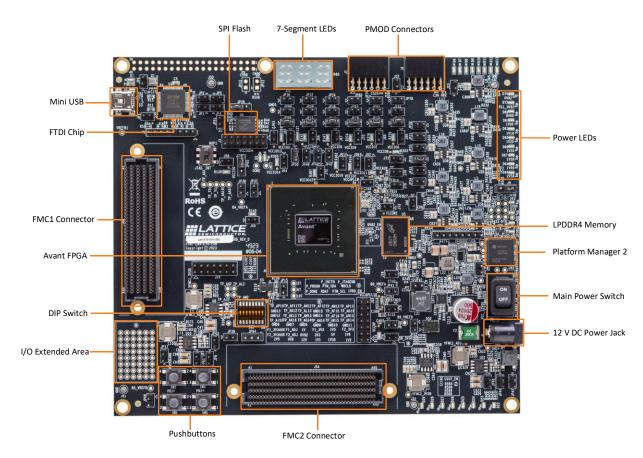

| 6.1.1   | . Avant-E Evaluation Board                                                                         | 107 |

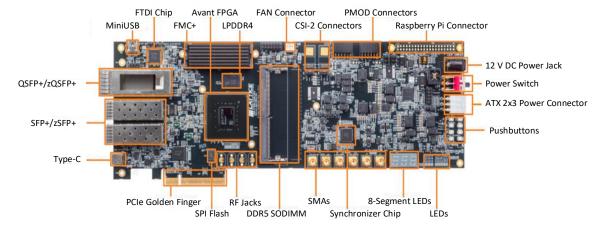

| 6.1.2   | . Avant G/X Versa Board                                                                            | 108 |

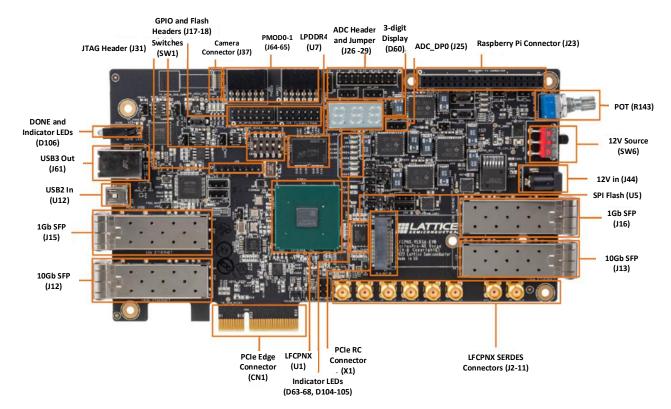

| 6.1.3   | . CertusPro-NX Versa Board                                                                         | 108 |

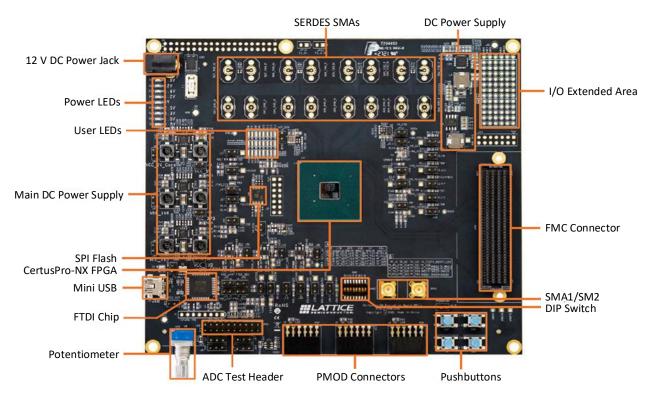

| 6.1.4   | . CertusPro-NX Evaluation Board                                                                    | 109 |

| 6.1.5   | . Ethernet FMC Module                                                                              | 110 |

| 6.2.    | Example Design Supported Configuration                                                             | 110 |

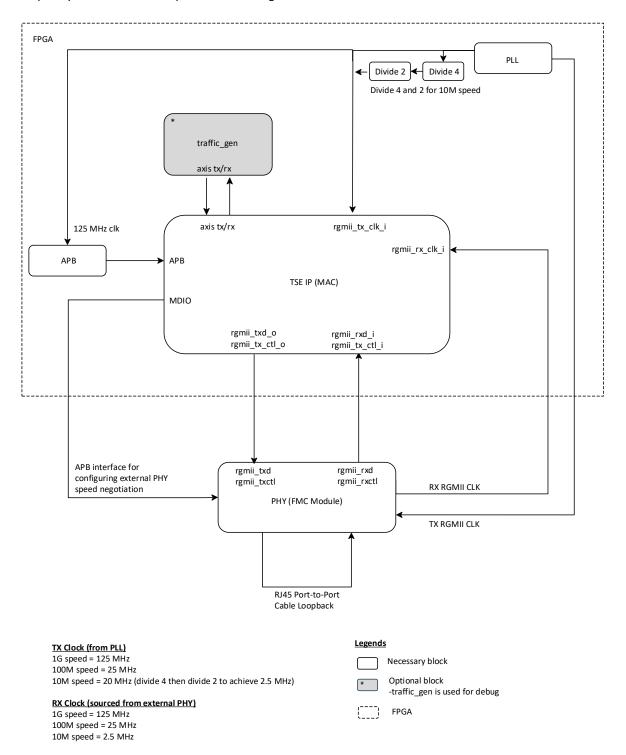

| 6.3.    | RGMII Example Design                                                                               |     |

| 6.3.1   | Overview of the RGMII Example Design and Features                                                  | 111 |

| 6.3.2   | · · · ·                                                                                            |     |

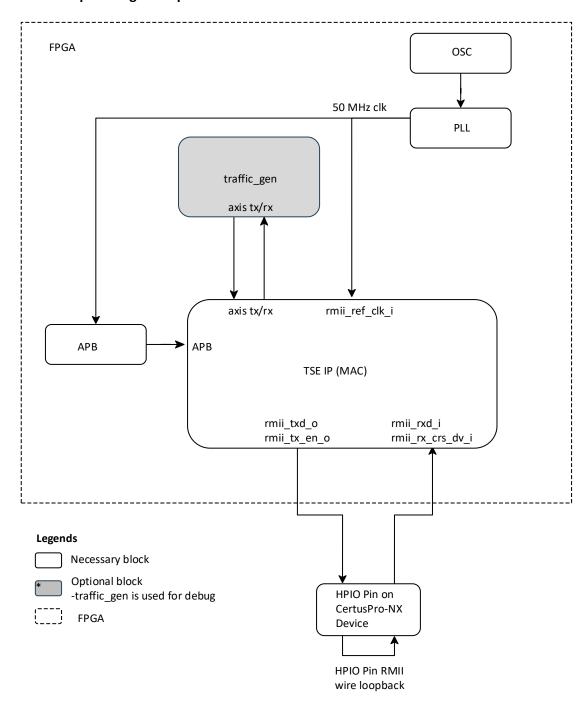

| 6.4.    | RMII Example Design                                                                                |     |

| 6.4.1   |                                                                                                    |     |

| 6.4.2   | · · · ·                                                                                            |     |

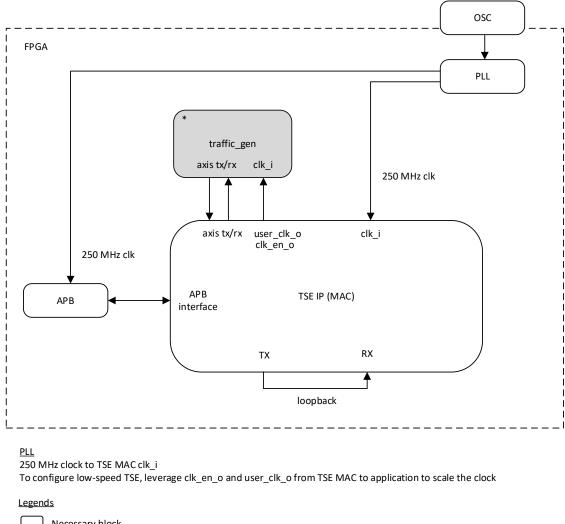

| 6.5.    | SGMII Example Design                                                                               |     |

| 6.5.1   |                                                                                                    |     |

| 6.5.2   |                                                                                                    |     |

| 6.6.    | Using Hardware Example Design                                                                      |     |

| 6.6.1   |                                                                                                    |     |

| 6.6.2   | ·                                                                                                  |     |

| 6.6.3   |                                                                                                    |     |

| 6.6.4   | ,                                                                                                  |     |

| 6.6.5   |                                                                                                    |     |

| 6.6.6   | · · · · · · · · · · · · · · · · · · ·                                                              |     |

| 6.6.7   |                                                                                                    |     |

| 6.6.8   |                                                                                                    |     |

|         | · · · · · · · · · · · · · · · · · · ·                                                              |     |

| 6.6.9   | · · · · · · · · · · · · · · · · · · ·                                                              |     |

| 6.7.    | Simulating the Example Design                                                                      |     |

| 6.7.1   |                                                                                                    |     |

| -       | gning with the IP                                                                                  |     |

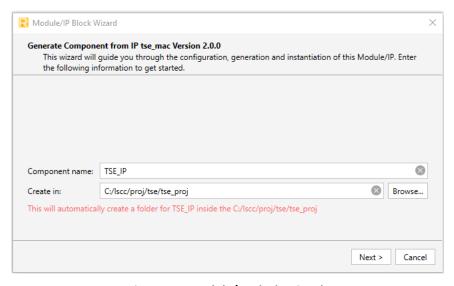

| 7.1.    | Generating and Instantiating the IP                                                                |     |

| 7.1.1   |                                                                                                    |     |

| 7.2.    | Design Implementation                                                                              |     |

| 7.3.    | Timing Constraints                                                                                 |     |

| 7.3.1   | • • • • • • • • • • • • • • • • • • • •                                                            |     |

| 7.3.2   | , , ,                                                                                              |     |

| 7.4.    | Specifying the Strategy                                                                            |     |

| 7.5.    | Running Functional Simulation                                                                      |     |

| 7.5.1   | 1 1 0 11 1                                                                                         |     |

| 7.5.2   | ( -, - , - , )                                                                                     |     |

| 7.5.3   | ` ' ' '                                                                                            |     |

| 7.5.4   | ( , )                                                                                              |     |

| 7.5.5   |                                                                                                    |     |

| 8. Knov | vn Issues                                                                                          |     |

| 8.1.    | RX Stat Vector Limitation for Carrier Event Previously Seen (bit[27]) and Packet Ignored (bit[26]) | 158 |

| 8.1.1   |                                                                                                    |     |

| 8.1.2   | 8                                                                                                  |     |

| 8.1.3   | . Issue Details                                                                                    | 158 |

| 8.1.4   |                                                                                                    |     |

| 8.2.    | Erroneous Length/Type Handling when the L/T is Smaller than 46                                     | 158 |

| 8.2.1   | . Devices Affected                                                                                 | 158 |

| 8.2.2   | . Designs Affected                                                                                 | 158 |

| 8.2.3   | . Issue Details                                                                                    | 158 |

| 8.2.4   | . Planned Fix                                                                                      | 158 |

| 8.3.    | Error Handling when rx_fifo_error_o is Asserted                                                    | 159 |

|         |                                                                                                    |     |

| 8.3.1.         | Devices Affected                                                                                | .159 |

|----------------|-------------------------------------------------------------------------------------------------|------|

| 8.3.2.         | Designs Affected                                                                                | .159 |

| 8.3.3.         | Issue Details                                                                                   | .159 |

| 8.3.4.         | Planned Fix                                                                                     | .159 |

| 8.4. SG        | MII Receiver Sampling Behavior at 100 Mbps and 10 Mbps                                          | .159 |

| 8.4.1.         | Devices Affected                                                                                | .159 |

| 8.4.2.         | Designs Affected                                                                                | .159 |

| 8.4.3.         | Issue Details                                                                                   | .159 |

| 8.4.4.         | Planned Fix                                                                                     | .159 |

| References     |                                                                                                 | .160 |

| Technical Sup  | port Assistance                                                                                 | .161 |

| Appendix A. R  | Resource Utilization                                                                            | .162 |

| Revision Histo | ory                                                                                             | .165 |

|                |                                                                                                 |      |

| Figures        |                                                                                                 |      |

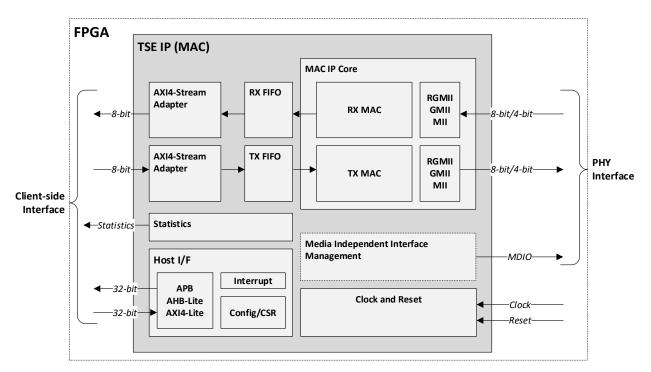

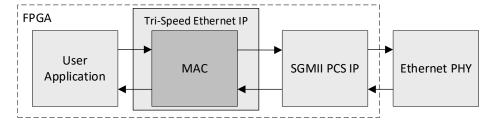

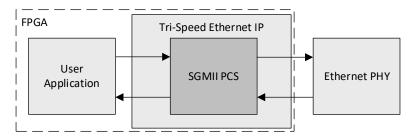

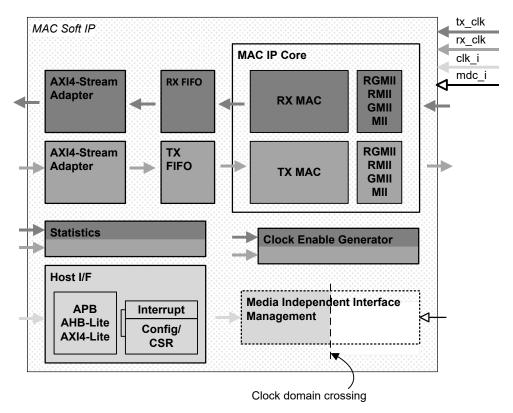

| _              | AC Block Diagram                                                                                | 16   |

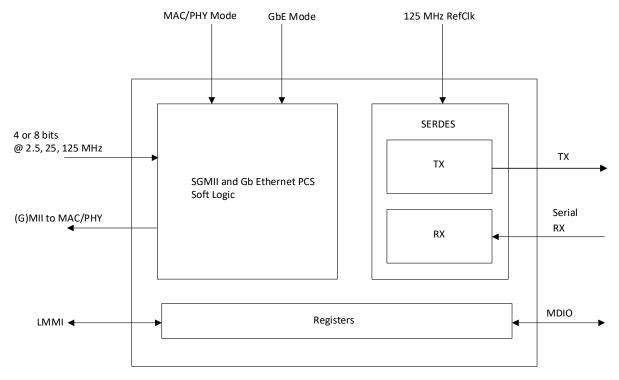

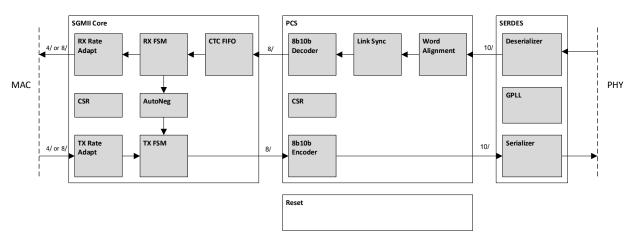

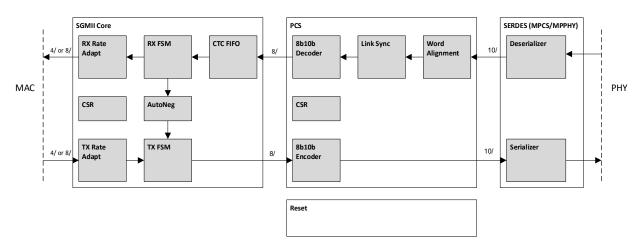

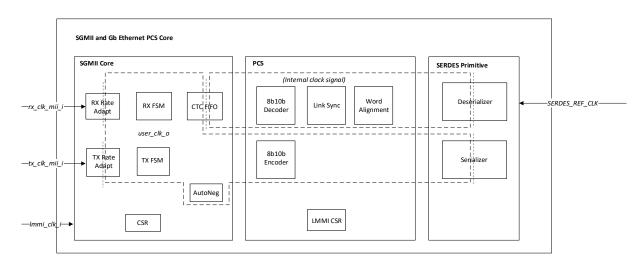

| •              | MII and Gb Ethernet PCS Block Diagram                                                           |      |

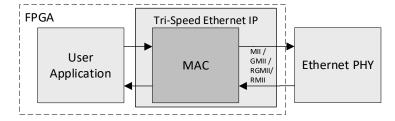

|                | E IP Connected to External PHY with MII/GMII/RGMII/RMII                                         |      |

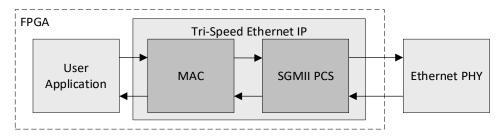

|                | E IP Connected to External Ethernet PHY with Serial Interface via Embedded SGMII PCS IP         |      |

| _              | E IP Connected to External Ethernet PHY with Serial Interface via SGMII PCS IP (Other Devices)  |      |

| -              | E IP Connected to External Ethernet PHY with Serial Interface via SGMII Only Mode (All Devices) |      |

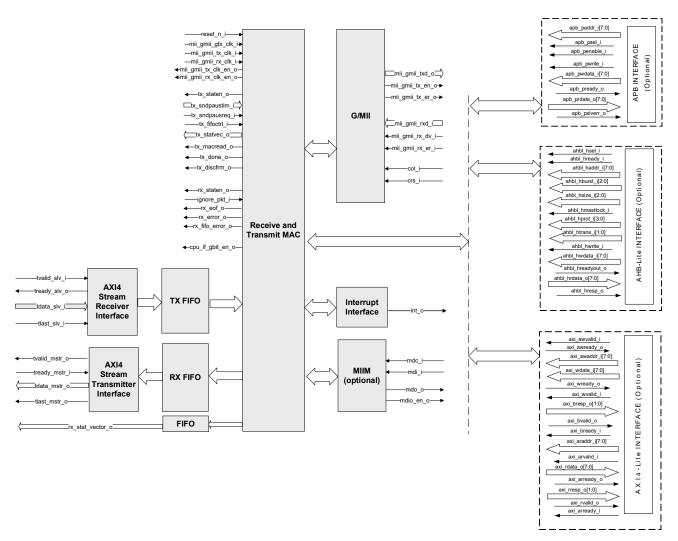

| •              | p-Level Block Diagram for the MII/GMII Configuration Option                                     |      |

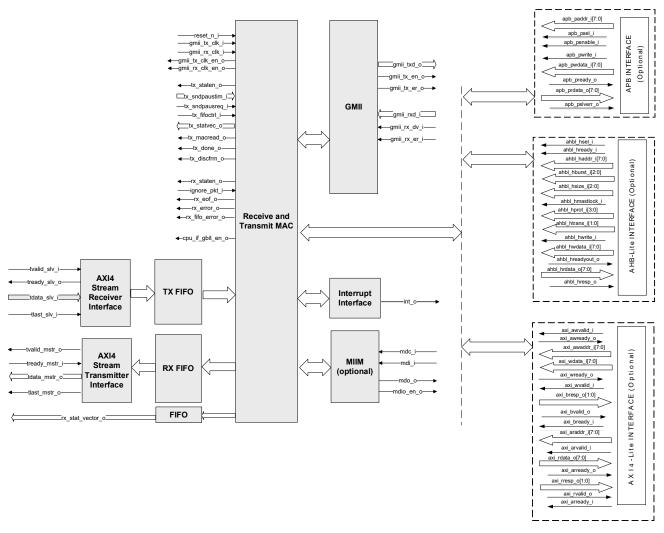

|                | p-Level Block Diagram for Gigabit MAC Configuration Option                                      |      |

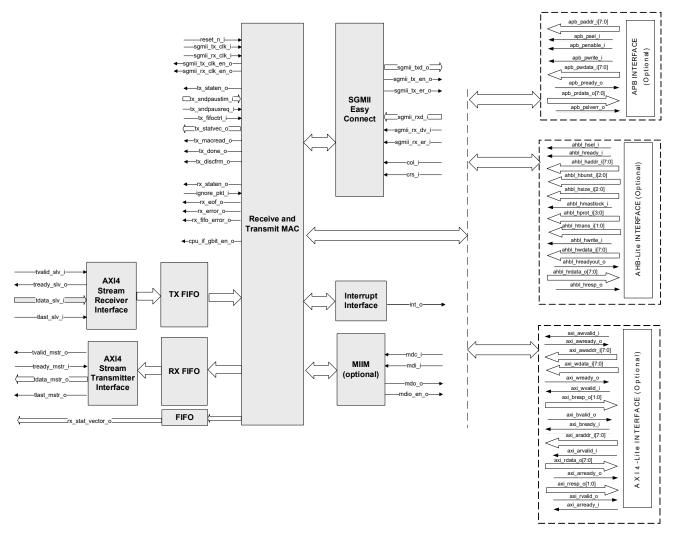

| _              | p-Level Block Diagram for the SGMII Easy Connect Configuration Option                           |      |

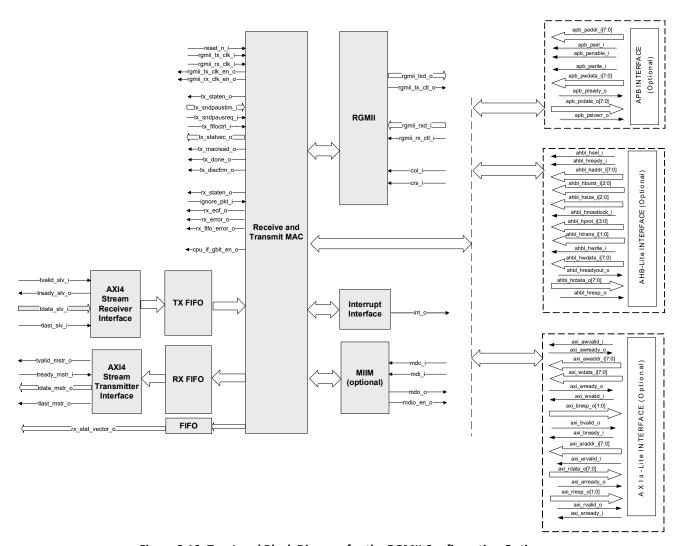

|                | op-Level Block Diagram for the RGMII Configuration Option                                       |      |

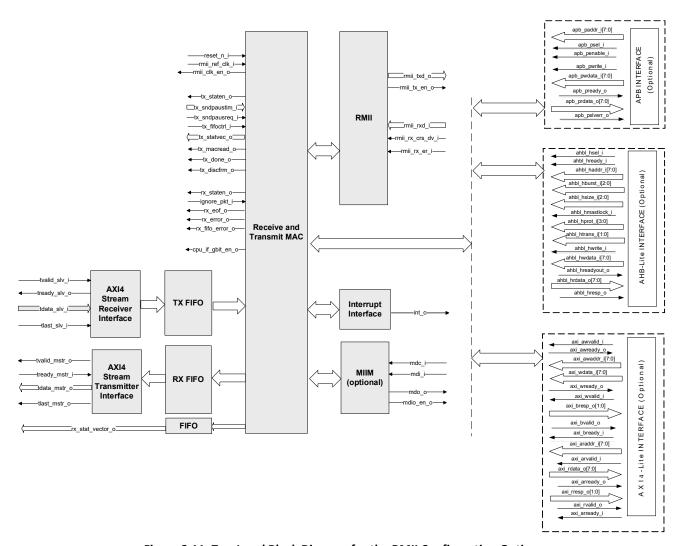

|                | op-Level Block Diagram for the RMII Configuration Option                                        |      |

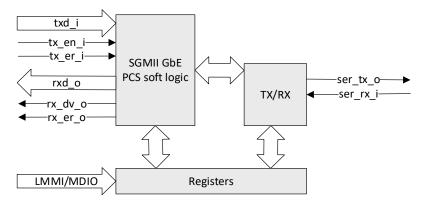

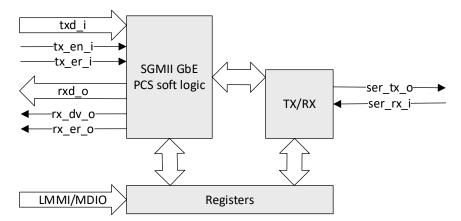

| _              | vetailed Block Diagram of the SGMII (LVDS) Only Mode                                            |      |

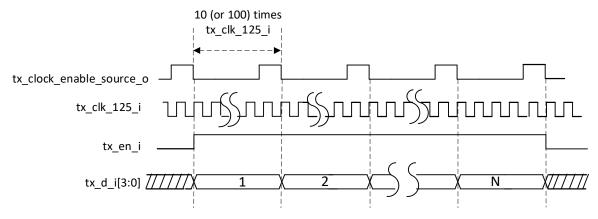

|                | GMII TX-Side Signals Relationship                                                               |      |

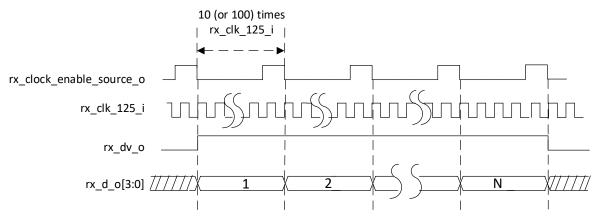

|                | GMII RX-Side Signals Relationship                                                               |      |

| _              | op-Level Block Diagram for MII/GMII Option                                                      |      |

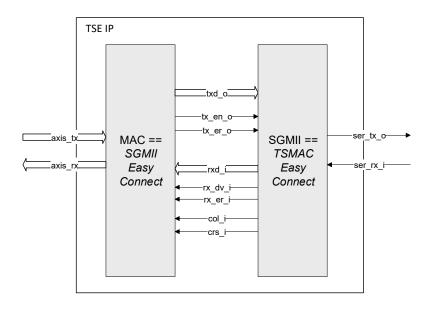

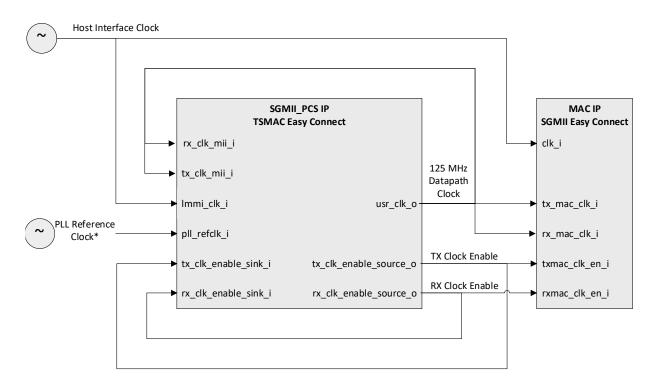

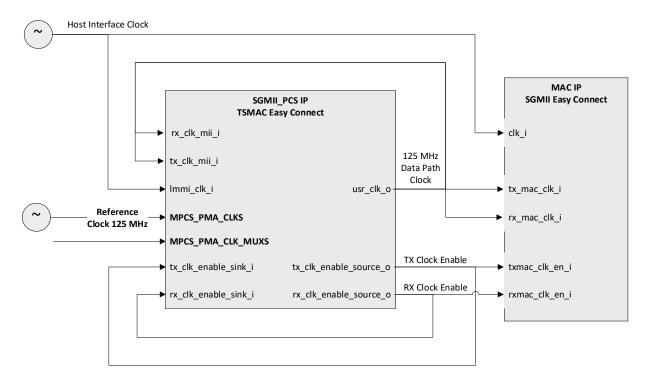

| _              | op-Level Block Diagram for TSMAC Easy Connect Option                                            |      |

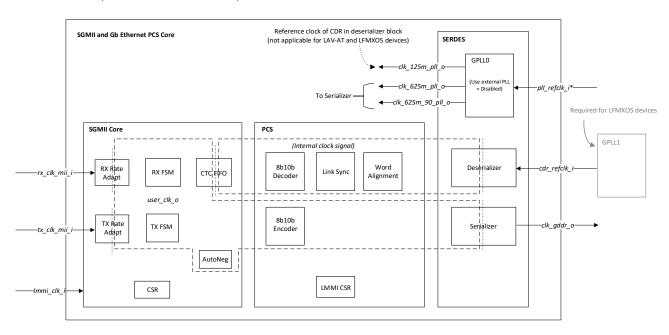

|                | vetailed Block Diagram of the SGMII (SERDES) Only Mode                                          |      |

|                | op-Level Block Diagram for Multi-Rate SGMII Ethernet Option                                     |      |

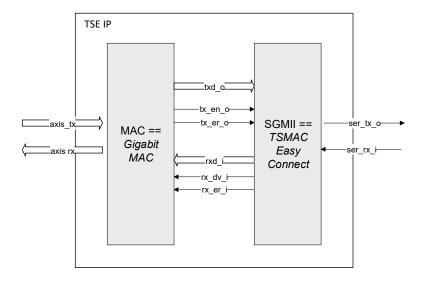

| -              | op-Level Block Diagram of Gigabit SGMII Ethernet Option                                         |      |

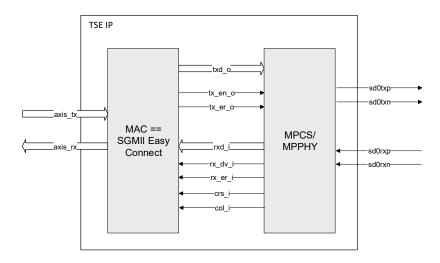

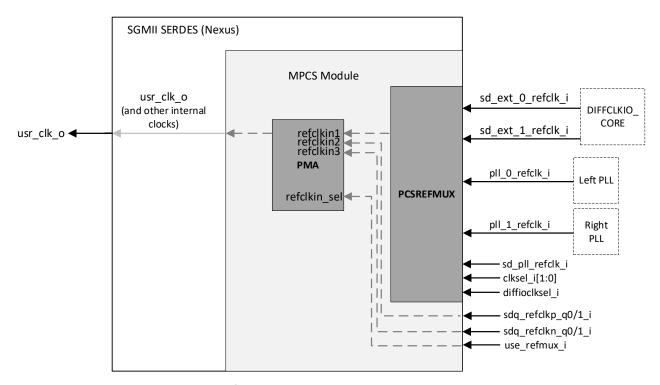

|                | op-Level Block Diagram of MPCS Gigabit Ethernet Option                                          |      |

|                | lock Network Diagram—Simplified Clock Scheme Design                                             |      |

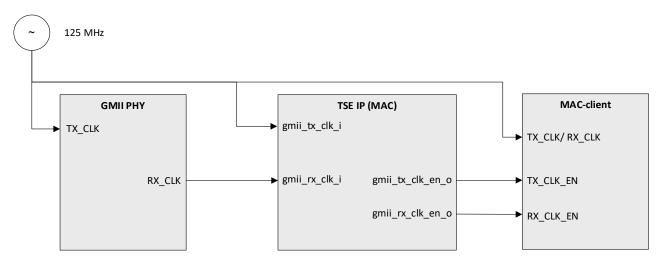

| _              | locking of Gigabit MAC—Simplified Clock Scheme Design                                           |      |

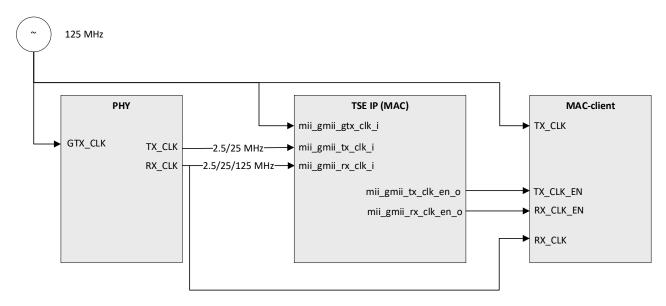

| _              | locking of MII/GMII—Simplified Clock Scheme Design                                              |      |

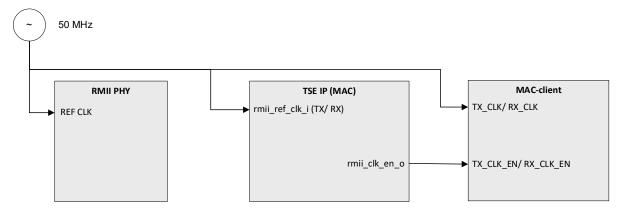

| _              | locking of RMII—Simplified Clock Scheme Design                                                  |      |

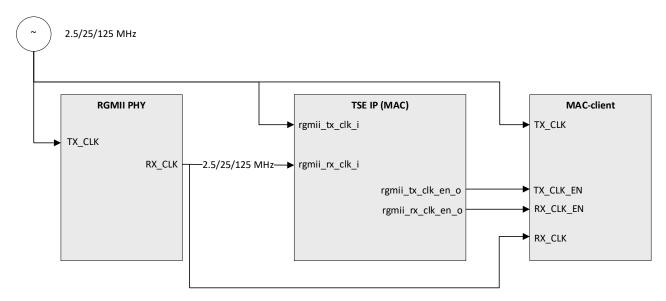

| _              | locking of RGMII—Simplified Clock Scheme Design                                                 |      |

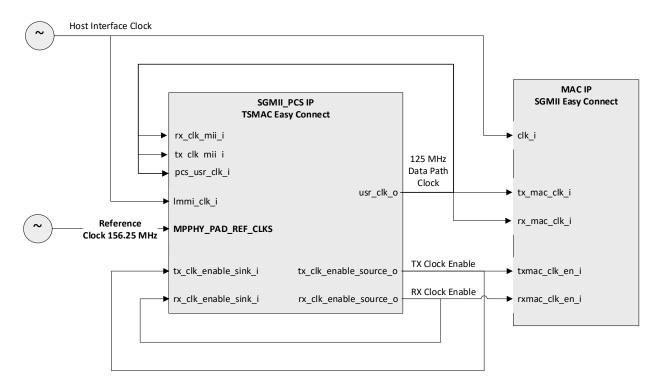

|                | locking of TSE IP MAC Option (Gigabit MAC) and SGMII PCS (TSMAC Easy Connect)—Simplified Clock  |      |

|                | n                                                                                               | 34   |

|                | lock Network Diagram of the SGMII (LVDS) Only Mode                                              |      |

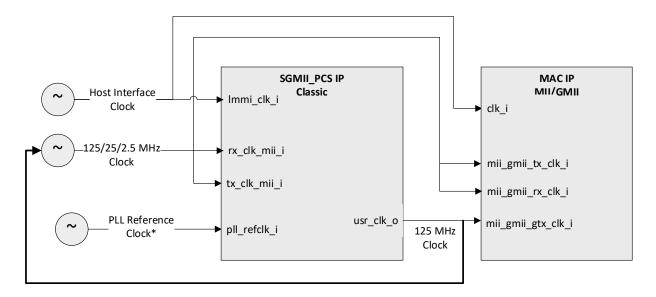

|                | locking of SGMII (LVDS) PCS in MII/GMII (Classic) Mode                                          |      |

| -              | locking of SGMII (LVDS) PCS in TSMAC Easy Connect Mode                                          |      |

| _              | lock Network Diagram, SGMII (SERDES) Only Mode                                                  |      |

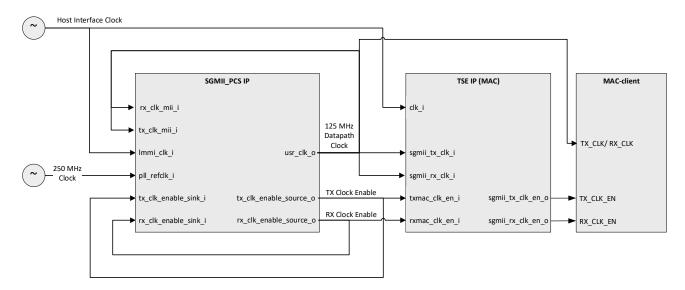

|                | locking of SGMII (SERDES) PCS in TSMAC Easy Connect Mode (Nexus Devices)                        |      |

| _              | eference Clock Dynamic Selection Block Diagram                                                  |      |

| _              | locking of SGMII (SERDES) PCS in TSMAC Easy Connect Mode (Avant Devices)                        |      |

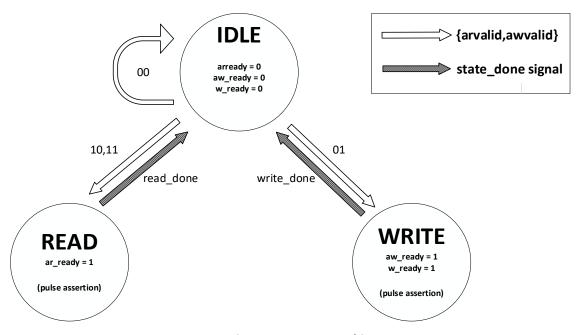

| -              | tate Machine                                                                                    |      |

| -              | In-Tagged Ethernet Frame Format                                                                 |      |

|                | LAN-Tagged Ethernet Frame Format                                                                |      |

| _              |                                                                                                 |      |

| Figure 2.37. Ethernet Control Frame Format                                                        | 42  |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 2.38. Set the Lane ID Configuration of the MAC + SGMII (SERDES)                            | 48  |

| Figure 2.39. Lane Merging Report File                                                             |     |

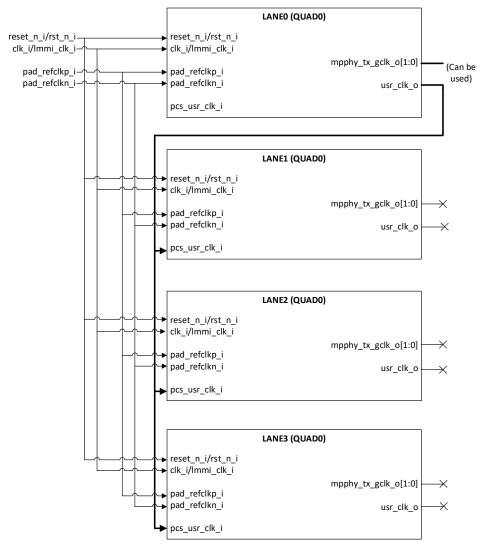

| Figure 2.40. Lane Merging Connection—SGMII (SERDES) only and MAC + SGMII (SERDES)                 |     |

| Figure 6.1. Top View of Avant-E Evaluation Board                                                  |     |

| Figure 6.2. Top View of the Avant-G/X Versa Board                                                 |     |

| Figure 6.3. Top View of CertusPro-NX Versa Board                                                  |     |

| Figure 6.4. Top View of CertusPro-NX Evaluation Board                                             |     |

| Figure 6.5. Top View of Ethernet FMC                                                              |     |

| Figure 6.6. RGMII_eval_top Block Diagram for Avant-E and CertusPro-NX Devices                     |     |

| Figure 6.7. RMII Block Diagram for CertusPro-NX Devices                                           |     |

| Figure 6.8. SGMII LVDS Example Design Block Diagram for Avant-X Devices                           |     |

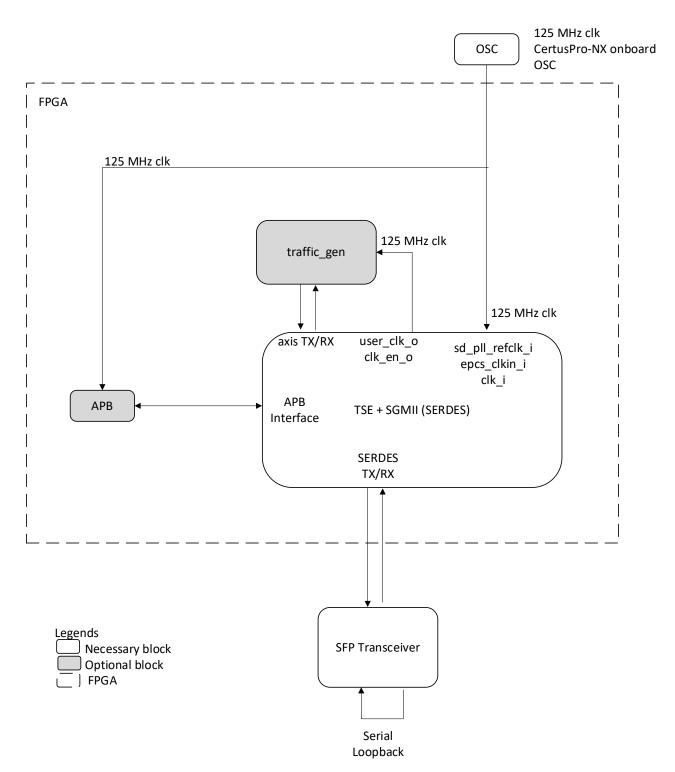

| Figure 6.9. SGMII SERDES Example Design Block Diagram for CertusPro-NX Devices                    |     |

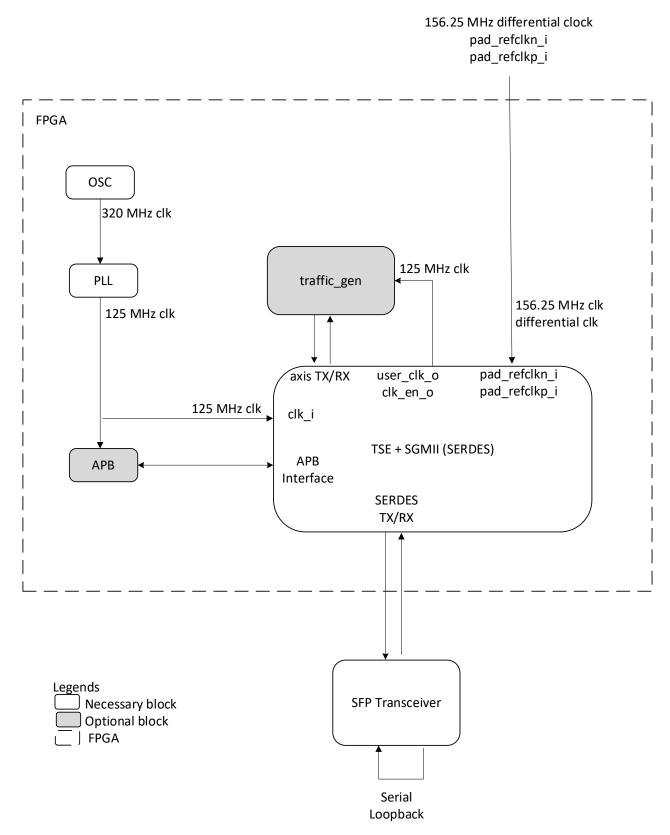

| Figure 6.10. SGMII SERDES Example Design Block Diagram for Avant-X Devices                        |     |

| Figure 6.11. Project Creation                                                                     |     |

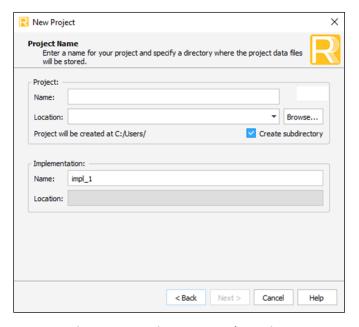

| Figure 6.12. Project Name and Location                                                            |     |

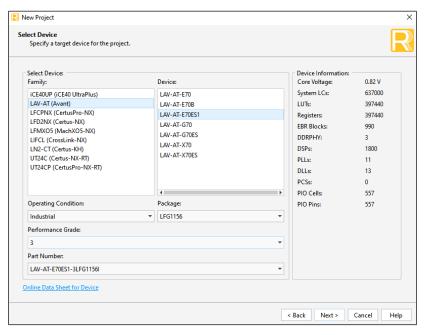

| Figure 6.13. Project Name and Eccation                                                            |     |

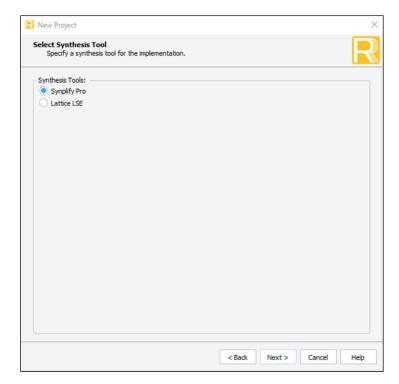

| Figure 6.14. Project Synthesis Tool                                                               |     |

|                                                                                                   |     |

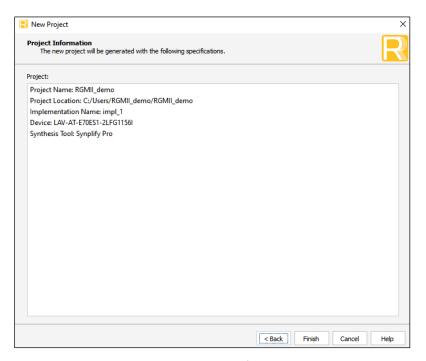

| Figure 6.15. Project Information                                                                  |     |

| Figure 6.16. Project Information                                                                  |     |

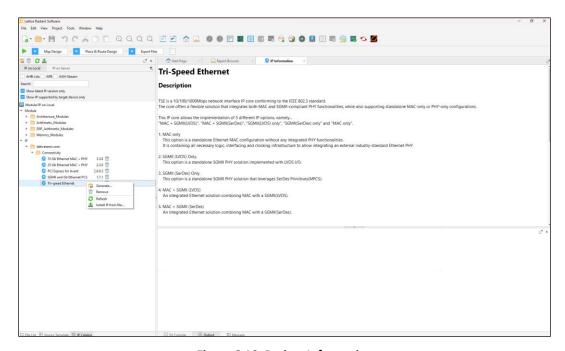

| Figure 6.17. IP Component                                                                         |     |

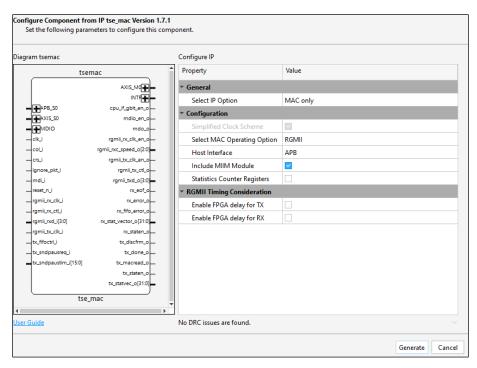

| Figure 6.18. IP Component Configuration – RGMII Example Design for Avant and CertusPro-NX Devices |     |

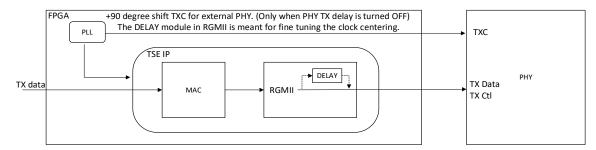

| Figure 6.19. TX Path Delay for RGMII                                                              |     |

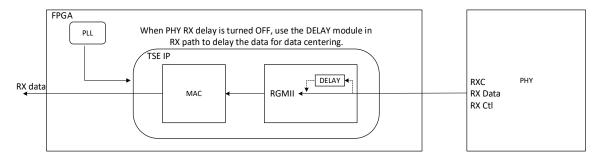

| Figure 6.20. RX Path Delay for RGMII                                                              |     |

| Figure 6.21. IP Component Configuration – SGMII LVDS Example Design for CertusPro-NX Devices      |     |

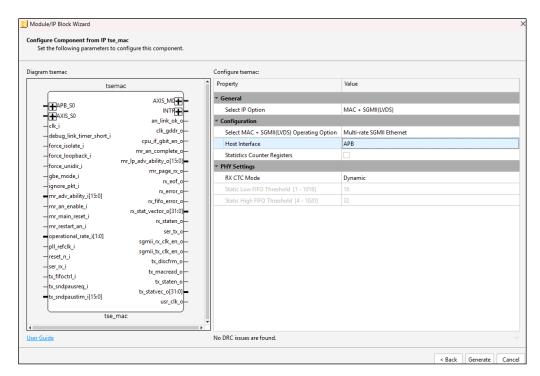

| Figure 6.22. IP Component Configuration – SGMII SERDES Example Design for Avant Devices           |     |

| Figure 6.23. IP Component Configuration – SGMII SERDES Example Design for CertusPro-NX Devices    |     |

| Figure 6.24. IP Components Configuration – RMII Example Design for CertusPro-NX Devices           |     |

| Figure 6.25. IP Generation Result                                                                 |     |

| Figure 6.26. Add an Existing File Using Graphical Interface                                       |     |

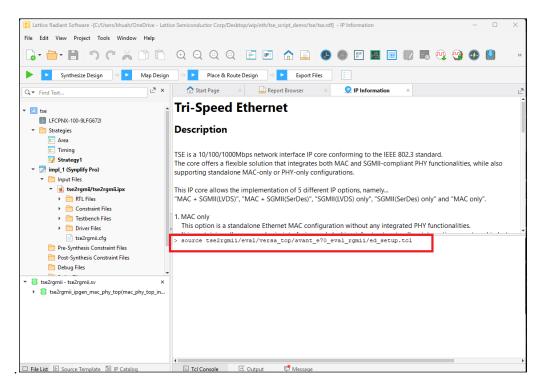

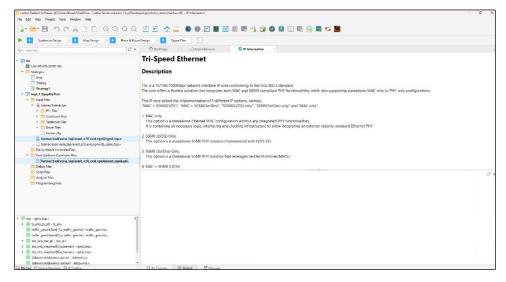

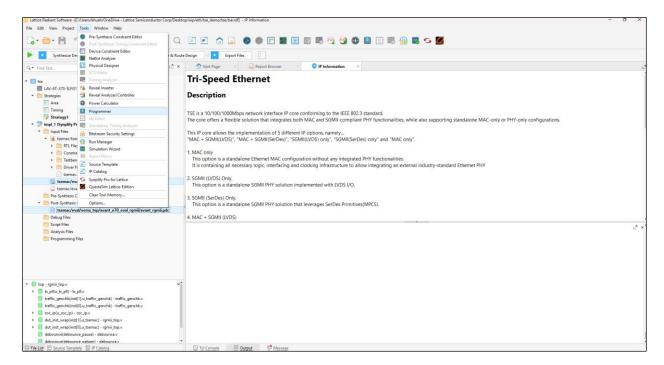

| Figure 6.27. Set Up Example Design Using TCL                                                      |     |

| Figure 6.28. Speed and Clock Alignment Param in rgmii_avant_e versa_toptop                        |     |

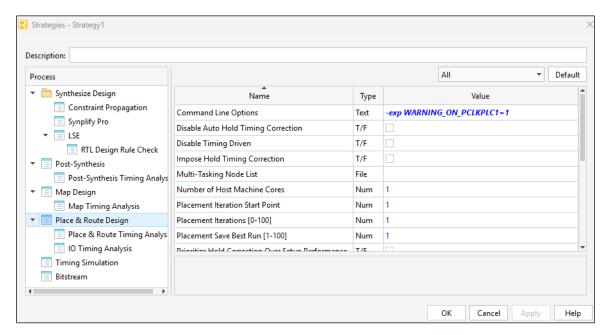

| Figure 6.29. Strategy Interface for Command Line Options in Place & Route Design                  |     |

| Figure 6.30. Set False Path Constraints in the .pdc file for Low-Speed RGMII                      |     |

| Figure 6.31. Generate Bitstream                                                                   |     |

| Figure 6.32. Bitstream Completion                                                                 | 132 |

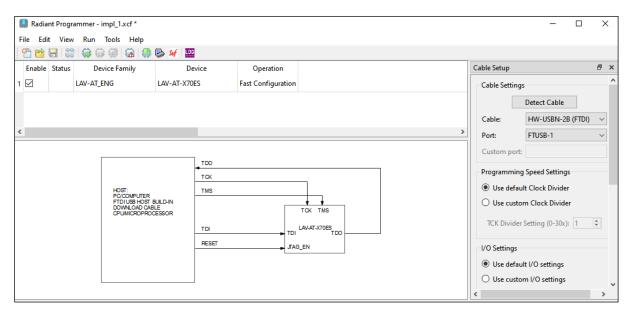

| Figure 6.33. Programmer                                                                           | 132 |

| Figure 6.34. Select Bitstream                                                                     | 133 |

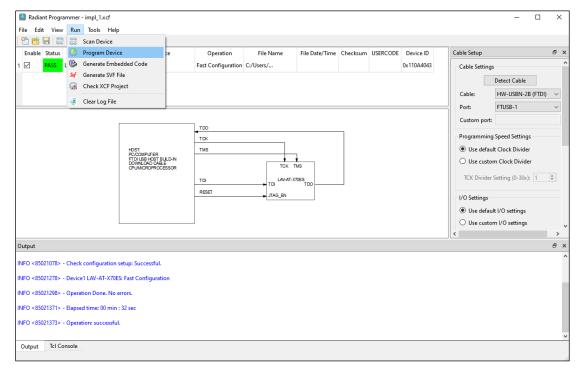

| Figure 6.35. Programming Bitstream                                                                | 133 |

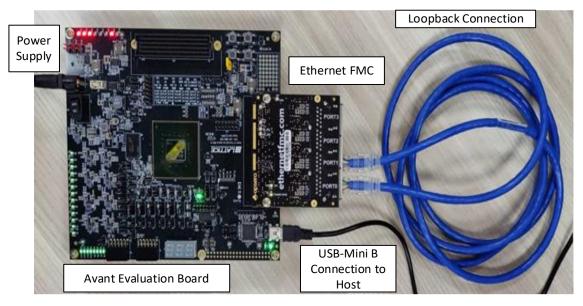

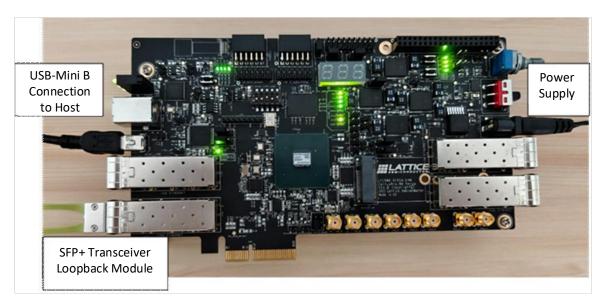

| Figure 6.36. Avant Evaluation Board and FMC Setup                                                 | 135 |

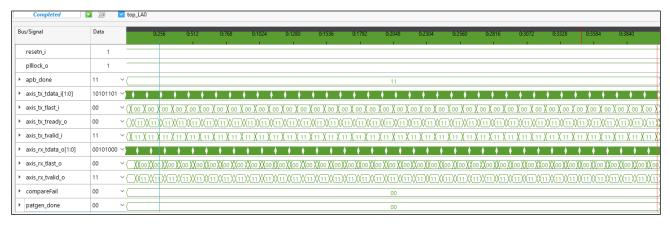

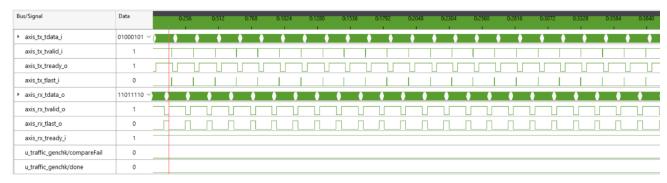

| Figure 6.37. Signals Shown on the Reveal Tool                                                     | 135 |

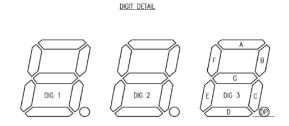

| Figure 6.38. 7-Segment LED from Avant-AT-X Devices                                                | 138 |

| Figure 6.39. Continuous Traffic Configuration from versa_top                                      | 138 |

| Figure 6.40. 7-Segment LED Sample of a Successful Transmission                                    | 138 |

| Figure 6.41. 7 Signals Shown on the Reveal Tool                                                   |     |

| Figure 6.42. 7-Segment LED from Avant-AT-X Devices                                                |     |

| Figure 6.43. Parameters for Frame Size in the Top File                                            |     |

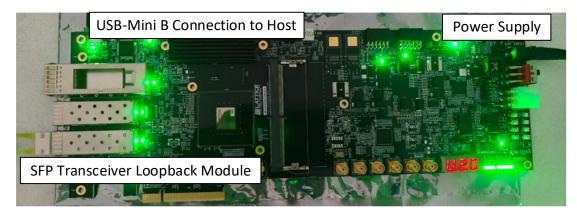

| Figure 6.44. Avant-X Versa Board with SFP Transceiver Loopback Module                             |     |

| Figure 6.45. Signals shown on the Reveal Tool                                                     |     |

| Figure 6.46. CertusPro-NX Versa Board with SFP+ Transceiver Loopback Module                       |     |

| Figure 6.47. Signals shown on the Reveal Tool                                                     |     |

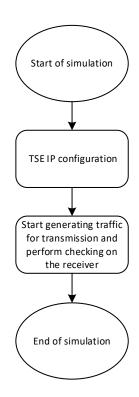

| Figure 6.48. SGMII Versa Testbench Example Design Flowchart                                       |     |

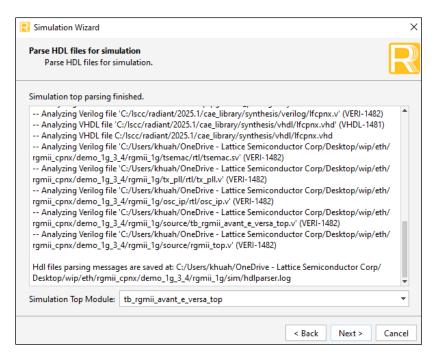

| Figure 6.49. Simulation Wizard Top Module Selection                                               |     |

| Figure 6.50. Simulation Results for MAC+SGMII (LVDS) Loopback                                     |     |

| · · · · · · · · · · · · · · · · · · ·                                                             |     |

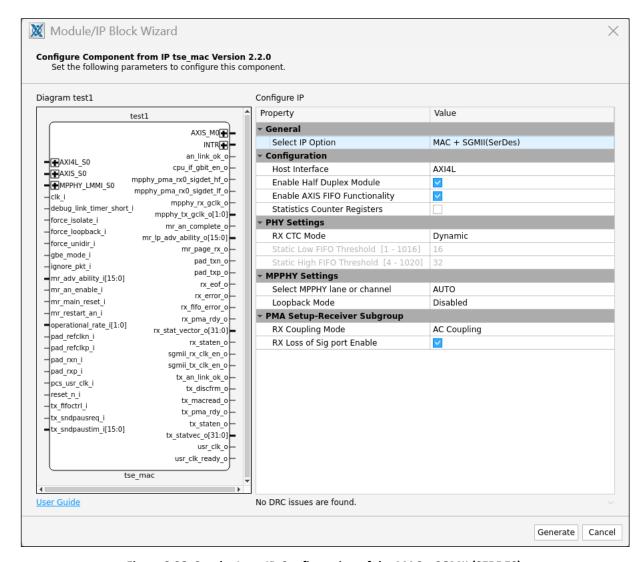

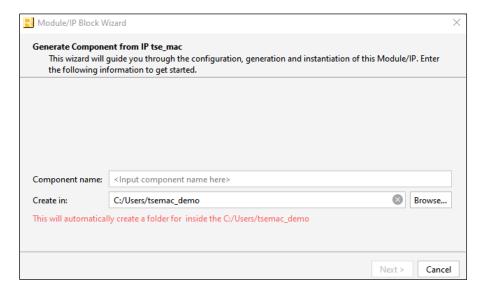

| Figure 7.1. Module/IP Block Wizard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 146 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

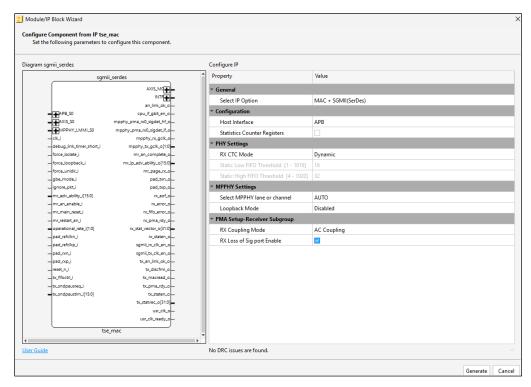

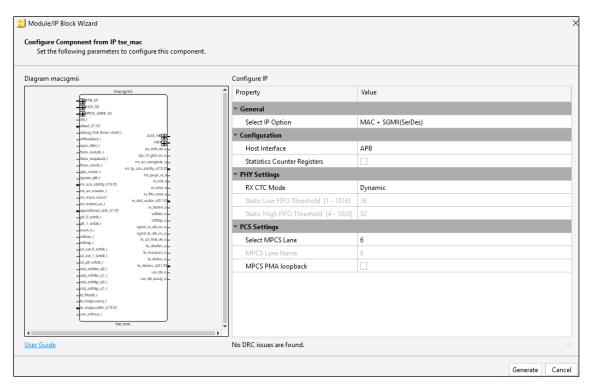

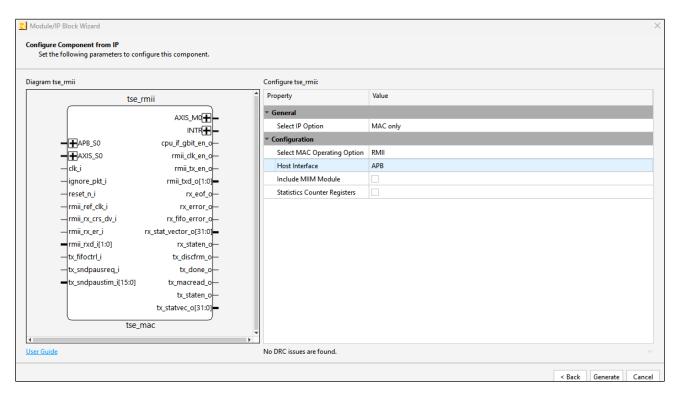

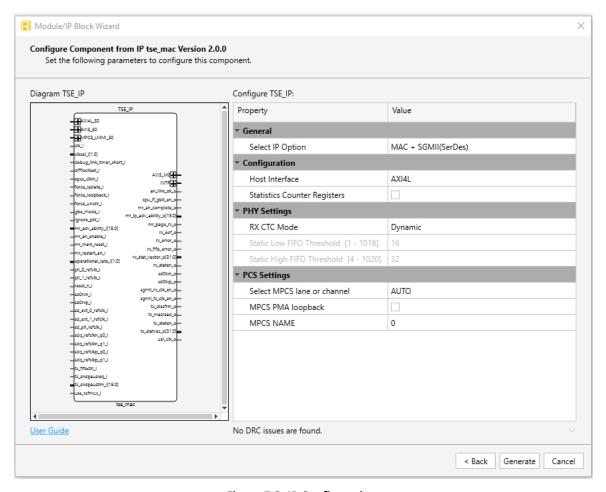

| Figure 7.2. IP Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 147 |

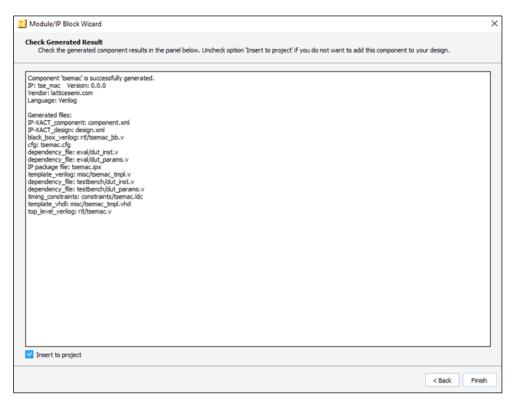

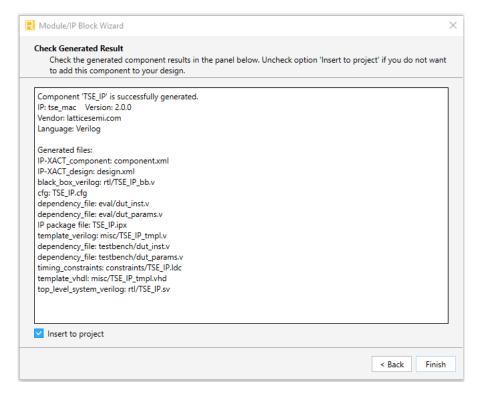

| Figure 7.3. Check Generated Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 148 |

| Figure 7.4 Timing Constraint File (.sdc) for the TSE IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 149 |

| Figure 7.5 Nexus SERDES Clocks Constraint File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

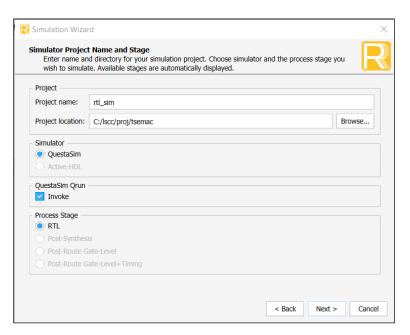

| Figure 7.6. Simulation Wizard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

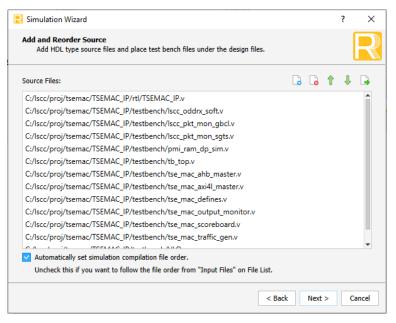

| Figure 7.7. Add and Reorder Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

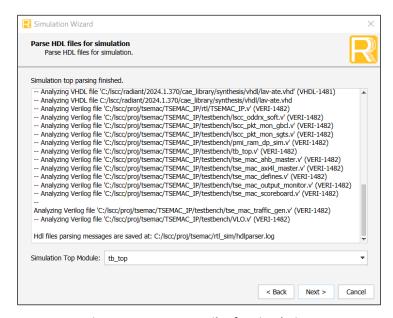

| Figure 7.8. Parse HDL Files for Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

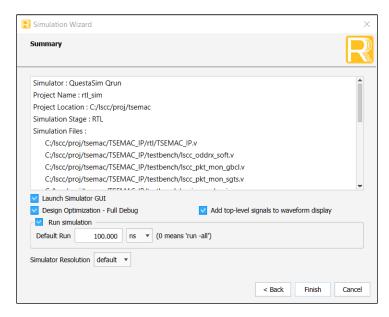

| Figure 7.9. Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

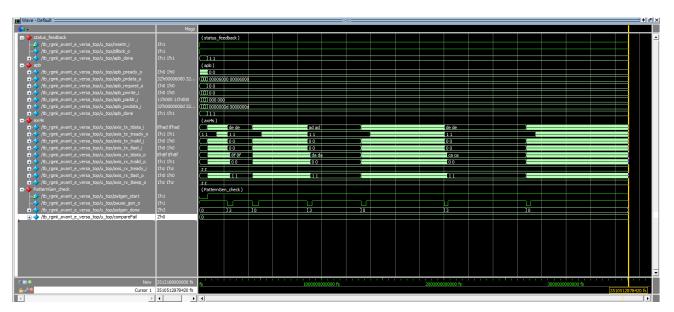

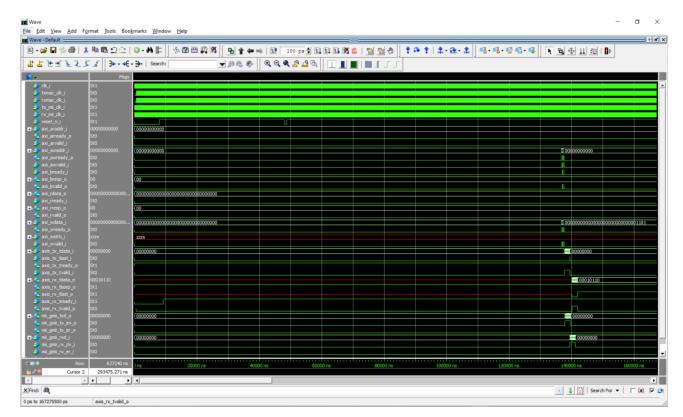

| Figure 7.10. Simulation Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

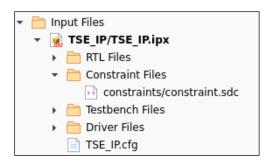

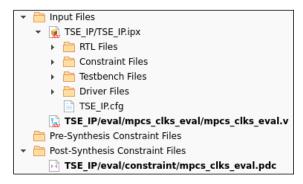

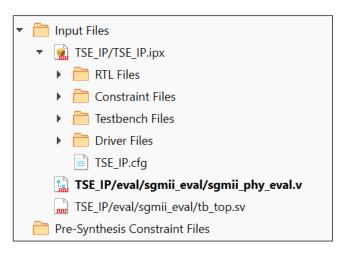

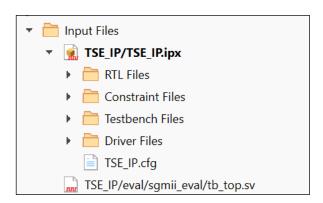

| Figure 7.11. Add SGMII Evaluation Top and Testbench in Input Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Figure 7.12. Add SGMII Testbench in Input Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

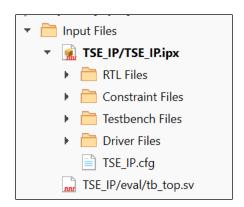

| Figure 7.13. Add MAC + SGMII Evaluation Top Testbench in Input Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

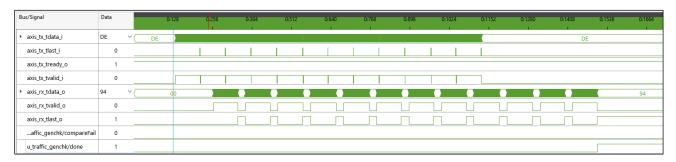

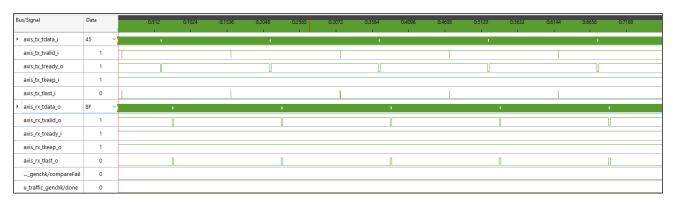

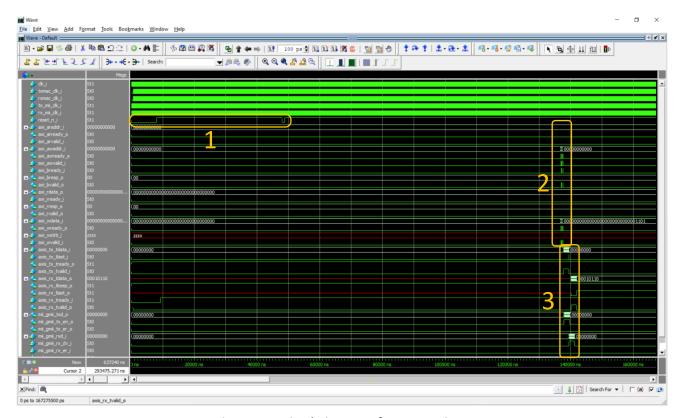

| Figure 7.14. Simulation Waveform: Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

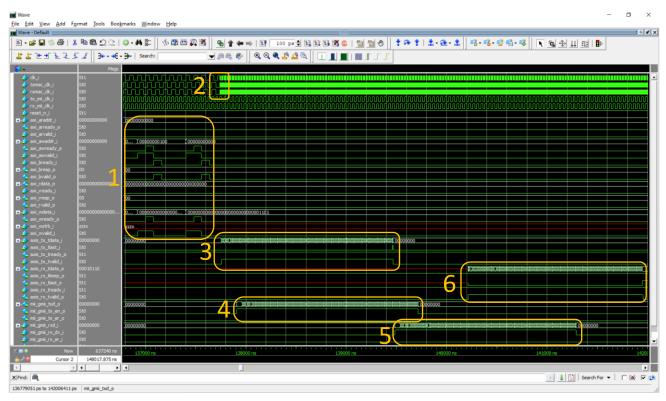

| Figure 7.15. Simulation Waveform: Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| Figure 7.16. Simulation Output: Beginning of the Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Figure 7.17. Simulation Output: Transmitted Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Figure 7.18. Simulation Output: Received Frame and End of Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15/ |

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Table 1.1. Summary of the TSE IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12  |