# Programming Tools User Guide

### Copyright

Copyright © 2016 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

# **Type Conventions Used in This Document**

| Items in the user interface that you select or click. Text that you type into the user interface. |

|---------------------------------------------------------------------------------------------------|

| Variables in commands, code syntax, and path names.                                               |

| Press the two keys at the same time.                                                              |

| Code examples. Messages, reports, and prompts from the software.                                  |

| Omitted material in a line of code.                                                               |

| Omitted lines in code and report examples.                                                        |

| Optional items in syntax descriptions. In bus specifications, the brackets are required.          |

| Grouped items in syntax descriptions.                                                             |

| Repeatable items in syntax descriptions.                                                          |

| A choice between items in syntax descriptions.                                                    |

|                                                                                                   |

Chapter 1

# **Contents**

Programming Tools Description 9

|           | Programmer 9 Deployment Tool 9 Programming File Utility 10 Download Debugger 10 Model 300 10 Embedded Flow 10 Driver Installation 11                                                                                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | Programmer Overview 13  Usage and flow 14  Programmer Design Flow 14  Programming Basics 14  In-System Programming 16  Programming Algorithm Basics 16  Programming Times 17  USERCODE 18  Programming Hardware 19  Programming Software 19  Embedded Programming 20  FPGA Configuration 20  Serial Peripheral Interface Flash 20 |

| Chapter 3 | Deployment Tool Overview 21  Deployment Tool Function Types 23  Output File Types 23  File Conversion Output File Types 23  Tester Output File Types 24  Embedded System Output File Types 25  External Memory Output File Types 27                                                                                               |

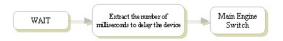

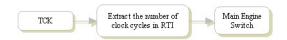

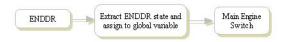

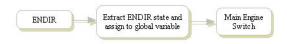

#### Chapter 4 **Embedded Flow Overview** JTAG Full VME Embedded 40 VME File Format 40 JTAG Full VME Embedded Flow 43 JTAG Full VME Embedded System Memory 44 JTAG Full VME Embedded Basic Operation 44 VME Source Code 45 JTAG Full VME Embedded Programming Engine 46 RAM Size Requirement for VME 47 ROM Size Requirement for JTAG Full VME Embedded 49 JTAG Full VME Embedded Required User Changes 49 Program Memory Requirement 51 Program Memory Allocation 51 Sample Program Size 52 VME File Size 53 Using JTAG Full VME Embedded 61 Generating VME Files 61 Testing VME Files 62 Converting an SVF File to VME File 62 Choosing the File-Based or EPROM-Based Version 62 Customizing for the Target Platform 63 Advanced Issues 63 EPROM-based JTAG Full VME Embedded User Flow 63 Programming Engine Flow 65 VME Byte Codes **79** Unsupported SVF Syntax 82 JTAG Slim VME Embedded 83 JTAG Slim VME Embedded Source Code 84 Using the PC-based JTAG Slim VME Embedded 85 Using the 8051-based JTAG Slim VME Embedded 86 VME Algorithm Format 86 VME Data Format 89 VME Required User Changes 90 Program Memory Requirement 91 Program Memory Allocation 92 Sample Program Size 93 VME File Size 93 Generating JTAG Slim VME Embedded Files 94 JTAG Slim VME Embedded Source Code 95 8051 JTAG Slim VME Embedded User Flow 96 Programming Engine Flow 97 VME Algorithm and Format 108 Slave SPI Embedded 110 Requirements 110 Slave SPI Embedded Algorithm Format 112 Slave SPI Embedded Data Format 113 Generating Slave SPI Embedded Files 113 Modifications 114 Usage 120 Return Codes from Slave SPI Embedded 120 Programming Considerations for SSPIEM modification with Aardvark SPI APIs 121 I2C Embedded 121

```

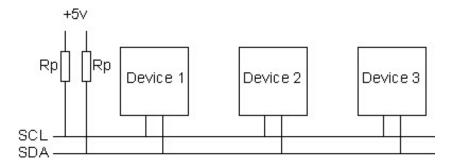

Masters and Slaves 122

MachXO2 or MachXO3L Slave I2C Programming 122

Using the PC-based I2C Embedded Programming 123

Using the 8051-based I2C Programming 124

I2C Algorithm Format 125

I2C Data Format 126

I2C Embedded Programming Required User Changes 127

Generating I2C Files 128

Programming Considerations for SSPIEM and I2CEM modification with

Aardvark I2C APIs 132

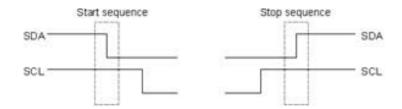

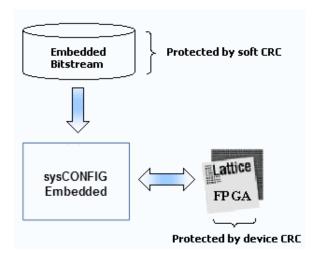

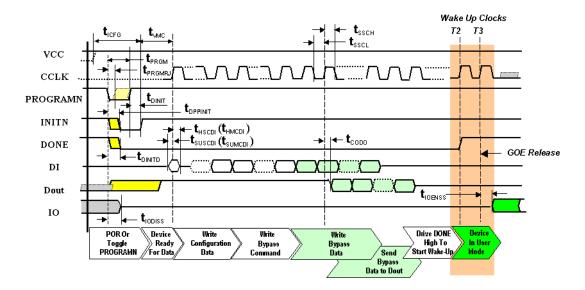

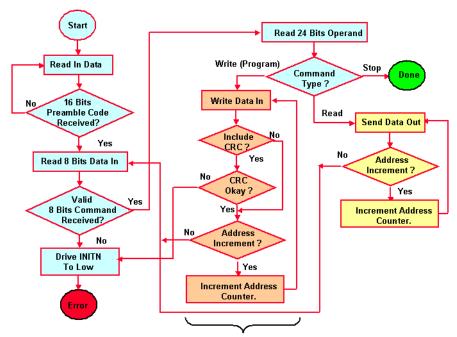

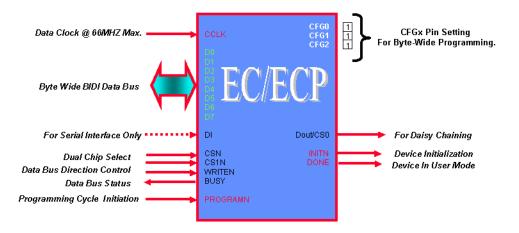

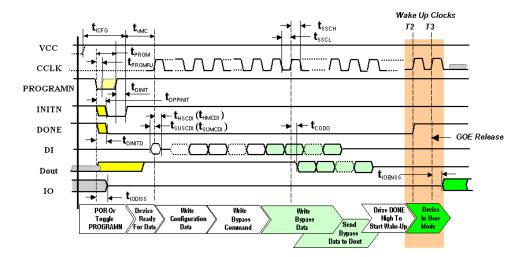

sysCONFIG Embedded 132

sysCONFIG Embedded Flow 133

sysCONFIG Embedded Bitstream Format 134

sysCONFIG Embedded Bitstream Structure 135

sysCONFIG Embedded Basic Operation 136

sysCONFIG Embedded Source Code 137

sysCONFIG Embedded Engine 138

Sample Program Size 140

Generating a sysCONFIG Embedded Bitstream 141

sysCONFIG SPI Port AC Parameters 142

sysCONFIG Interface 145

```

Index 157

# **Programming Tools Description**

This user guide is intended to provide users with basic information, and references on where to find more detailed information, to assist in configuring and programming Lattice devices using Diamond Programmer and related tools including Deployment Tool, Programming File Utility, Download Debugger, and Model 300 Programmer.

### **Programmer**

Diamond Programmer is a system for programming devices. The software supports both serial and concurrent (turbo) programming of Lattice devices using PC and Linux environments. The tool also supports embedded microprocessor programming. Refer to "Programmer Overview" on page 13.

### **Deployment Tool**

Deployment Tool is a stand-alone tool available from the Diamond Accessories. The Deployment Tool graphical user interface (GUI) is separate from the Diamond design environment.

The Deployment Tool allows you to generate files for deployment for single devices, a chain of devices, and can also convert data files to other formats and use the data files it produces to generate other data file formats. Refer to "Deployment Tool Overview" on page 21.

### **Programming File Utility**

Programming File Utility allows the viewing and editing of different format programming files. The Programming File Utility is a stand-alone tool that allows you to view and compare data files. When comparing two data files, the software generates an output (.out) file with the differences highlighted in red.

Detailed information and procedures on how to use the Programming File Utility are contained in the "Using Programming File Utility" section of the Lattice Diamond online help or in the stand-alone Programming File Utility online help.

### **Download Debugger**

Download Debugger is a utility for debugging programming for debugging Serial Vector Format (SVF) files, Standard Test And Programming Language (STAPL) files, and Lattice Embedded (VME) files. Download Debugger allows you to program a device, and edit, debug, and trace the process of SVF, STAPL, and VME files. Download Debugger also allows you to create, edit, or view a VME file in hexadecimal format.

Detailed information and procedures on how to use the Download Debugger are contained in the "Debugging SVF, STAPL, and VME Files" section of the Lattice Diamond online help or in the stand-alone Download Debugger online help.

### **Model 300**

The Model 300 Programmer is a simple engineering device programmer that allows you to perform single-device programming directly from a PC or Linux environment. The Model 300 Programmer software and hardware support all JTAG devices produced by Lattice, with device Vcc of 1.8, 2.5, 3.3, and 5.0V.

Detailed information and procedures on how to use the Model 300 hardware and software are contained in the "Using the Model 300 Programmer" section in the Lattice Diamond online help or in the stand-alone Model 300 online help.

### **Embedded Flow**

Programming flow using a processor to read the contents of a stored programming file and programming the FPGA. Lattice provides the option to generate several different file formats for different embedded target options. Refer to "Embedded Flow Overview" on page 29.

# **Driver Installation**

A utility is available for installing programming drivers after the Diamond or Programmer software has been installed. Refer to the topic "Installing/ Uninstalling Parallel Port Driver and USB Driver on a PC" in the Lattice Diamond online help or in the stand-alone Programmer online help.

# **Programmer Overview**

Diamond Programmer is integrated into the Lattice Diamond software, and is also available as a standalone tool. Both versions come with online help that provides essential information for using the tool to program Lattice devices. The two versions are virtually identical, except for the following differences:

**Integrated Mode** When Programmer is used in integrated mode, it checks that the bitstream (.bit) or JEDEC file (.jed) selected in the Diamond project (.xcf) matches the file generated by the project. If the file does not match when the file is originally selected, a warning dialog informs the user that the file is not the one generated by the project. If an existing .xcf is opened, and the file is not the correct one generated by the project, the file section for that device is highlighted in red in the Diamond graphical user interface.

**Standalone Mode** The stand-alone Programmer supports mature Lattice devices. A "Mature Device" license feature (LSC\_PROGRAMMER\_MATURE) is required in your license file to enable these devices. Without the license, Programmer will list the mature devices in the Device Selection and will be able to Scan the devices, but will not be able to program mature devices. The only operation available is Bypass. With the Mature Device license, full support is available.

Diamond Integrated Programmer (Programmer integrated into the Lattice Diamond software) will list the mature devices in the Device Selection and will be able to Scan the devices, but will not be able to program mature devices, even with the Mature Device license. The only operation available is Bypass.

Full support is only available when running Diamond Programmer as a standalone tool.

### **Usage and flow**

Programming is the process changing the state of a non-volatile programmable element (such as embedded Flash and external SPI Flash devices) by downloading data from JEDEC, bitstream, or hex files transmitted to the download cable through the host computer's serial communications port; from an embedded system; or from a third party programmer.

Configuring is the process of changing the state of a volatile programmable element (such as SRAM in the FPGA).

Before programming or configuring an FPGA, you need to create and verify your design, and then generate data files. To download a data file into the target device, use the Programmer tool which is integrated into the Diamond software, and also available in a standalone version.

# **Programmer Design Flow**

The design flow for creating and downloading a design chain is the same, whether you select the devices and settings from the software or use an existing chain configuration file.

- Create a design and compile it to a JEDEC, ISC, hex, or bitstream data file.

- Using Programmer, create a new chain configuration or open an existing one.

- 3. Add devices to the chain, and select the data file and operation for each.

- 4. Arrange the order of the devices in the chain and edit the options for each device as needed.

- 5. Program the daisy-chained devices using the Program toolbar command.

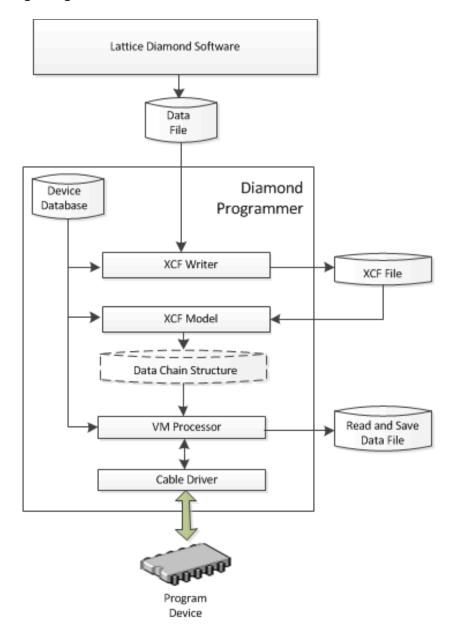

Figure 1 on page 15 describes the Lattice programming process.

### **Programming Basics**

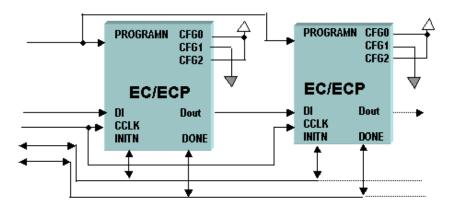

To successfully program devices in-system, there are a few simple requirements that must first be met. The first of these requirements is that the devices on the board must be correctly connected into an 1149.1 scan chain. This scan chain can be used for either programming or testing the board.

To program using Programmer a description of the scan chain must be developed. This description, called a chain file, contains basic information about all of the devices in the chain. For the Lattice devices, it includes the device type, the operation to be performed, and the data file, if required by the operation. Additional information in the chain file can include the state of the I/O pins during programming, along with security requirements. If the chain includes non-Lattice devices, the instruction register length is required for these devices. The instruction register length can be found from the BSDL file or the SVF file for the device.

**Figure 1: Programming Design Flow**

Another requirement for successful programming is thoughtful board design. The signals used in a scan chain (TCK, TMS, TDI, and TDO) rarely operate as fast as the data path signals on the board. However, correct board layout methodologies, such as buffering for large chains and termination resistors, are required to ensure trouble-free operation. Some Lattice devices have some additional pins (TRST, ispEN, PROGRAMN, INITN, DONE, SLEEPN, and TOE) that can affect boundary scan programming and test if not taken care of properly.

After all of these requirements have been met, it should be relatively straightforward to program any number of devices on a board. You can

program the devices using a PC or Linux system and a board test system connected by one of the following cables:

- A Lattice parallel port cable with the 8-pin AMP connector or 10-pin JEDEC connector

- A Lattice USB port cable

# **In-System Programming**

After you have compiled your design to a data file (JEDEC, hex, or bitstream) and device programming is necessary, you must serially shift the fuse map (a fuse map file is a design file that has the fuse data already pre-arranged in exactly the same format as the physical layout of the fuse array of the device) data into the device along with the appropriate addresses and commands.

Lattice non-volatile FPGA devices use embedded flash memory and require only TTL-level programming signals. An integrated state machine controls the sequence of programming operations, such as identifying the device, shifting in the appropriate data and commands, and controlling internal signals to program and erase the embedded Flash in the device. Programming consists of serially shifting the logic implementation stored in a data file into the device along with appropriate addresses and commands, programming the data into the embedded Flash, and shifting the data from the logic array out for device programming verification.

Most of Lattice's devices use the IEEE 1149.1-1993 Boundary Scan Test Access Port (TAP) as the primary interface for in-system programming.

### **Programming Algorithm Basics**

Programming a device is similar to programming any piece of memory, such as an EPROM or a Flash memory. The device can be thought of as an array that is programmed one row at a time. The programming information is provided to the software in the form of a data file that must be converted into the row and column fuse map data. Before a non-volatile device can be programmed, it first has to be erased. After the device has been erased, the programming data can be loaded and the device programmed. After the device has been programmed, it will be verified by reading out the data in the device and comparing it to the original.

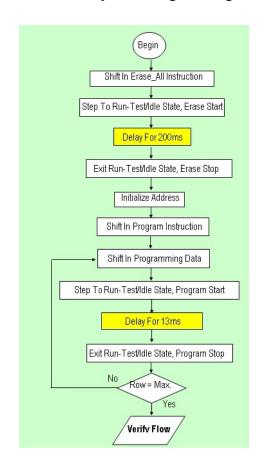

Figure 2 on page 17 shows the basic programming flow for the device. It does not include the data file conversion into fuse map data, for it assumes that

step has already been done. This programming flow will be the same, regardless of the programming hardware used.

Start reload Preload/Save I/Os or Save Using SAMPLE/PRELOAD O States No Enter Programming Mode Erase Device Program Device Verify Device Program Security Device? No Exit Programming Mode Reset Device End

Figure 2: Basic Device Programming Flow

#### Note

If the device will not be programmed in-circuit (that is, by a cable or an embedded processor), it is not necessary to preload or save the I/O states.

# **Programming Times**

The time it takes to program a device can often determine where in the manufacturing process a device, or group of devices, is programmed. A board test system costing hundreds of thousands of dollars to purchase and as much as one dollar per minute to operate can be an expensive alternative to programming if programming times are too long. In many instances, it is more cost-effective to buy a couple of PCs and program the devices using these much cheaper systems.

The time it takes to completely program a device is based on the time it takes to first erase the device, then to program each row in the device, and finally to

verify the device. The erase time for all devices is between 100 ms and 200 ms. A single row is programmed in 10 ms to 50 ms, depending on the device. The verification process is the quickest of the required steps in the programming sequence and mainly depends on the time required to shift the verification data out of any given device.

The benefit of minimal programming times is much more obvious on board test systems, because they are included as a part of the test program and are running at the fastest speed possible. Additionally, there is no translation needed to or from the data file, since this has already been done by Programmer.

### **USERCODE**

User-programmable identification can ease problems associated with document control and device traceability. Every Lattice 1149.1-compliant device contains a 32-bit register that is accessible through the optional IEEE 1149.1 USERCODE instruction. This user-programmable ID register is basically a user's notepad provided in Flash or SRAM cells on each device.

In the course of system development and production, the proliferation of PLD architectures and patterns can be significant. To further complicate the record-keeping process, design changes often occur, especially in the early stages of product development. The task of maintaining which pattern goes into what device for which socket becomes exceedingly difficult. Once a manufacturing flow has been set, it becomes important to "label" each PLD with pertinent manufacturing information, which is beneficial in the event of a customer problem or return. A USERCODE register is incorporated into devices to store such design and manufacturing data as the manufacturer's ID, programming date, programmer make, pattern code, checksum, ISC data file CRC, PCB location, revision number, or product flow. This assists you with the complex chore of record maintenance and product flow control. In practice, the user-programmable USERCODE register can be used for any of a number of ID functions.

Within 32 bits available for data storage, you may find it helpful to define specific fields to make better use of the available storage. A field may use only one bit (or all bits), and can store a wide variety of information. The possibilities for these fields are endless, and their definition is completely up to you.

Even with the device's security feature enabled, the USERCODE register can still be read. With a pattern code stored in the USERCODE register, you can always identify which pattern has been used in a given device. As a second safety feature, when a device is erased and re-programmed, the USERCODE identification is automatically erased. This feature prevents any situation in which an old USERCODE might be associated with a new pattern.

It is your responsibility to update the USERCODE when reprogramming. The USERCODE information is not included in the fuse map checksum reading.

Loading the USERCODE instruction makes the USERCODE available to be shifted out in the Shift-DR state of the TAP controller. The USERCODE register can be read while the device is in normal functional operation, allowing the device to be scanned while operating.

### **Programming Hardware**

All programming specifications, such as the programming cycle and data retention, are guaranteed when programming devices over the commercial temperature range (0 to 70 degrees C). It is critical that the programming and bulk erase pulse width specifications are met by the programming platform to ensure proper in-system programming. The details of device programming are invisible to you if you use Lattice programming hardware and software.

#### **Computer Hardware**

Programming is most commonly performed on a PC or Linux system using the parallel port cable or the USB port cable.

#### **Parallel Port Cable**

The cable uses the parallel port of a PC or Linux system for in-system programming of all Lattice devices. Programmer generates programming signals from the parallel port and passes them through the cable to the JTAG port of the devices. With this cable and a connector on the printed circuit board, no additional components are required to program a device. Refer to the cable data sheet for more detailed specifications and ordering information.

Hardware design considerations for new boards include whether the hardware designer will be using boundary scan test operations or low-voltage (3.3 V–1.8 V) devices. In a system using 3.3 V devices, the cable version 2.0 should be used. This cable operates with either a 3.3 V or 5 V power source. In a system using 1.8 V devices, cable version 3.0 must be used. This cable operates with a power of 1.8 V to 5.0 V.

#### **USB Port Cable**

The USB port cable uses the USB port of a PC or Linux system for in-system programming of all Lattice devices. Programmer generates programming signals from the USB port and passes them through the USB port cable to the JTAG, Slave SPI, or I<sup>2</sup>C port of the device.

# **Programming Software**

Programmer supports programming of all Lattice devices in a serial daisy chain programming configuration in a PC or Linux environment. The software is built around a graphical user interface. Any required data files are selected by browsing with a built-in file manager. The software supports both serial and

concurrent (turbo) programming of all Lattice devices. Any non-Lattice devices that are compliant with IEEE 1149.1 can be bypassed after their instruction register lengths are defined in the chain description. Any non-Lattice devices that are compliant with IEEE 1532 can be programmed using an IEEE 1532-compliant BSDL and ISC data file. Programmable devices from other vendors can be programmed through the vendor supplied SVF file.

# **Embedded Programming**

Programmer embedded source code is available for programming devices in an embedded or customized environment. The programming source code is written in ANSI-standard C language, which can be easily incorporated into an embedded system or tester software to support programming of devices. This code supports such common operations as Erase, Program, Verify, and Secure. After completion of the logic design and creation of a JEDEC file, Programmer can create the data files required for in-system programming on customer-specific hardware: PCs, testers, or embedded systems.

### **FPGA Configuration**

Programmer provides efficient and economical alternatives to large and expensive PROMs that are normally used for configuring FPGA devices.

Because SRAM-based FPGA devices are volatile, they require reconfiguration on power cycles. This means that external configuration data must be held in a non-volatile device. On systems that require quick configurations or that do not have processor resources readily available, a dedicated serial PROM can be used. But such a PROM has to be large to accommodate large FPGA devices or multiple devices.

A much easier solution is to use a low-cost, industry-standard flash memory device combined with a LatticeECP/EC, LatticeECP2, LatticeECP3, and LatticeSCM/SC device.

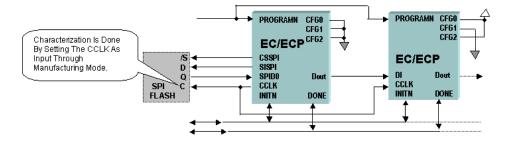

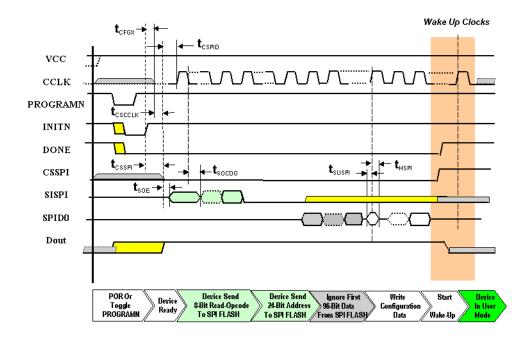

### **Serial Peripheral Interface Flash**

Programmer, combined with a Lattice cable download, supports the programming of Serial Peripheral Interface (SPI) flash devices.

Several Lattice FPGAs can be configured directly from an external serial peripheral interface (SPI) flash memory devices. Because of their bitstream compression capability, these Lattice FPGAs allow the use of smaller-capacity SPI memory devices.

For an up-to-date list of Lattice devices that can be configured using SPI flash, as well as a list of supported SPI flash devices, refer to the topic "Serial Peripheral Interface (SPI) Flash Support" in the Lattice Diamond online help or in the stand-alone Programmer online help.

# **Deployment Tool Overview**

Deployment Tool is a stand-alone tool available from the Diamond Accessories and is also available with stand-alone Programmer. The Deployment Tool graphical user interface (GUI) is separate from the Diamond and stand-alone Programmer design environment.

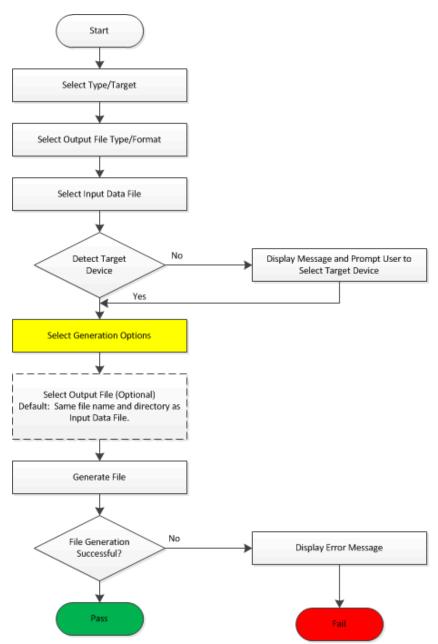

The Deployment Tool allows you to generate files for deployment for single devices, a chain of devices, and can also convert data files to other formats and use the data files it produces to generate other data file formats. A four-step wizard allows you to select deployment type, input file type, and output file type.

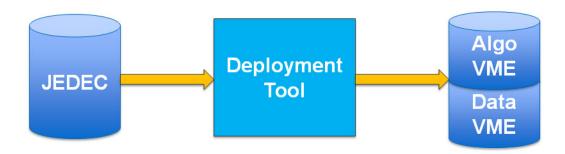

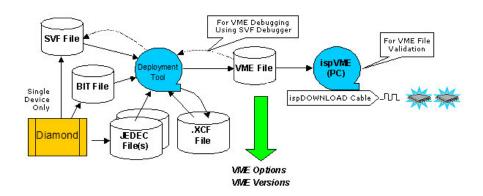

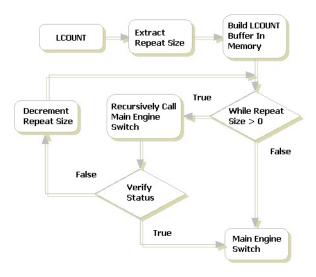

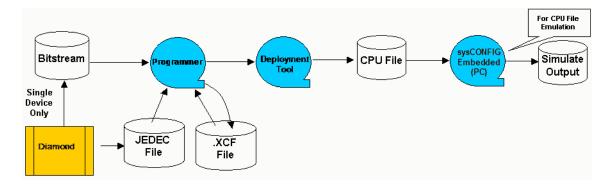

A basic block diagram of the Deployment Tool flow is shown in Figure 3 on page 22.

**Figure 3: Deployment Tool Flow**

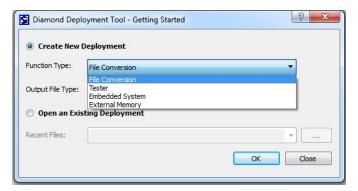

### **Deployment Tool Function Types**

There are four function types available in Deployment Tool:

- File Conversion

- Tester

- Embedded System

- External Memory

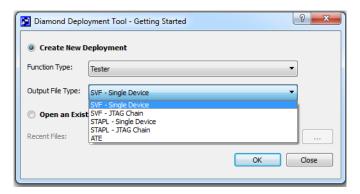

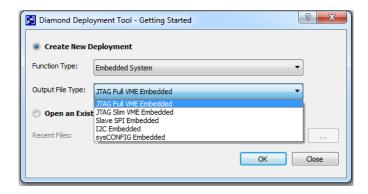

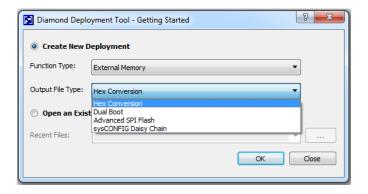

The function types are accessed from the Function Type dropdown menu on the Deployment Tool Getting Started dialog box, as shown in Figure 4.

**Figure 4: Deployment Tool Function Types**

### **Output File Types**

Each function type outputs different file types. This section describes all of the file types that are output by the five function types.

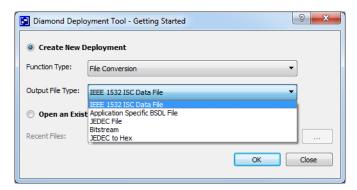

# **File Conversion Output File Types**

The File Conversion function outputs four different file types, as shown in Figure 5 on page 24. The output types are defined as follows:

**IEEE 1532 ISC Data File** Converts JEDEC files to IEEE 1532 compliant ISC (In System Configuration) data files, which are used in conjunction with IEEE 1532 compliant BSDL files to program a device.

**Application Specific BSDL File** Converts a generic BSDL (Boundary Scan Description Language) file to an Application Specific BSDL file, using the signal names from the input file (JEDEC or ALT file). Also, for any I/Os that support VREFs or LVDS pairs and are configured as VREFs or LVDS pairs, the application-specific BSDL file changes to accurately reflect the behavior of the VREF or LVDS pair. When generating the Application Specific BSDL file, you have the option to convert bi-directional I/O's to inputs or outputs based

**Figure 5: File Conversion Output File Types**

on your design, or to keep all I/Os as bi-directional. The generic BSDL files are available on the Lattice website.

**JEDEC File** Converts the following file types JEDEC, Binary Bitstream, ASCII Bitstream, or IEEE 1532 ISC into a JEDEC file. The USERCODE, USERCODE format, and set the Program Security Fuse for the JEDEC file.

**Bitstream** Takes a JEDEC, Binary Bitstream, or ASCII Bitstream file and can convert it into the following output formats Binary Bitstream, ASCII Bitstream, Intel Hex, Motorola Hex, and Extended Tektronix Hex. Users can specify the Program Security Bit, Verify ID Code, Frequency, Compression, CRC Calculation, USERCODE format, and USERCODE.

**JEDEC to Hex** Converts JEDEC (\*.jed) file type to either ASCII Raw Hex (\*.hex) or Binary Raw Hex (\*.bin) file type.

#### Note

The **JEDEC** to **Hex** feature supports JEDEC files generated by Lattice software. Using self-modified JEDEC files, corrupted JEDEC files, or JEDEC files generated using other software may result in incorrect data being generated, hanging, or crashing.

This feature does not support the following:

- Encrypted JEDEC files

- SED CRC

- TAG Memory

- USERCODE

- Feature Row

Refer to the Deployment Tool online help for information about specific device support.

# **Tester Output File Types**

The Tester function outputs five different file types, as shown in Figure 6.

**Figure 6: Tester Output File Types**

The output types are defined as follows:

**SVF - Single Device** SVF Single Takes one of the following user data files types JEDEC, ASCII Bitstream, Binary Bitstream, or IEEE 1532 ISC and then select an operation to generate an SVF (Serial Vector Format) file. Depending on the data file selected then a certain set of operation for the device are available to be selected. The user is able to check several options which will modify the SVF file.

**SVF - JTAG Chain** Takes an XCF file generated by Programmer and generates an SVF file. There are several options available that modify the SVF file including write header and comments, and set maximum data size per row.

**STAPL - Single Device** Takes a JEDEC, ASCII Bitstream, Binary Bitstream, or IEEE 1532 ISC and then depending on the input file type gives a set of available operation that can be performed on the device. A STAPL (Standard Test And Programming Language) file is generated using the data file and operation.

**STAPL - JTAG Chain** Generates a STAPL file for testing using only an XCF file generated by Programmer.

**ATE** Takes an XCF file and then the user is able to specify Tester Type, whether or not to skip the verify step in erase program verify or to split into separate files. An ATE (Automated Test Equipment) is a serial vector file specific to a test equipment vendor.

Refer to the Deployment Tool online help for information about specific device support.

### **Embedded System Output File Types**

The Embedded System function outputs five different file types, as shown in Figure 7.

The output types are defined as follows:

Figure 7: Embedded System Output File Types

**JTAG Full VME Embedded** Takes an XCF as an input file, then the user can check options such as Compress VME, include Header along with several other options. This operation generates a VME file which is a compressed hexadecimal representation of an SVF files.

**JTAG Slim VME Embedded** VME is a compressed version of a VME file. To generate a Slim VME file an XCF file must be specified, then specify whether it is a Compressed VME file and whether or not to generate a HEX file. This operation outputs an algorithm VME file and a data VME file.

**Slave SPI Embedded** This file type allows field upgrades via the slave SPI port. This operation can be given an XCF, Binary Bitstream, and ASCII Bitstream as an input file. If an Bitstream file is given then the operation for the device must be specified along with whether or not to compress the embedded file and whether or not to generate a HEX file. If an XCF file is given there are no other operations or options the user needs to provide. This operation will output an algorithm file (.sea) and a data file (.sed).

**I<sup>2</sup>C Embedded** I<sup>2</sup>C embedded files enable field upgrades via the I<sup>2</sup>C port. If an XCF file is specified then the user is given the option to compress the embedded files, generate a hex file, include comments, and if there should be a fixed pulse width. If a Bitstream file is specified then the previous options are available along with selecting the device operation and specifying the length of the I<sup>2</sup>C Slave Address. Two files will be generated a data file (.ied) and an algorithm file (.iea).

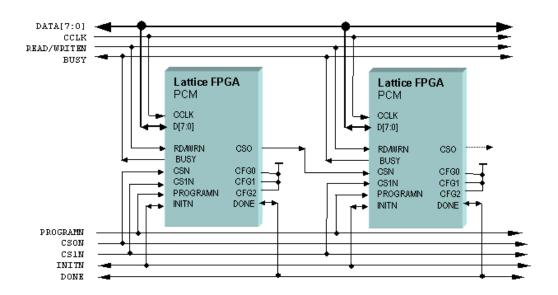

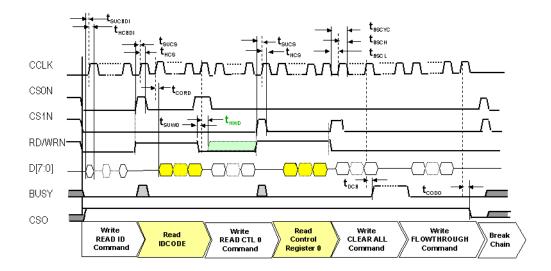

**sysCONFIG Embedded** Takes an XCF file as input and generates a CPU (.cpu) file which can be used for field upgrades via the slave parallel or slave serial modes.

Refer to the Deployment Tool online help for information about specific device support.

Also, refer to "Embedded Flow Overview" on page 29.

## **External Memory Output File Types**

The External Memory function outputs four different file types, as shown in Figure 8 on page 27. The output types are defined as follows:

**Figure 8: External Memory Output File Types**

**Hex Conversion** converts a file JEDEC, Binary Bitstream, ASCII Bitstream, Binary, or Hex to various Hexadecimal file formats which are used to configure the external SPI Flash memory of a device. The output file formats are Intel Hex, Motorola Hex, and Extended Tektronix Hex. The user is also able to set the Program Security bit, Verify ID Code, Frequency, compression, CRC Calculations and also the Starting Address.

**Dual Boot** Takes two JEDEC, Binary Bitstream or ASCII Bitstream files and then creates a single hex file to configure primary and golden sectors of an external SPI Flash. The output format can be Intel Hex, Motorola Hex, and Extended Tektronix Hex. The device will usually boot form the primary sector unless there is a problem then it will boot from the gold sector.

**Advanced** This operation is for generating hex files which handles more complicated operations such as Multiple Boot, and Quad I/O to configure external memory. Users can set the output hex format, how big the SPI Flash size is, whether or not to do a byte wide bit mirror, retain the bitstream header, and Whether or not to optimize the memory space. Another option is to set multiple user data file and where each of those data file's starting address should be in memory.

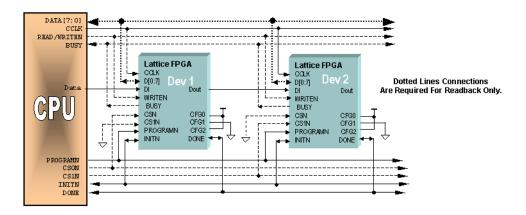

**sysCONFIG Daisy Chain.** This is used when multiple devices are in a daisy chain and configured from a single SPI flash or CPU. This operation will take two Binary or ASCII bitstreams and convert them into a single hex file.

Refer to the Deployment Tool online help for information about specific device support.

### **Embedded Flow Overview**

Lattice Embedded VME enables in-field upgrades of Lattice programmable devices by suitable embedded processors, and consists of the following:

JTAG Full VME Embedded Enable field upgrades via the JTAG port.

**JTAG Slim VME Embedded** Featured s reduced foot print and is designed for microcontrollers with limited resources, such as 8051 processors.

Slave SPI Embedded Enable field upgrades via the slave SPI port.

**12C Embedded** Enable field upgrades via the I<sup>2</sup>C port.

**sysCONFIG Embedded** Enable field upgrades via the slave parallel or slave serial modes.

There are three components to Embedded VME

- ANSI C source code, which is shipped with Diamond Programmer. The user compiles this ANSI C Source code into their target system.

- Algorithm VME File, which contains the programming algorithm for the target FPGA. The Algorithm VME file is generated using the Deployment Tool.

- Data VME File, which contains the data that will be programmed into the FPGA. The Data VME file is generated using the Deployment Tool.

For all five embedded types, the Embedded VME support is comprised of C source files that users must port into their embedded systems for the purpose of programming Lattice devices. The porting process is also known as the customization and compiling process. The end product of the porting process will be the Embedded VME in compiled form, which will reside in the embedded systems.

Depending on the port interface, such as JTAG, SPI, or I<sup>2</sup>C, the user can select one of the five embedded VME types.

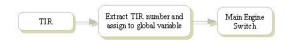

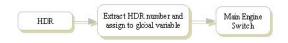

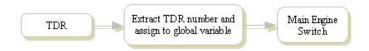

Figure 9 shows an example of Full VME embedded file generation for the JTAG port.

Figure 9: Full Embedded VME Flow

The programming data and programming instructions are compiled into a binary VME file format for the driver to load into the target devices. The VME file can be provided to the driver as a stand-alone file or linked together with the driver.

Figure 10 shows a high-level example of a file-based embedded VME used for field upgrades.

New Data

VME

VME

VME

VME

CPU

Customer Board

Memory

Algo

VME

VME

Device(s)

CPU

Figure 10: Example Embedded VME Programming Configuration

#### .

### Porting of the JTAG VME into Embedded Systems

Porting JTAG Embedded VME is simple and the requirements are very simple to follow:

#### AC Requirements:

- ► TCK Fmax = 25 MHz.

- TCK Rise Time and Fall Time = 50ns maximum.

- Delay function resolution and accuracy = 1 millisecond minimum.

#### DC Requirements:

- ► I/O voltage level of the driver = I/O voltage level of the VCC JTAG port of the target devices. The VCC that power the JTAG port can be:

- VCC core (All EE based devices)

- VCCIO (MachXO devices)

- VCCJ (All SRAM based and Flash based FPGA devices)

- Programming current = 1 Ampere maximum.

### **JTAG Programmability of Lattice Devices**

Lattice's devices can be classified into three groups based on programmability:

- SRAM based only devices (volatile devices).

- ▶ EE based devices (non-volatile devices).

- Flash based devices (non-volatile devices).

#### Note

For information on configuring the Lattice iCE40 family of devices from an embedded processor, refer to TN1248, *iCE40 Programming and Configuration Guide*.

The SRAM based only devices are the easiest devices to support in terms of Embedded VME porting for they normally do not require accurate timing.

The EE based devices are much more challenging for they require the 1 millisecond resolution and accurate timing.

The Flash based devices are the most challenging among the three types. The delay function not only must have the 1 millisecond resolution and accuracy, it also must be able to provide the cumulative delay time up to 150 seconds – the worst case erase time of some Flash based devices.

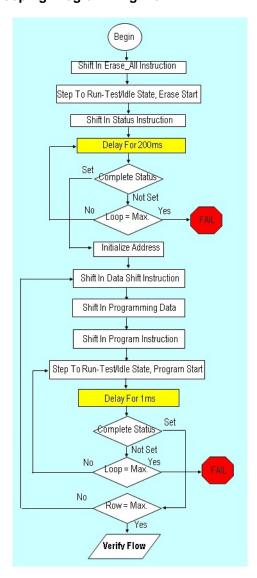

The EE based devices are supported by the programming flow generally referred to as the fixed pulse width flow. The Flash based devices require the

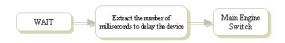

Figure 11: ispMACH4000 Fixed Delay Time Programming Flow

looping programming flow. The most critical requirement to ensure the devices are programmed reliably rests on the accuracy of the delay function.

If the devices are not given the required programming delay time, the Flash based devices will fail the verification during programming. It will be worse if failure happens during Flash erase.

When the erase operation is terminated before completion due to insufficient delay time, the Flash will have an unknown pattern residing in it which might cause the device entering the contentious state. When the device is in contentious state, it will be very hot and would not respond to further programming commands. EE based devices may not fail verification but they will fail to meet the 10 year data retention as specified.

All Lattice EE and Flash based devices are designed with the over-stress and over-charge protection technology. This technology is very critical to the superior In-System Programmability of Lattice's non-volatile devices. The devices cannot be damaged when given an erase delay time or programming delay time longer than the minimum specified.

The accuracy of the delay function discussed in this document will focus only on meeting the minimum requirement. It means that when the delay function is called to generate, for example, 100 ms delay time (by calling the delay

Figure 12: MachXO Looping Programming Flow

function 100 times), as long as the resulting delay time is equal to or greater than 100 ms, the delay time is considered accurate.

The only undesirable side effect of applying longer erase delay time or programming delay time to the devices is on the programming throughput. Diamond Programmer provides precise delay timing to meet the programming specification and optimizing on throughput.

The Deployment Tool software will automatically determine whether the device requires the fixed delay time programming flow or the looping programming flow when generating the VME file. Also, the device specific programming algorithm details, such as row size, the maximum loop count, and the delay required per each loop, are all embedded into the VME file automatically.

If interested to find out the details of their VME files, simply convert the binary VME files into the corresponding text based SVF file format using the Download Debugger shipped with Diamond Programmer.

The verify flow is identical for the looping and fixed pulse programming flow. The delay required for the verify flow is usually ~100us per row. The VME file still requires 1 millisecond delay per row since the PC cannot provide accurate timing if the delay is less than 1 millisecond.

Thus, the only Embedded VME implementation challenge is the development of an accurate delay function to provide 1 millisecond minimum delay time.

### **Embedded VME Porting Detail**

Step 1: Customize JTAG Embedded VME by modifying hardware.c

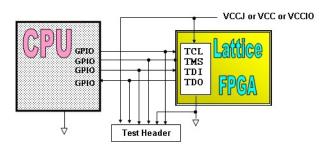

Figure 13: Map Four GPIO Pins from the CPU to the Four JTAG Pins

The pin mapping index table on the hardware.c must be revised to match with the customer's board layout. On the PCB that is the target for porting the Embedded VME, it is important and a good practice to route the JTAG port to a test header for easy access using an oscilloscope or connecting to Programmer for debugging.

All VME files begin with IDCODE verification to ensure the JTAG port pins are mapped and connected properly.

```

unsigned short g usOutPort = 0x378;

* This is the definition of the bit locations of each respective

* signal in the global variable g_siIspPins.

These lines of

* NOTE: users must add their own implementation here to define

code can be

the bit location of the signal to target their hardware.

commented

The example below is for the Lattice download cable on

out. They do

on the parallel port.

not need to be

mapped.

const unsigned char g_ucPinTDI = 0x01; /* Bit address of TDI signal */

const unsigned char g_ucPinTCK = 0x02; /* Bit address of TCK signal */ const unsigned char g_ucPinTMS = 0x04; /* Bit address of TMS signal */

const unsigned char g_ucPinENABLE = 0x08; /* Bit address of chip enable */

const unsigned char g_ucPinTRST = 0x10; /* Bit address of TRST signal */

const unsigned char g_ucPinTDO = 0x40; /* Bit address of TDO signal */

```

### **Modify the Delay Function**

When porting Embedded VME to a native CPU environment, the speed of the CPU or the system clock that drives the CPU is usually known. The speed or the time it takes for the native CPU to execute one loop then can be calculated.

The for loop usually is compiled into the ASSEMBLY code as shown below:

```

LOOP: EDC RA;

JNZ LOOP;

```

If each line of assembly code needs four (4) machine cycles to execute, the total number of machine cycles to execute the loop is  $2 \times 4 = 8$ .

Usually: system clock = machine clock (the internal CPU clock).

#### Note

Some CPUs have a clock multiplier to double the system clock for the machine clock.

Let the machine clock frequency of the CPU be F (in MHz), then one machine cycle = 1/F.

The time it takes to execute one loop =  $(1/F) \times 8$ .

It is obvious that the formula can be transposed into one microsecond = F/8.

Example: The CPU internal clock is set to 48 MHz, then one microsecond = 48/8 = 6.

The C code shown below can be used to create the millisecond accuracy. All that needs to be changed is the CPU speed.

```

void ispVMDelay (unsigned short a usTimeDelay)

unsigned short delay_index

= 0;

unsigned short loop index

= 0;

unsigned short ms index

= 0;

→ 0;

unsigned short us index

unsigned short cpu_frequency = 48; // Enter your CPU frequency here in MHz.

if (a_usTimeDelay & 0x8000) { /*Test for unit*/

a usTimeDelay &= ~0x8000; /*unit in milliseconds*/

else { // unit in microseconds

a usTimeDelay = a usTimeDelay/1000; //convert to millisecond

if ( a usTimeDelay <= 0 ) {

a_usTimeDelay = 1; //delay is 1 millisecond minimum

//users can replace the following section of code by their own

for( ms index = 0;ms index < a usTimeDelay; ms index++) {</pre>

// Loop 1000 times to produce the milliseconds delay

for (us index = 0; us index < 1000; us index++) {

// each loop should delay for 1 microsecond or more.

loop index = 0;

do {} //use do loop to force at least one loop

while (loop index++ < cpu frequency/8);

}

}

```

#### Step 2: Calibration

It is important to confirm if the delay function is indeed providing the accuracy required. It is also important to confirm the TCK frequency. As an example, we will estimate the minimum system clock frequency of the native CPU that does not require the TCK to be slowed down. The TCK could be generated by the following code.

```

writePort (g_ucPinTCK, 0x00);

writePort (g_ucPinTCK, 0x01);

```

Let the number of system clocks to execute one line of code = 8 clocks.

The total number of clock for one pulse =  $2 \times 8 = 16$ .

The total amount of time for one pulse =  $1/F \times 16$ .

Lattice devices TCK frequency max = 25 MHz.

The equation becomes:  $1/25 = 1/F \times 16$ .

The maximum frequency of the CPU:  $F = 16 \times 25 = 400 \text{ MHz}$ .

If the system clock of the native CPU is faster than 400 MHz, the TCK pulses must be slowed down to meet the 25 MHz maximum specification.

The setup time and hold time of TDI, TMS, and TDO relative to TCK is not of concern for Embedded VME is constructed in the fashion that it is not possible to violate that requirement whenever the frequency of TCK is within the specification.

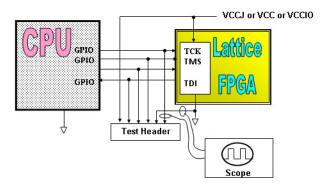

Figure 14: JTAG Embedded VME Delay Calibration

The calibrate function in Embedded VME can be launched by using the -c switch to cause the waveform as follow captured on the scope with the probe attached to the TCK wire.

If the pulse width is found to be smaller than 1 millisecond, then increase the cpu\_frequency value until 1 millisecond delay is captured by the calibration function.

If the TCK frequency is found to be faster than 25 MHz, then change the sclock() function in hardware.c as shown below. The IdleTime normally is

Figure 15: JTAG Embedded VME Delay Calibration TCK Waveforms

```

calibration

* It is important to confirm if the delay function is indeed providing

* the accuracy required. Also one other important parameter needed * checking is the clock frequency. * Calibration will help to determine the system clock frequency

* and the loop_per_micro value for one microsecond delay of the target

\star specific hardware.

void calibration(void)

//Apply 2 pulses to TCK.

writePort( g_ucPinTCK, 0x00 );

writePort( g_ucPinTCK, 0x01 );

writePort( g_ucPinTCK, 0x00 );

writePort( g_ucPinTCK, 0x01 );

writePort( g_ucPinTCK, 0x00 );

//delay for 1 millisecond. Pass on 1000 or 0x8001 both = 1ms delay.

ispVMDelay(0x8001);

//Apply 2 pulses to TCK.

writePort( g_ucPinTCK, 0x01 );

writePort( g_ucPinTCK, 0x00 );

writePort( g_ucPinTCK, 0x01 );

writePort( g_ucPinTCK, 0x00 );

This line of code launches the delay

function to produce the 1-millisecond

pulse width the ispVME driver must

be able to provide accurately.

40ns min.

One

millisecond

50ns max

min.

Same as

VCC-JTAG

20ns min.

```

initialized to 0. If it is initialized to 1, then the TCK frequency is effectively reduced by half. Use this technique to reduce the TCK frequency until meeting the specification.

```

sclock

Apply a pulse to TCK.

* This function is located here so that users can modify to slow down TCK if

* it is too fast (> 25MHZ). Users can change the IdleTime assignment from 0 to

* 1, 2... to effectively slowing down TCK by half, quarter...

Initialize to 1 if need to reduce

TCK speed by half.

void sclock()

unsigned short IdleTime

= 0; //change to > 0 if need to slow down TCK

unsigned short usIdleIndex = 0;

IdleTime++;

for ( usIdleIndex = 0; usIdleIndex < IdleTime; usIdleIndex++ ) {</pre>

writePort( g_ucPinTCK, 0x01 );

for ( usIdleIndex = 0; usIdleIndex < IdleTime; usIdleIndex++ ) {

writePort( g_ucPinTCK, 0x00 );

```

Step 3: Program Devices

Once the calibration is done, the Embedded VME (actually the JTAG port driver) is ready to program the devices. The device specific programming information is all self-contained in the VME file.

The VME file actually has six major sections:

- 1. Check the IDCODE,

- 2. Erase the device,

- 3. Program the device,

- 4. Verify the device,

- Program the done fuse,

- 6. Wake-up the device.

IDCODE check failure is the most common failure when porting Embedded VME. It is a good practice to generate a Verify IDCODE only VME file first. Run the VME file. If it passes, then the JTAG port to GPIO mapping is confirmed. Once the port mapping is confirmed, then the programming VME file can be used.

Accurate timing is very critical to program devices reliably.

Using the calibration routine provided by Embedded VME will achieve the accurate timing.

#### JTAG Full VME Embedded

The JTAG Full VME Embedded VME software brings programming software to embedded applications. Using Lattice Semiconductor's Diamond Programmer and Deployment Tools, you are provided with all necessary capabilities for programming devices in a single or multiple device chain. Developed to solve many programming issues facing today's PLD users, JTAG Full VME Embedded provides advanced features including fast programming times, and small file sizes.

The JTAG Full VME Embedded software is a simplified version of the full Diamond Programmer. By making it serial vector format (SVF) file centric, JTAG Full VME Embedded is better targeted for embedded systems. Lattice JTAG devices are supported and users are able to program competitor devices through a simple SVF file translator. Lattice JTAG devices are those devices that can be programmed using the IEEE 1149.1 boundary scan TAP controller interface. Users are able to quickly and efficiently program chains of devices using this powerful utility, thus improving productivity and lowering costs.

An advantage of JTAG Full VME Embedded over vendor or architecture-specific methods is that once it is developed, it supports all present and future devices. As long as the programming flow can be described as an SVF file, the main engine does not have to change. For embedded environments, it is important to have deterministic memory requirements. By pre-processing the SVF file, it is possible to know the exact resources required to implement the programming algorithm and to store the programming data. The nature of the SVF file also allows the resources available to determine how the file is processed. Large shift instructions can be broken into multiple instructions if the embedded system does not have enough RAM available to store the entire row in one pass. Since the SVF file is serial in nature, it can be segmented to fit available RAM, PROM or FLASH memory.

The JTAG Full VME Embedded source code is designed to be hardware and platform independent. A VME data file, or VME file, runs on all JTAG Full VME Embedded applications.

See Also JTAG Full VME Embedded Basic Operation

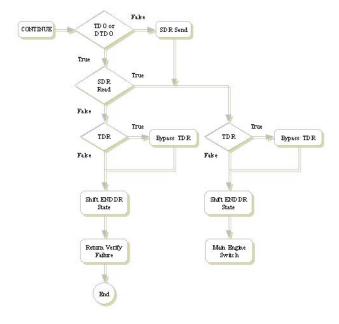

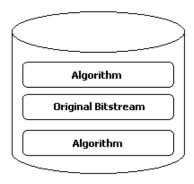

### **VME File Format**

A VME file is simply an SVF file that has been compressed. SVF file includes algorithm and data file in ASCII format, and VME file is the SVF file in the optimized binary format. Compared with SVF file, VME files require minimized memory space to store the bitstream file and has optimized code size. SVF keywords such as SIR and SDR are replaced with the byte codes 0x11 and 0x12, respectively. This reduces the VME file by writing only one byte of data, the byte codes, instead of writing the entire SVF keyword, which would use more characters.

JTAG Full VME Embedded file supports compression to reduce the VME file size by compressing the data and address streams. A looping compression is

also employed to reduce the file size even further by taking advantage of the repeating SVF constructs. The following describes each compression scheme.

**Compressed VME Files** The compression scheme is applied to the address and data stream following SIR and SDR, respectively. These streams will try to be compressed by 0x00, 0xFF, or by 4-bit count.

For example, consider the following line in a SVF file:

Compression by 4-bit count works by looking for repeating patterns within the data stream that are not zeros or 'F's.

For example, consider the following line in a SVF file:

```

SDR 80 TDI (7F97F97F97F97F97F9);

```

The repeating 4-bit count in this example would be '7F9,' because it repeats throughout the data stream. The 4-bit would be written only once in the VME file, and would be followed by the number of repetitions found within the data stream.

The compression scheme reduces the file size by not extrapolating repeating information within the address and data streams. That task is left for the VME processor.

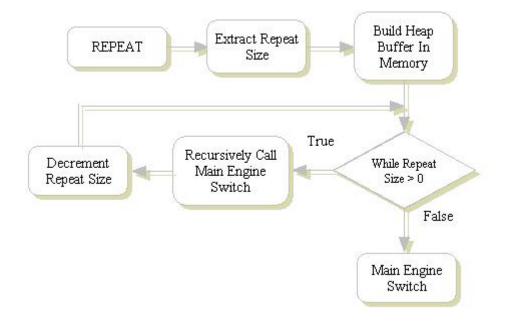

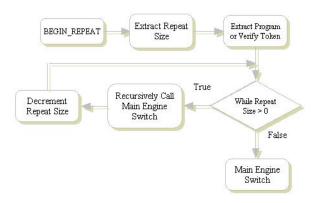

**Looping VME Files** In an SVF file, repeating constructs can be observed. The looping scheme takes advantage of these constructs by creating a template with the repeating information, and the differentiating date is replaced by a placeholder. The differentiating data will be written after the construct.

For example, the following data is found in a SVF file:

```

SIR 5 TDI (01);

SDR 102 TDI (2000000000000000000000000);

SIR 5 TDI (02);

SDR 80 TDI (7BFFF7BFFFF7BFFF7BFF);

SIR 5 TDI (07);

RUNTEST IDLE 3 TCK 1.20E-002 SEC;

SIR 5 TDI (01);

```

The looping template is built based on the repeating SIR lines. Notice how the TDI values for the SIR commands are a repeating sequence of 01, 02, and 07. In this case the resulting template would be:

```

SIR 5 TDI (01);

SDR 102 TDI VAR;

SIR 5 TDI (02);

SDR 80 TDI VAR;

SIR 5 TDI (07);

RUNTEST IDLE 3 TCK 1.20E-002 SEC;

```

VAR is written in place to hold the data that does not repeat. The non-repeating data will get written into the VME file following each template. The example above would look like this in the VME file:

```

LOOP 3

SIR 5 TDI (01);

SDR 102 TDI VAR;

SIR 5 TDI (02);

```

The 'LOOP 3' tells the VME processor to loop the template three times. Each time it encounters a 'VAR', it will grab the first available line of data following the 'ENDLOOP' and replace 'VAR' with it. This technique reduces the file significantly by keeping the similar constructs to a minimal, and only writing the differences.

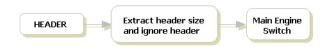

## **JTAG Full VME Embedded Flow**

The JTAG Full VME Embedded System allows you to program a device using the microprocessor in an embedded system. When you install the VM software, a separate VMEmbedded folder containing the VME source code and executables is installed on your hard drive. Compiling the VME source code gives you an executable file that you can store in your system's memory for programming using the JTAG port.

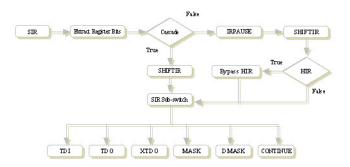

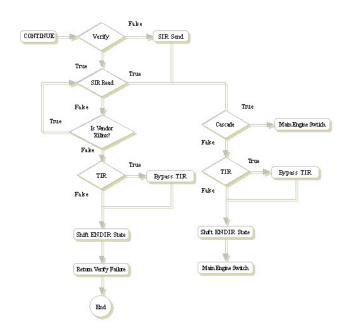

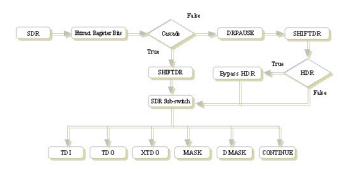

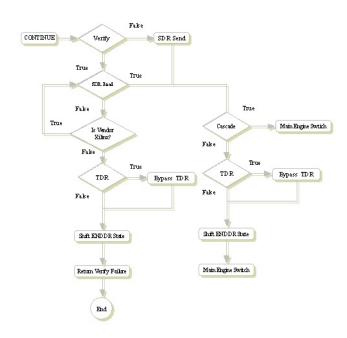

The following figure illustrates the JTAG Full VME Embedded flow.

See Also ▶ Generating VME Files

Testing VME Files

## JTAG Full VME Embedded System Memory

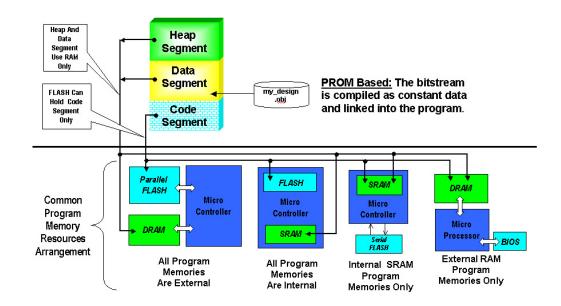

The following figure illustrates JTAG Full VME Embedded system memory.

See Also JTAG Full VME Embedded Basic Operation

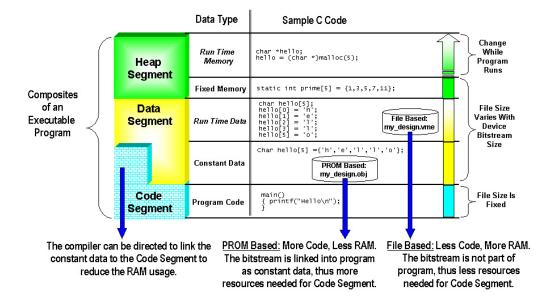

# JTAG Full VME Embedded Basic Operation

There are three modes of JTAG Full VME Embedded operation.

**File Mode** Under the file mode, data is stored in a file system such as a hard drive or a DOS flash. The data file is accessed using C library calls, such as fopen, fread, and fclose. The file read operations collect data into the system memory. The system memory of the Embedded system must be able to store the entire bitstream from the file in a contiguous block of memory. The memory block can be allocated in one of the three locations.

Data Segment – You can pre-determine how many bytes of data the bitstream will require and then create an uninitialized array variable to hold the data. This permanently allocates a portion of the Data Segment. For example:

char programmingData[0x10000]; // allocate 64K

Stack Segment – You can pre-determine how many bytes of data the bitstream will require and then create an uninitialized array variable to hold the data. Depending upon the function call sequence, this may or may not permanently allocate a portion of the system memory. See the example code below.

```

int MyFunction ( ) {

char bitstreamArray[0x10000];

}

```

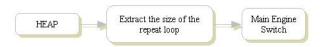

Heap Segment – You can determine at runtime how many bytes of data the bitstream will require and then dynamically allocate an uninitialized array variable to hold the data. You are responsible for freeing the memory when it is not being used any longer. Below is an example.

```

char *bitstreamData;

bitstreamData = (char *)malloc(numberOfBitstreamBytes);

```

**Static Linking Mode** Under the static linking mode, the bitstream data is converted from the file on the hard drive into a C source code file. The C source code defines a byte array. The byte array is exactly the size of the bitstream. The byte array can be linked into either the Code Segment or the Data Segment. The memory allocated for the bitstream is permanently consumed.

**PROM Mode** Under the PROM-based mode, the bitstream file is converted from the file on the hard drive into an Intel HEX file. The HEX file is loaded into a non-volatile memory using a PROM programming tool. The HEX file data is placed in the non-volatile memory at a known address (that is, a fixed address). The user C code initializes a pointer. The pointer is given the starting address of the HEX byte stream. The memory used by the bitstream is permanently allocated in the non-volatile memory.

See Also >JTAG Full VME Embedded System Memory

#### **VME Source Code**

The JTAG Full VME Embedded source code is written in standard ANSI C and is simplified with embedded applications in mind. Most embedded applications have greater limits on program and data sizes than PC or workstation applications. The areas most likely to differ between platforms are the timing delay function and hardware port manipulation.

The current version of the JTAG Full VME Embedded software is available through the Programmer installation. The installation creates a sub-directory called **VMEmbedded**, where the pre-compiled executables, source code, and readme.txt can be found.

There are four sets of embedded-related source code that are shipped with Programmer.

VME – The file-based VME is the programming engine that accepts VME files as command line arguments to process the devices. By default, the executable compiled from this source code targets Windows operating

- systems. You can make small modifications to make the compiled executable accommodate other platforms.

- VME\_eprom The PROM-based VME is the programming engine that requires compiling a HEX file, which is a C-programming file, with the source code to create an executable engine that can be embedded onto the embedded system.

- svf2vme The svf2vme is a command line utility that can convert SVF files into VME files.

- vme2hex The vme2hex is a command line utility that can convert VME files into HEX files.

Among all the source codes, only the hardware.c file requires user changes. You should customize the hardware.c file according to your target platform.

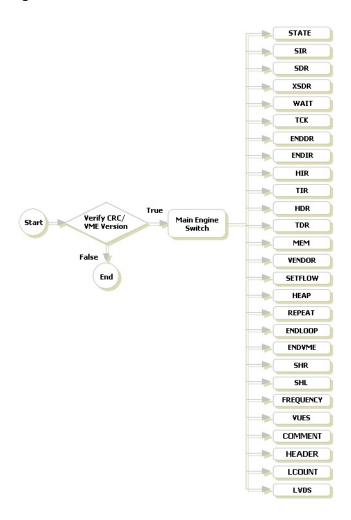

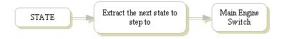

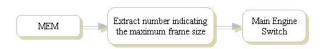

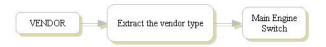

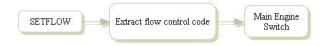

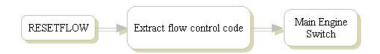

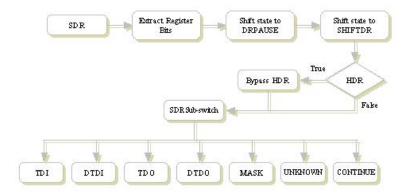

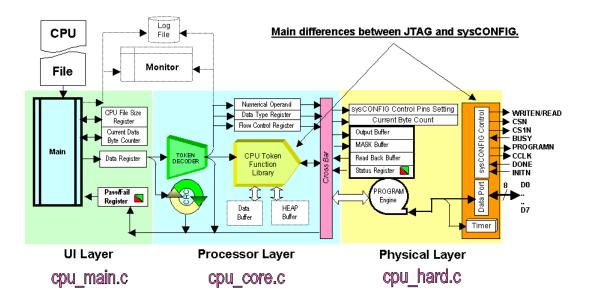

# JTAG Full VME Embedded Programming Engine

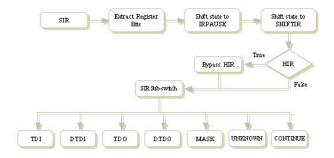

The programming engine of the JTAG Full VME Embedded software is driven by the byte codes of the VME format file. It manipulates the I/O ports and sends commands to the customer firmware. The commands sent from the programming engine requires the I/O system to be connected to the device's JTAG port. The VME byte codes instruct the engine as to what sequence of functions to follow in order to shift in instructions, move the TAP controller state machine, shift data in and out of the device, and observe delay. The engine has the following three layers.

- User interface layer (ispvm\_ui.c) Directs inputs and outputs.

- Processor layer (ivm\_core.c) Decodes commands, checks CRC prior to processing, and does optional decompression.

- Physical layer (hardware.c) Shifts data to target device. This is the only file that you need to edit. See Customizing for the Target Platform for details.

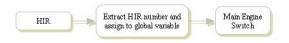

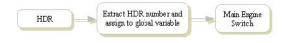

Log File VME File Numerical Operand Data Type Register TR Register HDR Registe VME File Size DR Registe Decompress NDDR State Current Data Current JTAG State Next JTAG State VM Token Function Library DO Buffer Pass#Fail ead Back Buffe **UI Layer Processor Layer Physical Layer**

The following figure illustrates JTAG Full VME Embedded JTAG port programming engine.

| Legend            | Size (bits)    | Type                   |

|-------------------|----------------|------------------------|

| 7                 | 8              | signed char            |

| $\Diamond$        | 8              | unsigned char          |

| $\mathcal{W}$     | 16/32 (Note 1) | integer                |

| $\Leftrightarrow$ | 16             | unsigned short integer |

| Legend | Description                                                                          |

|--------|--------------------------------------------------------------------------------------|

|        | Optional features enabled by the VME, CPU or SCM file                                |

| N      | Continue or Exit decision flag (Go / No Go)                                          |

|        | Memory allocated at run time using malloc() as required by the VME, CPU or SCM file. |

|        | Gray out means not used.                                                             |

## **RAM Size Requirement for VME**

To calculate the worst-case size of memory needed to program a device, in terms of bytes, locate the size of the largest register in the device. This is usually the data shift register. Divide that number by eight, and then multiply the quotient by two: one for TDI and one for TDO. If the device has MASK, multiply the quotient by three instead of two.

This method only calculates the RAM requirements for the data of the device. It does not account for transient variables that are used to execute the programming algorithm. Transient variables are more difficult to calculate because they appear in and out of scope often. Also, a variable size may depend on the microprocessor's register size. For example, an integer variable on a 32-bit system is four bytes while the same variable on a 16-bit system is only two bytes.

To approximate the RAM requirement for the run-time variables, add twenty percent to the required RAM.

## **RAM Calculation Example** The following is a partial SVF for the M4A3 32/32 device:

| SIR | 6   | TDI  | (03);                                      |  |

|-----|-----|------|--------------------------------------------|--|

| SDR | 80  | TDI  | 000000000000000000000000000000000000000    |  |

| SIR | 6   | TDI  | (04);                                      |  |

| SDR | 202 | TDI  | (20000000000000000000000000000000000000    |  |

| SIR | 6   | TDI  | (07);                                      |  |

| SDR | 202 | TDI  | (20000000000000000000000000000000000000    |  |

|     |     | TDO  | (0004104104104104104104104104104104104104  |  |

|     |     | MASK | (21041041041041041041041010410410410410410 |  |

The largest data frame size in this device is 202 bits. Therefore, TDI, TDO, and MASK each require 26 bytes, making it a total of 3\*26 = 78 bytes. To account for run-time variables, the total required size would be 78 \* 1.2 = 94 bytes.

To verify that the calculation is correct, convert the SVF file to VME, and use the VME2HEX utility to convert from VME to HEX. This utility generates the vme\_file.h file, which gives the definitive memory size requirement.

The variables that are of concern to memory are:

- MaskBuf

- TdiBuf

- TdoBuf

- HdrBuf

- TdrBuf

- HirBuf

- TirBuf

- HeapBuf

- CRCBuf

- CMASKBuf

As expected, MaskBuf, TdiBuf, and TDOBuf each requires 26 bytes. If the device were in a chain, HdrBuf (Header Data Register), TdrBuf (Trailer Data Register), HirBuf (Header Instruction Register), and TriBuf (Trailer Instruction Register) would need extra bytes.

If the VME file had been generated with the looping option, HeapBuf would require extra bytes as well. Looping requires slightly more RAM but significantly less ROM. When the VME file has not been looped, it does not require any additional RAM, but ROM size can significantly increase. This

trade-off is file-dependent. If the original SVF were 1532-compliant, CRCBuf and CMASKBuf would require extra bytes as well.

## ROM Size Requirement for JTAG Full VME Embedded

To calculate the worst-case ROM size for a given device, multiply the number of frames by the frame size. Divide that number by eight to obtain the required ROM size, in terms of bytes.

This method assumes that the SVF file will be generated with the turbo option. If the SVF file were generated with the sequential option, the worst-case ROM size would be doubled.

This method only calculates the ROM requirements for the data. It does not account for opcodes that are used to translate the algorithm of the device. To approximate the ROM requirement for the algorithm opcodes, add twenty percent to the required ROM.

The actual ROM requirement might be significantly less than the theoretical worst-case requirement because SVF2VME utilizes two compression techniques, compression and looping, to decrease the VME file. The file size difference is file-dependent.

**ROM Size Calculation Example** The following example calculates the worst-case ROM size for the device LC4128:

```

Frame size = 740

x Number of frames = 100

Data ROM size = 74000 bits

Data ROM size = 74000

x 1.2

Overall ROM size = 88800 bits

```

# JTAG Full VME Embedded Required User Changes

To make the JTAG Full VME Embedded or JTAG Slim VME Embedded software work on your target system, you need to modify the following C functions in the hardware.c source code.

**Timer** The engine requires the ability to delay for fixed time periods. The minimum granularity of the delay is 1 microsecond. You can determine the type of delay. This can be a simple software timing loop, a hardware timer, or an operating system call, for example, sleep().

**Port Initialization** The firmware needs to place the port I/O into a known state. The software assumes this has occurred.

**Get Data Byte** The engine calls the GetByte() function to collect one byte from the JTAG Full VME Embedded or CPU bytestream.

**Modify Port Register** The engine, as it parses the bitstream data, changes an in-memory copy of the data to be written onto the I/O pins. Calls to this function do not modify the I/O pins. The engine uses *virtual types* (for example, DONE\_PIN) which this function turns into physical I/O pin locations (for example, 0x400).

**Output Data Byte** The engine calls this function to write the in-memory copy onto the I/O pins.

**Input Status** This function is used by the engine to read back programming status information. The function translates physical pin locations (for example, 0x400) into *virtual types* used by the engine (for example, DONE PIN).

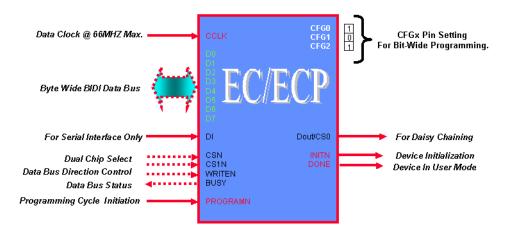

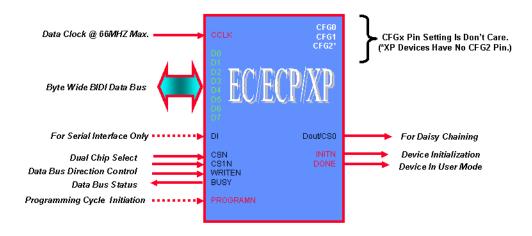

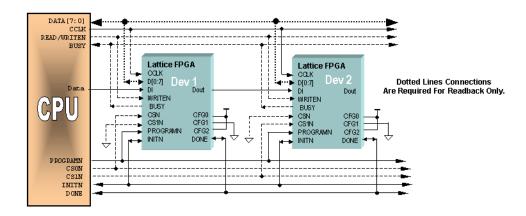

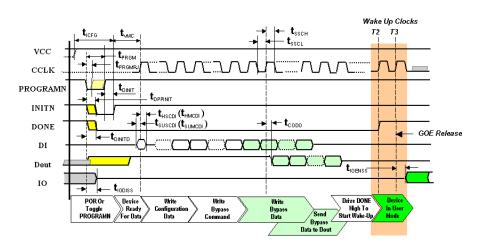

**Output Configuration Pins** Some systems may wish to use the FPGA CFG pins, and have the Embedded system control them. There is a separate function call to manipulate the CFG pins.

**Bitstream Initialization** You must determine how you plan to get the bitstream into your memory system, pre-compiled, HEX file based, or dynamically installed. Whichever method you use the data structures which pin to the bitstream need to be initialized prior to the first GetByte function call.

See Also ▶ Customizing for the Target Platform

- VME Source Code

- ▶ JTAG Slim VME Embedded Source Code

## **Program Memory Requirement**

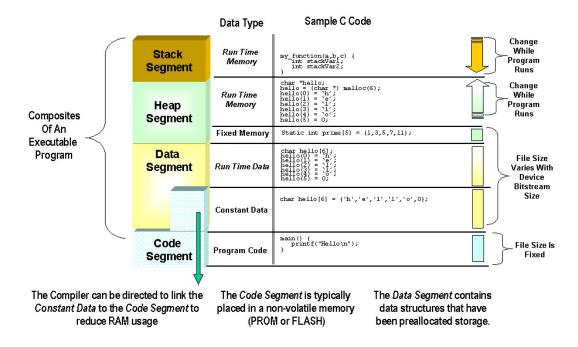

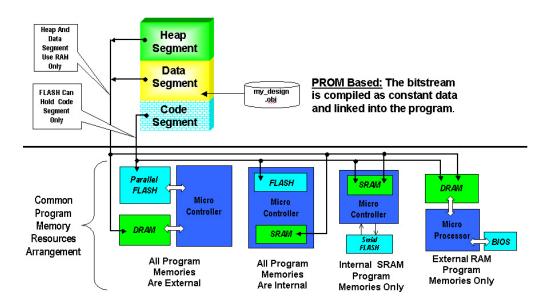

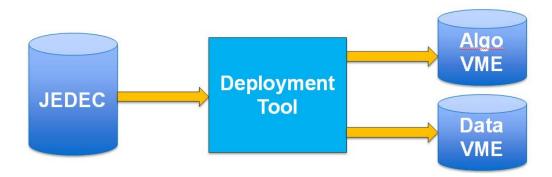

The following figure illustrates the JTAG Full VME Embedded program memory requirement.

## **Program Memory Allocation**

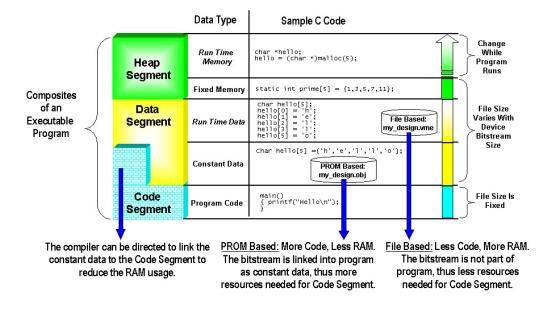

The following figure illustrates the JTAG Full VME Embedded program memory allocation.

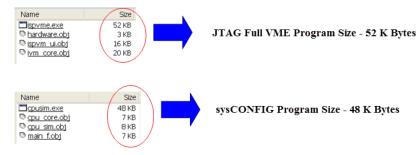

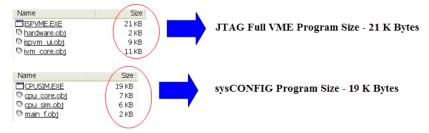

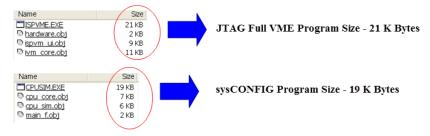

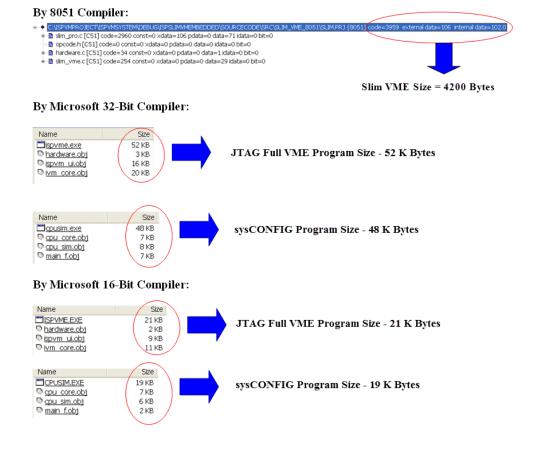

## **Sample Program Size**

This page provides sample program size for JTAG Full VME Embedded, JTAG Slim VME Embedded, and sysCONFIG Embedded.

| Embedded Tool                             | JTAG Port                 |        |                              | non-JTAG Port         |        | Total                       |

|-------------------------------------------|---------------------------|--------|------------------------------|-----------------------|--------|-----------------------------|

| Bitstream Location                        | JTAG Full VME<br>Embedded |        | JTAG Slim<br>VME<br>Embedded | sysCONFIG<br>Embedded |        |                             |

|                                           | 32-Bit                    | 16-Bit | 8-Bit                        | 32-Bit                | 16-Bit |                             |

| File Based<br>(Bitstream File External)   | 52KB                      | 21KB   | 4.2KB                        | 48KB                  | 19KB   | As Shown                    |

| PROM Based<br>(Bitstream File Integrated) | 52KB                      | 21KB   | 4.2KB                        | 48KB                  | 19KB   | As Shown +<br>VME File Size |

By 8051 Compiler:

• CIJSPWINFROJECTIJSPWINSYSTEMIDEBUGIJSPSLIMM/EMBEDDEDISOURCECODE(SRC)SLIM\_WINE\_8051\SLIM\_FRJ\_{8051}\code=3959 external data=106 internal data=102.0

• B sim\_pro.c [CS1] code=2960 const=0 xdata=106 pdata=0 data=71 idata=0 bit=0

• D pocode.h [CS1] code=2960 const=0 xdata=0 pdata=0 data=1 idata=0 bit=0

• B hardware.c [CS1] code=34 const=0 xdata=0 pdata=0 data=1 idata=0 bit=0

• B sim\_vme.c [CS1] code=254 const=0 xdata=0 pdata=0 data=29 idata=0 bit=0

By Microsoft 32-Bit Compiler:

#### By Microsoft 16-Bit Compiler:

Slim VME Size = 4200 Bytes

## **VME File Size**

The following table compares VME file sizes taking typical Lattice devices for examples.

| Device              | Device Row Size<br>(Bits) | JTAG Slim VME Embedded File Size No Compression (1K Byte = 1024 Bytes) | VME File Size<br>No Compression<br>(1K Byte = 1024 Bytes) |

|---------------------|---------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|

|                     |                           | Algorithm File Size                                                    |                                                           |

|                     |                           | Data File Size                                                         |                                                           |

|                     | ispMACH 40                | 000                                                                    |                                                           |

|                     | Programming Mod           | le: Turbo                                                              |                                                           |

|                     | Operation: Erase, Pro     | gram, Verify                                                           |                                                           |

| LC4032V/B/C/ZC      | 172                       | 1KB                                                                    | 8KB                                                       |

| LA4032V/ZC          |                           | 3КВ                                                                    |                                                           |

| LC4064V/B/C/ZC-32IO | 352                       | 1KB                                                                    | 12KB                                                      |

| LA4064V/ZC-32IO     |                           | 4KB                                                                    |                                                           |

| LC4064V/B/C/ZC      | 356                       | 1KB                                                                    | 13KB                                                      |

| LA4064V/ZC          |                           | 5KB                                                                    | -                                                         |

| LC4128V/B/C/ZC      | 740                       | 1KB                                                                    | 22KB                                                      |

| LA4128V/ZC          |                           | 10KB                                                                   | -                                                         |

| LC4256V/B/C/ZC      | 1592                      | 1KB                                                                    | 41KB                                                      |

|                     |                           | 19KB                                                                   |                                                           |

| LC4256V/B/C-160IO   | 1624                      | 1KB                                                                    | 43KB                                                      |

|                     |                           | 20KB                                                                   |                                                           |

| LC4384V/B/C         | 2616                      | 1KB                                                                    | 65KB                                                      |

|                     |                           | 31KB                                                                   |                                                           |

| LC4512V/B/C         | 3632                      | 1KB                                                                    | 89KB                                                      |

|                     |                           | 43KB                                                                   | _                                                         |

|                     | ispMACH 400               | )0ZE                                                                   | 1                                                         |

|                     | Programming Mod           |                                                                        |                                                           |

|                     | Operation: Erase, Pro     | gram, Verify                                                           |                                                           |

| LC4032ZE            | 172                       | 1KB                                                                    | 8KB                                                       |

|                     |                           | 3KB                                                                    |                                                           |