# I<sup>2</sup>C Master Controller

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

### **Contents**

| 1. Introduction                                                                          | 4  |

|------------------------------------------------------------------------------------------|----|

| 2. Features                                                                              | 4  |

| 3. Functional Description                                                                | 4  |

| 4. Pin Descriptions                                                                      | 5  |

| 5. Design Modules                                                                        | 5  |

| 5.1. I <sup>2</sup> C Bus Control FSM                                                    | 6  |

| 5.2. I <sup>2</sup> C Master Control FSM                                                 | 6  |

| 6. Internal Register Map                                                                 | 6  |

| 7. Register Bit Descriptions                                                             | 7  |

| 8. Timing Diagram                                                                        | 8  |

| 9. Operation Sequence                                                                    | 8  |

| 9.1. I <sup>2</sup> C Master Transmit Operation                                          | 8  |

| 9.2. I <sup>2</sup> C Master Receive Operation                                           | 9  |

| 9.3. Repeated Start Transactions                                                         | 9  |

| 10. HDL Simulation                                                                       | 10 |

| 11. Implementation                                                                       | 11 |

| References                                                                               | 12 |

| Technical Support Assistance                                                             |    |

| Revision History                                                                         | 14 |

| Figure 3.1. Block Diagram                                                                | 4  |

| Figure 5.1. Functional Block Diagram                                                     |    |

| Figure 8.1. Timing Diagram for Read and Write Data Transfer                              |    |

| Figure 9.1. Master Transmit Operation                                                    |    |

| Figure 9.2. Master Receive Operation                                                     |    |

| Figure 9.3. Repeated Start Operation                                                     |    |

| Figure 10.1. HDL Simulation Waveform                                                     |    |

| Figure 10.2. Simulation Waveform Showing the START Bit of the Configuration Register and |    |

| Figure 10.3. Timing Waveforms Showing Configure START and Rx Bits Along with Cmd sta     |    |

| I2C Busy Bits                                                                            |    |

| Figure 10.4. Simulation Timing Diagram Showing Transmit and Receive Operations           |    |

| Tigare 10. It officiation thining oraginal officiality and receive operations            |    |

|                                                                                          |    |

|                                                                                          |    |

| Tables                                                                                   |    |

| Table 4.1. Pin Descriptions                                                              | 5  |

| Table 6.1. Register List                                                                 |    |

| Table 7.1. Register Bit Descriptions                                                     |    |

| Table 11.1. Performance and Resource Utilization                                         |    |

#### 1. Introduction

$I^2C$  or Inter-Integrated Circuit is a popular serial interface protocol that is widely used in many electronic systems. The  $I^2C$  interface is a two-wire interface capable of half-duplex serial communication at moderate to high speeds of up to a few megabits per second. There are thousands of  $I^2C$  peripherals on the market today, ranging from data converters to video processors. The  $I^2C$  bus is a good choice for designs that need to communicate with low-speed peripherals due to its simplicity and low cost.

The I<sup>2</sup>C Master Controller reference design is implemented in Verilog. The Lattice iCECube2™ Place and Route tool integrated with the Lattice Synthesis Engine (LSE) tool is used for the implementation of the design. The design uses an iCE40™ ultra low density FPGA and can be targeted to other iCE40 family members.

#### 2. Features

- 7-bit slave address support

- Supports operation at 100 kHz (Standard Mode) and 400 kHz (Fast Mode)

- Supports repeated start operations

- Interrupt generation logic

- Verilog RTL, test bench

## 3. Functional Description

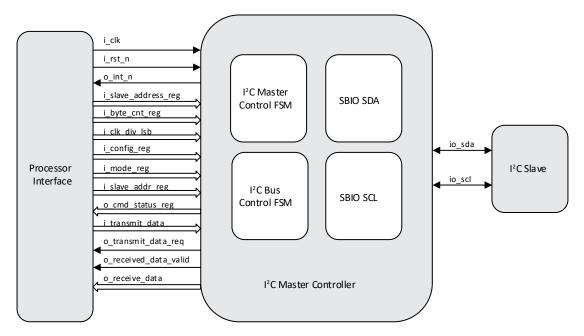

Figure 3.1. Block Diagram

## 4. Pin Descriptions

**Table 4.1. Pin Descriptions**

| Signal                    | Width | Туре   | Description                                                                                                                            |

|---------------------------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                     | 1     | Input  | System clock operating at 32 MHz                                                                                                       |

| i_rst_n                   | 1     | Input  | Asynchronous active-low system reset                                                                                                   |

| o_int_n                   | 1     | Output | Active-low processor interrupt                                                                                                         |

| i_slave_addr_reg          | 8     | Input  | 7-bit I <sup>2</sup> C slave address                                                                                                   |

| i_byte_cnt_reg            | 8     | Input  | Sets the number of data bytes to be read or written for the I <sup>2</sup> C transaction                                               |

| i_clk_div_lsb             | 8     | Input  | Sets the lower byte of the clock divider that is used to generate SCL from CLK. The upper three bits are located in the mode register. |

| i_config_reg              | 6     | Input  | Used to configure the I <sup>2</sup> C Master Controller (see Table 4.1)                                                               |

| i_mode_reg                | 8     | Input  | Sets the various modes of operation like speed, read/write (see Table 4.1)                                                             |

| o_cmd_status_reg          | 8     | Output | Lets the user know the status of the operation, I <sup>2</sup> C bus (see Table 4.1)                                                   |

| o_start_ack               | 1     | Output | Acknowledge to the start bit provided by the user through i_config_reg                                                                 |

| i_transmit_data           | 8     | Input  | Data to be transmitted over the SDA line to the I <sup>2</sup> C slave                                                                 |

| o_transmit_data_requested | 1     | Output | Lets the user know that transmit data is required                                                                                      |

| o_received_data_valid     | 1     | Output | A '1' corresponds to valid data availability on the o_receive_data line                                                                |

| o_receive_data            | 8     | Output | Received data bus                                                                                                                      |

| io_scl                    | 1     | Inout  | I <sup>2</sup> C clock line                                                                                                            |

| io_sda                    | 1     | Inout  | I <sup>2</sup> C data line                                                                                                             |

## 5. Design Modules

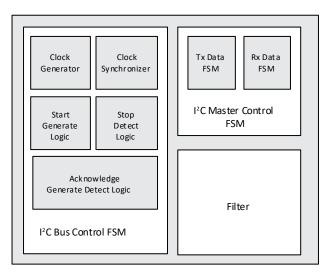

The design includes the modules shown in Figure 5.1.

Figure 5.1. Functional Block Diagram

#### 5.1. I<sup>2</sup>C Bus Control FSM

The I<sup>2</sup>C Bus Control FSM is comprised of the Clock Generator/Synchronizer, Start/Stop generate/detect logic and Acknowledge generate/detect logic.

The Clock Generation and Synchronization logic generates the I<sup>2</sup>C clock signal SCL, based on the system clock and clock divide factors configured by the processor. Due to the nature of the I<sup>2</sup>C bus, the actual SCL clock that is seen by all devices on the bus may not be running at the same frequency that the master generates. This module starts counting its SCL low period when the current master drives SCL low. Once a device's clock has gone low, the master holds the SCL line low until the clock high state is reached. When all devices have counted off their LOW period, the clock line will be released and goes HIGH. There will then be no difference between the device clocks and the state of the SCL line, and all the devices will start counting their HIGH periods. The first device to complete its HIGH period will again pull the SCL line LOW. In this way, a synchronized SCL clock is generated with its LOW period determined by the device with the longest clock LOW period, and its HIGH period determined by the one with the shortest clock HIGH period.

The start/stop logic generates and detects start and stop events on the I<sup>2</sup>C bus. The detection of start and stop events is necessary to determine whether or not the I<sup>2</sup>C bus is in use by another master on the bus when the primary master gets a START signal from the processor. When the I<sup>2</sup>C bus is idle, both SCL and SDA are pulled high by passive pull-ups. A start condition is signalled by transitioning SDA from high to low while SCL is still high. Likewise, a stop condition is signalled by transitioning SDA from low to high while SCL is high.

#### 5.2. I<sup>2</sup>C Master Control FSM

For controlling data transfer, the I<sup>2</sup>C master makes use of a control FSM, along with counters for controlling the bits and bytes. The byte counter is an 8-bit counter that keeps track of the number of bytes that have been written or read during the I<sup>2</sup>C transaction. This counter increments after each byte has been written to or read from the external I<sup>2</sup>C slave device. The count is then compared with the byte count register. If the value is a match, the I<sup>2</sup>C Master Controller considers the transaction complete, issues a stop signal on the I<sup>2</sup>C bus, asserts the RXTX\_DONE flag and waits for the next transaction to be initiated from the processor. This counter is fully controlled by the main control FSM.

## 6. Internal Register Map

The I<sup>2</sup>C Master Controller configuration can be performed on run-time. Table 6.1 lists the registers available to the user.

Table 6.1. Register List

| Port/Bit         | 7        | 6       | 5       | 4       | 3       | 2         | 1       | 0       |

|------------------|----------|---------|---------|---------|---------|-----------|---------|---------|

| i_slave_addr_reg |          | SADR[6] | SADR[5] | SADR[4] | SADR[3] | SADR[2]   | SADR[1] | SADR[0] |

| i_byte_cnt_reg   | BCNT[7]  | BCNT[6] | BCNT[5] | BCNT[4] | BCNT[3] | BCNT[2]   | BCNT[1] | BCNT[0] |

| i_clk_div_lsb    | DIV[7]   | DIV[6]  | DIV[5]  | DIV[4]  | DIV[3]  | DIV[2]    | DIV[1]  | DIV[0]  |

| i_config_reg     |          |         | RESET   | ABORT   | TX_IE   | RX_IE     | INT_CLR | START   |

| i_mode_reg       | BPS[1]   | BPS[0]  |         | ACK_POL | RW_MODE | DIV[10]   | DIV[9]  | DIV[8]  |

| o_cmd_status_reg | I2C_BUSY | TX_DONE | RX_DONE | TX_ERR  | RX_ERR  | ABORT_ACK |         |         |

## 7. Register Bit Descriptions

**Table 7.1. Register Bit Descriptions**

| Register Bit                       | Description                                                                                                                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_slave_addr_reg[7:0]              | 7-bit slave address                                                                                                                                                                                                             |

| I_byte_cnt_reg[7:0]                | Sets the number of data bytes to be written or read for the I <sup>2</sup> C transaction. For example, set the register to '8' to transfer eight data bytes.                                                                    |

| i_clk_div_lsb[7:0]                 | Sets the lower byte of the clock divider that is used to generate SCL from CLK. The upper three bits are located in the Mode Register. Please note that DIV[0] is not used since only even DIV values are supported.            |

| i_config_reg[5] – RESET –          | Writing a '1' will reset this I <sup>2</sup> C Master Controller.                                                                                                                                                               |

| i_config_reg[4] - ABORT –          | Writing a '1' will stop the current I <sup>2</sup> C transaction in progress. This bit is cleared by the ABORT_ACK status bit in the Command Status Register.                                                                   |

| i_config_reg[3] - TX_IE -          | Set this bit high to enable interrupt generation on transmit completion and a STOP is issued, or on any error.                                                                                                                  |

| i_config_reg[2] - RX_IE            | Set this bit high to enable interrupt generation on receive completion and a STOP is issued, or on any error.                                                                                                                   |

| i_config_reg[1] - INT_CLR          | Writing a '1' will clear all bits in the Command Status Register except the I2C_BUSY bit. Write a '0' to clear this bit.                                                                                                        |

| i_config_reg[0] - START            | Write a '1' to start an I <sup>2</sup> C transaction. This bit is auto-cleared after the master has successfully arbitrated and acquired the I <sup>2</sup> C bus.                                                              |

| i_mode_reg[7:6] - BPS[1:0]         | Selects the I2C speed mode (2'b00 = standard, 2'b01 = fast, others are reserved)                                                                                                                                                |

| i_mode_reg[4] - ACK_POL            | Sets the behavior of ACK during the last byte of a master read transaction. This bit should be '0' for ACK and '1' for NACK. If a repeat START is not used, this bit should be set to '1' (NACK) for I2C compliance.            |

| i_mode_reg[3]                      | RW_MODE – Sets the read or write operation on the I <sup>2</sup> C bus ('0' = write, '1' = read)                                                                                                                                |

| i_mode_reg[2:0]                    | DIV[10:8] – The upper three bits of the clock divide facto                                                                                                                                                                      |

| o_cmd_status_reg[7]                | I2C_BUSY – This read-only status bit indicates that the bridge is busy performing a data transaction and a STOP has not been issued. This bit reflects the state of the I <sup>2</sup> C bus and cannot be cleared by the user. |

| o_cmd_status_reg[6] -<br>TX_DONE   | This read-only status bit indicates that the I <sup>2</sup> C write operation issued has been completed, but the STOP condition may still be in progress.                                                                       |

| o_cmd_status_reg[5] -<br>RX_DONE   | This read-only status bit indicates that the I <sup>2</sup> C read operation issued has been completed, but the STOP condition may still be in progress.                                                                        |

| o_cmd_status_reg[4] - TX_ERR       | This read-only status bit indicates that an error has occurred during the I <sup>2</sup> C write operation.                                                                                                                     |

| o_cmd_status_reg[3] - RX_ERR       | This read-only status bit indicates that an error has occurred during the I <sup>2</sup> C read operation.                                                                                                                      |

| o_cmd_status_reg[2] -<br>ABORT_ACK | This read-only status bit indicates that the ABORT command has been completed. The user should clear the proper FIFO and status bits afterwards.                                                                                |

Note that all status bits, except I2C\_BUSY, are cleared by writing a '1' to the INTR\_CLR bit in the configuration 3 register.

### 8. Timing Diagram

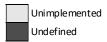

Figure 8.1 shows the timing diagram for read and write data transfer to the I<sup>2</sup>C Master Controller.

Figure 8.1. Timing Diagram for Read and Write Data Transfer

### 9. Operation Sequence

The operation sequence for transmit, receive and repeated start is illustrated below.

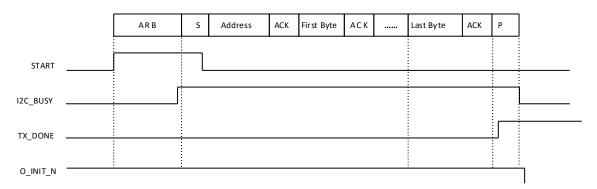

### 9.1. I<sup>2</sup>C Master Transmit Operation

Figure 9.1 illustrates the basic transmit operation of the I2C Master Controller. Note that 'S' is notation for START and 'P' is notation for STOP.

By writing a '1' to the START bit of the configuration register, the operation is started.

Figure 9.1. Master Transmit Operation

The I2C\_BUSY bit will go high before the START bit is cleared to indicate an active I<sup>2</sup>C transaction.

- 1. The I2C\_BUSY bit will clear itself after the entire I2C transaction is complete and the bus is idled.

- 2. The TX\_DONE signal is asserted after the last byte of transmit data has been sent, but the STOP condition may not have completed yet.

- 3. I2C\_BUSY is cleared after the STOP condition has completed and the bus is idled.

- 4. The interrupt is asserted if the transmit interrupt enable bit (TX\_IE) is set.

- 5. If the slave device did not assert ACK, then TX\_ERR and INT\_N will both be asserted.

© 2015-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

9

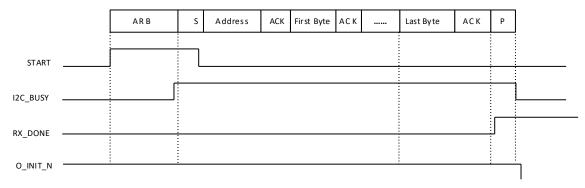

### 9.2. I<sup>2</sup>C Master Receive Operation

Figure 9.2 illustrates the basic receive operation of the I<sup>2</sup>C Master Controller.

Figure 9.2. Master Receive Operation

- 1. By writing a '1' to the START bit of the configuration register, the operation is started.

- 2. The I2C\_BUSY bit will go high before the START bit is cleared to indicate an active I<sup>2</sup>C transaction. The I2C\_BUSY bit will clear itself after the entire I<sup>2</sup>C transaction is complete and the bus is idled.

- 3. The RX\_DONE signal is asserted after the last byte of receive data have been latched, but the STOP condition may not have completed yet.

- 4. I2C BUSY is cleared after the STOP condition has completed and bus is idled.

- 5. The interrupt is asserted if the receiver interrupt enable bit (RX\_IE) is set.

- 6. If the slave device did not assert ACK during the address phase, then RX\_ERR and INT\_N will both be asserted.

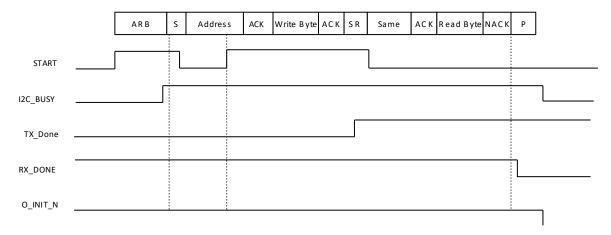

### 9.3. Repeated Start Transactions

To overcome the limited addresses provide by the I<sup>2</sup>C bus, some I<sup>2</sup>C slaves uses repeated start transactions to allow indirect access of internal registers. The I<sup>2</sup>C Master Controller supports the generation of repeat start transactions. Figure 9.3 illustrates a typical repeat start I<sup>2</sup>C transaction.

Note that "SR" is the I<sup>2</sup>C notation for a repeated start.

Figure 9.3. Repeated Start Operation

By writing a '1' to the START bit of the configuration register, the operation is started.

- 1. The initial parts of sequence are identical to the set-up for a normal read or write transaction shown earlier.

- 2. To perform a repeated start transaction, the user needs to update the Byte Count Register, Mode Register, and finally the configure register is written with '1' for the START bit. Note that the second START command needs to be issued before the TX\_DONE /RX\_DONE phase of the first transaction.

- 3. Do not change the slave address for the repeated START transaction; otherwise, a STOP is generated and another full transaction is executed.

- 4. I2C\_BUSY is cleared after the STOP condition is complete and the bus is idled.

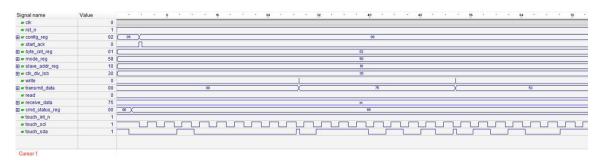

### 10. HDL Simulation

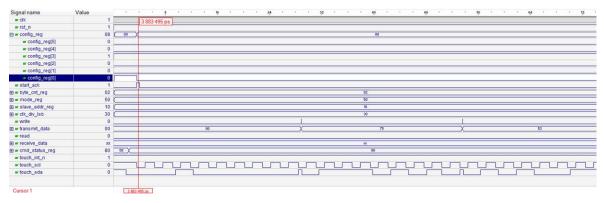

Figure 10.1. HDL Simulation Waveform

Figure 10.2. Simulation Waveform Showing the START Bit of the Configuration Register and Acknowledge Bit

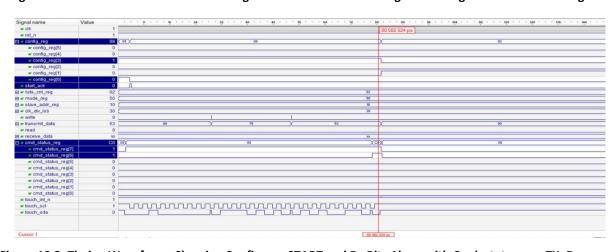

Figure 10.3. Timing Waveforms Showing Config\_reg START and Rx Bits Along with Cmd\_status\_reg TX\_Done and I2C\_Busy Bits

Figure 10.4. Simulation Timing Diagram Showing Transmit and Receive Operations

## 11. Implementation

This design is implemented in Verilog. When using this design in a different device, density, speed or grade, performance and utilization may vary.

**Table 11.1. Performance and Resource Utilization**

| Device Family      | Language | Synthesis Tool | Utilization<br>(LUTs) | f <sub>MAX</sub> (MHz) | I/Os | Architecture<br>Resources |

|--------------------|----------|----------------|-----------------------|------------------------|------|---------------------------|

| iCE40 <sup>1</sup> | Verilog  | LSE            | 295                   | 113.55                 | 65   | N/A                       |

|                    |          | Syn Pro        | 282                   | 77.52                  | 65   | N/A                       |

#### Note:

1. Performance utilization characteristics are generated using iCE40LP1K-CM121 with iCEcube2 2014.08 design software.

## References

• iCE40 LP/HX Family Data Sheet (FPGA-DS-02029)

## **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

## **Revision History**

#### Revision 1.2, February 2020

| Section     | Change Summary                                        |  |  |

|-------------|-------------------------------------------------------|--|--|

| All         | Changed document number from RD1139 to FPGA-RD-02155. |  |  |

|             | Updated document template.                            |  |  |

| Disclaimers | Added this section.                                   |  |  |

#### Revision 1.1, February 2015

| Section                      | Change Summary                                                                                                                 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Introduction                 | Updated Introduction section. Changed Synplify Pro to Lattice Synthesis Engine (LSE).                                          |

| Implementation               | Updated Implementation section. Updated Table 11.1, Performance and Resource Utilization.  • Changed Utilization (LUTs) value. |

| References                   | Updated References section.                                                                                                    |

| Technical Support Assistance | Updated Technical Support Assistance information.                                                                              |

#### Revision 1.0, October 2012

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

www.latticesemi.com