# CSI-2/DSI D-PHY Tx IP

IP Version: 2.4.0

# **User Guide**

FPGA-IPUG-02080-2.5

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Acronym  | s in This Document                                                                                     | 8      |

|----------|--------------------------------------------------------------------------------------------------------|--------|

| 1. Intro | oduction                                                                                               |        |

| 1.1.     | Overview of the IP                                                                                     | 9      |

| 1.2.     | Quick Facts                                                                                            | 9      |

| 1.3.     | IP Support Summary                                                                                     | 10     |

| 1.4.     | Features                                                                                               | 11     |

| 1.4.     | 1. Hard MIPI D-PHY Tx IP Core Features                                                                 | 11     |

| 1.4.     | 2. Soft MIPI D-PHY Tx IP Core Features                                                                 | 11     |

| 1.5.     | Licensing and Ordering Information                                                                     | 11     |

| 1.6.     | Hardware Support                                                                                       | 11     |

| 1.7.     | Minimum Device Requirements                                                                            | 11     |

| 1.8.     | Naming Conventions                                                                                     | 11     |

| 1.8.     | 1. Nomenclature                                                                                        | 11     |

| 1.8.     | 2. Signal Names                                                                                        | 11     |

| 2. Fun   | ctional Description                                                                                    | 12     |

| 2.1.     | IP Architecture Overview                                                                               | 12     |

| 2.2.     | User Interfaces                                                                                        | 15     |

| 2.2.     | 1. LMMI Device Target                                                                                  | 15     |

| 2.2.     | 2. AXI4-Stream Device Receiver                                                                         | 16     |

| 2.3.     | Wrapper Module                                                                                         | 17     |

| 2.3.     | 1. Hard D-PHY Module                                                                                   | 17     |

| 2.3.     | 2. Soft D-PHY Module                                                                                   | 17     |

| 2.3.     | 3. External PLL                                                                                        | 18     |

| 2.3.     | 4. Internal PLL                                                                                        | 18     |

| 2.4.     | Packet Formatter Module                                                                                | 19     |

| 2.5.     | Global Operation Module                                                                                | 19     |

| 2.6.     | Timing Diagrams                                                                                        | 21     |

| 2.6.     | 1. Initial Skew Calibration for Data Rates Above 1.5 Gbps                                              | 22     |

| 2.6.     | 2. Packet Transmission in CSI-2/DSI Interfaces with Packet Formatter for Soft D-PHY and Hard D-PHY wit | h Soft |

|          | CIL (CIL Bypass is Checked)                                                                            | 22     |

| 2.6.     | 3. Packet Transmission in CSI-2/DSI Interface with Packet Formatter for Hard D-PHY with Hardened CIL ( | CIL    |

|          | Bypass is Unchecked)                                                                                   | 24     |

| 2.6.     | 4. Packet Transmission in CSI-2/DSI Interface without Packet Formatter                                 | 24     |

| 2.6.     | 5. Non-Continuous D-PHY Clock Mode                                                                     | 26     |

| 2.6.     | 6. Manual Control of D-PHY Clock Lane to LP                                                            | 26     |

| 2.6.     | 7. Enable Periodic Skew Calibration                                                                    | 27     |

| 2.6.     | 8. CIL-Enabled Debug Ports                                                                             | 27     |

| 2.6.     | 9. Timing Configuration Registers                                                                      | 28     |

| 2.6.     | 10. Byte Data Arrangement                                                                              | 28     |

| 2.7.     | Dynamic Reconfiguration                                                                                | 29     |

| 3. IP P  | arameter Description                                                                                   | 30     |

| 3.1.     | General                                                                                                | 30     |

| 3.2.     | Protocol Timing Parameters                                                                             | 33     |

| 4. Sign  | al Description                                                                                         | 36     |

| 4.1.     | Clock and Reset Interface                                                                              | 36     |

| 4.2.     | D-PHY Tx                                                                                               |        |

| 4.3.     | LMMI Device Target                                                                                     | 41     |

| 4.4.     | AXI4-Stream Device Receiver                                                                            | 41     |

| 4.5.     | Debug Interface                                                                                        | 41     |

| 5. Regi  | ister Description                                                                                      | 43     |

| 5.1.     | Hard Configured D-PHY Tx IP Configuration Registers (MIPI Programmable Bits)                           | 43     |

|          |                                                                                                        |        |

| 5.2. D-PHY Tx IP Configuration Registers for Timing Parameters    | 48 |

|-------------------------------------------------------------------|----|

| 5.3. D-PHY Tx IP Packet Formatter Registers                       |    |

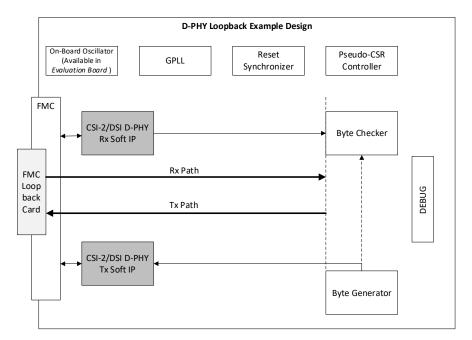

| 6. Example Design                                                 | 51 |

| 6.1. Example Design Supported Configuration                       | 51 |

| 6.2. Overview of the Example Design and Features                  | 51 |

| 6.3. Example Design Components                                    | 52 |

| 6.3.1. Byte Generator                                             | 52 |

| 6.3.2. Byte Checker                                               | 52 |

| 6.3.3. CSI-2/DSI D-PHY Tx Soft IP                                 | 52 |

| 6.3.4. CSI-2/DSI D-PHY Rx Soft IP                                 | 52 |

| 6.3.5. PLL                                                        |    |

| 6.3.6. Reset Synchronizer                                         |    |

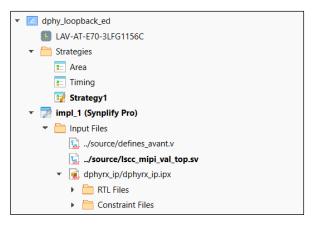

| 6.4. Generating and Using the Example Design                      | 53 |

| 6.4.1. Using the Example Design Sample Project                    | 53 |

| 6.4.2. Changing Configuration of the Example Design               | 53 |

| 6.5. Simulating the Example Design                                | 54 |

| 6.6. Hardware Testing                                             | 56 |

| 7. Designing with the IP                                          | 60 |

| 7.1. Generating and Instantiating the IP                          | 60 |

| 7.1.1. Generated Files and File Structure                         |    |

| 7.2. Design Implementation                                        | 62 |

| 7.3. Timing Constraints                                           |    |

| 7.4. Specifying the Strategy                                      | 64 |

| 7.5. Running Functional Simulation                                |    |

| 7.5.1. Simulation Results                                         | 67 |

| 8. Debugging                                                      | 68 |

| 8.1. Debug Methods                                                |    |

| 8.2. Debug Tools                                                  |    |

| 8.2.1. Reveal Analyzer                                            | 68 |

| 9. Design Considerations                                          |    |

| 9.1. Design Considerations When D-PHY PLL Mode is Set to External |    |

| 9.2. Limitations                                                  |    |

| Appendix A. Resource Utilization                                  |    |

| References                                                        |    |

| Technical Support Assistance                                      | 74 |

| Revision History                                                  | 75 |

## **Figures**

| Figure 1.1. D-PHY Tx IP                                                                                                       | ۵  |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Enabled                                                  |    |

| Figure 2.2. D-PHY Tx IP Block Diagram with AXI4-Stream Enabled and LMMI Disabled                                              |    |

| Figure 2.3. D-PHY Tx IP Block Diagram with AXI4-Stream Disabled and LMMI Enabled                                              |    |

| Figure 2.4. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Disabled                                                 |    |

| Figure 2.5. AXI4-Stream Enabled and Packet Formatter Enabled Data Format                                                      |    |

| Figure 2.6. AXI4-Stream Enabled, Packet Formatter Enabled and Extended Virtual Channel ID Enabled Data Format                 |    |

| Figure 2.7. AXI4-Stream Enabled and Packet Formatter Disabled Data Format                                                     |    |

| Figure 2.8. Sample Topology when Enable Edge Clock Synchronizer and Divider is Unchecked                                      |    |

| Figure 2.9. Internal PLL Block Diagram                                                                                        |    |

| Figure 2.10. MIPI D-PHY Tx LP to HS Transition Flow Diagram on Data Lanes                                                     |    |

| Figure 2.11. High-Speed Entry Sequence and Payload Data Transmission Cycle on Data Lanes                                      |    |

| Figure 2.12. High-Speed Data Transmission in Skew Calibration                                                                 |    |

| Figure 2.13. c2d_ready_o Timing for Non-Continuous D-PHY Clock Mode                                                           |    |

| Figure 2.14. c2d_ready_o Timing for Continuous D-PHY Clock Mode                                                               | 22 |

| Figure 2.15. D-PHY Tx Input Bus for Short Packet Transmission in CSI-2/DSI Interfaces                                         | 23 |

| Figure 2.16. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2/DSI Interface                                           |    |

| Figure 2.17. D-PHY Tx Input Bus for Short Packet Transmission in CSI-2/DSI Interfaces ( <i>CIL Bypass</i> Unchecked)          |    |

| Figure 2.18. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2/DSI Interface ( <i>CIL Bypass</i> Unchecked)            |    |

| Figure 2.19. D-PHY Tx Input Bus for LP Transmission in CSI-2/DSI Interface without Packet Formatter ( <i>D-PHY TX IP</i> = So |    |

| PHY or CIL Bypass Checked)                                                                                                    |    |

| Figure 2.20. D-PHY Tx Input Bus for Transmission without Packet Formatter (CIL Bypass Unchecked)                              |    |

| Figure 2.21. Example Configuration of Number of TX Lanes == 4, TX Gear == 16 with Unaligned Number of Bytes                   |    |

| Figure 2.22. D-PHY Tx Input Bus for Non-Continuous Clock Mode with CIL Bypass Unchecked (without Packet Formatt               |    |

| Figure 2.23. D-PHY Clock Lane Going to LP Mode Using the clk_hs_en_i Port                                                     |    |

| Figure 2.24. D-PHY Tx Input Bus to Enable Periodic Skew Calibration                                                           |    |

| Figure 2.25. CIL-Enabled Debug Ports                                                                                          |    |

| Figure 2.26. Timing Configuration Registers for Soft D-PHY or Hardened CIL Bypassed                                           |    |

| Figure 6.1. CSI-2/DSI D-PHY Tx to CSI-2/DSI D-PHY Rx Loopback Example Design Block Diagram                                    |    |

| Figure 6.2. Sample File List                                                                                                  | 53 |

| Figure 6.3. Example IP Settings                                                                                               | 54 |

| Figure 6.4. Example Generated IP Settings Section of the PDC File                                                             | 54 |

| Figure 6.5. Testbench Top File                                                                                                | 55 |

| Figure 6.6. Simulation Wizard GUI                                                                                             | 55 |

| Figure 6.7. Simulation Result                                                                                                 | 56 |

| Figure 6.8. Sample QRUN Command with MFCU Argument                                                                            | 56 |

| Figure 6.9. Gate-Level Simulation Example Design Compiler Directive                                                           | 56 |

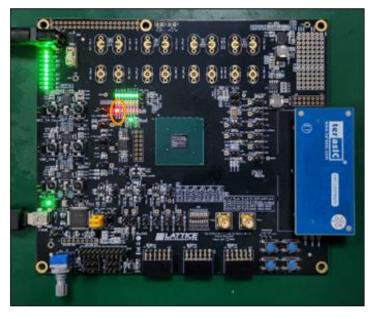

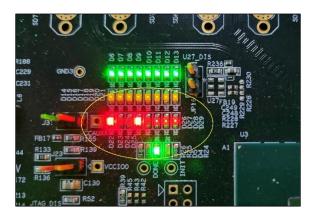

| Figure 6.10. Avant-E Evaluation Board with Terasic® FMC Loopback Card on FMC2 Connector (J54)                                 | 57 |

| Figure 6.11. CertusPro-NX Evaluation Board with FMC Loopback Card on FMC Connector (J48)                                      | 57 |

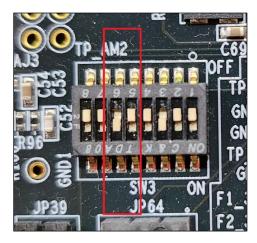

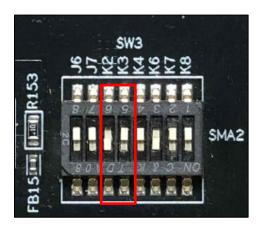

| Figure 6.12. DIP_SW Setting to Two Lanes on Avant-E Evaluation Board                                                          | 58 |

| Figure 6.13. DIP_SW Setting to Two Lanes on CertusPro-NX Evaluation Board                                                     | 58 |

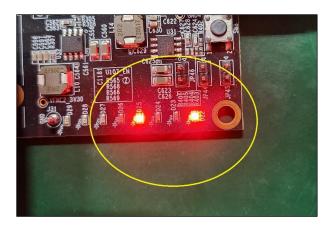

| Figure 6.14. Avant-E Evaluation Board LED Status for Successful Lane Reconfiguration                                          | 59 |

| Figure 6.15. CertusPro-NX Evaluation Board LED Status for Successful Lane Reconfiguration                                     | 59 |

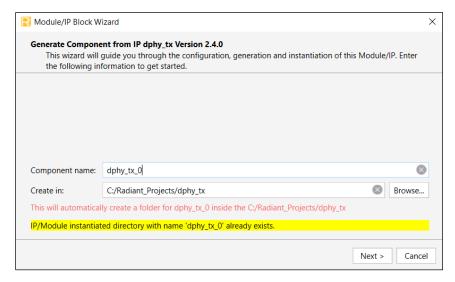

| Figure 7.1. Module/IP Block Wizard                                                                                            | 60 |

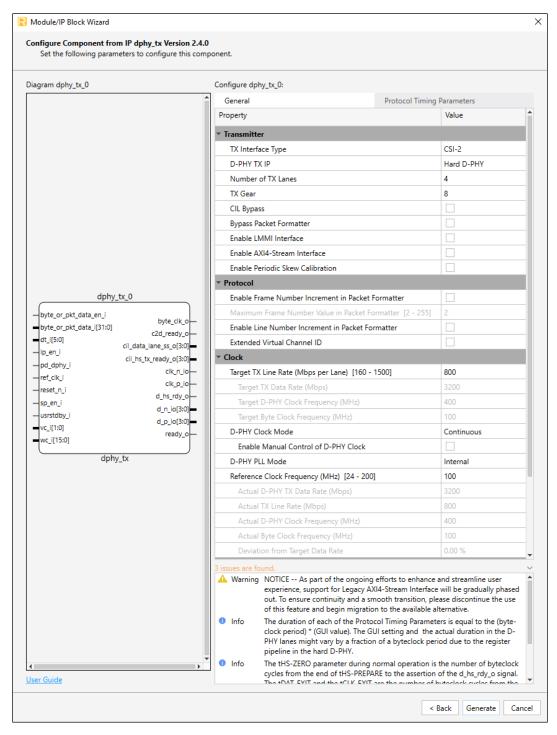

| Figure 7.2. IP Configuration                                                                                                  | 61 |

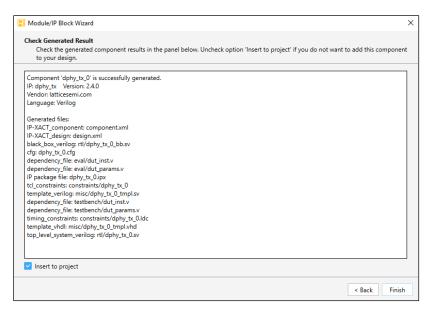

| Figure 7.3. Check Generated Result                                                                                            |    |

| Figure 7.4. Header of the Generated PDC Files                                                                                 |    |

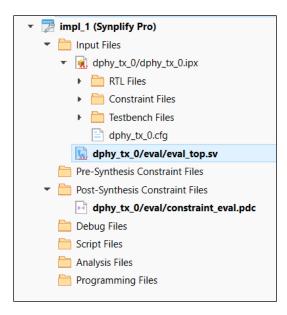

| Figure 7.5. Example Evaluation Project Settings                                                                               |    |

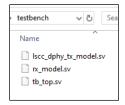

| Figure 7.6. Example Simulation Environment File Directory                                                                     |    |

| Figure 7.7. Adding USE_EVAL_TOP_DUT in the tb_top.sv File                                                                     |    |

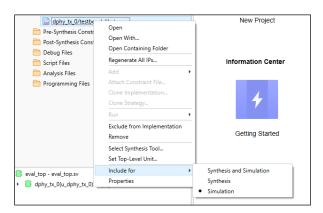

| Figure 7.8. Example Steps on How to Include File for Simulation Only                                                          |    |

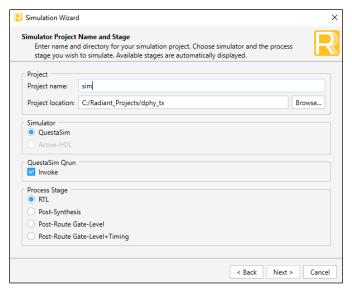

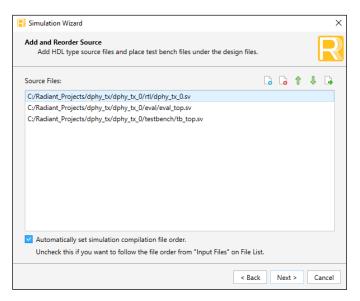

| Figure 7.9. Simulation Wizard                                                                                                 | 66 |

6

| Figure 7.10. Add and Reorder Source | 66 |

|-------------------------------------|----|

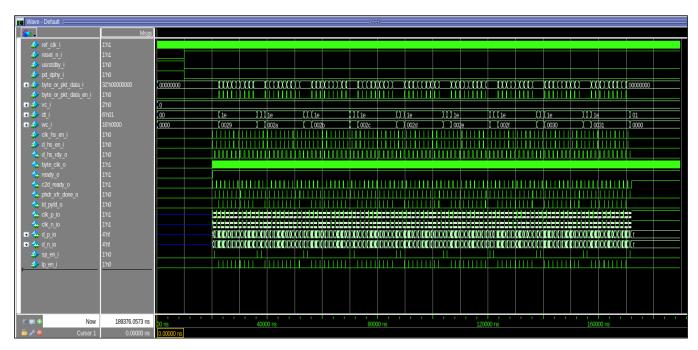

| Figure 7.11. Simulation Waveform    |    |

| Figure 7.12. Simulation Log         | 67 |

## **Tables**

| Table 1.1. CSI-2/DSI DPHY Tx IP Core Quick Facts                                                  | 9  |

|---------------------------------------------------------------------------------------------------|----|

| Table 1.2. CSI-2/DSI D-PHY Tx IP Support Readiness                                                | 10 |

| Table 2.1. User Interfaces and Supported Protocols                                                | 15 |

| Table 2.2. High-Speed Trail Timer for Different Data Rates                                        | 16 |

| Table 2.3. Interleaved versus Sequential Byte Data Input                                          | 28 |

| Table 2.4. D-PHY Tx Settings that Support Dynamic Reconfiguration                                 | 29 |

| Table 3.1. General Attributes                                                                     | 30 |

| Table 3.2. Protocol Timing Parameters Attributes <sup>1, 3, 5</sup>                               | 33 |

| Table 4.1. Clock and Reset Ports Description                                                      | 36 |

| Table 4.2. D-PHY Tx Signal Description                                                            | 37 |

| Table 4.3. LMMI Device Target Signal Description                                                  | 41 |

| Table 4.4. AXI4-Stream Device Receiver Signal Description                                         | 41 |

| Table 4.5. Debug Interface Signal Description                                                     | 41 |

| Table 5.1. Hard Configured D-PHY Tx Configuration Registers (MIPI Programmable Bits) <sup>6</sup> | 43 |

| Table 5.2. CN and CO Table of Values                                                              | 46 |

| Table 5.3. CM Table of Values                                                                     | 46 |

| Table 5.4. D-PHY Tx Configuration Registers for Timing Parameters                                 | 48 |

| Table 5.5. D-PHY Tx Status Registers for Timing Parameters                                        | 50 |

| Table 6.1. CSI-2/DSI D-PHY IP Configuration Supported by the Example Design                       | 51 |

| Table 6.2. Example Design File List                                                               | 53 |

| Table 7.1. Generated File List                                                                    | 62 |

| Table A.1. Device and Tool Tested                                                                 | 70 |

| Table A.2. Resource Utilization <sup>1,5</sup>                                                    | 70 |

| Table A.3. Device and Tool Tested                                                                 |    |

| Table A.4. Resource Utilization <sup>1,5</sup>                                                    | 71 |

| Table A.5. Device and Tool Tested                                                                 |    |

| Table A.6. Resource Utilization <sup>1,4</sup>                                                    | 71 |

| Table A.7. Device and Tool Tested                                                                 | 72 |

| Table A.8. Resource Utilization <sup>1,4</sup>                                                    | 72 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                          |

|---------|-------------------------------------|

| AXI     | Advance eXtensible Interface        |

| CIL     | Control and Interface Logic         |

| CSI-2   | Camera Serial Interface-2           |

| CRC     | Cyclic Redundancy Check             |

| DDR     | Double Data Rate                    |

| DSI     | Display Serial Interface            |

| EBR     | Embedded Block RAM                  |

| ECC     | Error Correction Code               |

| ECLK    | Edge Clock                          |

| EoTP    | End of Transmission Packet          |

| FPGA    | Field-Programmable Gate Array       |

| FSM     | Finite State Machine                |

| HS      | High Speed                          |

| IP      | Intellectual Property               |

| LMMI    | Lattice Memory Mapped Interface     |

| LP      | Low Power                           |

| LSE     | Lattice Synthesis Engine            |

| MIPI    | Mobile Industry Processor Interface |

| PLL     | Phase-Locked Loop                   |

| RTL     | Register Transfer Level             |

| SDC     | Synopsys Design Constraints         |

| UI      | Unit Interval                       |

| ULPS    | Ultra Low Power State               |

| XML     | Extensible Markup Language          |

## 1. Introduction

#### 1.1. Overview of the IP

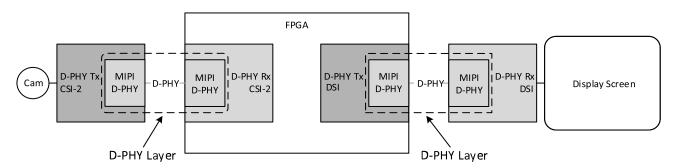

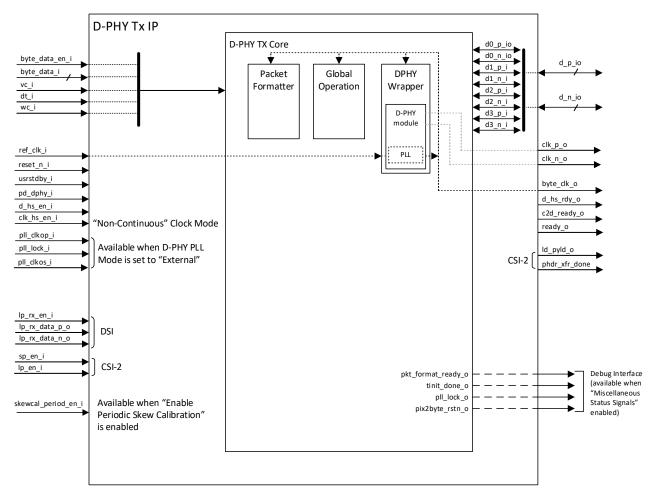

The Lattice Semiconductor CSI-2/DSI D-PHY Transmitter IP Core converts data bytes from a requestor to either DSI or CSI-2 data format for the Lattice Avant™, Nexus™, and Nexus 2 platforms as indicated in the dark gray boxes in Figure 1.1.

The CSI-2/DSI D-PHY Transmitter Submodule IP is intended for applications that require a D-PHY transmitter in the FPGA logic.

This IP supports both high-speed (HS) and low power (LP) modes. The payload data uses the high-speed mode whereas the control and status information are sent in low power mode.

The number of D-PHY data lanes for data transmission is configurable. This IP supports 1, 2, 3, or 4 data lanes.

Figure 1.1. D-PHY Tx IP

## 1.2. Quick Facts

Table 1.1 presents a summary of the CSI-2/DSI DPHY Tx IP Core.

Table 1.1. CSI-2/DSI DPHY Tx IP Core Quick Facts

| able 1.11 col 2/ 20101 111 1XII cole Quiek laces |                           |                                                                                        |  |  |  |  |  |

|--------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| ID Doggivernoute                                 | Supported Devices         | CrossLink™-NX, Certus™-NX, CertusPro™-NX, MachXO5™-NX, Lattice Avant, Certus-N2        |  |  |  |  |  |

| IP Requirements                                  | IP Changes <sup>1</sup>   | Refer to the CSI-2/DSI D-PHY Tx IP Release Notes (FPGA-RN-02041).                      |  |  |  |  |  |

| Danassana Hailinatian                            | Supported User Interfaces | LMMI/AXI4-Stream interface                                                             |  |  |  |  |  |

| Resource Utilization                             | Resource                  | See the Resource Utilization section                                                   |  |  |  |  |  |

|                                                  | Lattice Implementation    | IP Core v2.4.0 – Lattice Radiant software 2025.2                                       |  |  |  |  |  |

|                                                  | Cumthodia                 | Lattice Synthesis Engine (LSE)                                                         |  |  |  |  |  |

| Design Tool Support                              | Synthesis                 | Synopsys® Synplify Pro® for Lattice                                                    |  |  |  |  |  |

|                                                  | Simulation                | Refer to the Lattice Radiant Software User Guide for the list of supported simulators. |  |  |  |  |  |

#### Note:

1. In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

## 1.3. IP Support Summary

The table below shows the IP configurations that are hardware validated. Refer to the Features section for the full list of supported features.

Table 1.2. CSI-2/DSI D-PHY Tx IP Support Readiness

| Device<br>Family | TX<br>Interface<br>Type | Packet<br>Formatter | LMMI<br>Interface | D-PHY Clock<br>Mode           | Number of TX Lanes | TX Line Rate<br>(Mbps)                  | Radiant<br>Timing Model | Hardware<br>Validated |

|------------------|-------------------------|---------------------|-------------------|-------------------------------|--------------------|-----------------------------------------|-------------------------|-----------------------|

| Lattice<br>Avant | CSI-2                   | Enabled             | Disabled          | Continuous,<br>Non-continuous | 1, 4               | 800, 1000,<br>1500, 1800                | Preliminary             | Yes                   |

|                  |                         | Disabled            | Disabled          | Continuous                    | 2                  | 800                                     | Preliminary             | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 3                  | 1500                                    | Preliminary             | Yes                   |

|                  |                         |                     |                   |                               | 4                  | 1200, 1500                              | Preliminary             | Yes                   |

|                  | DSI                     | Enabled             | Disabled          | Continuous                    | 1, 4               | 800, 1200,<br>1500, 1800                | Preliminary             | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 4                  | 1500, 1800                              | Preliminary             | Yes                   |

|                  |                         | Disabled            | Disabled          | Continuous                    | 1                  | 1200, 1500                              | Preliminary             | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 1                  | 800                                     | Preliminary             | Yes                   |

| CertusPro-<br>NX | CSI-2                   | Enabled             | Disabled          | Continuous,<br>Non-continuous | 1, 4               | 800, 1000,<br>1500                      | Final                   | Yes                   |

|                  |                         |                     |                   | Continuous                    | 2                  | 1400, 1500                              | Final                   | Yes                   |

|                  |                         | Disabled            | Disabled          | Continuous                    | 2                  | 800                                     | Final                   | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 3                  | 1500                                    | Final                   | Yes                   |

|                  |                         |                     |                   |                               | 4                  | 1200, 1500                              | Final                   | Yes                   |

|                  | DSI Enabled Disabled Co |                     | Continuous        | 1, 4                          | 800, 1200,<br>1500 | Final                                   | Yes                     |                       |

|                  |                         |                     |                   |                               | 2                  | 900                                     | Final                   | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 4                  | 1500                                    | Final                   | Yes                   |

|                  |                         | Disabled            | Disabled          | Non-Continuous                | 1                  | 800                                     | Final                   | Yes                   |

|                  |                         |                     | Disabled          | Continuous                    | 1                  | 1200, 1500                              | Final                   | Yes                   |

| CrossLink-       | CSI-2                   | Enabled             | Disabled          | Continuous                    | 1                  | 800³, 1500²,³                           | Final                   | Yes                   |

| NX               |                         |                     |                   |                               | 2                  | 2400 <sup>1</sup> , 2500 <sup>1,2</sup> | Final                   | Yes                   |

|                  |                         |                     |                   |                               | 4                  | 1500 <sup>3, 4</sup>                    | Final                   | Yes                   |

|                  |                         | Disabled            | Disabled          | Continuous                    | 2                  | 1500 <sup>3</sup>                       | Final                   | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 4                  | 2500 <sup>2</sup>                       | Final                   | Yes                   |

|                  | DSI                     | Enabled             | Disabled          | Continuous                    | 4                  | 2400¹, 1500⁴,                           | Final                   | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 1                  | 1500 <sup>3</sup>                       | Final                   | Yes                   |

|                  |                         | Disabled            | Disabled          | Continuous                    | 2                  | 2500²                                   | Final                   | Yes                   |

|                  |                         |                     |                   | Non-Continuous                | 1                  | 2500¹, 1500³                            | Final                   | Yes                   |

#### Notes:

- 1. This covers only the hard D-PHY with CIL Bypass == checked and Tx Gear == 16.

- 2. This covers only the hard D-PHY with CIL Bypass == unchecked and Tx Gear == 16.

- 3. This covers only the hard D-PHY with CIL Bypass == checked and Tx Gear == 8.

- 4. This covers only the hard D-PHY with CIL Bypass == unchecked and Tx Gear == 8.

#### 1.4. Features

Key features of the CSI-2/DSI DPHY Tx IP include:

- Compliant with MIPI D-PHY v2.1, MIPI DSI v1.3, and MIPI CSI-2 v1.2 specifications.

- Supports 1, 2, 3, or 4 MIPI D-PHY data lanes.

- Supports DSI video modes.

- Supports low power (LP) mode during vertical and horizontal blanking.

- Option for AXI4-stream interface.

#### 1.4.1. Hard MIPI D-PHY Tx IP Core Features

- Maximum rate up to 2500 Mbps per lane available only in CrossLink-NX devices.

- Supports gearing: 8x, 16x.

- Option to use the dedicated D-PHY TX PLL or an external clock source.

- Output clock of the internal PLL is configurable through LMMI bus.

- Option to bypass the Control and Interface Logic (CIL).

- Reference clock frequency for the internal PLL from 24 MHz to 200 MHz.

- Internal PLL output clock frequency from 80 MHz to 1250 MHz.

- Hard D-PHY is supported only on CrossLink-NX devices.

- Supports periodic deskew calibration.

#### 1.4.2. Soft MIPI D-PHY Tx IP Core Features

- Maximum rate up to 1500 Mbps per lane for CrossLink-NX, Certus-NX, and CertusPro-NX devices.

- Maximum rate up to 1800 Mbps per lane for Lattice Avant devices.

- Supports gearing: 8x.

- External clock source.

- Soft D-PHY is supported on Lattice Avant, CrossLink-NX, Certus-NX, and CertusPro-NX devices.

- Supports dynamic lane and rate reconfiguration during run time. Refer to the <u>Dynamic Reconfiguration</u> section for details.

## 1.5. Licensing and Ordering Information

The CSI-2/DSI D-PHY Transmitter IP Core is provided at no additional cost with the Lattice Radiant software.

## 1.6. Hardware Support

Refer to the Example Design section for more information on the boards used.

## 1.7. Minimum Device Requirements

Refer to the Resource Utilization section for the minimum required resource to instantiate this IP.

### 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.8.2. Signal Names

- \_n are active low (asserted when value is logic 0)

- \_*i* are input signals

- o are output signals

- \_io are bidirectional signals

## 2. Functional Description

#### 2.1. IP Architecture Overview

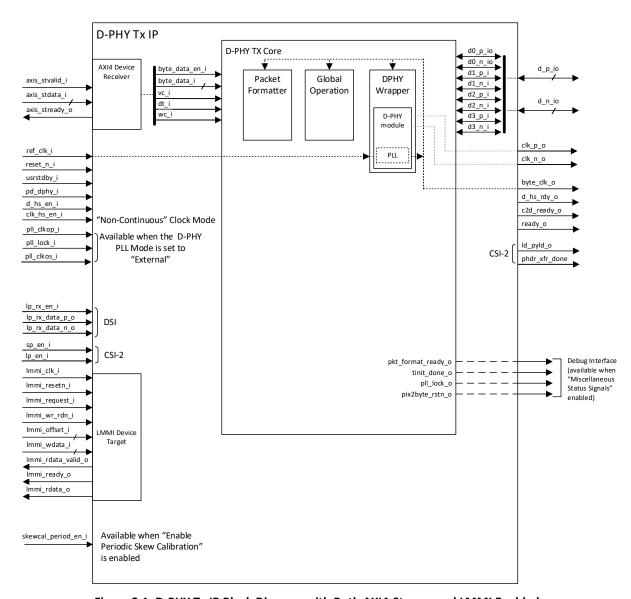

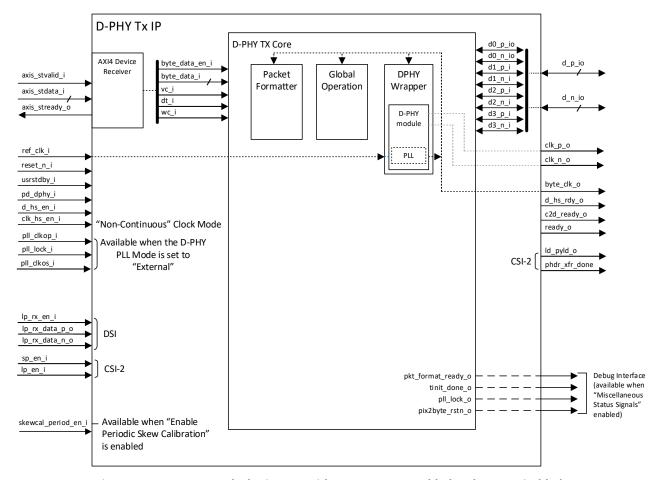

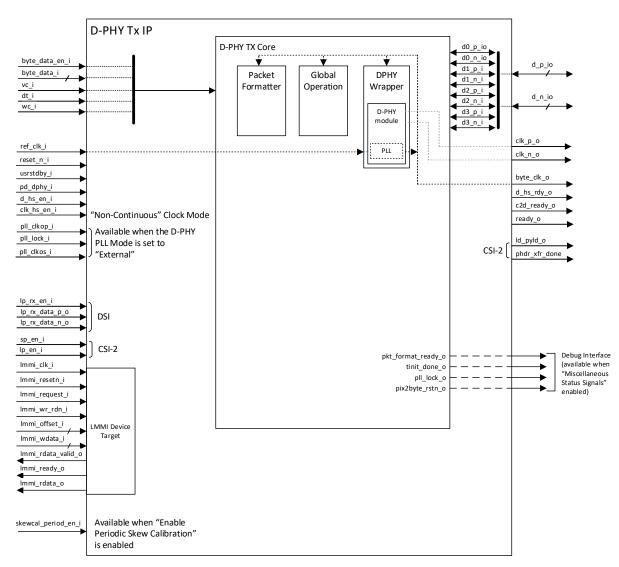

The CSI-2/DSI D-PHY Transmitter IP Core consists of the Global Operation Module, the D-PHY Tx Wrapper Module, an optional Packet Formatter Module, an optional AXI4 Stream Device Receiver, and an optional LMMI Target Module. Figure 2.1 shows the D-PHY Tx IP block with both LMMI Device and AXI4 Stream Device enabled. Figure 2.2 shows the D-PHY Tx IP block with AXI4 Stream Device enabled and LMMI Device disabled. Figure 2.3 shows the D-PHY Tx IP block with AXI4 Stream Device disabled and LMMI Device enabled. Figure 2.4 shows the D-PHY Tx IP block with both AXI4 Stream Device and LMMI Device disabled.

Figure 2.1. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Enabled

Figure 2.2. D-PHY Tx IP Block Diagram with AXI4-Stream Enabled and LMMI Disabled

Figure 2.3. D-PHY Tx IP Block Diagram with AXI4-Stream Disabled and LMMI Enabled

Figure 2.4. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Disabled

#### 2.2. User Interfaces

Table 2.1 lists the available user interface and protocols used on the D-PHY Tx IP.

Table 2.1. User Interfaces and Supported Protocols

| User Interface  | Supported Protocols | Description                                                                                                      |  |  |  |  |  |  |  |

|-----------------|---------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Control         | LMMI                | Configures the control registers of the D-PHY Tx IP, such as timing parameters.                                  |  |  |  |  |  |  |  |

| Device Receiver | AXI4                | Interface for receiving payload data (byte data or packet data with virtual channel, data type, and word count). |  |  |  |  |  |  |  |

#### 2.2.1. LMMI Device Target

The LMMI (Lattice Memory Mapped Interface) Device Target Module is used for configuring the control registers of the D-PHY Tx IP.

For more information on LMMI, see Lattice Memory Mapped Interface and Lattice Interrupt Interface User Guide (FPGA-UG-02039).

If the LMMI bus is not enabled, the Hard D-PHY configuration registers take on the corresponding values based on the IP configuration set in the user interface. See the Register Description section for the list of the configuration registers.

An example of how the T<sub>HS-TRAIL</sub> timing parameter changes depending on u\_PRG\_HS\_TRAIL[5:0] register is given in Table 2.2.

**Table 2.2. High-Speed Trail Timer for Different Data Rates**

| Data Rate | Min (ns) | Max (ns)   | u_PRG_HS_TRAIL [5:0] | THS-TRAIL (ns) |

|-----------|----------|------------|----------------------|----------------|

| 2.5 Gbps  | 61.6     | 109.8      | 011000               | 76.8           |

| 1.5 Gbps  | 62.67    | 113 001111 |                      | 80             |

| 1.0 Gbps  | 64       | 117        | 001100               | 96             |

| 500 Mbps  | 68       | 129        | 000110               | 96             |

| 250 Mbps  | 79       | 153        | 000100               | 128            |

| 80 Mbps   | 110      | 255        | 000010               | 200            |

The other timing parameters can be changed by changing corresponding registers following the same logic.

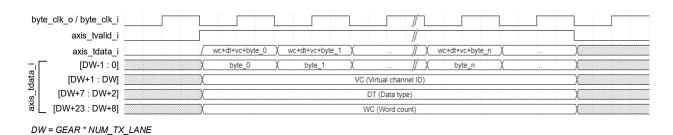

#### 2.2.2. AXI4-Stream Device Receiver

AXI4-Stream device receiver provides an interface for receiving payload data (byte data or packet data with virtual channel, data type, word count, and with or without extended virtual channel). This interface maps the input of the native interface as shown on Figure 2.5, Figure 2.6, and Figure 2.7.

Figure 2.5 shows data format when AXI4-Stream is ON and Packet Formatter is enabled. The data format is the same for configurations with LMMI disabled or enabled for dynamic reconfiguration. When LMMI is enabled, the NUM\_TX\_LANE value is the *Number of TX Lanes* setting. Figure 2.6 shows additional bits on data format when *Extended Virtual Channel ID* is enabled.

Figure 2.5. AXI4-Stream Enabled and Packet Formatter Enabled Data Format

Figure 2.6. AXI4-Stream Enabled, Packet Formatter Enabled and Extended Virtual Channel ID Enabled Data Format

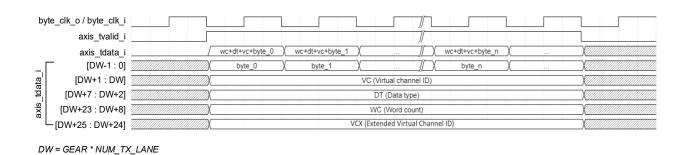

Figure 2.7 shows data format when AXI4-Stream is ON and Packet Formatter is disabled. Only byte data is available on the interface input data.

Figure 2.7. AXI4-Stream Enabled and Packet Formatter Disabled Data Format

If the AXI4-Stream device is not enabled, the following internal signals turn to top level input signals:

- byte or pkt data en i

- byte\_or\_pkt\_data\_i [...]

- vc i

- dt i

- wc i

- vcx i

#### 2.3. Wrapper Module

The D-PHY Tx Wrapper Module instantiates the PHY block. It may be configured to instantiate either a hardened D-PHY block or a soft logic implementation of the MIPI D-PHY.

Additional logic in the Wrapper Module is used to configure the connection between the PHY and the higher protocol layers.

#### 2.3.1. Hard D-PHY Module

The Hard D-PHY block is available only in CrossLink-NX devices.

When the hardened block is used, a dedicated D-PHY PLL may be used to generate the byte clock and the high-speed clock for the D-PHY clock lanes. This PLL may be reconfigured by accessing the hard D-PHY registers through the LMMI bus. If the LMMI is disabled, the PLL registers take on the value corresponding to the Reference Clock Frequency and the TX Line Rate per Lane attributes set in the user interface.

The hardened D-PHY block also has an option to use a clock source outside the Hard IP. This input clock pll\_clkop\_i is twice the D-PHY CLK lane and goes in directly to the hardened PHY.

#### 2.3.2. Soft D-PHY Module

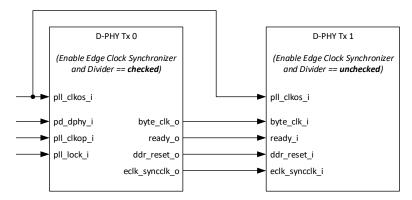

The D-PHY is implemented using the FPGA DDR elements. The D-PHY clock uses ECLK sync and clock divider elements. When *Enable Edge Clock Synchronizer and Divider == unchecked*, ports used to drive the DDR element are exposed as top-level ports of the IP. These ports are expected to be connected to the output of another D-PHY Tx instance which serves as the primary source of edge synchronizer and divider related clocks.

Figure 2.8. Sample Topology when Enable Edge Clock Synchronizer and Divider is Unchecked

This mode is useful when the design requires multiple Soft D-PHY Tx instances but is constrained by the number of ECLK sync and clock divider elements. For example, multiple instances are required to be located on the same bank. However, this feature is only valid when all the D-PHY Tx instances are required to be run at the same bit rate per lane. In the example above, both data interfaces on the D-PHY Tx 0 and D-PHY Tx 1 are synchronized to the byte\_clk\_o of the D-PHY Tx 0.

For details on building the Soft MIPI D-PHY interfaces, refer to the following documents:

- Certus-NX High-Speed I/O Interface (FPGA-TN-02216)

- CrossLink-NX High-Speed I/O Interface (FPGA-TN-02097)

- CertusPro-NX High-Speed I/O Interface (FPGA-TN-02244)

- Lattice Avant High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02300)

#### 2.3.3. External PLL

The Soft D-PHY needs external clock sources pll\_clkop\_i and pll\_clkos\_i to produce the byte clock and to drive the D-PHY CLK lanes respectively. The pll\_clkop\_i goes into a clock divider to produce the output byte clock. The pll\_clkos\_i is 90-degree phase shifted from the pll\_clkop\_i. Both signals run at the desired D-PHY clock frequency.

#### 2.3.4. Internal PLL

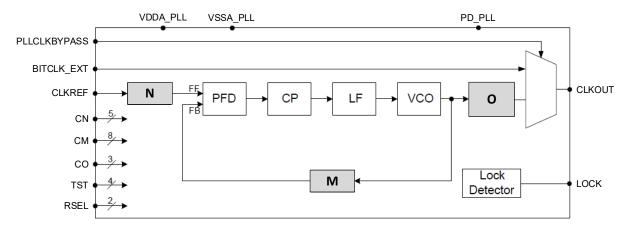

The hard D-PHY of CSI-2/DSI D-PHY Transmitter IP in CrossLink-NX devices contains its own PLL to generate the D-PHY clock lanes and the byte clock. The block diagram of the PLL is shown in Figure 2.9.

Figure 2.9. Internal PLL Block Diagram

The internal PLL multiplies the input frequency by  $(M/(N\times O))$ , where N is the input divider, M is the feedback divider, and O is the output divider. The CLKOUT frequency is twice the D-PHY clock lane frequency.

The valid CLKREF of the D-PHY PLL, connected to the signal ref\_clk\_i, ranges from 24 MHz up to 200 MHz. Program the input divider, N, such that the frequency FF after the input divider is within 24 MHz and 50 MHz. The VCO output, which is also the input to the O divider, must be between 1250 MHz and 2500 MHz.

When PLL Mode is Internal, change the frequency by reconfiguring the LMMI control registers CM, CN, CO, and the protocol timing parameters. See Table 5.1. for details on register offsets and corresponding values.

Compute the data rate using this equation:

$$TX \ line \ rate = \left(\frac{CLKREF}{N}\right) \times \left(\frac{M}{O}\right)$$

To update the data rate without reprogramming the FPGA, follow these steps:

- 1. Set user standby input, usrstdby\_i, to high. Keep it high at all times while registers CM, CN, and CO are written through LMMI write command.

- Perform LMMI write command to the CM, CN, and CO register addresses with the values for the desired PLL frequency. See Table 5.2 and Table 5.3 for the conversion of the control registers CM, CN, and CO to the respective M, N, and O values.

- 3. Perform LMMI write command to protocol timing registers to adjust for the new data rate.

- 4. Set user standby input, usrstdby i, to low.

- 5. Wait for the pll\_lock\_o to assert.

#### 2.4. Packet Formatter Module

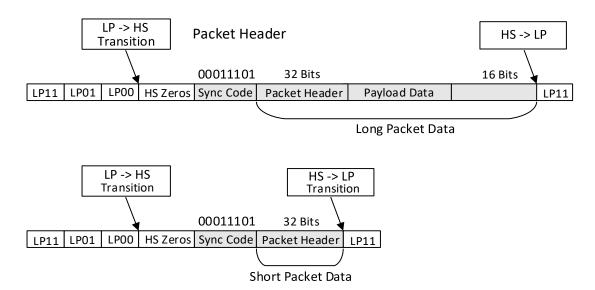

The Packet Formatter Module includes the Packet Header and Packet Footer modules.

The Packet Header module generates the 32-bit header, including the ECC, for the DSI or the CSI-2 packet based on the input information. For CSI-2 configured IP which frame and line number information are not available, there is an internal line and frame counter logic that can be enabled through the IP user interface.

The Packet Footer module appends the CRC checksum at the end of the payload. This module also generates the End-of-Transmit packet (EoTP) for DSI when it is enabled.

## 2.5. Global Operation Module

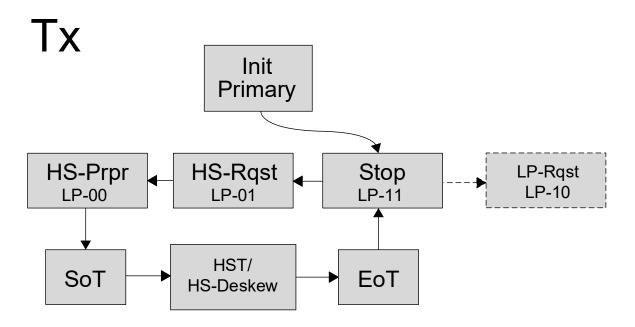

The Global Operation Module contains the finite state machine (FSM) for controlling the HS and LP transitions for high-speed transmission. This module also contains counters for the D-PHY protocol timing requirements. These timing parameters are listed in Table 3.2.

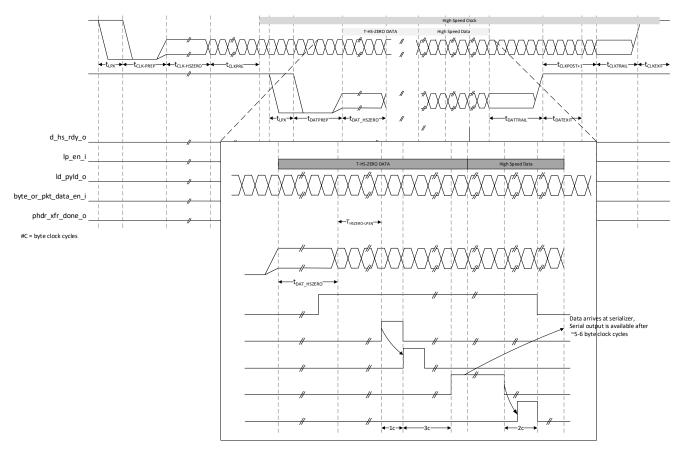

Figure 2.10 shows the LP-to-HS transition flow diagram for data lanes.

Only the sequences from the Stop State to the high-speed state and vice versa are supported; the LP-request, escape mode and turnaround path are not supported.

Figure 2.10. MIPI D-PHY Tx LP to HS Transition Flow Diagram on Data Lanes

During normal operation a data lane is either in control or in high-speed mode.

For sending payload data (the image data), the transmitter drives a particular sequence on data lanes to enter the receiver from the low power mode to high-speed mode.

As part of the initialization of D-PHY, initially all the lanes are held at LP11 state for a specified time. This LP11 state is also known as the Stop State. For sending the image data in high-speed, the transmitter drives the D-PHY lanes a particular LP sequence before the transmitter enters high-speed mode. The high-speed entry sequence (see Figure 2.11) consists of driving LP11->LP01->LP00 (LP->HS transition) on the lanes. On successful reception of this sequence, the high-speed receiver module enables its termination to receive the high-speed differential data.

After LP-to-HS transition, the transmitter sends HS Zeros (V(Dn)>V(Dp)) for a specified amount of time to make sure that the receiver is enabled properly before any payload data is transmitted. Internally, the FSM asserts the d\_hs\_rdy\_o signal to indicate to the requestor that the tHS-ZERO counter threshold has been reached. The data lanes are in HS-00 state until the Global Operation Module receives the packet data from the Packet Formatter Module (or from the external requesting module, if the packet formatter is disabled).

Before the payload data of every HS burst on each lane, the transmitting D-PHY inserts a sync sequence (00011101). This sync sequence is used by the data lanes of the receiving D-PHY to establish synchronization with the high-speed payload data.

After every HS burst, the data lanes go to LP11 state. A single HS burst represents the image data corresponding to one of the horizontal lines of an image and the LP11 state in-between the HS bursts represents the blanking periods.

21

Figure 2.11. High-Speed Entry Sequence and Payload Data Transmission Cycle on Data Lanes

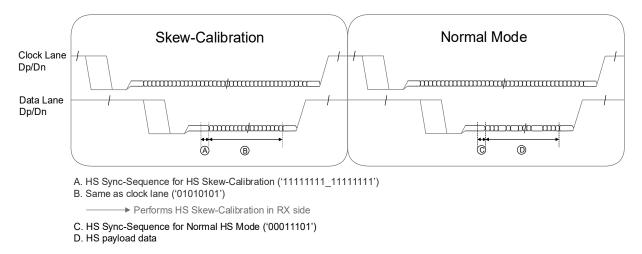

Receiver deskew is initiated by the Hard D-PHY when the data line rate is configured at greater than 1.5 Gbps. The transmitter sends a special deskew burst, as shown in Figure 2.12. When operating above 1.5 Gbps or changing to any rate above 1.5 Gbps, an initial deskew sequence is transmitted before high-speed data transmission in normal operation. Refer to the Initial Skew Calibration for Data Rates Above 1.5 Gbps section for timing details. When operating at or below 1.5 Gbps, the transmission of the initial deskew sequence is optional. Periodic deskew is optional irrespective of data rate.

Figure 2.12. High-Speed Data Transmission in Skew Calibration

## 2.6. Timing Diagrams

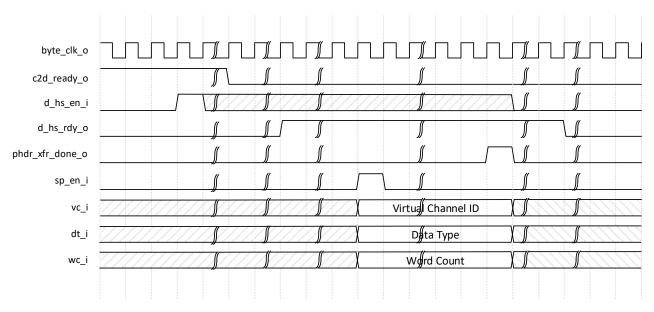

In the configurations without the AXI4-Stream, the requestor waits for the c2d\_ready\_o signal to ensure the CSI-2/DSI D-PHY Transmitter IP is not busy from a previous transmit request, and that the data lanes (and also the clock lane, in the case of non-continuous clock mode) have completed the required tHS-EXIT.

The d\_hs\_rdy\_o signal signifies the clock and data lanes have performed the LP-HS request sequence, including sending out the necessary tHS-ZERO and are in high-speed mode. The requestor can then send out the information of the packet to be transmitted, along with the payload. The c2d\_ready\_o signal goes back to high only after the completion of the tHS-EXIT.

The phdr\_xfr\_done\_o indicates the Packet Header FSM has sent out the packet header and payload, including the CRC, to the Tx Global Operation module.

See the subsections below for more information on the required handshake timing.

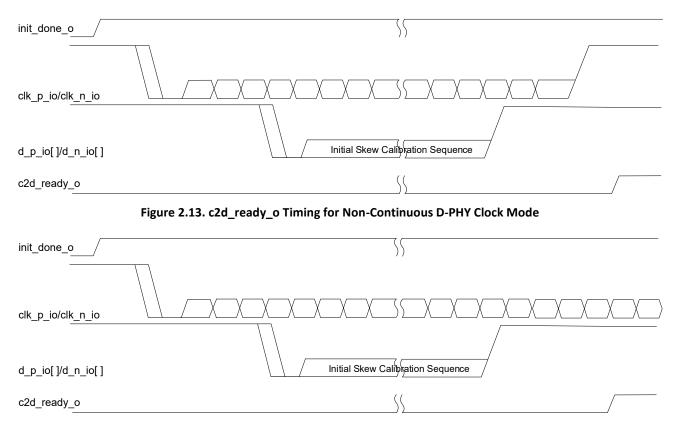

#### 2.6.1. Initial Skew Calibration for Data Rates Above 1.5 Gbps

D-PHY TX IP automatically drives initial skew calibration sequence after Initialization period is done (tinit\_done\_o = 1). c2d\_ready\_o remains de-asserted during initial skew calibration.

For non-continuous clock mode, c2d\_ready\_o goes back to high after the completion of tHS-EXIT for both clock and data lanes.

For continuous clock mode, c2d ready o goes back to high after the data lanes have completed tHS-EXIT.

Figure 2.14. c2d\_ready\_o Timing for Continuous D-PHY Clock Mode

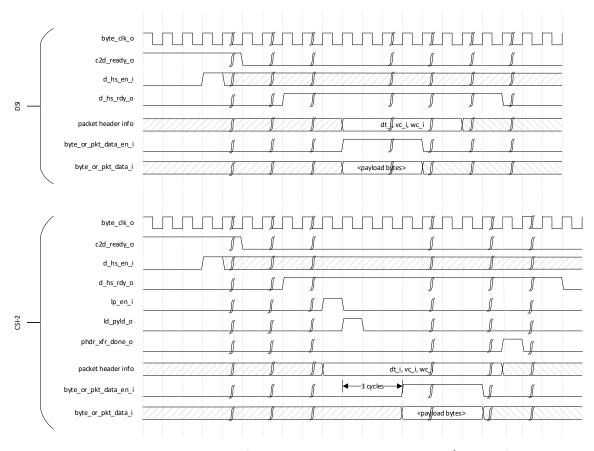

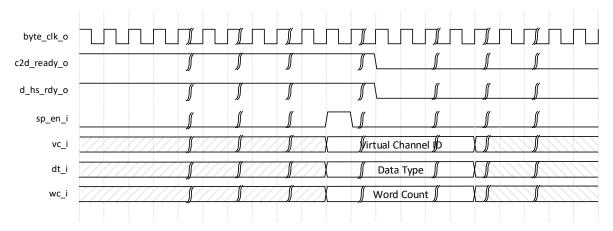

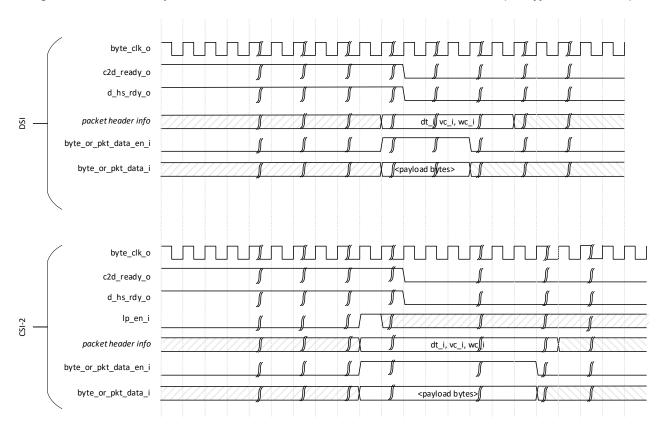

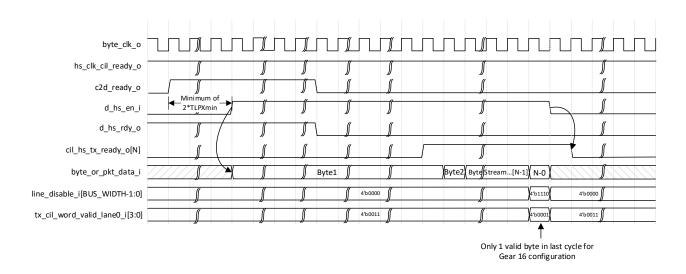

# 2.6.2. Packet Transmission in CSI-2/DSI Interfaces with Packet Formatter for Soft D-PHY and Hard D-PHY with Soft CIL (CIL Bypass is Checked)

When the protocol type selected is CSI-2, there is no internal buffer to save the incoming payload data before the creation of the header packet. The IP requires 3 cycles from the assertion of the ld\_pyld\_o to the arrival of the valid payload data. The ld\_pyld\_o asserts the next cycle after the detection of the lp\_en\_i.

Figure 2.15. D-PHY Tx Input Bus for Short Packet Transmission in CSI-2/DSI Interfaces

Figure 2.16. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2/DSI Interface

# 2.6.3. Packet Transmission in CSI-2/DSI Interface with Packet Formatter for Hard D-PHY with Hardened CIL (CIL Bypass is Unchecked)

Figure 2.17. D-PHY Tx Input Bus for Short Packet Transmission in CSI-2/DSI Interfaces (CIL Bypass Unchecked)

Figure 2.18. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2/DSI Interface (CIL Bypass Unchecked)

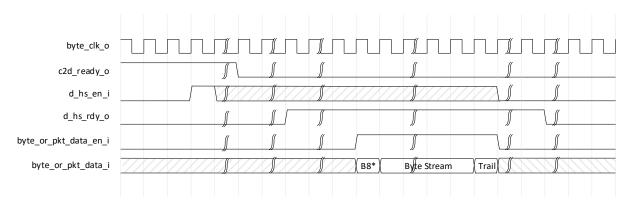

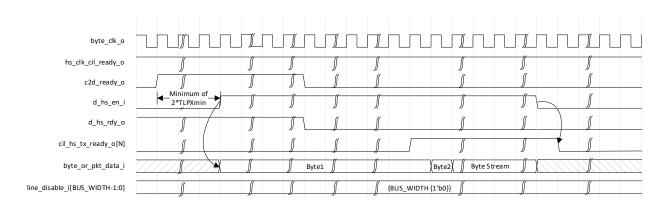

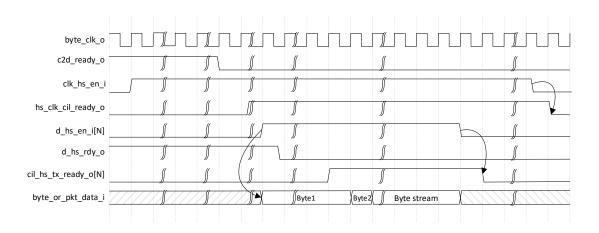

#### 2.6.4. Packet Transmission in CSI-2/DSI Interface without Packet Formatter

The Packet Formatter module appends the sync code before the packet header. If the packet formatter is disabled, the requestor interfaces directly to the Global Operations Control module, therefore the byte\_or\_pkt\_data\_i contains the sync code B8 for each lane. The Global Operations Control module is not aware of the boundary of the actual valid bits, therefore it cannot flip the last valid bit to create the trail. The last word is treated as pure trail bits, and is sent out to the data lanes until the tHS-TRAIL is met. If *CIL Bypass* is unchecked, byte\_or\_pkt\_data\_en\_i is unused and d\_hs\_en\_i serves as data valid of byte\_or\_pkt\_data\_i. Sync code B8 and trail bytes are also not needed in the input stream.

Figure 2.19. D-PHY Tx Input Bus for LP Transmission in CSI-2/DSI Interface without Packet Formatter (*D-PHY TX IP = Soft D-PHY* or *CIL Bypass* Checked)

Figure 2.20. D-PHY Tx Input Bus for Transmission without Packet Formatter (CIL Bypass Unchecked)

For CIL Bypass == unchecked and Bypass Packet Formatter == checked, d\_hs\_en\_i must be asserted only when hs\_clk\_cil\_ready\_o signal is high.

If the number of valid bytes in the last cycle of byte\_or\_pkt\_data\_i does not align with the number of active D-PHY lanes, the corresponding tx\_cil\_word\_valid\_lane#\_i and line\_disable\_i of the inactive lanes must be set accordingly. See the following figure for example.

Figure 2.21. Example Configuration of Number of TX Lanes == 4, TX Gear == 16 with Unaligned Number of Bytes

#### 2.6.5. Non-Continuous D-PHY Clock Mode

clk\_hs\_en\_i triggers the IP to start HS entry sequence on the clock lane. When *D-PHY TX IP = Soft D-PHY* or *CIL Bypass* is checked, this is an active high pulse going to the Tx Global Operation and can be toggled together with d\_hs\_en\_i. When *CIL Bypass* is unchecked and *Bypass Packet Formatter* is checked, this signal must be asserted in the entire duration that clock is expected to be active.

Figure 2.22. D-PHY Tx Input Bus for Non-Continuous Clock Mode with CIL Bypass Unchecked (without Packet Formatter)

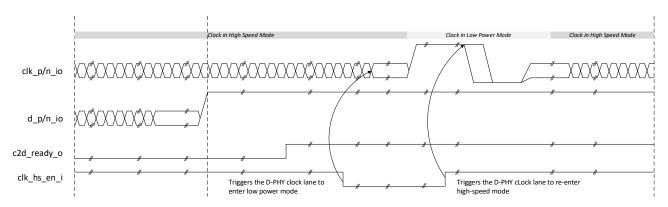

#### 2.6.6. Manual Control of D-PHY Clock Lane to LP

When Enable Manual Control of D-PHY Clock is checked, the clk\_hs\_en\_i port can be used to manually control the D-PHY clock lane to enter low power mode if CIL Bypass and Bypass Packet Formatter are both unchecked, or if D-PHY Clock Mode == Continuous. Setting clk\_hs\_en\_i to LOW triggers the D-PHY clock lane to enter the trail sequence and eventually LP mode (LP-11). Because of the internal processing within the IP, it may take up to 250 ns before the clock lane enters the trail sequence. Setting clk\_hs\_en\_i to HIGH again triggers the D-PHY clock lane to re-enter the HS sequence. Before manually putting the D-PHY clock lane into LP mode, ensure there are no ongoing transactions and that the data lanes are in the IDLE state (indicated by c2d\_ready\_o == HIGH). Additionally, allow sufficient time for the D-PHY clock lane to fully transition to LP mode before reasserting clk\_hs\_en\_i. Failure to do so may result in unpredictable IP behavior.

Figure 2.23. D-PHY Clock Lane Going to LP Mode Using the clk\_hs\_en\_i Port

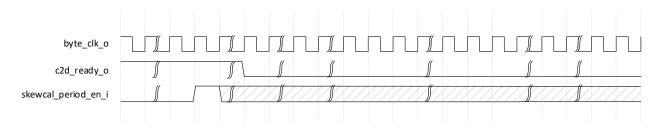

#### 2.6.7. Enable Periodic Skew Calibration

A low-to-high transition of skewcal\_period\_en\_i initiates the periodic skew calibration. The signal, skewcal\_period\_en\_i, is only available when the *Enable Periodic Skew Calibration* attribute is enabled. c2d\_ready\_o is high before initiating periodic skew calibration.

Figure 2.24. D-PHY Tx Input Bus to Enable Periodic Skew Calibration

#### 2.6.8. CIL-Enabled Debug Ports

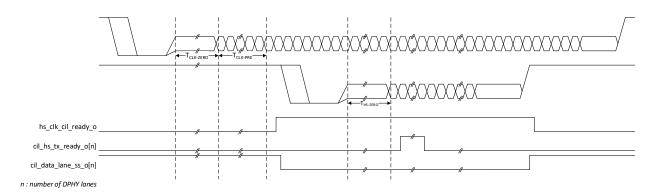

Figure 2.25. CIL-Enabled Debug Ports

### 2.6.9. Timing Configuration Registers

Figure 2.26. Timing Configuration Registers for Soft D-PHY or Hardened CIL Bypassed

#### 2.6.10. Byte Data Arrangement

When in gear 16, the CSI-2/DSI D-PHY Transmitter IP has an option to take the parallel data arranged in sequential byte order, or in lane interleaved arrangement. This is configurable through the *Interleaved Input Data* attribute in the user interface, as shown in the following table. For gear 8, payload is always sequential.

Table 2.3. Interleaved versus Sequential Byte Data Input

| had a all data t   | 4-Lane      |            | 3-Lane      |            | 2-Lane      |            | 1-Lane      |            |

|--------------------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|

| byte_or_pkt_data_i | Interleaved | Sequential | Interleaved | Sequential | Interleaved | Sequential | Interleaved | Sequential |

| [7:0]              | Byte 0      | Byte 0     |

| [15:8]             | Byte 4      | Byte 1     | Byte 3      | Byte 1     | Byte 2      | Byte 1     | Byte 1      | Byte 1     |

| [23:16]            | Byte 1      | Byte 2     | Byte 1      | Byte 2     | Byte 1      | Byte 2     | _           | _          |

| [31:24]            | Byte 5      | Byte 3     | Byte4       | Byte 3     | Byte 3      | Byte 3     | _           | _          |

| [39:32]            | Byte 2      | Byte 4     | Byte 2      | Byte 4     | _           | _          | _           | _          |

| [47:40]            | Byte 6      | Byte 5     | Byte 5      | Byte 5     | _           | _          | _           | _          |

| [55:48]            | Byte 3      | Byte 6     | _           | -          | _           | _          | _           | _          |

| [63:56]            | Byte 7      | Byte 7     | _           | _          | _           | _          | _           | _          |

Per lane distribution follows the ordinal number, depending on the number of active lanes. For example, in a 4-lane configuration with interleaved input data checked, Byte 0 to Byte 3 are distributed to Lane 0 to Lane 3 respectively. For gear 16 mode, the lane wraps around and Byte 4 to 7 are distributed to Lane 0 to Lane 3 respectively.

## 2.7. Dynamic Reconfiguration

Starting from IP v2.3.0, the IP can be reconfigured during run time to support dynamic lane and rate reconfiguration for the modes in the table below.

Table 2.4. D-PHY Tx Settings that Support Dynamic Reconfiguration

| IP Version <sup>1</sup> | Family | D-PHY TX IP | CIL Bypass | Bypass Packet Formatter |

|-------------------------|--------|-------------|------------|-------------------------|

| IP v2.3.0               | Nexus  | Soft D-PHY  | _          | Checked                 |

| IP v2.4.0               | Nexus  | Soft D-PHY  | _          | Unchecked               |

| IP V2.4.0               | Avant  | Soft D-PHY  | _          | Unchecked, Checked      |

#### Note:

1. All features available in previous versions of the IP remain fully supported in newer versions unless otherwise specified in the IP Release Notes. Each row highlights only the additional dynamic reconfiguration features introduced in each release.

To enable these functions, configure the IP based on the supported IP attributes in Table 2.4. Check the additional IP attributes in the Module/IP Blocks Wizard in the Lattice Radiant software as follows:

- Enable LMMI Interface is checked. This is required as registers are accessible only through LMMI.

- Set the parameter *Number of TX Lanes* and *Target TX Line Rate* to the maximum desired value at compile time to enable dynamic reconfiguration of all possible combinations.

**Note:** When the selected IP configuration at compile time is above 1.5 Gbps, the initial deskew calibration sequence is automatically transmitted even if the data rate is later dynamically reconfigured to 1.5 Gbps or below.

To reconfigure the dynamic registers, follow these steps:

- 1. Stop the upstream source from sending packets to the D-PHY IP.

- Configure the D-PHY receiver.

- 3. Configure the IP registers.

- For Soft D-PHY:

- Write to register 0x0A[2:1] to change the number of active lanes.

- If you plan to change the data rate, update the timing parameters registers (0x1F to 0x31) to adjust the protocol timing parameters accordingly. For detailed information, refer to Table 5.4.

- 4. Configure the upstream source to the new settings.

- If you also plan to change the data rate, you must reconfigure the PLL such that the output clocks that are driving the pll\_clkop\_i and pll\_clkos\_i pins match the new data rate.

- Modify the byte data drivers to re-order the bytes accordingly to match the new lane configuration.

- 5. Assert all the resets and clock control ports of the IP (whichever are available in the selected configuration) except the LMMI reset:

- reset\_n\_i

- pd\_dphy\_i

- pll lock i

- 6. Trigger the upstream source to send normal transactions based on the new configuration. Ensure that the D-PHY receiver is already out of reset and operating in active mode before valid packet transmission starts. This precaution helps prevent any packet loss.

## 3. IP Parameter Description

The configurable attributes of the D-PHY Tx IP are shown in the following tables. You can configure the IP by setting the attributes accordingly in the IP Catalog Module/IP Block Wizard of the Lattice Radiant software.

Wherever applicable, default values are in bold.

#### 3.1. General

**Table 3.1. General Attributes**

| Attribute                                               | Selectable Values         | Description                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General Settings                                        |                           |                                                                                                                                                                                                                                                                                                                                                   |  |

| Transmitter                                             |                           |                                                                                                                                                                                                                                                                                                                                                   |  |

| TX Interface Type                                       | DSI, CSI-2                | D-PHY Tx interface type.                                                                                                                                                                                                                                                                                                                          |  |

| D-PHY TX IP                                             | Hard D-PHY,               | Implementation of the PHY layer of the D-PHY Tx.                                                                                                                                                                                                                                                                                                  |  |

|                                                         | Soft D-PHY                | For Avant, Certus-NX, and CertusPro-NX devices, only <i>Soft D-PHY</i> is available.                                                                                                                                                                                                                                                              |  |

| Number of TX Lanes                                      | 1, 2, 3, 4                | Number of active D-PHY Tx data lanes. The 3-lane configuration is available only when <i>Bypass Packet Formatter</i> is checked.                                                                                                                                                                                                                  |  |

| TX Gear                                                 | 8, 16                     | Gearing ratio between the ports in fabric and the high-speed I/O.  TX Gear = 16 is available only on D-PHY TX IP = Hard D-PHY and wher selected, it is recommended to operate the IP at data rates of 1000 Mbps or higher to ensure optimal performance.                                                                                          |  |

| Interleaved Input Data                                  | checked, unchecked        | When this option is checked, the input parallel data is already interleaved across the lanes. See Table 2.3. Available only when TX Gear = 16.                                                                                                                                                                                                    |  |

| CIL Bypass                                              | checked, unchecked        | When using <i>D-PHY TX IP</i> = <i>Hard D-PHY</i> , this option bypasses the bin Control Interface Logic of the Hard D-PHY. CIL is the hardened block that controls the clock and data lane state transitions. If the is bypassed, soft logic is used.  When using <i>D-PHY TX IP</i> = <i>Soft D-PHY</i> , this option is automatically checked. |  |

| Bypass Packet Formatter                                 | checked, <b>unchecked</b> | Bypasses the Packet Formatter module. The data input to the IP is in packet format and the bytes are interleaved across the active data lanes.                                                                                                                                                                                                    |  |

| Enable LMMI Interface                                   | checked, unchecked        | Enables the LMMI bus used for accessing IP registers.  When <i>D-PHY TX IP = Hard D-PHY</i> , the Immi_clk_i signal is limited to a maximum operating frequency of 60 MHz.                                                                                                                                                                        |  |

| Enable AXI4-Stream<br>Interface <sup>2</sup>            | checked, unchecked        | Enables the AXI4-Stream bus.                                                                                                                                                                                                                                                                                                                      |  |

| Enable Periodic Skew<br>Calibration                     | checked, unchecked        | When this option is checked, there is an option to perform periodic skew calibration through the skewcal_period_en_i port. This option is available only when <i>D-PHY TX IP = Hard D-PHY</i> .                                                                                                                                                   |  |

| Protocol                                                | ·                         |                                                                                                                                                                                                                                                                                                                                                   |  |

| Enable Frame Number<br>Increment in Packet<br>Formatter | checked, unchecked        | Enables the Frame Number Increment in the Packet Formatter. Editable only if <i>Bypass Packet Formatter</i> is unchecked. When unchecked, information is derived from the wc_i input port.                                                                                                                                                        |  |

| Maximum Frame Number<br>Value in Packet Formatter       | <b>2</b> –255             | Maximum frame number used in packet formatter.  This option is editable only if <i>Enable Frame Number Increment in Packet Formatter</i> is checked.                                                                                                                                                                                              |  |

| Enable Line Number<br>Increment in Packet<br>Formatter  | checked, unchecked        | Enables the line number increment feature for the Packet Formatter. This option is editable only if <i>Bypass Packet Formatter</i> is unchecked. When unchecked, information is derived from the wc_i input port.                                                                                                                                 |  |

| Attribute                                     | Selectable Values                | Description                                                                                                                                                                                                                    |  |  |

|-----------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Extended Virtual Channel ID                   | checked, unchecked               | Enables 4-bit instead of 2-bit Virtual Channel ID in CSI-2.                                                                                                                                                                    |  |  |

| EoTp Enable                                   | checked, <b>unchecked</b>        | When checked, the IP appends an end-of-transmit packet at the end of a high-speed transmission.  This option is enabled only if TX Interface = DSI and Bypass Packet                                                           |  |  |

|                                               |                                  | Formatter is unchecked.                                                                                                                                                                                                        |  |  |

| Clock                                         |                                  |                                                                                                                                                                                                                                |  |  |

| Target TX Line Rate (Mbps                     | 320–2500, <b>800</b>             | Maximum bandwidth per lane for TX Gear = 16.                                                                                                                                                                                   |  |  |

| per Lane) <sup>1</sup>                        | 160–1500 or 160–1800, <b>800</b> | Maximum bandwidth per lane for TX Gear = 8.                                                                                                                                                                                    |  |  |

|                                               |                                  | Maximum line rate is 1800 Mbps for Avant devices and 1500 Mbps for other devices.                                                                                                                                              |  |  |

| Target TX Data Rate (Mbps)                    | 160–10000, <b>3200</b>           | Target total bandwidth of the D-PHY TX channel. The value is Target TX Line Rate (Mbps per Lane) x Number of TX Lanes. Not editable. For information only.                                                                     |  |  |

| Target D-PHY Clock                            | 80–1250, <b>400</b>              | Target frequency of the D-PHY clock lane.                                                                                                                                                                                      |  |  |

| Frequency (MHz)                               |                                  | The value is Target TX Line Rate (Mbps per Lane) / 2.                                                                                                                                                                          |  |  |

|                                               |                                  | Not editable. For information only.                                                                                                                                                                                            |  |  |

| Target Byte Clock Frequency (MHz)             | 10–225, <b>100</b>               | Target operating frequency of the internal clock byte_clock_o. The value is <i>Target TX Line Rate (Mbps per Lane) / TX Gear</i> . Not editable. For information only.                                                         |  |  |

| D-PHY Clock Mode                              | Continuous,                      | Determines the clock mode of the PHY layer.                                                                                                                                                                                    |  |  |

|                                               | Non-continuous                   | Continuous – If the clock lane is always in high-speed mode.                                                                                                                                                                   |  |  |

|                                               |                                  | Non-continuous – The clock lane goes to low power mode in between high-speed transactions.                                                                                                                                     |  |  |

| Enable Manual Control of D-<br>PHY Clock      | checked, <b>unchecked</b>        | Enables manual control of D-PHY clock via clk_hs_en_i port. This useful when you want to manually stop the DPHY clock lane and enter LP mode.  Available only when either condition is valid:  • D-PHY Clock Mode – Continuous |  |  |

| D-PHY PLL Mode                                | Internal, External               | <ul> <li>CIL Bypass and Bypass Packet Formatter are both unchecked</li> <li>Enables or disables the internal PLL when TX Interface = Hard D-PI</li> <li>For Soft D-PHY, only external PLL sources are supported.</li> </ul>    |  |  |

| Enable Edge Clock<br>Synchronizer and Divider | checked, unchecked               | Enables or disables the Edge Clock Synchronizer and Divider block when <i>D-PHY TX IP = Soft D-PHY</i> .                                                                                                                       |  |  |

| Reference Clock Frequency<br>(MHz)            | 24–200, <b>100</b>               | Operating frequency of the components interfaced with the fabric                                                                                                                                                               |  |  |

| Actual D-PHY TX Data Rate<br>(Mbps)           | 160–10000, <b>4000</b>           | Actual D-PHY TX data rate based on the PLL settings and Reference Clock Frequency.  Not editable. For information only. Available only when <i>D-PHY PLL Mode</i> == Internal.                                                 |  |  |

| Actual TX Line Rate (Mbps)                    | 160–2500, <b>1000</b>            | Actual data rate per lane based on the PLL settings and Reference Clock Frequency.  Not editable. For information only. Available only when <i>D-PHY PLL Mode</i> == Internal.                                                 |  |  |

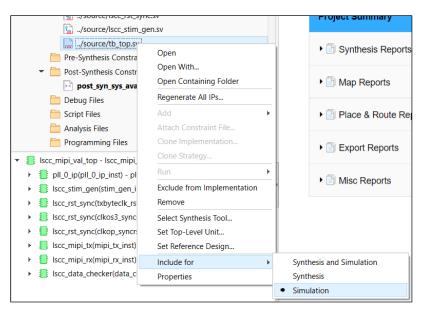

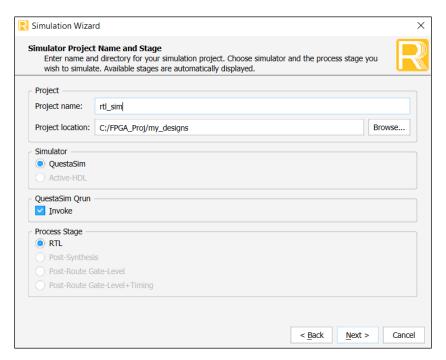

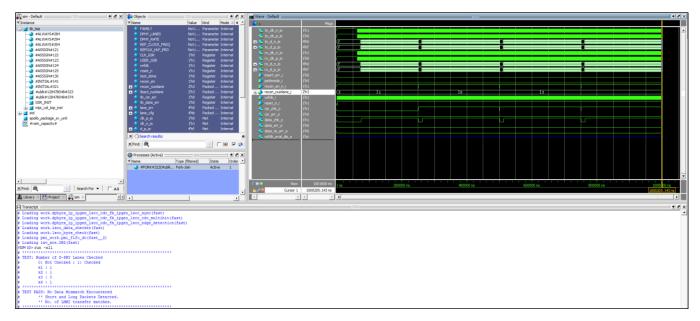

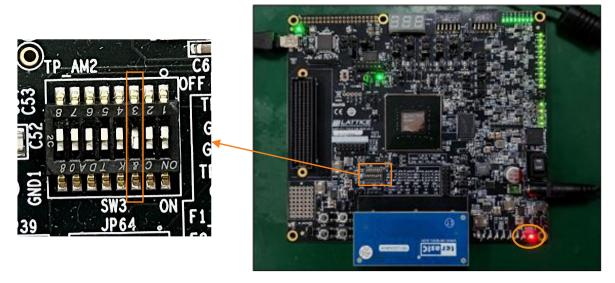

| Actual D-PHY Clock<br>Frequency (MHz)         | 80–1250, <b>500</b>              | Actual D-PHY TX clock frequency based on the PLL settings and Reference Clock Frequency.  Not editable. For information only. Available only when <i>D-PHY PLL Mode</i> == Internal.                                           |  |  |