# Lattice Diamond Platform Designer User Guide

#### Copyright

Copyright © 2015 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

## **Type Conventions Used in This Document**

| Convention | Meaning or Use                                                                                    |

|------------|---------------------------------------------------------------------------------------------------|

| Bold       | Items in the user interface that you select or click. Text that you type into the user interface. |

|            | Variables in commands, code syntax, and path names.                                               |

| Ctrl+L     | Press the two keys at the same time.                                                              |

| Courier    | Code examples. Messages, reports, and prompts from the software.                                  |

|            | Omitted material in a line of code.                                                               |

|            | Omitted lines in code and report examples.                                                        |

| [ ]        | Optional items in syntax descriptions. In bus specifications, the brackets are required.          |

| ( )        | Grouped items in syntax descriptions.                                                             |

| { }        | Repeatable items in syntax descriptions.                                                          |

|            | A choice between items in syntax descriptions.                                                    |

## **Contents**

| Designing with Lattice Diamond Platform Designer 1                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| About Platform Designer 3 Platform Designer User Interface 3 Platform Designer Input Files 5 Platform Designer Output Files 6                                                                                                                       |

| Platform Designer Flow 6                                                                                                                                                                                                                            |

| Launching Platform Designer 7 Creating a New Platform Designer Project 8 Opening an Existing Platform Designer Project 9                                                                                                                            |

| Working with Platform Designer Project (.ptm) Files 10                                                                                                                                                                                              |

| Working with Platform Designer Editors 11                                                                                                                                                                                                           |

| Setting Global Options 14 Setting ASC Options 14 Setting Device Options 15 Configuring a SPI Flash Model 16                                                                                                                                         |

| Configuring Voltage Sense (VMON) and Control (TRIM) Setting Multiple VMON/Trim Properties 18 Setting VMON Properties 19 Setting Trim and Margin Properties 20 Defining DC-DC Converter Models 21 Configuring Voltage Identification (VID) Tables 23 |

| Configuring Current Sense (IMON) 24                                                                                                                                                                                                                 |

| Configuring Temperature Sense (TMON) 25                                                                                                                                                                                                             |

| Configuring Fan Control 26                                                                                                                                                                                                                          |

| Setting Fault Logging Options 27                                                                                                                                                                                                                    |

| Configuring Hot Swap 28                                                                                                                                                                                                                             |

| Configuring PMBus Adapter 32                                                                                                                                                                                                                        |

| Implementing the Platform Management Algorithm 33 Configuring and Viewing Ports and Nodes 33 Designing with the Logic Editor 36                                                                                                                     |

Sequence Controller Instruction Set 38 Designing Control Sequences 39 Entering Supervisory Equations 45 Copying and Pasting Sequences and Equations 46 Importing HDL Modules 47 Building the Design 47 Checking Design Rules 48 Examining Resource Utilization 48 Compiling the Design 48 Assigning Pins 49 Generating the JEDEC 49 Exporting a Detailed Configuration Report 49 Simulating the Design **50** Generating a Stimulus and Test Bench File 50 Simulating the Design 51 Working with Power Calculator 53

Index 55

# Designing with Lattice Diamond Platform Designer

Included with the Lattice Diamond software is the Platform Designer tool which enables you to build and control a complete hardware management system using the Platform Manager 2, or a MachXO2 with external Analog Sense and Control (ASC) devices.

Digital I/O Voltage Sense Voltage Rail Drive Output FPGA I/O Control Block Current ADC Voltage/ **Current Sense** ASC LUT-Based Interface FPGA Fabric (ASCI) Temperature Non-SPI Diode Volatile 12C Fault Log JTAG DC/DC Trim/ Trim & Margin Feedback Control **ANALOG SENSE & FPGA SECTION CONTROL SECTION**

Figure 1: Platform Manager 2 Block Diagram

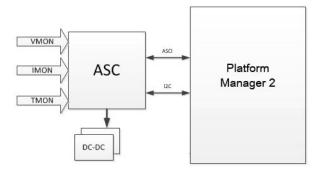

As shown in the previous figure, the Platform Manager 2 device is made up of an ASC block and an FPGA block. These two blocks provide the necessary programmable building blocks to enable integration of various combinations of hardware management functions into a single chip. The hardware management algorithm is implemented within the FPGA block of the Platform Manager 2. The monitoring and control resources can be scaled up, to meet application requirements, by adding an external ASC to the Platform Manager 2. Each of the ASCs provides additional monitor and control of up to ten voltage rails, two temperature sensors and two current sensors. The overall platform management algorithm that uses the inputs from the external ASC device(s) is located within the FPGA block of the Platform Manager 2. The following diagram shows how an ASC device can be connected to a Platform Manager 2 device to implement a hardware management circuit that monitors the board voltage rails (V), supply currents (I), and board temperatures (T).

Figure 2: ASC Device Connected to a Platform Manager 2 Device

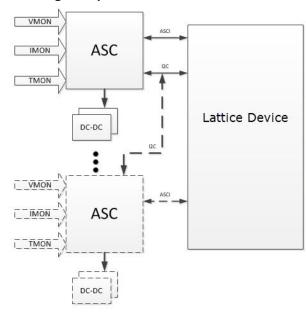

Multiple ASC devices (up to 8) can also be connected to a MachXO2 HC device (640 LUT or larger), similar to the Platform Manager 2, to offer wider flexibility and control when implementing a complete hardware management system.

Figure 3: Connecting Multiple ASCs to Lattice Device

See Also ▶ "Platform Designer User Interface" on page 3

"Platform Designer Flow" on page 6

## **About Platform Designer**

Platform Designer provides an integrated design environment that enables you to configure the device, implement the hardware management algorithm, simulate, assign pins, and finally generate the JEDEC files required to program and configure the device on the circuit board. It also allows you to import other HDL files to integrate other desired functions.

See Also ▶ "Launching Platform Designer" on page 7

- "Platform Designer User Interface" on page 3

- "Platform Designer Flow" on page 6

## **Platform Designer User Interface**

Platform Designer contains separate editors for configuring global settings; current, temperature, and voltage monitors; fan controller and fault logger components; ports, nodes, and logic controls. It also provides a view for checking design rules and resources and building the design. Each editor and view is accessed from the Platform Designer menu pane on the left, which is divided into five main sections: Global, Analog, Components, Control, and Build.

**Global** The Global Configuration view provides global configuration options, including options for each ASC device. The global ASC Options provide

access to configuration settings like the I<sup>2</sup>C address and other default settings. The Device Options enable you to select the programming interface, clock source, and boot mode.

**Components** The Components section enables you to configure the fan, fault logging, hot swap, and PMBus Adapter. It includes the following views:

- ► Fan Controller The Fan Controller allows you to add a fan, specify the fan interconnections, and configure the control parameters. The fan controller can be configured to work with 2-wire, 3-wire, or 4-wire fans, and up to sixteen fans can be controlled. The fan controller generates a pulse width modulated (PWM) signal to set fan speeds.

- Fault Logger The Fault Logger enables you to specify and configure fault conditions that are logged to non-volatile memory. You have the option of using standard fault logging that is based on voltage, current, and temperature status; or using the full-featured fault logging.

- Hot Swap The Hot Swap component enables you to configure the ASC for a hysteretic closed-loop to limit the in-rush current in an application where power is rapidly applied. Such an application can include such a line card, blade, or a PCB that is plugged into a "hot" backplane.

- PMBus Adapter The PMBus Adapter component allows you to configure the adapter for connecting analog Point of Load (POL) DC-DC converters to PMBus using the ASC and FPGA.

**Analog** The Analog section enables you to configure the settings for current, temperature, and voltage monitors. It includes the following editors:

- Current The Current editor enables you to configure the low-voltage and high-voltage current monitors for each ASC device. Platform Designer automatically populates the current trip points available based on the sense resistor selection. You can configure the trip points and other current monitor settings here.

- ► Temperature The Temperature editor enables you to configure the temperature monitors (TMON) for each ASC device. Multiple monitor levels can be selected for each TMON, with temperature values displayed in °C.

- Voltage The Voltage editor allows you to configure voltage monitoring, trimming, margining, and voltage identification (VID) settings for each ASC device in your system. You can edit multiple settings by using the Voltage Monitor & Control dialog box. To open the dialog box, double-click an active cell in the ASC column or the Pins Monitor/Trim column on any of the three spreadsheets, or right-click the cell and choose Edit. You can also edit settings individually on the Voltage spreadsheet or the VID spreadsheet by single-clicking an editable cell.

**Control** The Control section enables you to configure signals and set the control logic. It includes the following editors:

Ports & Nodes – The Ports & Nodes editor provides spreadsheets for viewing the internal nodes and configuring external signals (ports) of the chip set. The Ports sheet shows all physical FPGA-based PIOs that are available for use as external connections to the design and allows you to assign labels to logical ports, specify the I/O and register type, and group ports of a common type to form a bus. The Nodes sheet shows internal signals already generated to connect the implemented features of the design. The nodes sheet allows you to create additional signals for connecting different features on-chip. The GPIO sheet allows you to configure and label the ASC-based general purpose I/Os. The HV Outputs sheet allows you to label and configure the high-voltage output ports.

Logic – The Logic editor enables you to create sequences, exception logic, supervisory equations, and timers for one or more state machines. It also allows you to import modules into your design from HDL code. The Sequence page of the Logic editor allows you to add state machines and gives you access to the Multiple State Machines dialog box for managing the state machine library.

**Build** The Build view enables you to check the design status, examine the amount of hardware resources consumed, run DRC check, compile the design, and generate the merged JEDEC file. The Build view includes a summary table of enabled components and programming options, and it shows the amount of hardware resources of the device that have been consumed by the current design configuration. The Build view enables you to generate a test bench, including stimulus, for simulating your design. It also allows you to export a detailed configuration report.

See Also ▶ "Working with Platform Designer Editors" on page 11

## **Platform Designer Input Files**

The input files for Platform Designer include the Platform Designer project file (.ptm) and HDL source files (.v, .vhd).

The .ptm file holds all of the Analog Sense and Control settings, as well as the logic and port information, for the active Platform Designer project. A .ptm file is generated automatically for a new project. You can also add a new or existing .ptm file, which allows you to choose from multiple project files in a single implementation.

HDL source files are not required, but you can add them to the Diamond project. Once the HDL files are added to the Diamond project, you can use Platform Designer's Logic Editor to import an HDL module into the Platform Designer project.

See Also ► See "Working with Platform Designer Project (.ptm) Files" on page 10

- "Importing HDL Modules" on page 47.

- "Creating a New Platform Designer Project" on page 8

## **Platform Designer Output Files**

Platform Designer automatically generates the background HDL files when you compile the design. The "Generate Jedec" process produces a merged JEDEC of the FPGA and ASC JEDEC files for programming.

See Also ▶ "Building the Design" on page 47

## **Platform Designer Flow**

The number of tasks involved in the Platform Designer flow will vary, depending on the selected Platform Manager 2, or MachXO2, the number of external ASC devices selected, and the types of configuration needed to complete the design. The following outline shows a typical flow of required and optional tasks.

- 1. Create a project in Lattice Diamond. Select the base device and package; Platform Manager 2, or MachXO2 HC. Then add the number of external ASC devices needed.

- 2. Specify global settings:

- ASC options, including reset type, and default options for voltage, current, and temperature

- b device options, including programming interface, clock source, and boot mode

- 3. Configure the ports and nodes:

- ports and port groups

- internal nodes

- general-purpose I/Os

- high-voltage outputs

- 4. Configure the analog settings:

- Configure the voltage monitors (VMONs):

- schematic net names and parameters

- trim/margin parameters

- voltage identification (VID) tables

- Configure the current monitors (IMONs).

- Configure the temperature monitors (TMONs).

- Configure one or more fans:

- fan type and pulse width modulation

- fan interconnections

- Configure PMBus Adapter.

- Enable and configure fault logging.

- 5. Define the platform management logic, including sequencing and monitoring:

- timers

- sequencer instructions and exceptions for one or more state machines

- supervisory logic equations

- modules that are imported from HDL

- 6. Build the design.

- Examine the resources consumed.

- Run design rule check.

- Compile the design to generate the HDL code and synthesize the logic.

- Assign Pins in Spreadsheet View.

- Generate the JEDEC to process the design and generate the merged JEDEC file.

- 7. Simulate the design.

See Also Platform Designer User Interface" on page 3

- "Creating a New Platform Designer Project" on page 8

- "Working with Platform Designer Project (.ptm) Files" on page 10

## **Launching Platform Designer**

You can launch Platform Designer by creating a new project in Diamond that targets a Platform Manager 2, or a MachXO2 HC (640 LUT or larger) with external ASCs. You can also launch Platform Designer by opening an existing Platform Designer project file (.ptm).

Platform Designer is also available from the Diamond Tools menu when you open an existing project that targets a Platform Manager 2, or a MachXO2 with external ASCs

See Also ▶ "Creating a New Platform Designer Project" on page 8

- "Opening an Existing Platform Designer Project" on page 9

- "Working with Platform Designer Project (.ptm) Files" on page 10

- "Working with Platform Designer Editors" on page 11

# Creating a New Platform Designer Project

When you create a new project that targets the Platform Manager 2, or a MachXO2 HC (640 LUT or larger) with external ASCs, Diamond generates a new Platform Designer project file (.ptm) and opens the Platform Designer user interface.

#### To create a new Platform Designer project in Diamond:

- In Diamond, choose File > New Project to open the Create a Lattice Diamond Project wizard.

- Click Next.

- 3. In the Project section, type a name for the project and use the Browse button to navigate to a location.

- 4. Click Next.

- The Add Source section is an optional step that allows you to add HDL source files to the project or an existing Platform Designer project (.ptm) file. If you add an existing .ptm file, the default .ptm file will not be added to the project.

To skip the Add Source step, click **Next**.

To add source files to the project, click the **Add Source** button to navigate to the files and select them, and then click **Next**.

- 6. In the Select Device dialog box, do one of the following:

- Select Platform Manager 2 in the Family section, and then select the desired LPTM device from the Device section.

- Platform Manager 2 devices contain one embedded Analog Sense and Control (ASC) device. The LPTM21 device allows you to add up to three external ASC devices. The LPTM20 device allows you to add one external ASC device. To add an external ASC device, select LPTM21. The "Select ASC Device" section will then appear near the bottom of the dialog box.

- Select MachXO2 in the Family section, and then select the desired LCMXO2 HC device—640HC or larger—from the Device section.

- The "Select ASC Device" section appears near the bottom of the dialog box. Up to eight ASC devices can be added, depending upon the size of MachXO2 device.

- In the "Select ASC Device" section, select the number of ASC devices you would like to include.

The package type, performance grade, operating conditions, and part name are all tied to the device selection.

8. Click Next.

In the Select Synthesis Tool dialog box, select the synthesis tool that you want to use. The choices are **Lattice LSE** and **Synplify Pro** and can be changed at any time.

#### 9. Click Next.

In the Project Information dialog box, the option "Create Platform Designer file" is selected by default. This will create a .ptm file using the project name shown in the File name box and cause Platform Designer to open. If desired, you can assign a different name for the .ptm file and select a different directory location.

#### Note

If you added an existing .ptm file to the project in Step 4, the "Create Platform Designer file" option will not be available.

#### 10. Click Finish.

Platform Designer opens within Diamond and loads the .ptm file.

See Also ▶ "Opening an Existing Platform Designer Project" on page 9

"Working with Platform Designer Project (.ptm) Files" on page 10

## Opening an Existing Platform Designer Project

After you have created a project in Diamond that targets a Platform Manager 2, or a MachXO2 HC (640 LUT or larger) with external ASCs, you can open the Platform Designer project file (.ptm) for the active implementation.

#### To open an existing Platform Designer project in Diamond:

1. In Diamond, choose **File > Open > Project**, and navigate to the Lattice Diamond file (.ldf) for the Platform Designer project.

Diamond loads the file and shows the .ptm file in the File List view.

- 2. Do one of the following:

- Click the Platform Designer button on the toolbar or from the Tools menu.

Platform Designer opens and loads the active .ptm file

In the File List view, expand the Input Files folder and double-click the .ptm file that you want to open.

Platform Designer opens and loads the .ptm file.

See Also ▶ "Working with Platform Designer Project (.ptm) Files" on page 10

## Working with Platform Designer Project (.ptm) Files

The Platform Designer project file (.ptm) holds all of the Analog Sense and Control settings, as well as the logic and port information, for the active implementation. When you create a new Platform Designer project, the .ptm file is generated automatically by Diamond. You can also add a new or existing .ptm file to your project. The project's .ptm files are maintained in the Platform Design Files folder in the File List view for the active implementation, and the active .ptm file in this folder is displayed in bold. Only one .ptm file can be active for an implementation.

#### To add a new .ptm file to a Platform Designer project:

- 1. In the File List view of Diamond, right-click the name of the active implementation, and choose **Add > New File**.

- 2. In the dialog box, select **Source Files** from the Category list, and then select **Platform Designer File**.

- 3. Type a name for the new .ptm file. If desired, select a different location for the file by clicking the Browse button.

- 4. Click New.

Diamond loads the new .ptm file and sets it as the active Platform Designer file for the current implementation.

#### To add an existing .ptm file to a Platform Designer project:

- 1. In the File List view of Diamond, right-click the name of the active implementation, and choose **Add > Existing File**.

- 2. In the "Files of type" list, select **Platform Designer Files** from the drop-down menu.

- Browse to the location of the desired .ptm file, select it, and click Add.

Diamond loads the .ptm file and sets it as the active Platform Designer file for the current implementation.

#### To change the active/inactive status of a .ptm file:

- 1. If the .ptm file that you want to make active or inactive is still open in Platform Designer, close it.

- 2. Right-click the .ptm file and choose the appropriate command: **Set as Inactive** or **Set as Active**.

**Opening an Inactive .ptm File** Platform Designer allows you to open an inactive .ptm file to examine the configurations. The inactive file will open in read-only mode, which will enable you to examine each view but notallow any changes. Platform Designer will close the active .ptm file, if it is open, before opening the inactive one. It will also prompt you to save any changes. You will not be able to execute any of the operations in the Build view (such as Compile, Generate JEDEC) when viewing an inactive .ptm.

**Saving a .ptm File** When you save an active .ptm File, Platform Designer takes all of the configuration changes that are in memory and saves them to

the .ptm file. When you use the "Save as" command to save the.ptm file with a different name or to a new location, Platform Designer includes all of the collateral files for the implementation, as well as any changes in memory. You can also use the "Save as" command for an opened inactive .ptm file.

See Also ▶ "Creating a New Platform Designer Project" on page 8

"Platform Designer Flow" on page 6

## **Working with Platform Designer Editors**

The Current, Temperature, Voltage, and Ports & Nodes editors in Platform Designer use a format that is very similar to a spreadsheet. The columns for these editors are arranged in the order of the most commonly used settings. For example, in the Voltage editor, the four most commonly used columns—ASC Device, Pins Monitor/Trim, VMON Schematic Net Name, and Nominal Profile 0—are positioned first and are locked from horizontal scrolling so that they are always visible for association with other columns and for easy access. The cells of columns that are locked from horizontal scrolling are colored with a light gray background. Columns for less frequently used settings, such as Window Mode, are positioned further to the right and are not locked from horizontal scrolling. The cells of these columns have a white background.

Platform Designer editors differ in a couple of ways from standard spreadsheet formats. In Platform Designer spreadsheets, when you click a cell to enter a value, you click only once and then choose a selection from the drop-down menu or type a value, depending on the type of cell selected. Because of this, navigating from cell to cell by keyboard is slightly different, and copying or cutting and pasting from multiple cells is not supported. The following sub-topics explain how to use the features of Platform Designer editors.

**Sort by Columns** You can sort the row order by a single column by clicking the column heading. An up arrow in the heading indicates that the rows are sorted in ascending order. Click the heading again to sort the list in descending order.

In the Voltage, Current, and Temperature editors, you can also sort the rows by multiple columns.

#### To sort by multiple columns:

- 1. Choose **View** > **M Sort** to open the Sort by Column(s) dialog box.

- 2. Select the first column to sort by from the "Sort by" drop-down menu. Click Ascending or Descending to control the order of the sorted rows.

- 3. Use the "Then by" boxes to select additional columns, as well as the Ascending/Descending option for each column. Click **More** to add more "Then by" menus if needed.

The rows will be sorted first by the column specified in the "Sort by" box and then by the additional columns in the "Then by" boxes in sequence.

#### 4. Click OK.

#### To return to the default layout:

Right-click any column heading and choose **Default Layout** option. This returns the sorted order to the original view.

**Adjust Column Width** You can adjust column widths manually or choose the right-click command to fit the column to the text.

#### To adjust the column width manually:

Drag the vertical border on the right of a column heading.

#### To fit the column width to the text, do one of the following:

- Double-click the vertical border on the right of a column heading.

- ▶ Right-click the desired column heading and choose **Fit Column**.

- Choose View > Column > Fit All Columns to fit all column widths to the text.

**Hide and Re-display Columns** You can hide a single column in the Voltage, Current, or Temperature editor or select several columns that you want displayed or hidden.

#### To hide a single column:

Right-click the desired column heading and choose Hide Column.

#### To hide several columns:

- 1. Choose **View > Column > Visible Columns** or press Shift+F5 to open the Visible/Hide Columns dialog box.

- 2. Do one of the following:

- In the "Show these Columns list," select the columns that you want to hide, and then click the single-arrow button to move them to the "Hide these Columns" list.

- ➤ Click the double-arrow button to move all columns to the "Hide these Columns" list, and then select those you want displayed by selecting them and moving them to the "Show these Columns" list.

- 3. Click OK.

#### To re-display some of the hidden columns:

Press Shift+F5, and move the hidden columns back to the "Show these column(s) list."

#### To re-display all columns:

Press Shift+F5, and click the double-arrow button to move all hidden columns to the "Show these column(s)" list. **Edit Cell Values** The editable cell values in each editor are color-coded blue or black. Blue indicates a default value, and black indicates an edited value. Values that appear in gray are values that cannot be edited, including tool calculated settings or settings that are implied by other areas of the editor.

To edit a single cell value, click once inside the editable cell and enter or select a new value. In the Voltage editor, you can use the Voltage Monitor and Control dialog box to edit the properties for an entire row. See "Setting Multiple VMON/Trim Properties" on page 18.

You can copy or cut a text entry of a single editable cell and paste it into another cell of the same type. You can do this by using the right-click menus or the standard Ctrl+C, Ctrl+X, and Ctrl+V keyboard shortcuts. Copying and pasting multiple cells is not supported.

**Right-click a Text-entry Cell to Open the Complete Menu** The right-click menu will sometimes vary for text-entry cells, depending on whether you have single-clicked a cell for editing or have highlighted the entire cell. For example, on the Ports sheet, when you single click a Logical Name cell, the text in the cell is highlighted so that you can type a new label. But if you right-click while only the text is highlighted, the menu will display editing commands such as cut, copy, paste, or delete, but it will not include the Add Group or Show In commands.

#### To access the complete right-click menu for a text-entry cell:

- ▶ Right-click a cell without clicking it to highlight the entire cell.

- If you have already single-clicked the cell, press the Enter key to highlight the entire cell.

**Navigate from Cell to Cell** Because of the convenient one-click access to parameters in the Current, Temperature, Voltage, and Ports & Nodes editors, navigating by keyboard from cell to cell involves an additional small step.

#### To enable the navigation capability, do one of the following:

- Select a cell in the ASC Device column or the Pin column by singleclicking it.

- If you have already opened an editable cell by clicking it, press **Enter** to highlight the entire cell. If the cell contains a drop-down menu, you might need to press Enter a second time to enable navigation.

#### Note

If you have single-clicked an editable cell in one of the columns that are locked from horizontal scrolling, you will only be able to navigate among the cells of the locked columns after you press Enter. To enable full navigation afterward, click a cell in the ASC Device column or Pin column, or click an editable cell in a column that is not locked from horizontal scrolling and press Enter.

You can then use the arrow keys to move up and down the cells of a column or across the cells in a row. You can also use the Tab key and the Shift+Tab combination to move forward and back across a row. When you have reached a targeted cell for editing, single-click the cell. To continue navigating afterward, press the Enter key.

## **Setting Global Options**

For a new Platform Designer project, you would normally begin by using the Global Configuration view to configure those features that affect the entire design. This includes device options for operation mode and externally connected components such as dual-boot SPI flash. It includes ASC global options as well as options for each individual ASC of the target chip set.

See Also ▶ "Setting ASC Options" on page 14

- "Setting Device Options" on page 15

- "Configuring a SPI Flash Model" on page 16

## **Setting ASC Options**

The ASC options are divided into global ASC options, which affect the entire project, and specific ASC options that affect only a given ASC. Use the left portion of the ASC Options to set the values for each individual ASC, and use the Global ASC Options on the right to set global ASC values.

**Options for Each ASC** The following options are available for individual ASCs:

- ASC Name labels the ASC with a unique name that will identify it globally.

- ► CLT Rate sets the closed loop trim update rate, in µs or ms.

- I<sup>2</sup>C Base Address (ASC0 only) − sets the 4 MSB in the 7-bit I<sup>2</sup>C address of ASC0. This base 4 MSB is common for all ASCs in the system.

- ► I<sup>2</sup>C External Resistor displays the resistor values that are used by the ASC to set the three LSB of the I<sup>2</sup>C address. See the ASC data sheet for more details.

- ▶ I<sup>2</sup>C Address displays the full address of each ASC, using the configured base address and the 3 LSB that are set by the external resistor.

- ▶ UES Bits sets a 32-bit user electronic signature for storing unique data inside the ASC.

- ▶ Reset Type configures the reset type as mandatory or optional. For ASC0, the reset type is fixed to mandatory. Mandatory ASCs have their reset signals tied together on the board. If one of these ASCs needs to be reset, the whole system is reset. Optional ASCs are handled individually and have a dedicated reset signal.

Reset Source – displays the port defined in the reset source for an optional reset type.

#### **Global ASC Options** The following global options affect all ASCs:

- ▶ EIA Resistor Standard limits the resistor selection to the EIA standard selected or, if Exact is selected, calculates the exact resistor values. This value is used by the TRIM calculator in the voltage editor. It determines which resistor values will be recommended by the calculator.

- Open Resistor Threshold sets the maximum resistor value above which the resistor is treated as an open circuit. This setting is used by the TRIM calculator.

- DC-DC Options

- DC-DC Library Directory sets the location for the DC-DC Library. The default directory location is inside the Diamond installation subdirectories.

- ▶ Build DC-DC Library opens the DC-DC Library Builder Wizard, which enables you to add or edit a DC-DC Converter model.

- VID Options

- VID Tables Directory sets the location for the voltage ID tables. The default directory location is inside the Diamond installation subdirectories.

- Build VID Tables opens the VID Table dialog box, which enables you to add or edit a VID table.

- Voltage, Current, and Temperature Options

The Voltage, Current and Temperature monitors are populated with default trip points each time a new project is started. The ASC Global Options Default Trip Point Selections allow you to change the default trip points for each of the monitor types at the start of a new project.

See Also ▶ "Configuring Voltage Identification (VID) Tables" on page 23

"Defining DC-DC Converter Models" on page 21

## **Setting Device Options**

Select the Device Options tab of the Global Configuration View to configure the operation mode and the external connected components.

**Operation Mode Options** The Operation Mode section includes the following options:

- Programming Interface:

- ► MachXO2 and Platform Manager 2: JTAG or I<sup>2</sup>C

- Background Programming:

- Platform Manager 2 and MachXO2 None, I2C, or JTAG.

- ▶ 8MHz Clock Source for Device Operation ASC0 or Global\_Clock

**External Connected Components** The External Connected Components section includes the following options:

- SPI Models Directory Select a location for the SPI models directory.

- Build SPI Models Configure a new SPI model and add it to the SPI Models Directory, or edit or delete an existing SPI model.

- Boot Mode Normal or Dual Boot. When Dual-Boot is selected, the SPI model option will appear. Dual-boot requires that a SPI flash be specified.

- ► ASC I<sup>2</sup>C Write Feature This feature allows you to configure the I<sup>2</sup>C write access to the ASC.

- When "Disabled" is selected, it prevents writing to the ASC on-chip registers over the I<sup>2</sup>C bus.

- When "Enabled" is selected, it allows writing to the ASC on-chip registers over the I<sup>2</sup>C bus.

- When "Controlled by ASCx\_GPIO1" is selected, the ASCx\_GPIO1 input is used to control whether I<sup>2</sup>C write access is enabled.

- ► FPGA Port (External Connection) This option appears when "Controlled by ASCx\_GPIO1" has been selected. You will need to select the FPGA port that will connect to the GPIO1 on all ASCs. Afterwards, the GPIO1 will be changed to "IN" type for each ASC.

See Also ▶ "Defining DC-DC Converter Models" on page 21

"Configuring a SPI Flash Model" on page 16

## **Configuring a SPI Flash Model**

You can use the Global Configuration View to add and configure a new SPI flash model or edit a current one. The SPI flash models are saved in the SPI Models directory. The default directory location is inside the current project sub-directories.

#### To configure a SPI flash model:

- 1. In the Global Configuration View, select the Device Options tab.

- 2. In the External Connected Components section on the right, do one of the following:

- Click Add/Edit SPI Model in the Value column of SPI Options.

- If you are using Dual Boot mode, select **Add/Edit SPI Model** from the Dual-Boot SPI Flash pop-up menu in the Value column.

The SPI Models Configuration dialog box opens and displays the library of currently available SPI models.

- 3. Do one of the following:

- ▶ To edit an existing SPI model, select it from the list on the left.

- ➤ To add a new SPI flash model, click **New**, and then select the newly created model from the list.

- 4. Optionally, give the selected model a unique name, by single-clicking the name and typing a new one.

- Select the desired values for the Flash Configurations and Flash Opcodes by double-clicking the value cell and choosing from the menu, and then press enter. Click **Apply** to save one or more selected values or to save all the values for a selected model.

- 6. If desired, select a different SPI flash model from the list, and repeat Steps 4 and 5.

- 7. When all options have been set for all the models you are configuring, click **OK**.

See Also ▶ "Setting ASC Options" on page 14

"Setting Device Options" on page 15

# Configuring Voltage Sense (VMON) and Control (TRIM)

The Voltage editor enables you to manage voltages and settings related to voltage monitors (VMONs) and trim channels in the Platform Manager 2 or external ASC devices. You can edit a voltage property by clicking the desired cell on the Voltage spreadsheet, or you can use the Voltage Monitor and Control dialog box to edit multiple properties. Double-clicking a VMON/Trim cell in the Pins Monitor/Trim column opens the Voltage Monitor and Control dialog box. From the Voltage Monitor and Control dialog box, you can access the DC-DC Converter Library and the VID Table library.

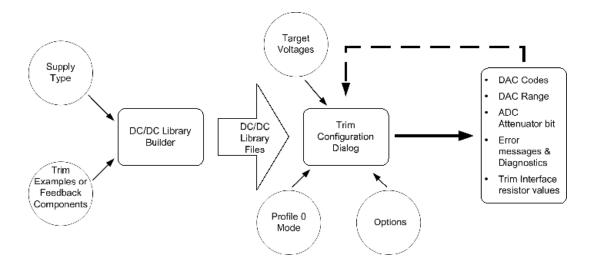

Setting up the trim and margin capabilities involves the DC-DC Library Builder, which is used to define the voltage adjustment characteristics of the power supply or supplies that you wish to use. The Trim/Margin portion of the Voltage Monitor and Control dialog box is then used to configure each trim channel for the desired power supplies and output voltages. The following diagram illustrates this flow:

Modifications to existing DC/DC library files must be made from within the DC/DC Library Builder Wizard. The DC-DC Converter selection, as well as changes in the desired target voltages, can be made in the Trim/Margin section of the Voltage Monitor and Control dialog box. It is strongly advised that library files not be modified while trim cells are being configured, because this can create confusion and make it difficult to detect errors in your work. If a "discrete" supply is to be used at several different voltages, a separate library entry for each unique output voltage should be created.

The Trim/Margin dialog enables you to recalculate the trim with a minimum amount of parameter re-entry. Target voltages need to be re-entered only if the desired supply type is changed.

See Also ▶ "Defining DC-DC Converter Models" on page 21

"Setting VMON Properties" on page 19

## **Setting Multiple VMON/Trim Properties**

The easiest way to set multiple properties for a selected voltage monitor (VMON) or high-voltage monitor (HVMON) is to use the Voltage Monitor & Control Properties dialog box. The edited settings will then be displayed in the Voltage editor.

#### To access the Voltage Monitor & Control Properties dialog box:

- 1. Select the tab in the Voltage editor for those settings that you want to configure.

- In the Pins Monitor/Trim column, double-click the VMON that you want to configure. Alternatively, right-click and choose Edit from the pop-up menu.

The Voltage Monitor & Control Properties dialog box opens and displays the Voltage, Trim/Margin, or VID section, depending on the tab you selected in the Voltage editor.

The number of tabs available in the Voltage Monitor & Control Properties will depend on whether the selected VMON supports an associated TRIM pin. Most of these properties can also be defined individually on the Voltage spreadsheet.

See Also ▶ "Setting VMON Properties" on page 19

- "Setting Trim and Margin Properties" on page 20

- "Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## **Setting VMON Properties**

The Voltage section of the Voltage Monitor & Control Properties dialog box allows you to specify the nominal voltage and the logical names and trip points for each comparator.

- ► Schematic Net Name This can consist of any combination of alphanumeric characters.

- Nominal Voltage This defines both the nominal voltage and the closed loop trim target value for voltage profile 0. If the value is 5.7V or more and the monitor is not an HVMON, the voltage will be used to calculate an external resistor divider and select an associated trip point. A negative voltage will calculate a divider reference as well as the resistor divider. Acceptable values are from -100 volts to 100 volts.

- ▶ Logical Name The logical names, for comparators A and B, are used in the logic builder to control the sequence and equations based on the VMON status.

- ► Trip Point Selection A specific VMON trip point, for comparator A and comparator B, is associated with each logical name.

- 64 µs Glitch Filter When selected, this option configures the comparator so that supply glitches narrower than 64 microseconds are ignored. The output will transition only if the changed status remains active for a period longer than 64 microseconds. If this option is not selected, the comparator output will toggle within 16 microseconds from the time the voltage transitions through the appropriate trip point.

- Window Mode To use the window mode, the Comparator B threshold should be lower than the threshold setting of comparator A. The window mode output will replace the comparator A output. The window output is logical high if the Comparator B output is high and the Comparator A output is low (i.e., the voltage monitor reading is between Comparator A and Comparator B).

- ▶ External Resistor Divider This section is used for monitoring a voltage whose highest trip point exceeds 5.70V or is a negative voltage. These values are calculated automatically when the nominal voltage specified is negative or exceeds 5.70V. You can overwrite these values to work with your preferred components.

- Rsupply Valid value range is 10 ohms to 10 M ohms

- Rground Valid value range is 10 ohms to 15 K ohms. The Rground maximum value is restricted to maintain the accuracy of the voltage monitors.

- Divider Reference Valid value range is 2.5 V to 6 V. The divider reference is used when monitoring voltages below ground. The external divider is connected between the negative supply being monitored and a positive reference supply.

See Also ▶ "Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## **Setting Trim and Margin Properties**

The Trim/Margin section of the Voltage Monitor and Control dialog boxenables you to configure the trim cell operating mode and desired output voltages measured at a voltage monitor (VMON).

- ► Trim Schematic Net Name This can consist of any combination of alphanumeric characters.

- Trim Configuration Mode The Trim Calculator, which is selected by default, calculates resistor interface and DAC values from the target voltages and DC-DC converter.

- Manual trim configuration mode allows you to select the CLT loop polarity and to manually enter the DAC code for each voltage profile.

- DC-DC Converter Select a DC-DC converter model from the drop-down menu. The menu includes all of the models that are in the DC-DC Library. To add a new model, scroll down and select Add/Edit DC-DC to open the DC-DC Library Builder Wizard.

- ► CLT Loop Polarity If you selected Manual for the trim configuration model, select the polarity for closed loop trim.

- Voltage profile − Enter a desired output voltage for each profile. These profiles are used, along with the nominal voltage profile (profile 0), as the targets for the trim calculator.

- DAC Output Range (BPZ Voltage) If you are using the Trim Calculator, the bipolar zero output voltage range will be calculated automatically. If you are using manual trim configuration mode, select the value from the drop-down menu.

If you have selected Trim Calculator for the trim configuration mode, click the **Calculate** button after you have made your selections. The dialog box will then provide the following information:

- the resistor values needed to interface the DAC to the TRIM pin in the DC-DC converter

- b the voltage that will be achieved with each of the voltage profiles

- the DAC code needed to produce each of the desired output voltages

If a profile target voltage is outside an achievable range, it will be tagged with \*Error. To resolve errors, click the **Error Details** button and follow the instructions for obtaining a possible solution.

**Setting Trim Configuration Options** Use the Trim Configuration Options dialog boxto adjust settings and to help resolve a target voltage error.

Click the **Options** button in the Trim/Margin Properties dialog box to set the following options:

Maximum DAC Code Range – This setting and the Max Supply Adjustment Range work together to define the sensitivity of the trim system. The value entered defines the DAC value required to trim the supply voltage by the amount specified in the Max Supply Adjustment Range box.

- Max Supply Adjustment Range This value defines how much the power supply output voltage will change when the DAC code is at the value in the Maximum DAC Code Range box.

- Attenuation Crossover Voltage If the voltage in Voltage Profile 0 is greater than the voltage in the Attenuation Crossover Voltage text box, the DAC input attenuator will be enabled. The attenuation crossover voltage should be selected so that the attenuation bit is turned on if any portion of the trim range is over 2.048 volts. The default value of 1.9 volts is appropriate in most cases.

- Vbpz Selection When Auto is selected, the bi-polar zero output voltage is calculated automatically to reach all the target voltages. Selecting one of the other voltages (0.6V, 0.8V, 1V, or 1.25V) can sometimes reduce the number of resistors.

See Also

"Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## **Defining DC-DC Converter Models**

The DC-DC Library Builder Wizard enables you to define the voltage adjustment characteristics of DC-DC converters and voltage regulators. This information is stored in a library so that any given model of DC-DC converter can be used in multiple trim cells or Platform Designer projects without having to re-enter the information each time.

You can add new DC-DC converter models to the library, delete models, or edit the parameters of a model at any time by launching the wizard. Any converter model in the library can be selected in the Trim/Margin portion of the Voltage Monitor and Control dialog box.

You can launch the DC-DC Library Builder Wizard from the Global Configuration view or from the Voltage Monitor and Control dialog box.

## To launch the DC-DC Library Builder Wizard from the Global Configuration View:

- 1. In the Global Configuration view, select the ASC Options tab.

- 2. In the DC-DC Options section of Global ASC Options, click **Add/Edit DC-DC**.

## To launch the DC-DC Library Builder Wizard from the Voltage Monitor and Control dialog box:

- 1. In the Voltage view, select the Trim/Margin tab.

- 2. Double-click a cell in the DC-DC Converter column or a VMON/Trim cell in the Pins Monitor/Trim column.

- In the Voltage Monitor and Control dialog box, click the DC-DC Converter drop-down menu.

- 4. Scroll down and choose Add/Edit DC-DC.

The DC-DC Library Builder Wizard provides the option of creating a new entry in the library (using the New button) or modifying an existing entry. The flow for both operations is similar, the only exception being that when an existing entry is being edited, the previously saved parameters appear in the different dialog box sections of the Wizard.

#### To define a DC-DC converter model:

In the DC-DC Converter Model Selection, select a model from the list, or click **New** to add a new model.

The Library Builder classifies all DC-DC converters and regulators into four different families:

- Supplies that can be adjusted up or down a few percent about a nominal voltage by connecting a resistor between the supply's TRIM pin and its output or ground.

- Supplies that can be adjusted over a wide range by connecting a resistor between the supply's TRIM pin and ground.

- Supplies that can be adjusted over a wide range by connecting a resistor between the supply's TRIM pin and Vout.

- Supplies that use an external feedback network. The Library Builder calls this a "discrete" implementation.

- 2. Click **Next** to open the Select the type of DC-DC Converter section.

- 3. Select the type of DC-DC Converter and click **Next**.

The wizard opens the configuration section of the dialog box, which enables you to set the parameters for the type of converter you selected.

For the Trim-up Trim-down supply type and the Programmable supply type, the dialog box asks for several trimming examples to be entered, and the supply's adjustment characteristics are determined from the data. Many power supply data sheets provide tables of resistor values needed to achieve various different outputs. These examples can be entered directly into the dialog box.

For discrete implementation types, the dialog box requests the values of the feedback network components and the internal reference voltage. From the data, the supply's adjustment characteristics are determined. When a specific model of voltage regulator will be used several times to produce different voltages, separate library entries will be needed for each unique set of feedback network components.

4. After setting the configuration parameters, click **Finish**.

See Also ▶ "Setting Multiple VMON/Trim Properties" on page 18

- "Setting VMON Properties" on page 19

- "Setting Trim and Margin Properties" on page 20

## Configuring Voltage Identification (VID) Tables

Voltage identification tables define the target voltage outputs of a DC-DC converter based on inputs of a selected bus. The VID section of the Voltage Monitor and Control dialog box enables you to select and configure a VID table for the selected voltage monitor. If your design does not yet contain VID tables, you can build them and add them to the VID Table Library.

**Building VID Tables** The Voltage – VID Table Library interface enables you to build a library of voltage identification tables. By default, Platform Designer stores the VID tables inside the Diamond installation sub-directories. You can specify a different location in the Global ASC Options section of the Global Configuration View.

#### To create a new VID table:

- In the Voltage editor, open the VID Table library dialog box by using one of the following methods:

- Open the Voltage Monitor & Control Properties dialog box by doubleclicking the VMON/TRIM cell. Select the VID tab, and choose Add / Edit a table from the VID Lookup Table drop-down menu.

- In the Global Configuration View, select the ASC Options tab. In the VID Options section on the right, click Add / Edit a table.

- In the VID Table Library dialog box, click **New** to open the Create New VID Table dialog box.

- 3. Type a name for the VID table in the text box, and then select the table size from the drop-down menu.

- 4. In the Auto fill section, specify a voltage starting value and step size. Alternatively, you can manually enter each value in the table by double-clicking each Voltage (V) cell and typing a value. If you choose manual entry, skip Step 5.

- Select either the Top Down or Bottom Up option, and then click Fill.

Platform Designer fills in the voltage for each VID value, based on the step size and starting value. You can edit any of these values as desired.

- 6. Click OK.

The new VID table is added to the VID Library and will be listed in the VID Table menu in the Voltage editor and in the Voltage Monitor & Control Properties dialog box.

**Selecting and Configuring the VID Table** The VID page of the Voltage editor enables you to select the VID lookup table from the VID Table Library and select the bus, strobe port or node, and VID strobe edge. You can also select and configure the VID table from the Voltage Monitor & Control dialog box.

**Editing a VID Table** To edit a VID Table, open the VID Table library dialog box by using any of the methods described in Step 1. Select a VID table and

click **Edit**. In the Edit the VID Table dialog box, change the settings as desired and click **OK**.

See Also "Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## Configuring Current Sense (IMON)

The Current editor allows you to set parameters for the current monitor (IMON) and high-voltage current monitor (HIMON) for each Analog Sense and Control device. Each monitor includes settings for two precision comparators (A and B) and one fast (F) comparator.

- Schematic Net Name Each IMON or HIMON must be identified by a unique name. The name can consist of any combination of alphanumeric characters.

- ▶ Logical Name The monitor's comparator outputs A, B, and F must each be identified by a unique name. The name can consist of any combination of alphanumeric characters.

- Sense Resistor (Ohm) The sense resistor value will be the same for all comparators within the monitor and can range from .0001 to 1000000.0 ohms.

- ➤ Trip Point Selection (Amps) The selected trip point, for comparators A, B, and F, will be associated with each logical name. The trip points available are determined by the Sense Resistor value.

- Hysteresis Hysteresis can be enabled or disabled for comparators A and B. This automatically updates the available trip point selections.

- Glitch Filter (μ) The glitch filter can be enabled or bypassed for comparators A and B. When Yes is selected, this option configures the comparators so that supply glitches narrower than 64 microseconds are ignored.

- Window Mode Window mode can be used for comparators A and B. To use the window mode, the Comparator B threshold should be lower than the threshold setting of comparator A. The window mode output will replace the comparator A output. The window output is logical high if the Comparator B output is high and the Comparator A output is Low.

- Low Side Sense When Yes is selected, this sets the low voltage side sense for comparators A, B, and F. It is not available for high-voltage sense monitors.

The Programmable Gain Amplifier (PGA) Gain setting is displayed by the tool based on the selected trip points. This information is used when performing A/D measurements of the current over I<sup>2</sup>C.

The V-Drop (V) and Peak Power (W) are calculated based on the values entered for trip point and sense resistor.

See Also ▶ "Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## Configuring Temperature Sense (TMON)

The Temperature editor allows you to set parameters for the external temperature sensor interfaces (TMON1, TMON2, etc) and the internal temperature sensor (TMON\_Int). The temperature monitor function includes an A/D converter measurement with averaging support, as well as an alarm monitor function with programmable hysteresis and filtering. Each TMON channel includes two separate programmable comparison points. The temperature sensor hardware also supports a configurable offset and ideality factor. The parameters for each temperature monitor comparator can be set in Platform Designer's Temperature editor, as follows:

- Schematic Net Name The schematic net name must be unique and can consist of any combination of alphanumeric characters.

- Logical Name This must be a unique name that will identify each TMON pin and comparator output. It can consist of any combination of alphanumeric characters.

- ► Monitoring Type Over temperature (OT) or under temperature (UT) monitoring can be selected.

- ▶ Trip Point Selection This sets the trip point for the comparator in degrees Celsius.

- ► Hysteresis This defines the hysteresis for updating the trip point output for the comparator.

- ▶ Monitor Alarm Filter (Depth) This sets the number of consecutive alarms that must be detected before setting the comparator output high.

- Measurement Averaging (Filter Coefficient) This sets the coefficient on the averaging filter implemented on the temperature sensing of the TMON.

- Offset This calibration value is used to correct the temperature reading, in degrees Celsius for the TMON.

- Short Fault Measurement Reading This defines the measurement reading under a short fault condition. It implies the Open fault measurement reading as well. See the Platform Manager 2 or MachXO2 data sheet for more details.

- ▶ Ideality Factor This calibration value is used to correct the diode imperfection for the TMON.

- Sensor Configuration The external temperature monitors can be configured to interface with several different transistor circuits.

See Also ▶ "Configuring Fan Control" on page 26

"Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## **Configuring Fan Control**

Platform Designer's Fan Controller provides fan control for 2-wire, 3-wire, or 4-wire fans. The fan controller supports multiple fan speeds, under-speed alarm detection, and a configurable startup pulse. It enables you to set three levels of speed control through the pulse width modulated (PWM) signal. Up to 18 separate fans can be controlled.

#### To configure fan control:

- Select Fan Controller from the menu pane, and then select a fan in the "Fan in System" list or add a new fan by clicking the add button on the lower left.

- 2. In the Type Setting section on the Parameters page, select the fan type from the drop-down menu.

- 3. If you selected 3 Wire (Low Side Drive), 3 Wire (High Side Drive), or 4 Wire, also specify the **Sense Type** for alarm detection, as follows:

- If the fan supports a locked signal as fan feedback to indicate that the fan is locked or stuck, select Alarm (Active High) or Alarm (Active Low).

- If the fan includes a tachometer feedback signal, select **Tach** (2 Pulses/Rev), and then do the following:

- In the Alarm Interval box, type a value for the number of ms that will be allowed between pulses before an under-speed violation is registered.

- Select a value between 1 and 10 from the Alarm Filter Count. This is the number of times the alarm interval must be detected before the Alarm signal will be asserted.

With tachometer feedback, a +/- 10% hysteresis will be applied to the corresponding assertion/de-assertion of the failure count to prevent a false alarm.

- 4. In the PWM Setting section, use the sliders to select a duty cycle percentage for Speed3, Speed2, and Speed1.

- Each can be set in 5% increments, ranging from 5% to 95%. The fastest speed must be assigned to Speed3, with the middle speed assigned to Speed2, and the slowest speed assigned to Speed1.

- 5. Use the slider to specify the PWM frequency. The frequency can be set in increments of 0.8 kHz, up to 80.0 kHz.

- Select the polarity for the PWM signal, based on the nature of the MOSFET switch and on-board buffers.

- Refer to the fan data sheet and the board requirements for information about the correct setting of PWM polarity.

- 7. Optionally, enable the Startup Control and select the pulse duration, in increments of .25s for the startup period.

- When startup control is enabled, the fan controller will send a kickstart pulse of the chosen duration to the fan before switching to the selected PWM setting.

Select the InterConnections tab.

The InterConnections page allows you to specify the signals that the Platform Designer will use as fan controller ports. Each fan has an independent set of interconnections.

The PWM Out and Tach/Alarm Sense are the external connections to the fan. The other signals (Speed Sel 1 ... Alarm Out) are logical connections that set the operation of the fan controller during runtime.

- 9. Assign the PWM Out and Tach/Alarm Sense to external ports by dragging the desired ports from the Signal Pool.

- 10. Drag the desired signals from the Signal Pool to set the logical connections for Speed Sel, Run Off, Run Full, and Alarm Out.

See Also ▶ "Configuring Temperature Sense (TMON)" on page 25

"Configuring Voltage Sense (VMON) and Control (TRIM)" on page 17

## **Setting Fault Logging Options**

The Fault Logger, available from the Components section of the menu pane, enables you to specify and configure fault conditions that are logged to non-volatile memory. You have the option of using standard fault logging that is based on voltage, current, and temperature status; or using the full-featured fault logging. By default, fault logging is disabled.

Each ASC device contains a block of EEPROM memory that can be used for either the V, I, T Fault Log or for User Tag Operation. The User Tag Memory is enabled automatically when fault logging is disabled or when full-featured fault logging is selected. It is disabled when V, I, T fault logging is selected.

**V, I, T Fault Logging** When you select this option, the Analog Sense and Control device will log the voltage (V), current (I), and temperature (T) status when a fault is detected. The V, I, T fault log supports the logging of 8 signals per Analog Sense and Control device, in addition to the V, I, T signals. These can be digital I/O or other signals.

#### To configure V, I, T fault logging:

- 1. In the Fault Logger, select **Enable V, I, T Fault Log** from the options shown at the top left.

- 2. Select a signal name from the Fault Logging Trigger Signal Name dropdown menu. This signal can be an output from the user logic, an external digital I/O, or a specific monitor alarm signal.

- 3. In the "Basic Configuration" section, select the type of memory to log to: EEPROM or SRAM. The EEPROM is non-volatile, but a log takes longer to execute. The SRAM memory is volatile but is executed more quickly.

- 4. The V, I, T fault log supports the logging of 8 signals per Analog Sense and Control device in addition to the V, I, T signals. These can be digital I/O or other signals. For each signal that you want to log, drag it from the "User Signals to Log" list over to a D cell of the desired ASC.

**Full-Featured Fault Logging** The full-featured fault logging uses either the UFM Flash memory within the device or an external SPI flash memory. Full-featured fault logging is available for Platform Manager 2 LPTM21 devices and for MachXO2 devices of 1200 and above.

#### To configure full-featured fault logging:

- 1. In the Fault Logger, select **Enable Full-Featured Fault Log** from the options shown at the top left.

- 2. Select a signal name from the Fault Logging Trigger Signal Name dropdown menu. This signal can be an output from the user logic, an external digital I/O, or a specific monitor alarm signal.

- 3. n the "Basic Configuration" section, do the following:

- a. From the drop-down menu, select the contiguous ASCs that you want logged.

- b. Select **Include Timestamp** if you want Platform Designer to include a 32-bit timestamp timer.

- c. Select a signal to be used as the busy signal name from the "Busy" Signal Name menu. This signal is an output from the fault logger and can be used to inform the user logic that a fault log recording is in progress.

- Select a "Log to" option: the on-chip UFM memory or external SPI flash.

- e. If you selected External SPI Flash as the "Log to" option, use the Model drop-down menu to select the external flash model to be used for fault logging.

- 4. In the User Log Fields menu, located above the user log table on the right, select the number of additional bits to record in the fault log.

- 5. For each additional signal that you want to log, drag it from the "User Signals to Log" list over to a D cell of the desired user log column.

See Also ▶ "Configuring a SPI Flash Model" on page 16

### Configuring Hot Swap

Platform Designer's Hot Swap utility enables you to configure a hot swap component that will control the in-rush current in applications where power is rapidly applied, such as a circuit board that is plugged into a backplane. The Hot Swap utility contains a separate page for each of the following three tasks:

- Hot Swap Specify the settings of a hot swap component.

- Interface Connect the hot swap component to the Platform Manager 2 resources.

- ► InterConnections Connect the hot swap component to the hardware management logic.

#### To specify the settings of a hot swap component:

- 1. Select **Hot Swap** from the Components section of the menu pane.

- 2. On the Hot Swap page, select a hot swap component from the list or create a new hot swap component by clicking the add button on the lower left.

- 3. Specify the desired options and settings:

- Input Supply

- V<sub>IN</sub> Input voltage. This is the supply voltage input, which is used to charge C<sub>LOAD</sub>. Together with I<sub>MAX</sub>, C<sub>LOAD</sub> and the MOSFET SOA (Safe Operating Area) information will be used to calculate the hot swap parameters, including the number of phases, voltage and current trip points.

- ▶ I<sub>MAX</sub> Maximum current available from the input supply.

#### MOSFET Parameters

- Load/Supply Allows you to place the MOSFET at either the Supply or the Load. Select the setting that matches your application.

- ▶ MOSFET Name Used, for informational purposes only, to track the part number of the MOSFET in your application.

- V1/A1 Voltage/Current data point pair from the MOSFET SOA curve found in the MOSFET datasheet.

- V2/A2 Voltage/Current data point pair from the MOSFET SOA curve. V1 must be greater than V2, and A1 must be less than A2.

#### Current Sensing Configuration

- R<sub>S</sub> Sense Resistor used in the application. Platform Designer uses this sense resistor value to calculate available current sensing trip points.

- Current Sense Amp choices Determines the current sense amp circuit used in the application.

- The choice among "External and VMON," "External and IMON," and "IMON (Internal)" will determine whether additional current sensing circuit information is required. The choice also determines which monitor circuits are available for assignment in the Interface tab. Certain configurations of  $V_{\text{IN}}$  and Current Sense Amp are prohibited, such as using IMON (Internal) with  $V_{\text{IN}}$  voltages above 13.2V.

- Low Side option Determines whether the IMON is used in a near ground hot swap application (such as -48V). Selecting this option enables the Low-Side Sense feature in the IMON circuit.

#### Hot Swap Settings

C<sub>LOAD</sub> – The load capacitor charged up during the hot swap operation. This value is used to calculate the hot swap parameters, including the number of phases and the voltage and current trip points.

- Fast Shutdown Limit Sets the current limit for fast shutdown during hot swap. The menu is automatically populated with available current limit trip points related to the Sense Resistor and Current Sense Amp settings. If the current exceeds the selected limit during hot swap, the hot swap will be aborted and the over current error signal will be asserted. This feature can be disabled by selecting "None."

- Cooldown Period The period used by the hot swap algorithm to ensure that the MOSFET does not overheat. Each time the hot swap algorithm detects a timeout, remaining in a phase longer than 10 ms, the cooldown period will be used as a wait time prior to resuming the hot swap operation.

- ► Hot Swap Name A user-defined name for the hot swap setup.

- 4. After all the parameters have been selected, click the Calculate button.

The  $V_{LOAD}$  and  $I_D$  graphs are updated with the estimated Voltage and current profiles based on the calculated Hot Swap algorithm and settings. The Results/Comments area is updated with information, including the number of hot swap phases and the number of VMON and IMON channels required to support the hot swap implementation.

The hot swap calculation might not be able to provide a solution for all circuit configurations. In this case, error information is displayed in the Diamond message console.

5. If the results are not satisfactory, adjust the settings and calculate again.

#### To connect the hot swap component to Platform Manager 2 resources:

1. After you are satisfied with the hot swap calculation results, select the **Interface** tab.

The Interface page consists of several menus that are used to assign VMONs, IMONs, HVOUT, GPIO and PIO channels to the different hot swap functions. When you assign VMON, IMON, and HVOUT channels in the Interface tab, their settings, such as trip point thresholds, will be updated automatically.

- 2. Select the desired setting from each of the drop-down menus in the gold-colored boxes, as follows:

- V<sub>IN</sub> Monitor Associates a VMON channel with the input voltage monitoring function of a given hot swap. This VMON channel can be re-used across multiple hot swap components, if they use the same input voltage. The V<sub>IN</sub> Monitor can be from any ASC in the Platform Manager 2 system.

Selecting a V<sub>IN</sub> Monitor is mandatory.

ASC – Specifies the ASC device to be used. The ASC menu is automatically populated with the ASCs used in the system. All channels from the drop-down menus inside the pink rectangle will be selected from the chosen ASC.

- MOSFET/Charge Pump Driver Associates an HVOUT or GPIO with the controlled output signal used in the hot swap algorithm.

- Selecting an HVOUT or GPIO is mandatory.

- Current Sensing Monitor Specifies the IMON or VMON channel for current sensing. The channels available are those that support the configurations that were set on the Hot Swap page.

- Selecting a current sensing monitor is mandatory.

- ► Fast Current Sense Monitor Specifies an IMON or VMON channel for fast current sense. This menu is used only when a fast shutdown limit is selected on the Hot Swap page. It is used in conjunction with the fast current sense output, fast path input, and fast shutdown signal.

- Fast Current Sense Output Specifies an HVOUT or GPIO as a fast output signal. This menu is populated with the output signals available on the ASC.

- Fast Path Input Specifies a signal for fast path input. This menu is populated with the PIO signals from the FPGA I/O used in the Platform Manager 2 system. The signal should be externally connected to the fast current sense output signal in the application.

- ► Fast Shut Down Output Specifies a signal for fast shutdown output. This menu is populated with the PIO signals from the FPGA I/O used in the Platform Manager 2 system. The signal is controlled by the hot swap IP and will perform a fast shutdown of the MOSFET when necessary.

- ▶ Load Voltage Monitor(s) Specifies the load VMON or HVMON. This menu is populated with the voltage monitor channels from all ASCs in the Platform Manager 2 system. The number of drop-down menus available is determined by the number of phases required by the hot swap algorithm. These menus can be filled with voltage monitor channels from any ASC in the system.

- Selecting a load voltage monitor from each available menu is mandatory.

#### To connect the hot swap component to the hardware management logic:

- 1. Select the **Interconnections** tab.

- The Interconnections page includes a set of control signals that are used to connect the hot swap component to the hardware management logic. Each of these signals is typically assigned to a node.

- 2. Drag the desired signal from the Signal Pool over to the appropriate box, as follows:

- ▶ Hot Swap Enable Input signal to the hot swap component. Asserting this signal high will start the hot swap operation.

- Over-Current Clear Input signal to the hot swap component. This signal needs to be asserted to clear any existing Over-Current Error status.

- Hot Swap Done Output signal from the hot swap component. This signal is asserted by the hot swap component to inform the hardware management logic that the hot swap operation was successfully completed. This signal is cleared when the hot swap enable signal is asserted again.

- Hot Swap Error Output signal from the hot swap component. This signal is asserted by the hot swap component to inform the hardware management logic that an error occurred during the hot swap operation. This signal is cleared when the hot swap enable signal is asserted again.

- Over-Current Error Output signal from the hot swap component. This signal is asserted by the hot swap component to inform the hardware management logic that an overcurrent error occurred during the hot swap operation. This is in addition to the fast path shutdown behavior. This signal will be cleared when the over-current clear signal is asserted.

# **Configuring PMBus Adapter**

PMBus is a serial communication bus that allows a microcontroller to configure and monitor Digital Point of Load (DPOL) DC-DC Converters. The PMBus Adapter allows the connection of analog POLs to the PMBus controller using the FPGA and ASC. Multiple POLs may be mapped to different pages configured in the PMBUS adapter. Dedicated pages for voltage, current, and temperature monitoring are provided.

The PMBus adapter supports Packet Error Checking and SMBAlert options. The PMBus adapter supports a pre-defined subset of PMBus commands.

#### To configure PMBus Adapter: