# NOR Flash Memory Controller with WISHBONE Interface

November 2010 Reference Design RD1087

## Introduction

NOR Flash memory provides random access capabilities to read and write data in specific locations in the memory without having to access the memory in sequential mode. Its high-speed read capacity allows the NOR Flash memory to be the first choice for code storage and direct execution in a variety of systems from computer BIOS to portable electronic devices.

In today's NOR Flash market, most NOR Flash memory devices share common basic design concepts. These memory devices are controlled by chip enable (CEn), output enable (OEn) and write enable (WEn). Device operations are executed by a standard set of command codes. These command codes are supported by most NOR Flash memory devices in the market. The command codes are combined with addresses and data, and are written sequentially to the command registers using microprocessor write timing.

This reference design describes the use of Lattice programmable devices to implement a NOR Flash memory controller through a WISHBONE bus. It supports several common operational modes of a NOR Flash, including reset operation, autoselect manufacturer ID operation, read operation, program operation, chip erase operation and sector erase operation. It is available in both Verilog and VHDL languages.

#### **Features**

- WISHBONE host interface

- Supports reset operation, autoselect manufacturer ID operation, read operation, program operation, chip erase operation and sector erase operation of NOR Flash memory

- · Supports both Word configuration Flash memory and Byte configuration Flash memory

- Address width of NOR Flash memory configurable from 1 to 32 bits

- Read/write cycle access time can be optimized for a specific NOR Flash memory through the setting of timing parameters in the design

# **Functional Description**

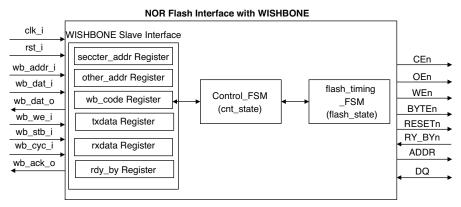

The functional block diagram of the NOR Flash Memory controller with WISHBONE interface is shown in Figure 1. This design has a standard WISHBONE slave bus that connects the NOR Flash memory device with a microprocessor and other on-chip components. From the WSHIBONE bus, this design appears as a set of addressable registers that can be read from or written to. Through these registers, the WISHBONE master can transmit and receive data and control the operation of the NOR Flash memory. The control Finite State Machine (FSM) is used to enter the appropriate operational modes of NOR Flash based on the WISHBONE code (wb\_code) register which is set by the WISHBONE master. For every operational mode of NOR Flash, the control\_FSM calls a timing FSM to generate appropriate control signals to access the NOR Flash based on the NOR Flash memory timing specification.

Figure 1. NOR Flash interface with WISHBONE Block Diagram

## Interface

Table 1. NOR Flash Interface with WISHBONE I/O Interface Descriptions

| Signal Name              | Signal       | Active State    | Definition                        |  |  |  |  |

|--------------------------|--------------|-----------------|-----------------------------------|--|--|--|--|

| WISHBONE Slave Interface |              |                 |                                   |  |  |  |  |

| clk_i                    | Input        | N/A             | System clock signal.              |  |  |  |  |

| rst_i                    | Input        | High            | Asynchronous system reset signal. |  |  |  |  |

| wb_addr_i[3:0]           | Input        | N/A             | Slave address bus.                |  |  |  |  |

| wb_dat_i[15:0]           | Input        | N/A             | Slave data input bus.             |  |  |  |  |

| wb_dat_o[15:0]           | Output       | N/A             | Slave data output bus.            |  |  |  |  |

| wb_we_i[3:0]             | Input        | 1 write; 0 read | Slave write/read signal.          |  |  |  |  |

| wb_stb_i                 | Input        | High            | Slave strobe signal.              |  |  |  |  |

| wb_cyc_i                 | Input        | High            | Slave cycle signal.               |  |  |  |  |

| wb_ack_o                 | Output       | High            | Slave acknowledge signal.         |  |  |  |  |

| NOR Flash Memory Interi  | face         |                 | ·                                 |  |  |  |  |

| CEn                      | Output       | Low             | Chip enable signal.               |  |  |  |  |

| OEn                      | Output       | Low             | Output enable signal.             |  |  |  |  |

| WEn                      | Output       | Low             | Write enable signal.              |  |  |  |  |

| BYTEn                    | Output       | 1 word; 0 byte  | Word/Byte selection.              |  |  |  |  |

| RESETn                   | Output       | Low             | Hardware reset signal.            |  |  |  |  |

| RY_BYn                   | Input        | 1 ready; 0 busy | Ready/Busy signal.                |  |  |  |  |

| ADDR[addr_width-1:0]     | Output       | N/A             | Address signal.                   |  |  |  |  |

| DQ[15:0]                 | Input/Output | N/A             | Data inputs/outputs.              |  |  |  |  |

#### **WISHBONE Interface**

The WISHBONE slave interface consists of six registers which are used to interact with the WISHBONE master. A description of each of these addressable registers is shown in Table .

Table 2. Register Descriptions

| Register    | Width             | WISHBONE<br>Access | Address | Description                                                                  |

|-------------|-------------------|--------------------|---------|------------------------------------------------------------------------------|

| sector_addr | SECTOR_ADDR_WIDTH | Read/Write         | 0x0     | Sector address.                                                              |

| other_addr  | OTHER_ADDR_WIDTH  | Read/Write         | 0x1     | Least significant bits of the ADDR.                                          |

| txdata      | 16                | Read/Write         | 0x2     | Data to be sent to the NOR Flash.                                            |

| rxdata      | 16                | Read Only          | 0x3     | Data to be received from the NOR Flash.                                      |

| rdy_by      | 1                 | Read Only          | 0x4     | Ready/Busy status register.                                                  |

| wb_code     | 4                 | Read/Write         | 0x5     | Code in this register indicates the operation the WISHBONE master initiates. |

The address (defined by the ADDR signal) of a NOR Flash is divided into two parts. The most significant bits of ADDR indicate the address of a sector/bank/block. Different manufacturers may use any of these terms to describe this. The least significant bits of ADDR indicate a certain address in the specified sector. The sector\_addr register contains the most significant bits of ADDR and the other\_addr register contains the least significant bits. The width of the sector\_addr register and other\_addr register is defined by the parameters SECTOR\_ADDR\_WIDTH and OTHER\_ADDR\_WIDTH, respectively. The width of the ADDR signal is defined by the parameter ADDR\_WIDTH. These parameters are described in Table 3.

Table 3. Parameter Descriptions

| Parameter         | Description                                                                                          | Active Value | Default Value |

|-------------------|------------------------------------------------------------------------------------------------------|--------------|---------------|

| SECTOR_ADDR_WIDTH | Specifies the sector address width.                                                                  | 1 to 16      | 8             |

| OTHER_ADDR_WIDTH  | Specifies the address width in a certain sector.                                                     | 1 to 16      | 8             |

| ADDR_WIDTH        | Specifies the width of the ADDR signal. Equals to the sum of SECTOR_ADDR_WIDTH and OTHER_ADDR_WIDTH. | 1 to 32      | 16            |

| WORD_BYTEn        | '1' indicates Flash in Word configuration. '0' indicates Flash in Byte configuration.                | 0, 1         | 1             |

The txdata register contains the data that is written to the Flash memory and the rxdata register contains the data that is read from the Flash memory.

The wb\_code register contains the code that indicates the operation the WISHBONE master initiates. Table 4 lists the coding of wb\_code register. The rdy\_by register indicates whether the NOR Flash finishes the current operation. '1' means the NOR Flash is ready for the next operation and '0' means the NOR Flash is busy.

Table 4. Coding of wb\_code Register Descriptions

| Coding of wb_code Register | Description                                                                |

|----------------------------|----------------------------------------------------------------------------|

| "0001"                     | WISHBONE master initiates the reset operation to the Flash.                |

| "0010"                     | WISHBONE master initiates the read manufacturer ID operation to the Flash. |

| "0011"                     | WISHBONE master initiates the sector erase operation to the Flash.         |

| "0100"                     | WISHBONE master initiates the chip erase operation to the Flash.           |

| "0101"                     | WISHBONE master initiates the read operation to the Flash.                 |

| "0110"                     | WISHBONE master initiates the program (write) operation to the Flash.      |

## **WISHBONE Master Command Sequence**

Each operation to the NOR Flash memory has its own event sequence initiated by the WISHBONE master. This section details the command sequence for each operation.

#### Reset operation:

- 1. Write code "0001" to the wb code register.

- 2. Read the rdy\_by register until the value of this register is '1'.

#### Read manufacturer ID:

- 1. Write code "0010" to the wb\_code register.

- 2. Read the rdy\_by register until the value of this register is '1'.

#### Sector erasure:

- 1. Write the sector address to the sector\_add register.

- 2. Write code "0011" to the wb\_code register.

- 3. Read the rdy\_by register until the value of this register is '1'.

#### Initiating chip erase:

- 1. Write code "0100" to the wb\_code register.

- 2. Read the rdy\_by register until the value of this register is '1'.

#### Read operation:

- 1. Write the sector address (most significant bits of ADDR) to the sector\_addr register.

- 2. Write to the other\_address with the least significant bits of ADDR.

- 3. Write code "0101" to the wb\_code register.

- 4. Read the rdy\_by register until the value of this register is '1'.

- 5. Read the rxdata register which contains the data from the Flash.

#### Program/write operation:

- 1. Write the sector address (most significant bits of ADDR) to the sector\_addr register.

- 2. Write to other\_address with the least significant bits of ADDR.

- 3. Write to the txdata register with the data to be written to the Flash.

- 4. Write code "0110" to the wb\_code register.

- 5. Read the rdy\_by register until the value of this register is '1'.

#### Operational Mode of the NOR Flash

Once the wb\_code register is set to the appropriate value, the control\_FSM is forced to the corresponding state. Figure 2 shows the state diagram of the control\_FSM.

Figure 2. State Diagram of the control\_FSM

For every operational mode of the NOR Flash, control\_FSM calls timing\_FSM (flash\_timing\_FSM) to generate the appropriate control signals to access the NOR Flash based on the NOR Flash timing specification. Each operational mode has its own command set. A proper command with specific address and data sequences must be written into the NOR Flash. The defined command set sequences are shown in Table 5. This design supports both Word configuration and Byte configuration of Flash memory. The parameter WORD\_BYTEn defines the Word or Byte configuration (listed in Table 3).

Table 5. NOR Flash Command Sequence

|              |        |       | First<br>Cycle |       | Second<br>Cycle |       | Third<br>Cycle |       | Fourth<br>Cycle |               | Fifth<br>Cycle |       | Sixth<br>Cycle |       |

|--------------|--------|-------|----------------|-------|-----------------|-------|----------------|-------|-----------------|---------------|----------------|-------|----------------|-------|

| Command Se   | quence | Cycle | Word           | Byte  | Word            | Byte  | Word           | Byte  | Word            | Byte          | Word           | Byte  | Word           | Byte  |

| Reset        | Addr   | 1     | XX             | ¢χ    |                 |       |                |       |                 | •             |                |       |                |       |

| 116361       | Data   | '     | 0x             | :fO   |                 |       |                |       |                 |               |                |       |                |       |

| Manufacturer | Addr   | 4     | 0x555          | 0xaaa | 0x2aa           | 0x555 | 0x555          | 0xaaa | 0x              | 00            |                |       |                |       |

| ID           | Data   | 4     | 0x             | aa    | 0x              | 55    | 0x             | 90    | ID from         | ID from Flash |                |       |                |       |

| Sector Erase | Addr   | 6     | 0x555          | 0xaaa | 0x2aa           | 0x555 | 0x555          | 0xaaa | 0x555           | 0xaaa         | 0x2aa          | 0x555 | 5              | SA    |

| Secioi Erase | Data   | 0     | 0xaa           |       | 0x55            |       | 0x80           |       | 0xaa            |               | 0x55           |       | 0x30           |       |

| Chip Erase   | Addr   | 6     | 0x555          | 0xaaa | 0x2aa           | 0x555 | 0x555          | 0xaaa | 0x555           | 0xaaa         | 0x2aa          | 0x555 | 0x555          | Охааа |

| Chip Erase   | Data   | 0     | 0xaa           |       | 0x55            |       | 0x80           |       | 0xaa            |               | 0x55           |       | 0x10           |       |

| Read         | Addr   | 4     | R              | A     |                 |       |                |       |                 |               |                |       |                |       |

| nedu         | Data   | ı     | R              | RD    |                 |       |                |       |                 |               |                |       |                |       |

|              | Addr   | 4     | 0x555          | 0xaaa | 0x2aa           | 0x555 | 0x555          | 0xaaa | P               | A             |                |       |                |       |

| Program      | Data   | 4     | 0x             | aa    | 0x              | 55    | 0x             | a0    | Р               | D             |                |       |                |       |

#### Notes:

- 1. RA: Read Address, located in the sector\_addr register and the other\_addr register.

- 2. RD: Read Data, located in the rxdata register.

- 3. PA: Program /Write Address, located in the sector\_addr register and the other\_addr register.

- 4. PD: Program/Write Data, located in the txdata register.

- 5. xxx: Don't care.

- 6. SA: Sector Address, located in the sector\_add register.

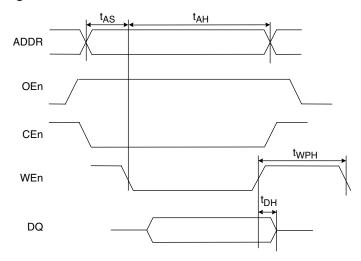

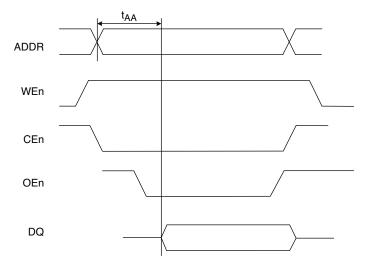

The flash\_timing\_FSM is used to generate every write command and read data cycle timing. In order to write the command or data to the Flash, CEn and WEn must be low and OEn must be high. Addresses are latched on the falling edge of WEn and data are latched on the rising edge of WEn. Figure 3 shows the Flash write timing. To read the data from the Flash memory, the CEn and OEn must be low while WEn is high. Figure 4 shows the Flash read timing.

Figure 3. Flash Write Timing

Figure 4. Flash Read Timing

Table 6. Parameter Descriptions

| Symbol           | Parameter              |  |  |  |

|------------------|------------------------|--|--|--|

| t <sub>AS</sub>  | Address Setup Time     |  |  |  |

| t <sub>AH</sub>  | Address Hold Time      |  |  |  |

| t <sub>DH</sub>  | Data Hold Time         |  |  |  |

| t <sub>WPH</sub> | Write Pulse Width High |  |  |  |

| t <sub>AA</sub>  | Address Access Time    |  |  |  |

The access timing requirements are different for different NOR Flash devices. These timing parameters are defined as constants in the source file. They can be modified accordingly to meet the timing of a specific NOR Flash memory device.

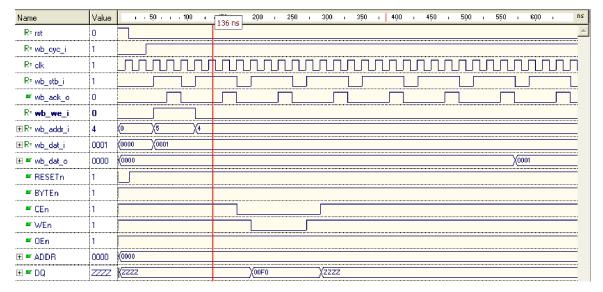

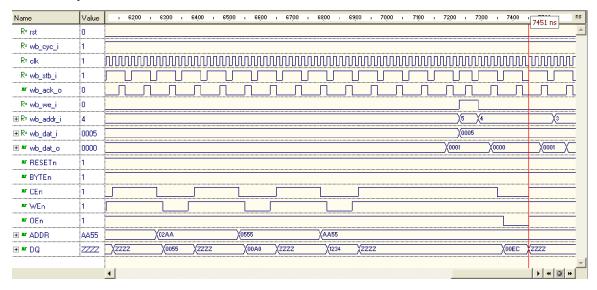

# **Test Bench Description**

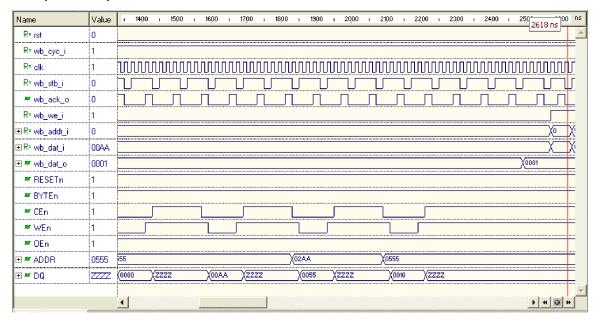

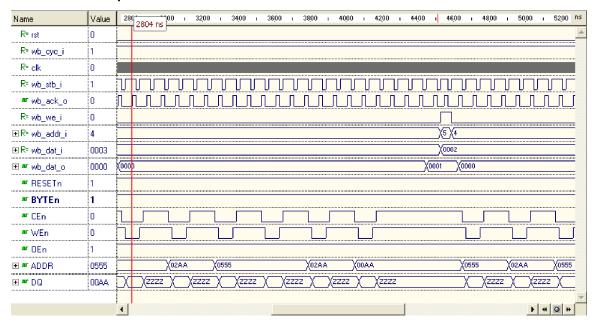

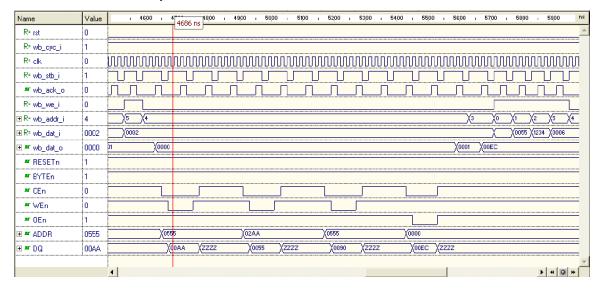

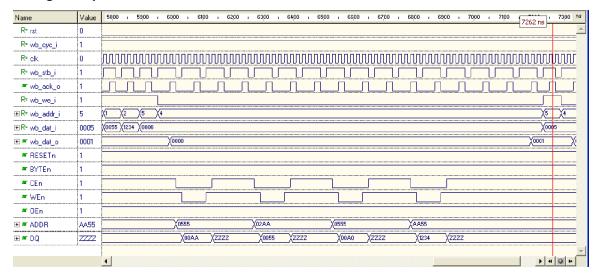

The test bench simulates every operational mode of NOR Flash timing supported in this design.

Figure 5. Reset Operation of NOR Flash

Figure 6. Chip Erase Operation of NOR Flash

Figure 7. Sector Erase Operation of NOR Flash

Figure 8. Read Manufacturer Operation of NOR Flash

Figure 9. Program Operation of NOR Flash

Figure 10. Read Operation of NOR Flash

## **Implementation**

Table 7. Performance and Resource Utilization

| Device Family           | Language | Speed Grade | Utilization<br>(LUTs) | f <sub>MAX</sub> (MHz) | I/Os | Architecture<br>Resources |

|-------------------------|----------|-------------|-----------------------|------------------------|------|---------------------------|

| MachXO2 <sup>TM 1</sup> | Verilog  | -6          | 185                   | >80                    | 80   | N/A                       |

| IVIACITACE              | VHDL     | -6          | 190                   | >80                    | 80   | N/A                       |

| MachXO <sup>TM 2</sup>  | Verilog  | -3          | 182                   | >80                    | 80   | N/A                       |

| IVIACITAC               | VHDL     | -3          | 187                   | >80                    | 80   | N/A                       |

Performance and utilization characteristics are generated using LCMXO2-1200HC-6TG144CES, with Lattice Diamond<sup>™</sup> 1.1 or ispLEVER<sup>®</sup> 8.1 SP1. When using this design in a different device, density, speed, or grade, performance and utilization may vary.

# **Technical Support Assistance**

Hotline: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com

Internet: www.latticesemi.com

## **Revision History**

| Date          | Version | Change Summary                                                               |

|---------------|---------|------------------------------------------------------------------------------|

| April 2010    | 01.0    | Initial release.                                                             |

| November 2010 | 01.1    | Added support for MachXO2 device family and Lattice Diamond design software. |

<sup>2.</sup> Performance and utilization characteristics are generated using LCMXO1200C-3T144C, with Lattice Diamond 1.1 or ispLEVER 8.1 SP1 software. When using this design in a different device, density, speed, or grade, performance and utilization may vary.